TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# **TA1227AP**

# EDTV2 IDENTIFICATION CONTROL SIGNAL DETECTOR

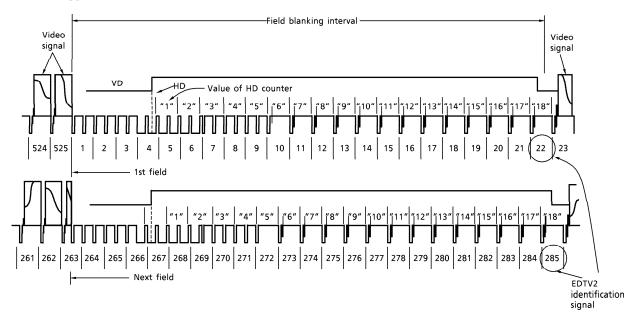

The TA1227AP detects EDTV2 identification signals. It detects the 27 bits on the 22H and 285H lines of each frame and outputs to the read bus. The methods of detection are following.

B1 to B5, and B24 NRZ signal:

Y signal level detection

B25 to B27 (4/7) fsc:

Y signal level detection at BPF output

B6 to B23 fsc phase modulation signal: Converts the IQ demodulation signal of the main signal processing IC to a color difference signal and detects the level

Weight: 1.11g (Typ.)

#### **FEATURES**

- I<sup>2</sup>C bus-controllable

- Y and I, Q inputs

- Compatible with sandcastle pulse (VD, HD, and GP) input

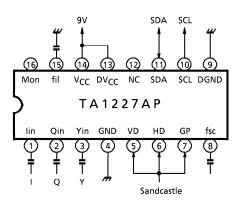

SDA SCL

Auto adjustment of 4/7 fsc BPF fo

Mon (D / A)

#### **BLOCK DIAGRAM**

### 1<sup>2</sup>C bus Det $\mathsf{DV}_\mathsf{CC}$ fsc Det Register 0-11 4/7 Timing → DGND fsc Det Generator

#### PIN ASSIGNMENT DIAGRAM

All capacitors are  $0.01 \mu F$

961001EBA2

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified to the product of the product of the product specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

- TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

fsc

Sandcastle

Mon (BPF)

# **TERMINAL FUNCTION**

| PIN<br>No. | PIN NAME | FUNCTION                                                                                                                                                                                                                                                                                                                     | INTERFACE CIRCUIT                                                                                                                                                                                                                                           |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | l input  | I signal input terminal. Input the I signal to this terminal via a clamping capacitor (0.01 $\mu$ F recommended). The typical input level is 0.3 V <sub>p-p</sub> . This terminal is used to identify bits 6 to 23 of the identification signal. If no I signal is input, connect this terminal to the AC GND.               | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                       |

| 2          | Q input  | Q signal input terminal. Input the Q signal to this terminal via a clamping capacitor (0.01 $\mu$ F recommended). The typical input level is 0.3 V <sub>p-p</sub> . This terminal is used to identify bits 6 to 23 of the identification signal. If no Q signal is input, connect this terminal to the AC GND.               | 2 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                                                                                                                                                                                                     |

| 3          | Y input  | Y signal input terminal. Input the Y signal to this terminal via a clamping capacitor (0.01 $\mu$ F recommended). The typical input level is 1.0 V <sub>p-p</sub> . This terminal is used to identify bits 1 to 5 and 24 to 27 of the identification signal.                                                                 | 3.5v<br>3.5v<br>3.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>7.5v<br>8.0v<br>8.0v<br>1.kΩ<br>8.0v<br>1.kΩ<br>8.0v<br>1.kΩ<br>8.0v<br>1.kΩ<br>8.0v<br>1.kΩ<br>8.0v<br>1.v<br>1.v<br>1.v<br>1.v<br>1.v<br>1.v<br>1.v<br>1. |

| 4          | GND      | GND terminal for analog block                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                           |

| 5          | VD input | VD signal input terminal. Input a signal of positive polarity. The threshold level is 1.5V (typ.). The rising phase of the VD signal acts as the trigger to start the HD count and the 22H and 285H lines are identified. This terminal can also be used to input sandcastle pulses to which VD, HD, and GP are multiplexed. | 2.25V<br>5.0KΩ<br>2.25V<br>2.25V<br>2.25V                                                                                                                                                                                                                   |

| PIN<br>No. | PIN NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                | INTERFACE CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6          | HD input  | HD signal input terminal. Input a signal of positive polarity with a width that can accommodate GP. The threshold level is 3.5V (typ.). Note that VD is canceled if HD rises within 1 $\mu$ s of VD rising. This terminal can also be used to input sandcastle pulses to which VD, HD, and GP are multiplexed.                                          | ο 1κΩ<br>Θ 1κΩ<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Α<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους<br>Αμους |

| 7          | GP input  | Gate pulse input terminal. Input a signal of positive polarity. The threshold level is 7.0V (typ.). The read timing for each 27 bits is determined from the rising phase of the GP signal. Note that Y and I, Q inputs are clamped while GP is high. This terminal can also be used to input sandcastle pulses to which VD, HD, and GP are multiplexed. | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8          | fsc input | Terminal for input of 3.58MHz continuous signal for the IC's internal reference clock. Input a signal locked to the color subcarrier of the video signal to be demodulated. The typical input level is 0.6V <sub>p-p</sub> .                                                                                                                            | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9          | D.GND     | GND pin for digital block                                                                                                                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10         | SCL       | SCL input terminal for I <sup>2</sup> C bus. The threshold level is 2.5V.                                                                                                                                                                                                                                                                               | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PIN<br>No. | PIN NAME           | FUNCTION                                                                                                                                                                                                                     | INTERFACE CIRCUIT                                       |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 11         | SDA                | SDA I/O terminal for I <sup>2</sup> C bus. The threshold level is 2.5V. The current flowing through this terminal should not exceed 3.0mA.                                                                                   | ΛCC                                                     |

| 12         | N.C.               | This terminal is not connected and should be left open.                                                                                                                                                                      | _                                                       |

| 13         | D.V <sub>CC</sub>  | Power supply pin for the digital block. Apply 9.0V (typ.).                                                                                                                                                                   | _                                                       |

| 14         | V <sub>CC</sub>    | Power supply terminal for the analog block. Apply 9.0V (typ.).                                                                                                                                                               | _                                                       |

| 15         | fo adjust-<br>ment | Terminal for connecting $f_0$ automatic adjustment filter of 4/7fsc BPF. The recommended capacitance is $0.01\mu F$ .                                                                                                        | ν <sub>CC</sub> (ξ) |

| 16         | Monitor<br>output  | Terminal for monitoring DAC output for NRZ-Compared level and 4/7fsc BPF output. Write Data D4 of the I <sup>2</sup> C bus switches functions. When "0", the pin is set for DAC output: when "1", for monitoring BPF output. | VCC D/A Out BPF Out BUS CONTROL                         |

# I<sup>2</sup>C BUS MAP

| MODE                     | DATA |        |     |         |                |     |        |      |  |  |  |

|--------------------------|------|--------|-----|---------|----------------|-----|--------|------|--|--|--|

| MODE                     | D7   | D6     | D5  | D4      | D3             | D2  | D1     | D0   |  |  |  |

| WRITE                    |      | Timing |     | Monitor | NRZ-Det. level |     |        |      |  |  |  |

| (Slave Address : BC HEX) |      | (100)  |     | (0)     | (1000)         |     |        |      |  |  |  |

|                          | B1   | B2     | В3  | B4      | В5             | В6  | В7     | В8   |  |  |  |

| READ                     | В9   | B10    | B11 | B12     | B13            | B14 | B15    | B16  |  |  |  |

| (Slave Address : BD HEX) | B17  | B18    | B19 | B20     | B21            | B22 | B23    | B24  |  |  |  |

|                          | B25  | B26    | B27 | _       | _              | _   | P.O.R. | Busy |  |  |  |

( ): Default values are shown in parenthesis.

# I<sup>2</sup>C BUS CONTROL

|   | Timing [sc] |            |  |  |  |  |  |  |  |  |

|---|-------------|------------|--|--|--|--|--|--|--|--|

|   | 001         | -3         |  |  |  |  |  |  |  |  |

|   | 010         | <b>-</b> 2 |  |  |  |  |  |  |  |  |

|   | 011         | <b>– 1</b> |  |  |  |  |  |  |  |  |

| * | 100         | 0          |  |  |  |  |  |  |  |  |

|   | 101         | 1          |  |  |  |  |  |  |  |  |

|   | 110         | 2          |  |  |  |  |  |  |  |  |

|   | 111         | 3          |  |  |  |  |  |  |  |  |

|   | Monitor |                |  |  |  |  |  |

|---|---------|----------------|--|--|--|--|--|

| * | 0       | NRZ-Ref. level |  |  |  |  |  |

|   | 1       | BPF            |  |  |  |  |  |

|   | level | [IIVL] | [III A b-b] |

|---|-------|--------|-------------|

|   | 0000  | 10     | 71.4        |

|   | 0001  | 12     | 85.7        |

|   | 0010  | 14     | 100.0       |

|   | 0011  | 16     | 114.3       |

|   | 0100  | 18     | 128.6       |

|   | 0101  | 20     | 142.9       |

|   | 0110  | 22     | 157.1       |

| Ī | 0111  | 24     | 171.4       |

| * | 1000  | 26     | 185.7       |

|   | 1001  | 28     | 200.0       |

|   | 1010  | 30     | 214.3       |

|   | 1011  | 32     | 228.6       |

|   | 1100  | 34     | 242.9       |

|   | 1101  | 36     | 257.1       |

|   | 1110  | 38     | 271.4       |

|   | 1111  | 40     | 285.7       |

[IRE]

$[mV_{n-n}]$

NRZ-Det.

1sc = 280ns (1 / fsc)

\* Default value

Timing : The phase of the sampling pulse for reading each 27 bits of the

identification signal can be adjusted by 7sc in 1sc steps. Don't use the

data (000).

Monitor : Switches the signal output from pin 16.

NRZ-Det. level : Adjusts the NRZ detection level.

The det. level can be adjusted by 30IRE (= 214mV) in 2IRE steps. There are errors within a tolerance  $\pm$ 3IRE (=  $\pm$ 21.4mV) against upper

values.

P.O.R. (Power On Reset): This bit shows that the bus data has been reset to the default value

when the power is turned ON. After the POR, this bit is "1" for the first data output, then "0" for subsequent output. POR is applied at  $V_{CC} = 6V$

(typ.).

Busy : This bit is "1" while reading the 27 bits of the identification signal on

the 22H and 285H lines, and "0" at other times.

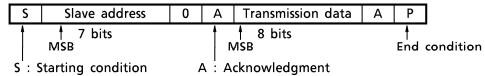

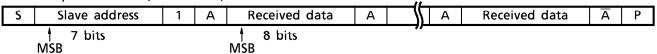

# I<sup>2</sup>C BUS TRANSMISSION AND RECEPTION METHODS

Slave address

| А6 | A5 | Α4 | А3 | A2 | Α1 | Α0 | W/R |

|----|----|----|----|----|----|----|-----|

| 1  | 0  | 1  | 1  | 1  | 1  | 0  | 0/1 |

# Data transmission format (Write mode)

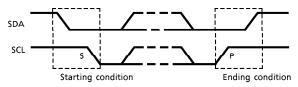

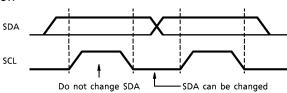

# Starting and ending conditions

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the philips I<sup>2</sup>C patent rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C standard specification as defined by philips.

#### Bit transmission

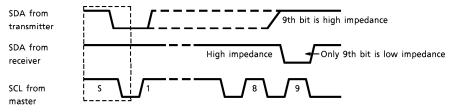

# Acknowledgment

# Data reception format (Read mode)

When receiving data, the master transmitter changes to a receiver immediately after the first acknowledgment, while the slave receiver changes into the transmitter.

The master always creates the end condition.

Detailed specifications conform to the PHILIPS  $I^2C$  Specification.

# **MAXIMUM RATINGS**

| CHARACTERISTIC        | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Power Supply Voltage  | Vcc              | 14.0            | V    |

| Power Dissipation     | $P_{D}$          | 1380 (Note)     | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 20∼6</b> 5 | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>- 55∼150</b> | °C   |

(Note) When using the device at above  $Ta = 25^{\circ}C$ , decrease the power dissipation by 11.2mW for each increase of 1°C.

# **RECOMMENDED OPERATING CONDITIONS**

( $V_{CC} = 9V$ ,  $D.V_{CC} = 9V$ , and  $T_a = 25^{\circ}C$  unless otherwise specified)

| PIN<br>No. | CHARACTERISTIC      | SYMBOL             | MIN. | TYP.     | MAX. | UNIT             | REMARKS                          |

|------------|---------------------|--------------------|------|----------|------|------------------|----------------------------------|

| 13         | D.V <sub>CC</sub>   | D.V <sub>C</sub> C | 8.1  | 9.0      | 9.9  | V                | _                                |

| 14         | VCC                 | ۷ <sub>CC</sub>    | 8.1  | 9.0      | 9.9  | ٧                | _                                |

| 1          | I Input Amplitude   | lin                | 0.15 | 0.3      | 0.35 | V <sub>p-p</sub> | When ID signal demodulated       |

| 2          | Q Input Amplitude   | Qin                | 0.15 | 0.3      | 0.35 | V <sub>p-p</sub> | When ID signal demodulated       |

| 3          | Y Input Amplitude   | Yin                | 0.8  | 1.0      | 1.2  | 1/               | Amplitude between bottom of      |

|            | i input Amplitude   | 1111               | 0.8  | 1.0      | 1.2  | V <sub>p-p</sub> | sync and 100% white              |

| 5          | VD Input Voltage    | VDin               | 1.8  | 1        | 9.0  | ٧                | Pulse high level                 |

| 6          | HD Input Voltage    | HDin               | 3.8  | _        | 9.0  | V                | Pulse high level                 |

| 7          | GP Input Voltage    | GPin               | 7.3  | _        | 9.0  | V                | Pulse high level                 |

| 8          | fsc Input Amplitude | fsc in             | 0.3  | 0.6      | _    | V <sub>p-p</sub> | _                                |

|            |                     |                    |      |          |      |                  | The rising phase should be       |

| 9          | VD Rise Phase       | t <sub>VD</sub>    | 1085 | <b>—</b> | 1130 | $\mu$ s          | before the starting point in the |

|            |                     |                    |      |          |      |                  | 22 / 285H lines.                 |

| 10         | GP Rise Phase       | ten                | 5.6  |          | 7.3  | ,,,              | After fall in H.sync (While      |

|            | Of Mise Finase      | tGP                | 3.0  |          | 7.3  | $\mu$ s          | adjusting from -3sc to +3sc)     |

| 11         | GP Width            | W <sub>GP</sub>    | 1.0  |          | _    | μS               | _                                |

<sup>\*</sup> HD must be input with a line blanking interval such that its width accommodates GP.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 9.0V$ ,  $D.V_{CC} = 9.0V$  and  $Ta = 25^{\circ}C$  unless otherwise specified) DC CHARACTERISTICS Terminal voltages

| PIN<br>No. | CHARACTERISTIC                    | SYMBOL             | TEST<br>CIR-<br>CUIT | MIN. | TYP. | MAX. | UNIT | REMARKS                 |

|------------|-----------------------------------|--------------------|----------------------|------|------|------|------|-------------------------|

| 1          | I Input                           | V1                 | _                    | 3.80 | 4.25 | 4.70 | V    | Pin 7: greater than 7V  |

| 2          | Q Input                           | V2                 | _                    | 3.80 | 4.25 | 4.70 | ٧    | Pin 7 : greater than 7V |

| 3          | Y Input                           | V3                 | _                    | 3.80 | 4.25 | 4.70 | V    | Pin 7 : greater than 7V |

| 4          | GND                               | _                  | _                    | _    | 0    | _    | V    | _                       |

| 8          | fsc Input                         | V8                 | _                    | 6.20 | 6.75 | 7.30 | V    | _                       |

| 9          | D.GND                             | _                  | _                    |      | 0    | _    | ٧    | _                       |

| 13         | D.V <sub>CC</sub>                 | D.V <sub>C</sub> C | _                    |      | 9.0  | _    | V    | _                       |

| 14         | VCC                               | VCC                | _                    |      | 9.0  | _    | ٧    | _                       |

| 15         | f <sub>0</sub> Auto<br>Adjustment | V15                | _                    | 1.0  | 1.5  | 2.0  | ٧    | _                       |

| 16         | Monitor Output                    | V16                |                      | 3.1  | 3.6  | 4.1  | >    | D/A output              |

# **Current consumption**

| PIN<br>No. | CHARACTERISTIC    | SYMBOL             | TEST<br>CIR-<br>CUIT | MIN. | TYP. | MAX. | UNIT |

|------------|-------------------|--------------------|----------------------|------|------|------|------|

| 13         | D.V <sub>CC</sub> | D.I <sub>C</sub> C | _                    | 23.0 | 30.0 | 37.0 | mΑ   |

| 14         | VCC               | ICC                |                      | 10.0 | 12.5 | 15.0 | mΑ   |

# **AC CHARACTERISTICS**

| CHARACTERISTIC                 | SYMBOL             | TEST<br>CIR-<br>CUIT | MIN.   | TYP. | MAX.   | UNIT              | REMARKS                                        |

|--------------------------------|--------------------|----------------------|--------|------|--------|-------------------|------------------------------------------------|

| VD Threshold Level             | $v_{VDth}$         | _                    | 1.3    | 1.5  | 1.7    | V                 | Design value                                   |

| HD Threshold Level             | $V_{HDth}$         | _                    | 3.3    | 3.5  | 3.7    | V                 | Design value                                   |

| GP Threshold Level             | $v_{GPth}$         | _                    | 6.8    | 7.0  | 7.2    | ٧                 | Design value                                   |

| NRZ Detection Errors           | ∆NRZ               | _                    | - 3    | 0    | + 3    | IRE               | Against the level set by bus                   |

|                                |                    |                      | - 21.4 | 0    | + 21.4 | mV                |                                                |

| 4/7fsc Detection Level         | V <sub>47fsc</sub> | _                    | _      | 118  | 150    | mV <sub>p-p</sub> | Design value, f = 2.04545MHz                   |

| BPF Attenuation                | G <sub>1</sub>     | _                    | 20     | _    | _      | dB                | Design value, f = 1MHz                         |

|                                | G3.08              | _                    | 20     | 25   | _      | dB                | Design value, f=3.08MHz                        |

|                                | G <sub>3.58</sub>  | _                    | 30     | 35   | _      | dB                | Design value, f = 3.579545MHz                  |

|                                | G <sub>4.5</sub>   | _                    | 35     | 40   | _      | dB                | Design value, f = 4.5MHz                       |

| BPF Group Delay                | $\tau$ 47fsc       | _                    | _      | 1.2  | _      | μs                | Design value, f = 2.04545MHz                   |

| Sampling Start Phase<br>(Note) | t <sub>SP</sub>    | _                    | 2.79   | 3.07 | 3.35   | μs                | Design value, should be later than rise in GP. |

(Note) Bus data : default

#### VD, HD, AND GP INPUT TIMING

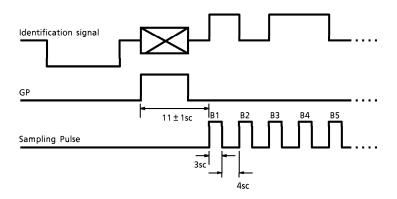

In the TA1227AP, the rise in VD triggers the start of the HD count. A window is opened between the 17th and 18th fall in HD during which GP is sampled (see figure). The rise in the sampled GP is used as a reference for creating a sampling pulse for reading the bits of the EDTV2 identification signal. Therefore, it should be set so that VD rises during the 4H and 267H lines. The sampling pulse for the first bit rises 11sc after the rise in the reference gate pulse. The pulse width ratio is 3: 4 (high: low). The sampling pulse phasing is under bus control (-3sc to +3cs).

The threshold levels of the respective pulses are : VD : 1.5V, HD : 3.5V, and GP : 7.0V. Note that, if HD rises within  $1\mu$ s of a rise in VD, that VD is canceled.

The TA1227AP will accept the input of sandcastle pulses to which VD, HD, and GP are multiplexed.

#### **HD, VD TIMINGS**

# 22 / 285H LINE

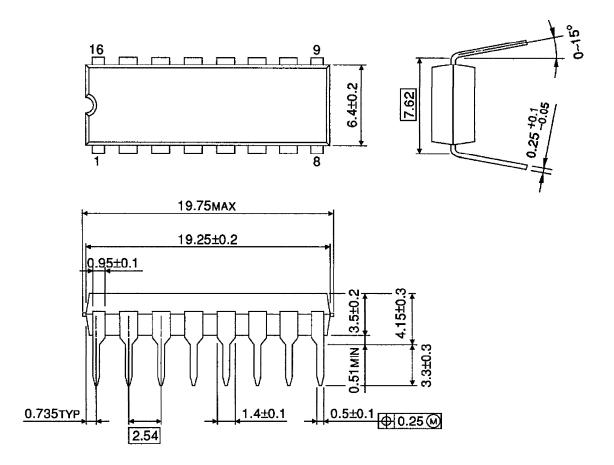

# **OUTLINE DRAWING**

DIP16-P-300-2.54A Unit: mm

Weight: 1.00g (Typ.)