# Coaxial transceiver interface for Ethernet/Thin Ethernet

**NE8392C**

#### DESCRIPTION

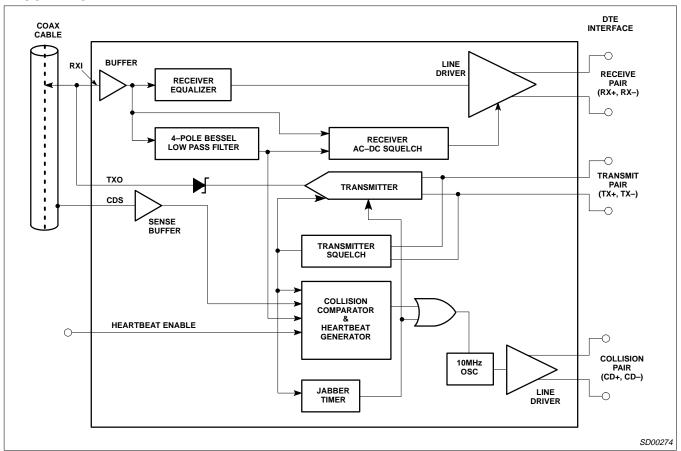

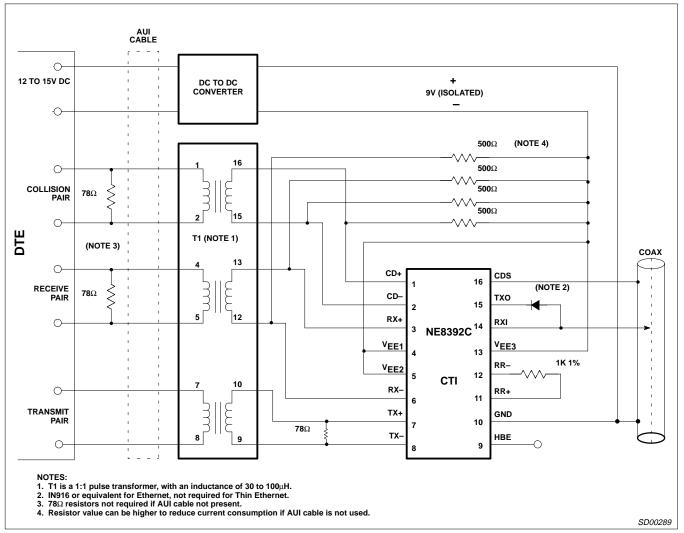

The NE8392C Coaxial Transceiver Interface (CTI) is a bipolar coaxial line driver/receiver for Ethernet (10base5) and Thin Ethernet (10base2) local area networks. The CTI is connected between the coaxial cable and the Data Terminal Equipment (DTE) and consists of a receiver, transmitter, receive-mode collision detector, heartbeat generator and jabber timer (see Block Diagram). The transmitter output connects directly to a doubly terminated  $50\Omega$  cable, while the receiver output, collision detector output and transmitter input are connected to the DTE through isolation transformers. Isolation between the CTI and the DTE is an IEEE 802.3 requirement that can be met on signal lines by using a set of pulse transformers normally available in a standard 16-pin DIP. Power isolation for the CTI is achieved using DC-to-DC conversion through a power transformer (see Figure 1, Connection Diagram).

During transmission the jabber timer is initiated to disable the CTI transmitter in the event of a longer than legal length data packet. Receive-mode collision detection circuitry monitors the signals on the coaxial cable to determine the presence of colliding packets and signals the DTE in the event of a collision. At the end of every transmission the heartbeat generator creates a pseudo collision for a short time to ensure that the collision circuitry is functioning correctly. The heartbeat function can be disabled for repeater applications.

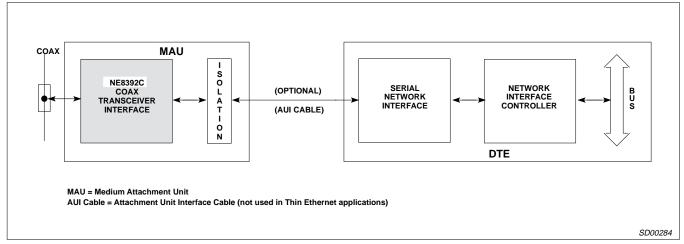

The CTI is normally part of a three chip set that implements a complete Ethernet/ Thin Ethernet network interface for a DTE (see Figure 2, Interface Diagram). The other chips are a Serial Network Interface (SNI) and a Network Interface Controller (NIC). The SNI provides Manchester Encoding and Decoding while the NIC handles the media access protocol and buffer management tasks.

### **FEATURES**

- Compatible with Ethernet II IEEE 802.3 10base5 and 10base2, and ISO 8802/3 interface specifications

- 100% drop-in compatible with industry standard 8392 sockets

- Integrates all transceiver electronics except signal and power isolation

- Only one external resistor required for setting coaxial signaling current

- Jabber timer function integrated on chip

- Heartbeat generator can be externally disabled for operation as IEEE 802.3 compatible repeaters

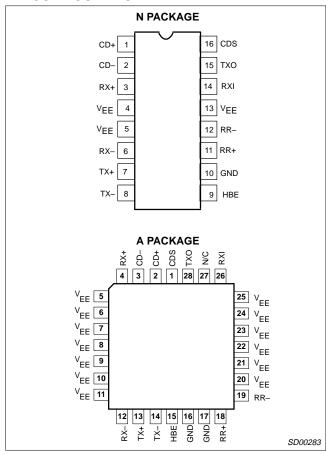

#### PIN CONFIGURATION

- On-chip precision voltage reference for receive mode collision detection

- Squelch circuitry on all signal inputs rejects noise

- Full ESD protection

- Standard 16-pin DIP and 28-pin PLCC packages

- Power-on reset prevents glitches on coaxial cable during power up.

- Also available in advanced low-power BiCMOS technology. (See selection chart and data sheets for the NE83C92, NE83Q92 or NE83Q93 for appropriate optimal usages)

### ORDERING INFORMATION

| DESCRIPTION                               | TEMPERATURE RANGE | ORDER CODE | DWG#     |  |

|-------------------------------------------|-------------------|------------|----------|--|

| 16-Pin Plastic Dual In-Line Package (DIP) | 0 to +70°C        | NE8392CN   | SOT28-4  |  |

| 28-Pin Plastic Lead Chip Carrier (PLCC)   | 0 to +70°C        | NE8392CA   | SOT261-3 |  |

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

### **PIN DESCRIPTIONS**

| PIN NO.<br>N PKG | PIN NO.<br>PLCC     | SYMBOL          | DESCRIPTION                                                                                                                                                                                                                 |  |  |

|------------------|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 2              | 2<br>3              | CD+<br>CD-      | Collision Outputs. Balanced differential line driver outputs which send a 10MHz oscillation signal to the DTE in the event of a collision, jabber interrupt or heartbeat test.                                              |  |  |

| 3<br>6           | 4<br>12             | RX+<br>RX–      | Receiver Outputs. Balanced differential line driver outputs which send the received signal to the DTE.                                                                                                                      |  |  |

| 7<br>8           | 13<br>14            | TX+<br>TX-      | Transmitter Inputs. Balanced differential line receiver inputs which accept the transmission signal from the DTE and apply it to the coaxial cable at TXO once it meets Tx squelch threshold.                               |  |  |

| 9                | 15                  | HBE             | Heartbeat Enable. The heartbeat function is disabled when this pin is connected to $V_{\text{EE}}$ and enabled when connected to GND or left floating.                                                                      |  |  |

| 11<br>12         | 18<br>19            | RR+<br>RR-      | External Resistor. A 1k $\Omega$ (1%) resistor connected between these pins establishes the signaling current at TXO. RR– is internally connected to V <sub>EE</sub> .                                                      |  |  |

| 14               | 26                  | RXI             | Receiver Input. This pin is connected directly to the coaxial cable. Received signals are equalized, amplified, and sent to the DTE through the RX+ pins once it meets Rx squelch threshold.                                |  |  |

| 15               | 28                  | ТХО             | Transmitter Output. This pin is connected directly (Thin Ethernet) or through an external isolating diode (Ethernet) to the coaxial cable.                                                                                  |  |  |

| 16               | 1                   | CDS             | Collision Detect Sense. Ground sense connection for the collision detection circuitry. This pin should be directly connected to the coaxial cable shield to prevent ground drops affecting the collision threshold voltage. |  |  |

| 10               | 16<br>17            | GND             | Positive Supply Pin.                                                                                                                                                                                                        |  |  |

| 4<br>5<br>13     | 5 to 11<br>20 to 25 | V <sub>EE</sub> | Negative supply pins. These pins also serve as a low thermal resistance path for extracting heat from the die. They should, therefore, be connected to a large metal area on the PC board.                                  |  |  |

### NOTE:

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                         | RATING      | UNIT |

|-------------------|---------------------------------------------------|-------------|------|

| V <sub>EE</sub>   | Supply voltage <sup>1</sup>                       | -12         | V    |

| V <sub>IN</sub>   | Voltage at any input <sup>1</sup>                 | 0 to −12    | V    |

| T <sub>STG</sub>  | Storage temperature range                         | -65 to +150 | °C   |

| T <sub>SOLD</sub> | Lead soldering temperature (10sec.)               | +300        | °C   |

| $T_J$             | Recommended max junction temperature <sup>2</sup> | +130        | °C   |

| $\theta_{JA}$     | Thermal impedance (N and A packages)              | 60          | °C/W |

### NOTE:

1. 100% measured in production.

2. The junction temperature is calculated from the following expression:  $T_J = T_A + \theta_{JA} \left[ V_{EE} \left( 0.08 + n \times 0.05 / 100 \right) + 8 \left( V_{EE} - 2 \right) / R \right]$

$\begin{array}{lll} T_A & = & \text{Ambient temperature in }^\circ C. \\ \theta_{JA} & = & \text{Thermal resistance of package.} \\ V_{EE} & = & \text{Normal operating supply voltage in volts.} \end{array}$

n = Percentage transmitter duty cycle.  $R = Pull down resistors on the RX and CD pins in <math>\Omega$ .

The N package is specially designed to have a low  $\theta_{JA}$  by directly connecting the four center Pins 4, 5, 12, and 13 to the die attachment area. These four pins then provide a conductive heat flow path from the die to the PCB where they should be soldered to a large area  $V_{EE}$  track. For the A package, Pins 5 to 11 and 19 to 25 should similarly be soldered to a large area  $V_{EE}$  and rack.

<sup>1.</sup> The IEEE 802.3 name for CD is CI; for RX is DI; for TX is DO.

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

### **BLOCK DIAGRAM**

1995 May 1 3

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

### **ELECTRICAL CHARACTERISTICS**

$V_{EE} = -9V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  unless otherwise specified 1,2. No external isolation

| SYMBOL            | PARAMETER                                                               | TEST CONDITIONS                             | LIMITS               |       |                      | UNIT |  |

|-------------------|-------------------------------------------------------------------------|---------------------------------------------|----------------------|-------|----------------------|------|--|

|                   |                                                                         |                                             | MIN                  | TYP   | MAX                  | וואט |  |

| V <sub>POR</sub>  | Power–on reset voltage. Transmitter disabled for $ V_{EE}  <  V_{POR} $ |                                             |                      | -6.5  |                      | V    |  |

|                   | Supply current non-transmitting                                         |                                             |                      | -80   | -130                 | mA   |  |

| IEE               | Supply current transmitting                                             |                                             |                      | -125  | -180                 |      |  |

| I <sub>RXI</sub>  | Receive input bias current                                              | $V_{RXI} = 0V$                              | -2                   |       | +25                  | μΑ   |  |

| I <sub>CDS</sub>  | Cable sense input bias current                                          | V <sub>CDS</sub> = 0V                       |                      | +2    | +6                   | μΑ   |  |

| V <sub>IH</sub>   | HBE input HIGH voltage                                                  |                                             | V <sub>EE</sub> +1.4 |       |                      | V    |  |

| V <sub>IL</sub>   | HBE input LOW voltage                                                   |                                             |                      |       | V <sub>EE</sub> +0.4 | V    |  |

| I <sub>IH</sub>   | HBE input HIGH current                                                  | V <sub>HBE</sub> = 0V                       |                      | 250   | 500                  | μΑ   |  |

| I <sub>IL</sub>   | HBE input LOW current                                                   | $V_{HBE} = V_{EE}$                          |                      | -500  | -1000                | μΑ   |  |

| I <sub>TDC</sub>  | Transmit output DC current level <sup>3</sup>                           |                                             | -37                  | -41   | -45                  | mA   |  |

| I <sub>TAC</sub>  | Transmit output AC current level <sup>3</sup>                           |                                             | ±28                  |       | ±l <sub>TDC</sub>    | mA   |  |

| I <sub>TX10</sub> | Transmit current                                                        | V <sub>TXO</sub> = −10V                     | -250                 |       | +250                 | μΑ   |  |

| V <sub>ТСОМ</sub> | Transmitter output voltage compliance <sup>4</sup>                      |                                             |                      |       | -3.7                 | V    |  |

| V <sub>CD</sub>   | Collision threshold <sup>5</sup>                                        | Measured by applying<br>DC voltage at RXI   | -1450                | -1530 | -1580                | mV   |  |

| V <sub>OD</sub>   | Differential output voltage – non idle at RX $\pm$ and CD $\pm^6$       |                                             | ±600                 |       | ±1200                | mV   |  |

| V <sub>OB</sub>   | Differential output voltage imbalance – idle at RX $\pm$ and CD $\pm^7$ |                                             |                      |       | <u>+</u> 40          | mV   |  |

| V <sub>OC</sub>   | Output common mode voltage at RX± and CD±                               |                                             | -1.5                 | -2    | -2.5                 | V    |  |

| V <sub>RS</sub>   | Receiver squelch threshold                                              | V <sub>RXI</sub> average DC                 | -130                 | -250  | -370                 | mV   |  |

| V <sub>TS</sub>   | Transmitter squelch threshold                                           | (V <sub>TX+</sub> – V <sub>TX</sub> –) peak | -175                 | -225  | -300                 | mV   |  |

| R <sub>RXI</sub>  | Shunt resistance at RXI non–transmitting                                |                                             | 100                  |       |                      | kΩ   |  |

| C <sub>RXI</sub>  | Input capacitance at RXI                                                |                                             |                      | 2     |                      | pF   |  |

| R <sub>TXO</sub>  | Shunt resistance at TXO transmitting                                    |                                             |                      | 10    |                      | kΩ   |  |

- 1. Currents flowing into device pins are positive. All voltages are referenced to ground unless otherwise specified. For ease of interpretation, the parameter limit that appears in the MAX column is the largest value of the parameter, irrespective of sign. Similarly, the value in the MIN column is the smallest value of the parameter, irrespective of sign.

- All typicals are for  $V_{EE} = -9V$  and  $T_A = 27^{\circ}C$ .  $I_{TDC}$  is measured as  $(V_{MAX} + V_{MIN})/(2 \times 25)$  where  $V_{MAX}$  and  $V_{MIN}$  are the max and min voltages at TXO with a  $25\Omega$  load between TXO and GND.  $I_{TAC}$  is measured as  $(V_{MAX} V_{MIN})/(2 \times 25)$ . The TXO pin shall contain AC size through the property of the type of type

- Collision threshold for an AC signal is within 10% of V<sub>CD</sub>.

- Measured on secondary side of isolation transformer (see Connection Diagram, Figure 1). The transformer has a 1:1 turns ratio with an inductance between 30 and 100 $\mu H$  at 5MHz.

- 7. Measured as the voltage difference between the RX pins or the CD pins with the transformer removed.

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

#### **TIMING CHARACTERISTICS**

$V_{EE} = -9V \pm 5\%$ ;  $T_A = 0$  to  $70^{\circ}$ C, unless otherwise specified 1. No external isolation diode on TXO.

| SYMBOL            | PARAMETER                                                                                                        | TEST CONDITIONS                   | LIMITS |             |                      | LINUT |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|-------------|----------------------|-------|

|                   |                                                                                                                  |                                   | MIN    | TYP         | MAX                  | UNIT  |

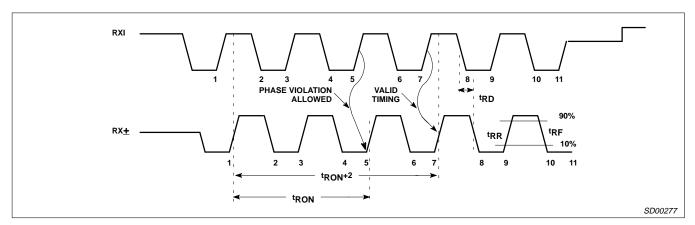

| t <sub>RON</sub>  | Receiver start up delay RXI to RX± (Figure 3) First received bit on RX±                                          | V <sub>RXI</sub> = -2V peak       |        |             | 5                    | bits  |

|                   | First validly timed bit on RX±                                                                                   |                                   |        |             | t <sub>RON</sub> +2  |       |

| $t_{RD}$          | Receiver prop. delay RXI to RX±                                                                                  | V <sub>RXI</sub> = -2V peak       |        | 35          | 50                   | ns    |

| t <sub>RR</sub>   | Differential output rise time on RX± and CD±2,3                                                                  |                                   |        | 5           |                      | ns    |

| t <sub>RF</sub>   | Differential output fall time on RX± and CD±2,3                                                                  |                                   |        | 5           |                      | ns    |

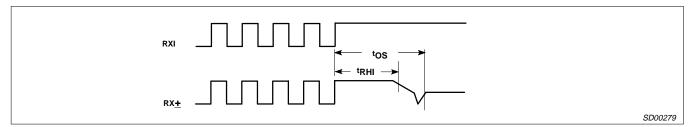

| tos               | Differential output settling time on RX $\pm$ and CD $\pm$ to V <sub>OB</sub> = 40mV <sup>2</sup> (see Figure 4) |                                   |        | 1           |                      | μs    |

| t <sub>RJ</sub>   | Receiver and cable total jitter                                                                                  |                                   |        | ±3          |                      | ns    |

| t <sub>RHI</sub>  | Receiver high to idle time                                                                                       | Measured to +210mV                | 150    |             | 850                  | ns    |

| t <sub>RM</sub>   | Rise and fall time matching on RX± and CD±                                                                       | t <sub>RF</sub> – t <sub>RR</sub> |        | 0.4         |                      | ns    |

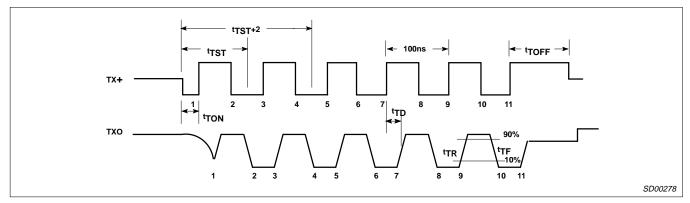

| t <sub>TST</sub>  | Transmitter start–up delay TX± to TXO (Figure 5) First transmitted bit on TXO                                    | V <sub>TX</sub> ± = −1V peak      |        | 1           | 2                    | bits  |

|                   | First validly timed bit                                                                                          |                                   |        | <del></del> | t <sub>TST</sub> + 2 | 1     |

| t <sub>TD</sub>   | Transmitter prop delay TX± to TXO (see Figure 5)                                                                 | V <sub>TX</sub> ± = 1V peak       |        | 35          | 50                   | ns    |

| t <sub>TR</sub>   | Transmitter rise time 10% to 90% (see Figure 5)                                                                  |                                   |        | 25          |                      | ns    |

| t <sub>TF</sub>   | Transmitter fall time 10% to 90% (see Figure 5)                                                                  |                                   |        | 25          |                      | ns    |

| t <sub>TM</sub>   | t <sub>TF</sub> – t <sub>TR</sub> mismatch                                                                       |                                   |        | ±2          |                      | ns    |

| t <sub>TS</sub>   | Transmitter added skew <sup>4</sup>                                                                              |                                   |        | ±2          |                      | ns    |

| t <sub>TON</sub>  | Transmitter turn on pulse width (see Figure 5)                                                                   | V <sub>TX</sub> ± = 1V peak       | 10     |             | 40                   | ns    |

| t <sub>TOFF</sub> | Transmitter turn off pulse width (see Figure 5)                                                                  | V <sub>TX</sub> ± = 1V peak       | 150    | 250         | 340                  | ns    |

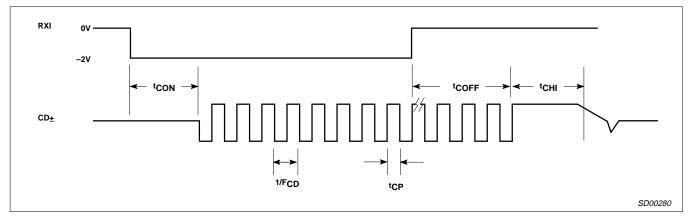

| t <sub>CON</sub>  | Collision turn on delay (see Figure 6)                                                                           | 0V to -2V step at RXI             |        |             | 13                   | bits  |

| t <sub>COFF</sub> | Collision turn off delay (see Figure 6)                                                                          | –2V to 0V step at RXI             |        |             | 16                   | bits  |

| t <sub>CHI</sub>  | Collision high to idle time (see Figure 6)                                                                       | Measured to +210mV                | 150    |             | 850                  | ns    |

| f <sub>CD</sub>   | Collision frequency (see Figure 6)                                                                               |                                   | 8.0    | 10          | 12.5                 | MHz   |

| t <sub>CP</sub>   | Collision signal pulse width (see Figure 6)                                                                      |                                   | 35     |             | 70                   | ns    |

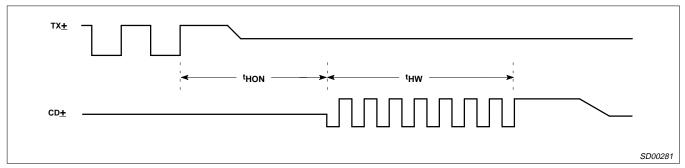

| t <sub>HON</sub>  | Heartbeat turn on delay (see Figure 7)                                                                           |                                   | 0.6    |             | 1.6                  | μs    |

| t <sub>HW</sub>   | Heartbeat test duration (see Figure 7)                                                                           |                                   | 0.5    |             | 1.5                  | μs    |

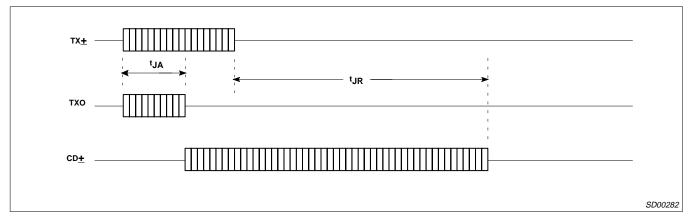

| t <sub>JA</sub>   | Jabber activation delay measured from TX± to CD± (see Figure 8)                                                  |                                   | 20     |             | 60                   | ms    |

| $t_{JR}$          | Jabber reset delay measured from TX± to CD± (see Figure 8)                                                       |                                   | 250    |             | 750                  | ms    |

#### NOTES

- 1. All typicals are for  $V_{EE} = -9V$  and  $T_A = 27^{\circ}C$ .

- Measured on secondary side of isolation transformer (see Figure 1, Connection Diagram). The transformer has a 1:1 turn ratio with an inductance between 30 and 100μH at 5MHz.

- The rise and fall times are measured as the time required for the differential voltage to change from -225mV to +225mV, or +225mV to -225mV, respectively.

- 4. Difference in propagation delay between rising and falling edges at TXO.

### **FUNCTIONAL DESCRIPTION**

The NE8392C contains four main functional blocks (see Block Diagram). These are:

- The receiver which takes data from the coaxial cable and sends it to the DTE.

- The transmitter which receives data from the DTE and sends it onto the coaxial cable.

- c. The collision detection and heartbeat generation circuitry which indicates to the DTE any collision on the coaxial cable and tests

for collision circuitry functionality at the end of every transmission.

d. The jabber timer which disables the transmitter in the event of a longer than legal length data packet.

### **Receiver Functions**

The receiver consists of an input buffer, a cable equalizer, a 4-pole Bessel low pass filter, a squelch circuit and a differential line driver.

The buffer provides high input resistance and low input capacitance to minimize loading and reflections on the coaxial cable.

1995 May 1 5

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

The equalizer is a high pass filter that compensates for the low pass effect of the coaxial cable and results in a flatband response over all signal frequencies to minimize signal distortion.

The 4-pole Bessel low pass filter extracts the average DC voltage level on the coaxial cable for use by the receiver squelch and collision detection circuits.

The receiver squelch circuit prevents noise on the coaxial cable from falsely triggering the receiver in the absence of a true signal. At the beginning of a packet, the receiver turns on when the DC level from the low pass filter is lower than the DC squelch threshold. For normal signal levels this will take less than 500ns, or 5 bits. However, at the end of a packet, a fast receiver turn off is needed to reject both dribble bits on the coaxial cable and spurious responses due to settling of the on-chip bandpass filter. This is accomplished by an AC timing circuit that disables the receiver if the signal level on the coaxial cable remains high for typically 250ns and only enables the receiver again after approximately 1µs. Figures 3 and 4 illustrate receiver timing.

The differential line driver provides typically  $\pm 900$ mV signals to the DTE with less than 7ns rise and fall times. When in idle state (no received signal) its outputs provide <20mV differential voltage offset to minimize DC standing current in the isolation transformer. The line driver outputs are emitter followers and, for Ethernet applications where they drive a  $78\Omega$  transmission line, require a  $500\Omega$  pull-down resistor to  $V_{EE}$ . For Thin Ethernet applications where the AUI cable is not used, the pull-down resistor can be increased to 1.5k $\Omega$  to save power consumption.

#### **Transmitter Functions**

The transmitter has differential inputs and an open collector current driver output. The differential input common mode voltage is established by the CTI and should not be altered by external circuitry. Controlled rise and fall times of 25ns (±5ns) minimize higher harmonic components in the transmitted spectrum, while matching of these rise and fall times to typically 2ns minimizes signal jitter. The drive current levels of the CTI are set by an on-chip bandgap voltage reference and an external 1% resistor. An on-chip isolation diode is provided to reduce the transmitter's coaxial cable load capacitance. For Thin Ethernet applications, no further external isolation diode is required, since the NE8392C meets the capacitive loading specifications. For Ethernet applications a further external diode should be added to reduce loading capacitance.

The transmitter squelch circuit ensures that the transmitter can only be enabled by negative-going differential signals of typically greater than 225mV in magnitude and 15ns in duration. The transmitter will be disabled at the end of a packet if there are no negative going signals of greater than 225mV for more than typically 250ns. Figure 5 illustrates transmitter timing.

### **Collision Functions**

The collision detection scheme implemented in the NE8392C is receive mode detection, which detects a collision between any two stations on the network with certainty at all times, irrespective of whether or not the local DTE is producing one of the colliding

signals. This is the only detection scheme allowed by the IEEE 802.3 standard for both repeater and non-repeater nodes.

The collision circuitry consists of the 4-pole Bessel low pass filter, a comparator, a precision voltage reference that sets up the collision threshold, a heartbeat generator, a 10MHz oscillator, and a differential line driver.

The collision comparator monitors the DC level at the output of the low pass filter and enables the line driver if it is more negative than the collision threshold. A collision condition is indicated to the DTE by a 10MHz oscillation signal at the CD outputs and typically occurs within 700ns of the onset of the collision. The collision signal begins with a negative-going pulse and ends with a continuous high-to-idle state longer than 170ns. Figure 6 illustrates collision timing.

At the end of every transmission, the heartbeat generator creates a pseudo collision to ensure that the collision circuitry is properly functioning. This pseudo collision consists of a  $1\mu s$  burst of 10 MHz oscillation at the line driver outputs approximately  $1\mu s$  after the end of the transmission. The heartbeat function can be disabled externally by connecting the HBE (heartbeat enable) to  $V_{EE}.$  This allows the CTI to be used in repeater applications. Figure 7 illustrates heartbeat timing.

As with the receiver outputs, the collision outputs also require a pull down resistor to  $V_{\text{EE}}$  and maintain <20mV differential voltage offset in the idle state to minimize DC standing current in the isolation transformers.

### **Jabber Functions**

The jabber timer monitors the transmitter and inhibits transmission if it is active for longer than typically 30ms. The jabber circuit then enables the collision outputs for the remainder of the data packet and for typically 450ns (unjab time) after it has ended. At this point the transmitter becomes uninhibited. Figure 8 illustrates jabber timing.

### **Detection of Coaxial Cable Faults**

In the NE8392C there is no internal loopback path from the TX inputs to the RX outputs. This means that, when the local DTE is transmitting, the signal will only be present at the receiver outputs RX+ and RX– if it appears on the coaxial cable and is larger than the receiver squelch threshold  $V_{RS}.$  If a short circuit fault condition occurs at the cable connector to the CTI, then no signal will appear at the receiver outputs. An intelligent DTE can, therefore, detect this fault. If the fault is an open circuit, then a continuous collision signal will be sent to the DTE, provided the average DC voltage at the RXI pin is greater than the typical collision threshold of  $-1.53 \rm V.$

If a short or open circuit occurs elsewhere on the coaxial cable, the resulting reflections can result in an impedance at the CTI of any value between a short circuit and  $50\Omega$ , depending on the distance of the CTI from the fault. The upper limit of  $50\Omega$  results from the fact that the coaxial cable is terminated in  $50\Omega$  at both ends. Faults on the cable itself are, therefore, not guaranteed to be detected by simply monitoring the RX and CD pins when in the transmit mode, and more sophisticated schemes may be necessary.

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

Figure 1. Connection Diagram

Figure 2. Interface Diagram for Ethernet/Thin Ethernet Local Area Network

1995 May 1 7

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

Figure 3. Receiver Timing

Figure 4. Receiver End-of-Packet Timing

Figure 5. Transmitter Timing

Figure 6. Collision Timing

# Coaxial transceiver interface for Ethernet/Thin Ethernet

NE8392C

Figure 7. Heartbeat Timing

Figure 8. Jabber Timing