# Designing With the Si9978DW Configurable H-Bridge Controller

#### Wharton McDaniel

Currently, there are a number of fully integrated H-bridges on the market. Both bipolar and MOS technologies have been used to create these parts. However, all of them suffer from problems such as limited current handling capability, large package size, and difficulty of assembly. The Si9978DW addresses these problems with an architecture that allows flexible current handling capability, small size, and ease of assembly. Instead of trying to integrate the power devices with the controller on a single piece of silicon, the Si9978DW approach is to separate the controller from the MOSFETs. The benefit is efficient manufacture of both the controller and the MOSFETs, the flexibility to select the optimum MOSFET for the application, and the ability to use surface-mount parts for both the controller and MOSFETs which makes assembly easier. Altogether this means a low cost H-bridge solution.

The Si9978DW is a monolithic controller designed to be used with LITTLE FOOT® power MOSFETs to create an all-n-channel H-bridge or two separate half bridges. In addition to this functional flexibility, the dual function allows standardization of components and reduces inventory costs. The Si9978DW features integral high-side drive circuitry and an internal voltage regulator, which allows operation over a 20to 40-V dc input voltage range. Protection features include cross-conduction protection, current limiting, and undervoltage lockout. The FAULT outputs indicate when undervoltage or overcurrent shutdown has occurred. The Si9978DW is packaged in a 24-pin wide body SOIC.

#### **CONTROL LOGIC**

The Si9978 has two modes of operation, full H-bridge, and independent half-bridge. The mode of operation determines the function of the input pins and the FAULT outputs. With the MODE pin at logic 1, which is the default condition, the Si9978 functions as a full H-bridge. With the MODE pin at logic 0, the Si9978DW functions as two independent half-bridges. The definitions of the control inputs depend on the mode of operation. All control inputs are pulled up to V<sub>DD</sub>. The FAULT outputs are open drain. Truth Tables have been provided for each mode of operation.

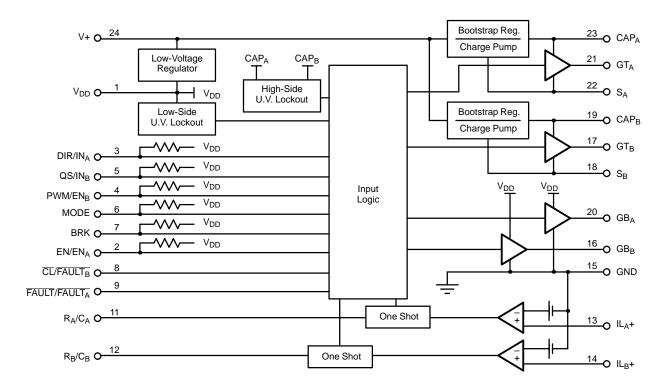

FIGURE 1. The Si9978 is made up of the control logic, the gate drive outputs, V<sub>DD</sub> regulator, and protection circuitry.

Document Number: 70574 08-Jun-00

#### **Full H-Bridge Operation**

When operating as a full H-bridge, the control inputs become DIR, QS, PWM, BRK, and EN. When connecting the bridge for anti-phase operation, the DIR input is driven by the control system PWM signal. When connected for sign-magnitude operation, the DIR input controls direction, and the system PWM signal drives the PWM input.

#### Independent Half-Bridge Operation

In the independent half-bridge mode, the control inputs become the independent controls for each half-bridge, INA, ENA, INB, ENB. The BRK input is not functional in this mode of operation.

#### **Gate Drive Outputs**

Each half-bridge output is driven by a pair of n-channel MOSFETs. These are controlled by a low- and a high-side gate driver. They have been designed to drive a 600-pF load with a 110-ns rise time and a 50-ns fall time.

The low-side gate is driven directly from the commutation logic and is powered by  $V_{DD}$ . This means that  $V_{DD}$  must be decoupled with a 1- $\mu$ F capacitor; otherwise the turn-on surge current can cause  $V_{DD}$  to drop to the level of an undervoltage condition. The high side is a floating circuit powered from a combination bootstrap/charge pump supply. The bootstrap capacitor is charged to  $V_{DD}$  when ever the low-side MOSFET is turned on. At all other times, the charge pump keeps the bootstrap capacitor charged, replacing the charge used in powering the high-side circuitry and in turning on the MOSFET.

The value of the bootstrap capacitor is a function of the MOSFET being driven. The bootstrap voltage should not drop more than 1 V as the result of a MOSFET turn-on. For a 60-V dual n-channel MOSFET like the Si4946EY, 30 nC (Qg) is required for turn-on at a Vgs of 10 V. Using the equation C = Qg/V<sub>GS</sub>, 30 nF is required to provide sufficient charge for turn-on. To meet the criterion of dropping only 1 V at turn-on, the capacitor needs to be 10 times as large, making the equation  $C_{BOOT} = 10(Qg/V_{GS})$ . This makes the minimum value of  $C_{BOOT} = 10(Qg/V_{GS})$ . This makes the minimum value of C<sub>BOOT</sub> equal to 0.039  $\mu$ F. Table 3 gives minimum recommended values for several MOSFETs that might be used with the Si9979. This minimum recommended value is one standard value above the minimum calculated value.

| TABLE 1. H-BRIDGE MODE |                         |                        |                        |                         |     |                   |                   |     |                 |                 |                 |                           |                              |                                    |

|------------------------|-------------------------|------------------------|------------------------|-------------------------|-----|-------------------|-------------------|-----|-----------------|-----------------|-----------------|---------------------------|------------------------------|------------------------------------|

| MODE                   | DIR/<br>IN <sub>A</sub> | EN/<br>EN <sub>A</sub> | QS/<br>IN <sub>B</sub> | PWM/<br>EN <sub>B</sub> | BRK | IL <sub>A</sub> + | IL <sub>B</sub> + | GTA | GB <sub>A</sub> | GT <sub>B</sub> | GB <sub>B</sub> | CL/<br>FAULT <sub>B</sub> | FAULT/<br>FAULT <sub>A</sub> | Condition                          |

| 1                      | 1                       | 1                      | 1                      | Л                       | 0   | L                 | Х                 | н   | L               | L               | L               | 1                         | 1                            |                                    |

| 1                      | 1                       | 1                      | 0                      |                         | 0   | L                 | Х                 | Л   | L               | L               |                 | 1                         | 1                            | Normal<br>Operation                |

| 1                      | 0                       | 1                      | 1                      | Л                       | 0   | L                 | Х                 | L   | Л               | Н               | L               | 1                         | 1                            |                                    |

| 1                      | 0                       | 1                      | 0                      |                         | 0   | L                 | Х                 | L   |                 | Л               | L               | 1                         | 1                            |                                    |

| 1                      | Х                       | 1                      | Х                      | Х                       | 1   | L                 | Х                 | L   | н               | L               | Н               | 1                         | 1                            | Brake                              |

| 1                      | Х                       | 0                      | Х                      | Х                       | Х   | L                 | Х                 | L   | L               | L               | L               | 1                         | 1                            | Disable                            |

| 1                      | Х                       | 1                      | Х                      | Х                       | 0   | Л                 | Х                 | L   | L               | L               | L               |                           |                              | Over-current                       |

| 1                      | х                       | Х                      | Х                      | х                       | Х   | х                 | х                 | L   | L               | L               | L               | 1                         | 0                            | Undervoltage<br>on V <sub>DD</sub> |

| TABLE 2. HALF-BRIDGE MODE |                         |                        |                        |                         |     |                   |                   |     |                 |                 |                 |                           |                              |                                    |

|---------------------------|-------------------------|------------------------|------------------------|-------------------------|-----|-------------------|-------------------|-----|-----------------|-----------------|-----------------|---------------------------|------------------------------|------------------------------------|

| MODE                      | DIR/<br>IN <sub>A</sub> | EN/<br>EN <sub>A</sub> | QS/<br>IN <sub>B</sub> | PWM/<br>EN <sub>B</sub> | BRK | IL <sub>A</sub> + | IL <sub>B</sub> + | GTA | GB <sub>A</sub> | GT <sub>B</sub> | GB <sub>B</sub> | CL/<br>FAULT <sub>B</sub> | FAULT/<br>FAULT <sub>A</sub> | Condition                          |

| 0                         | 1                       | 1                      | Х                      | 0                       | Х   | L                 | L                 | Н   | L               | L               | L               | 1                         | 1                            | Normal<br>Operation                |

| 0                         | 0                       | 1                      | Х                      | 0                       | Х   | L                 | L                 | L   | н               | L               | L               | 1                         | 1                            |                                    |

| 0                         | Х                       | 0                      | 1                      | 1                       | Х   | L                 | L                 | L   | L               | н               | L               | 1                         | 1                            |                                    |

| 0                         | Х                       | 0                      | 0                      | 1                       | Х   | L                 | L                 | L   | L               | L               | Н               | 1                         | 1                            |                                    |

| 0                         | х                       | 1                      | Х                      | х                       | х   | Л                 | х                 | L   | L               | Х               | Х               | 1                         | T                            | Over-current<br>on A               |

| 0                         | х                       | х                      | х                      | 1                       | х   | х                 | Л                 | х   | х               | L               | L               | Ţ                         | 1                            | Over-current<br>on B               |

| 0                         | х                       | х                      | х                      | х                       | х   | х                 | х                 | L   | L               | L               | L               | 0                         | 0                            | Undervoltage<br>on V <sub>DD</sub> |

www.vishay.com • FaxBack 408-970-5600 2

| TABLE 3. BOOTSTRAP CAPACITOR<br>SELECTION |                     |                                        |                                                  |  |  |  |  |  |  |

|-------------------------------------------|---------------------|----------------------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Part<br>Number                            | r <sub>DS(on)</sub> | Qg @<br>V <sub>GS</sub> = 10 V<br>(nC) | Minimum<br>Recommended<br>C <sub>BOOT</sub> (μF) |  |  |  |  |  |  |

| Si4946                                    | 0.055               | 30                                     | 0.039                                            |  |  |  |  |  |  |

| Si9956                                    | 0.10                | 7                                      | 0.01                                             |  |  |  |  |  |  |

## **PROTECTION CIRCUITRY**

The protection circuitry provides current limit, crossconduction protection, undervoltage lockout, and the FAULT output.

#### Current Limit

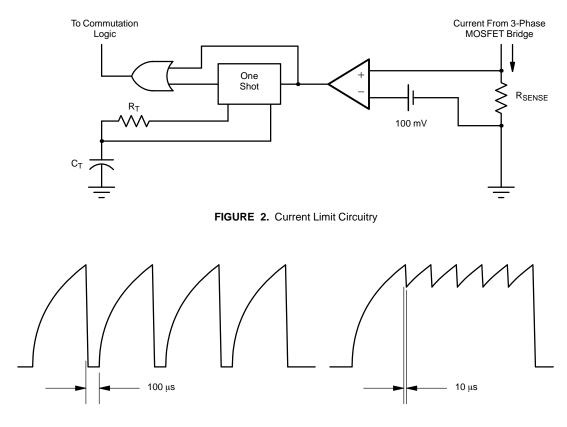

The current limit circuitry consists of two comparators, each driving a one-shot multivibrator (Figure 2). In the full H-bridge mode, comparator A controls the entire H-bridge. In the half-bridge mode, the two comparators function independently with their respective half-bridge. Each comparator has an internal

100-mV reference voltage on the inverting input and an external sensing resistor connected to the non-inverting input. These inputs should be connected directly to the sensing resistor. This will eliminate the effects of any noise in the ground traces.

The motor current must generate 100 mV across a sensing resistor for the comparator to trip. This in turn triggers theone-shot, turning off the active MOSFETs for a period defined by the product of the appropriate R and C.

If the current has dropped below the threshold by the time the off period has expired, the MOSFETs will be turned on again. If the overcurrent condition remains after the off period has expired, the MOSFETs will be held off until the current drops below the threshold.

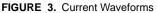

Cycle-by-cycle current limiting is achieved when the current limit off period is in the 100- $\mu$ s range. If the current limit off period is reduced to the 10- $\mu$ s range, a constant current mode current limit is achieved. In this mode, the RMS current (and therefore the torque) is maximized for the current limit setting. This result is particularly useful when a maximum acceleration rate is required at power on. Figure 3 shows typical current waveforms for both durations of the off period.

Document Number: 70574 08-Jun-00

## AN603 Vishay Siliconix

#### **Cross Conduction Protection**

When driven as an anti-phase H-bridge or in the independent half-bridge mode, the high-side and low-side MOSFETs of each active phase are toggled. To prevent shoot-through, each half-bridge has break-before-make circuitry. This delays the MOSFET turn-on for approximately 250 ns from the turn-off of the opposite MOSFET.

#### **Undervoltage Lockout**

Internal circuitry monitors the voltage level on V<sub>DD</sub> and the high-side supplies. This ensures that there is sufficient voltage to turn on the MOSFETs. Should the voltage level on V<sub>DD</sub> drop below 0.75 x V<sub>DD</sub>, all gate drives will be turned off until the undervoltage condition is gone. Each of the high-side supplies is monitored only when it is referenced to ground. If the high-side voltage is under V<sub>DD</sub> - 3.3 V, the high side will not be allowed to turn on.

#### **FAULT** Outputs

The Si9978DW has a pair of FAULT outputs whose exact function changes according to mode of operation. In the H-bridge mode, the FAULT output indicates either an undervoltage or a current limit condition. The CL output indicates when there is a current limit condition. In the half-bridge mode, these outputs become FAULT<sub>A</sub> and FAULT<sub>B</sub>, indicating either an undervoltage or a current limit condition for their respective half-bridge.

These outputs are configured as open drain outputs. The open drain configuration permits connection to wide range of voltages and several FAULT outputs can be wire-OR'd. A negative going transition indicates the undervoltage or current limit condition exists.

### **AN H-BRIDGE CIRCUIT**

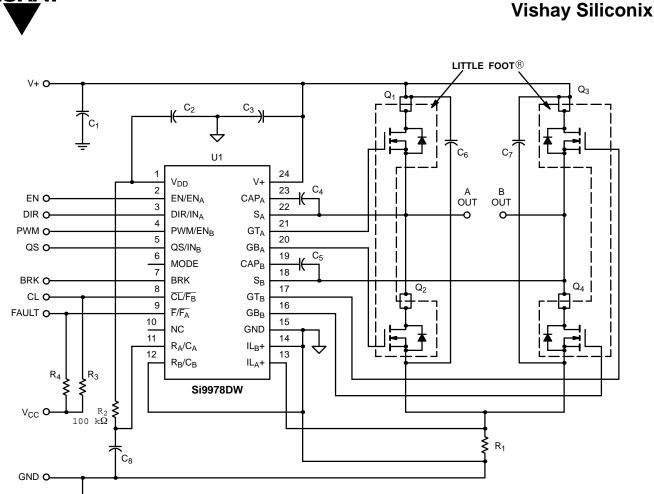

Figure 4 shows a basic H-bridge circuit. This circuit is based on the Si9978DW driving two dual MOSFETs in SO packages (LITTLE FOOT). All that remains is the passive devices required for current limit timing, filtering of the floating high-side supplies, pull-ups for the FAULT outputs, and decoupling of the V+ power supply, the Si9978DW, and the power MOSFETs.

#### The Power MOSFETs

Assuming that the H-bridge has to handle a 2-A load, a 130-m $\Omega$  (@25°C) MOSFET is needed to allow operation at elevated temperature. The Si4946EY exceeds this requirement with on-resistance of 55 m $\Omega$  at 25°C. With the junction at 150°C, the R<sub>DS(on)</sub> will rise to 0.11  $\Omega$ . At a 2-A load, the 0.5-W dissipation is within the Si4946EY's rating and leaves headroom for starting current.

#### The Current Sense Resistor

The current limit level is determined by the motor starting requirements, such as acceleration time, the power capability of the power MOSFETs, and the ability of the system power supply to supply current to the motor. For this design, the current limit level will be set at 3 A peak. There is a simple way to set this level. Select a sensing resistor which will give 100 mV when 3 A flows through it. Using Ohm's law, RS = 100 mV/IPK. Thus a 33-m $\Omega$  resistor is required. A 0.5-W resistor will handle the starting condition. At the load current of 2 A, power dissipation is less than 150 mW.

#### **Current Limit One-Shot Timing**

If the current limit off-time is kept short, acceleration can take place as quickly as possible while respecting the peak starting current of 3 A. The recommended setting is 10  $\mu s$ . Since this off-time is defined by the product of R and C, R is set to 100 k $\Omega$ , making C equal to 100 pF. Since the Si9978DW is connected as a full H-bridge, the comparator driven by IL<sub>A</sub>+ controls the current limit function for the entire H-bridge. R<sub>A</sub> and C<sub>A</sub> are the timing components and therefore assume the values of 100 k $\Omega$  and 100 pF. IL<sub>B</sub>+ and R<sub>B</sub>/C<sub>B</sub> should be connected to ground to ensure that noise does not cause a malfunction.

#### **Bootstrap Capacitor Selection**

The value of the bootstrap capacitor is determined by the gate charge required for the MOSFET selected. The Si4946EY requires 30 nC (Qg) at a V<sub>gs</sub> of 10 V. Using the equation C<sub>BOOT</sub> = 10 (Qg/V<sub>GS</sub>), the typical value is 0.039  $\mu$ F.

#### Decoupling

Decoupling is required for V+, V<sub>DD</sub>, and the power MOSFETs. A 0.1- $\mu$ F capacitor, C3, should be connected to the V+ pin. V<sub>DD</sub> requires a 1- $\mu$ F capacitor, C2. C2 provides the surge current required from V<sub>DD</sub> during low-side MOSFET turn on in addition to stabilizing the V<sub>DD</sub> regulation circuit. Finally, 1- $\mu$ F capacitors should be connected directly across each half-bridge from high-side drain to low-side source. This will minimize or eliminate the ringing seen on the MOSFET gate signals and noise generated by high switching speeds.

#### **PC Board Layout**

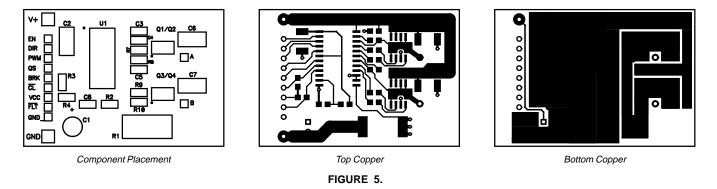

Figure 5 shows the board layout of the basic H-bridge circuit. The board is double sided FR4 and measures 2.05" by 1.38". There are a couple of issues that need to be stressed when designing the PC board.

FIGURE 4. Basic H-Bridge Circuits

**Decoupling Capacitors** - Care must be taken in the placement and connection of the decoupling capacitors. The capacitor should be placed physically close to the device being decoupled. The connections should be direct and as short as possible. When decoupling a pin on an integrated circuit, connect the capacitor directly from the pin being decoupled to the ground pin of the IC. When decoupling a MOSFET half-bridge, connect the capacitor directly from the drain of the high-side MOSFET to the Source of the low-side MOSFET.

**Power and Ground Traces** - The traces carrying the motor current should be kept separate from the power traces of

devices carrying signal level currents. This will minimize noise due to the high level currents drawn by a motor load. Do not use power or ground plane for this purpose. Also, make certain that these traces are made wide enough to minimize the voltage drop created by the motor current.

AN603

*Heat Transfer and* LITTLE FOOT - Surface mount power MOSFETs rely on the PC board to serve as a heat sink. Wide traces should be connected to the Drain pins of the power MOSFETs to draw heat away from their packages and transfer the heat into the PC board. These traces should be at least 0.1" wide.

Document Number: 70574 08-Jun-00

SHA

## CONCLUSION

By separating the controller and the power MOSFETs, the Si9978DW yields a good balance between circuit integration, compact H-bridge size and flexibility in application. The controller functions are highly integrated, leaving only a few external passive components. The integration makes it easy to use n-channel LITTLE FOOT which are electrically, volumetrically, and economically efficient. Also, since they are separate from the controller, the MOSFETs can be matched to the load. The Si9978DW, combined with LITTLE FOOT, gives compact, flexible H-bridge drive circuits for dc motor control.