# Band-pass filter for spectrum analyzer BA3835S / BA3835F

The BA3835S and BA3835F are 5-band, band-pass filter ICs that use microprocessor time division to produce serial output for spectrum analyzer displays. To minimize the number of external components required and enable compact and reliable designs, all of the capacitors for the filters are on the chip.

#### Applications

CD radio cassette players, mini-component stereo systems, car stereos

#### Features

- 1) Five band-pass filter elements for spectrum analyzer displays.

- High-speed readout (output response time : 5μsec. Typ.).

- 3) Discharge time constant circuit for each band is on the chip.

- 4) Differential input amplifier rejects common-mode noise.

- 5) Single 5V power supply.

# ● Absolute maximum ratings (Ta = 25°C)

| Parameter             |         | Symbol | Limits          | Unit |  |

|-----------------------|---------|--------|-----------------|------|--|

| Power supply voltage  |         | Vcc    | 7               | V    |  |

| Power dissipation     | BA3835S | Pd     | 600*1           | mW   |  |

|                       | BA3835F | Pa     | 450*²           |      |  |

| Operating temperature |         | Topr   | <b>−25~</b> +75 | c    |  |

| Storage temperature   |         | Tstg   | <b>−55∼+125</b> | c    |  |

<sup>\*1</sup> Reduced by 6mW for each increase in Ta of 1°C over 25°C.

#### • Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply voltage | Vcc    | 4.5  | 5.0  | 6.5  | V    |

<sup>\*2</sup> Reduced by 4.5mW for each increase in Ta of 1°C over 25°C.

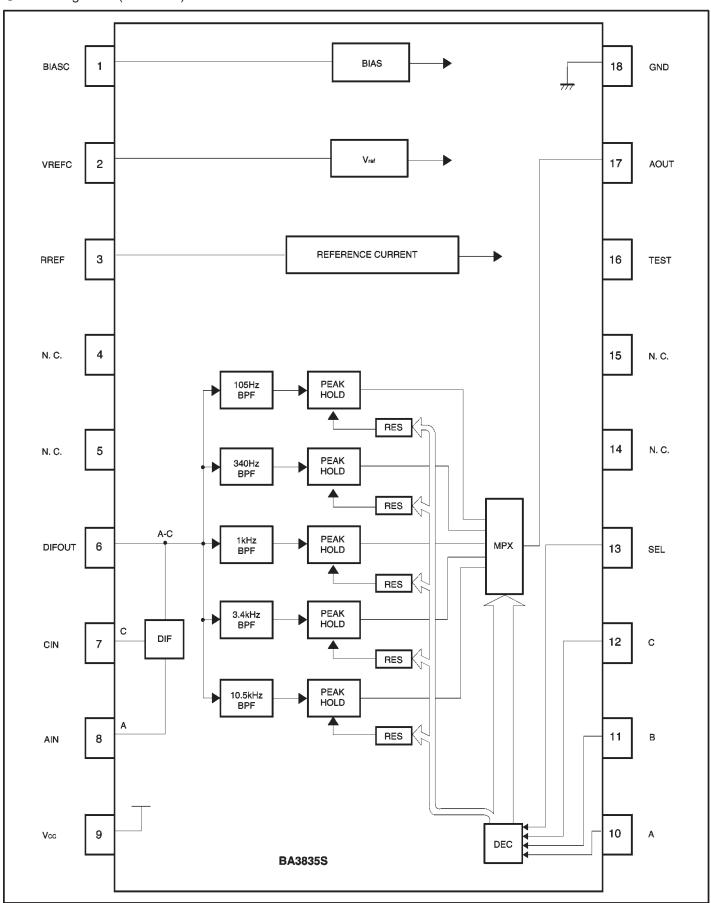

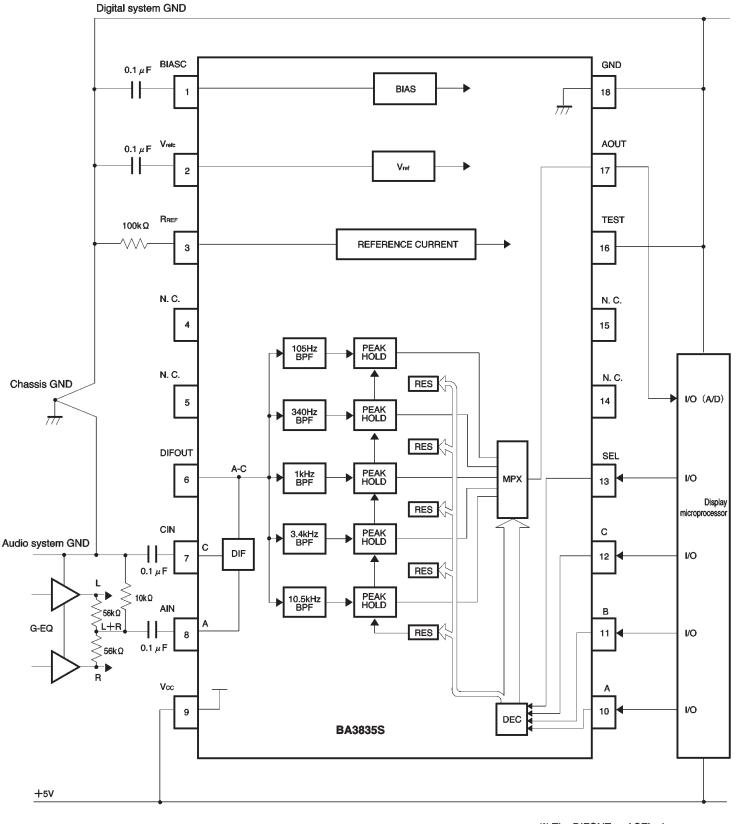

# ●Block diagram 1 (BA3835S)

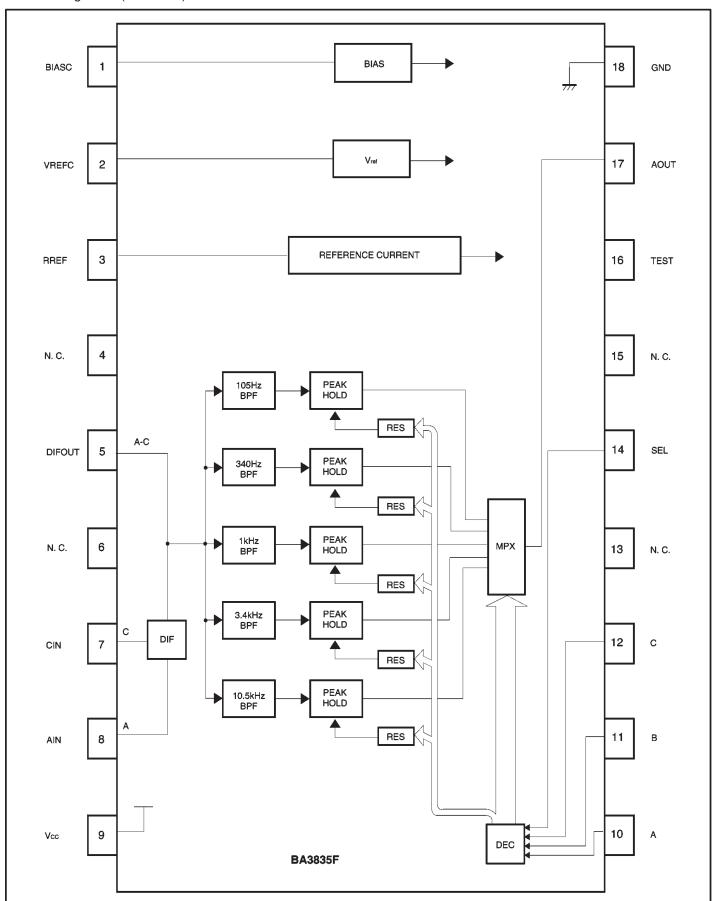

# ●Block diagram 2 (BA3835F)

• Electrical characteristics (unless otherwise noted, Ta = 25 °C,  $V_{CC}$  = 5V,  $R_L$  = 10M $\Omega$ ,  $V_{AIN}$  = - 30dBV and SEL = 1)

| Parameter                   | Symbol          | Min. | Тур. | Мах. | Unit | Conditions                                                                   |

|-----------------------------|-----------------|------|------|------|------|------------------------------------------------------------------------------|

| Circuit current             | lcc             | _    | 8.5  | 13   | mA   | V <sub>AIN</sub> =0V, A, B, C, SEL=0                                         |

| Maximum output level        | Vом             | 4.0  | 4.8  | _    | ٧    | V <sub>AIN</sub> =-14dBV, Measured at each output                            |

| Output offset voltage       | Vos             | _    | 30   | 150  | mV   | V <sub>AIN</sub> =0V, SEL=0/1 Measured at each output (cycle time : Ts=50ms) |

| Standard output level 1     | <b>V</b> 01     | 0.65 | 1.35 | 1.70 | ٧    | f <sub>IN</sub> =105Hz, A=0, B=0, C=1                                        |

| Standard output level 2     | V <sub>02</sub> | 0.65 | 1.35 | 1.70 | ٧    | f <sub>IN</sub> =340Hz, A=0, B=1, C=0                                        |

| Standard output level 3     | V <sub>03</sub> | 0.65 | 1.35 | 1.70 | ٧    | f <sub>IN</sub> =1kHz, A=1, B=0, C=0                                         |

| Standard output level 4     | V <sub>04</sub> | 0.65 | 1.35 | 1.70 | ٧    | f <sub>IN</sub> =3.4kHz, A=1, B=1, C=0                                       |

| Standard output level 5     | V <sub>05</sub> | 0.65 | 1.35 | 1.70 | ٧    | f <sub>IN</sub> =10.5kHz, A=1, B=1, C=1                                      |

| Input impedance             | Rin             | 80   | 100  | 120  | kΩ   | f <sub>IN</sub> =1kHz                                                        |

| Common-mode rejection ratio | CMRR            | 25   | 50   | _    | dB   | f <sub>IN</sub> =1kHz, V <sub>AIN</sub> =V <sub>CIN</sub>                    |

| Logic input high level      | ViH             | 2.5  | 5.0  | _    | ٧    |                                                                              |

| Logic input low level       | VIL             | _    | 0    | 0.5  | ٧    | Not applicable in the when item 3 of the operation notes applies.            |

| Output response time*1      | То              | _    | 5    | 10   | μS   |                                                                              |

| Discharge level             | DL              | _    | 3    | _    | dB   | Reset pulse width T <sub>R</sub> = 10 $\mu$ s (Typ.) *2                      |

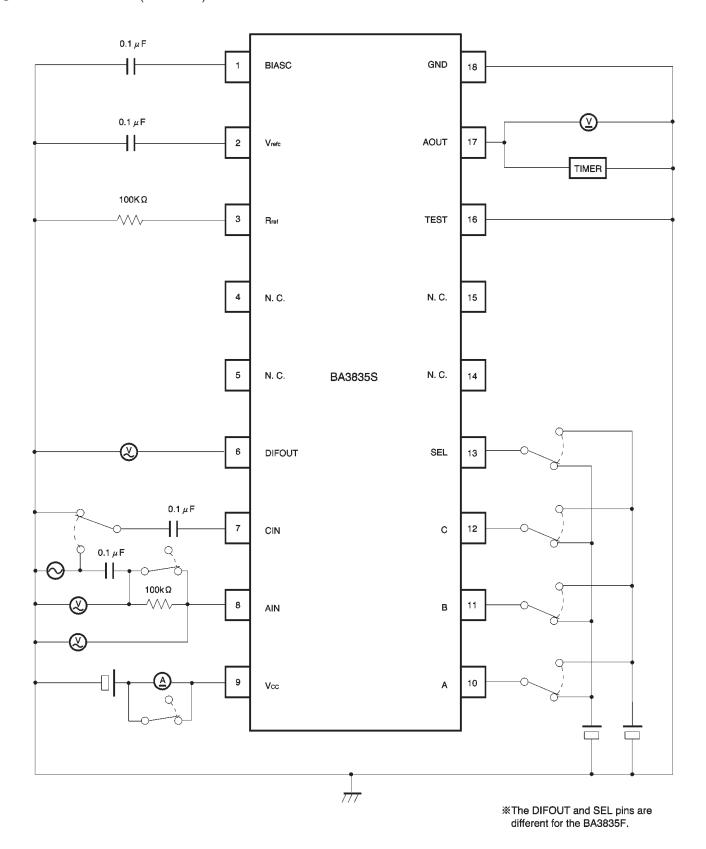

The measurement circuit is given in Fig. 1.

<sup>\*1</sup> The time from the rise of A, B, C or SEL until the rise of AOUT (90% of peak). If the output selection time is less than this, the output value is not guaranteed and the reset pulse is not generated.

<sup>\*2</sup> Automatically generated internally based on the output select signal. For the duration that this signal is "H", a resistor is connected to the peak hold capacitor, and the output level drops by -3dB (typ.) for one pulse.

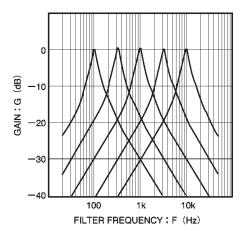

<sup>\*3</sup> The Q of the bandpass filter is 3.5.

O Not designed for radiation resistance.

# ■Measurement circuit (BA3835S)

Fig. 1

# Output select logic table

| SEL | Α | В | С | AOUT    |

|-----|---|---|---|---------|

| 0   | × | × | × | GND     |

| 1   | 0 | 0 | 0 | GND     |

| 1   | 0 | 0 | 1 | 105Hz   |

| 1   | 0 | 1 | 0 | 340Hz   |

| 1   | 0 | 1 | 1 | GND     |

| 1   | 1 | 0 | 0 | 1kHz    |

| 1   | 1 | 0 | 1 | GND     |

| 1   | 1 | 1 | 0 | 3.4kHz  |

| 1   | 1 | 1 | 1 | 10.5kHz |

<sup>\*</sup> X: Don't Care.

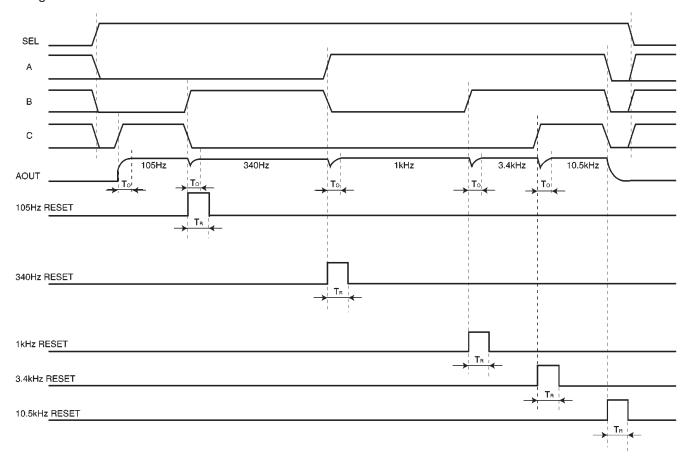

# Timing chart

Fig. 2

# Application example (BA3835S)

Fig. 3

\* The DIFOUT and SEL pins are different for the BA3835F.

#### Operation notes

# (1) Frequency characteristics

The frequency characteristics of this IC are determined by the resistor connected between the R<sub>REF</sub> terminal and GND. For the specification conditions, the value of this resistor is  $100k\Omega$ . If it is necessary to set the frequency characteristics accurately, use a variable resistor (note: all bands will shift together).

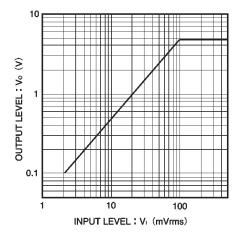

#### (2) Load characteristics

To convert the bias sense output signal to the GND sense signal, the IC performs a V / I conversion, and then an I / V conversion using a  $10k\Omega$  resistor (typ.) for the output.

Therefore, if the load circuit connected to the A OUT pin has a MOS structure there is no problem (eg. microprocessor input port), but if the connected circuit has a low input impedance, it may cause the output level to drop.

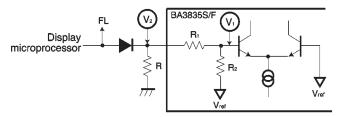

# (3) External resistor for the control pin

When using a common port for the output select control and FL drive, you must add a diode and resistor as shown in Fig. 4 to prevent the FL drive "L" voltage from destroying the IC.

Fig. 4

In this case, the "L" voltage applied to the internal comparator input terminal  $V_1$  is given by :

$$V_1 = \frac{R_1 + R}{R_1 + R_2 + R} \times Vref$$

To maintain a noise margin of at least 2.5V with respect to the comparator threshold level  $V_{ref}$ , the representative values for  $V_{ref}$ ,  $R_1$  and  $R_2$  are 1.5V,  $20k\Omega$ , and  $10k\Omega$  respectively. This gives :

$$\frac{20k\Omega + R}{20k\Omega + 10k\Omega + R} \times 1.5V + 0.25V < 1.5V$$

And from this, the following condition is obtained:

$$R < 30k\Omega$$

In this case, the "L" level voltage V<sub>2</sub> for the IC will be:

$$V_2 < 0.75V$$

# (4) Recommended operating ranges

Provided that the IC is operated within the recommended operating conditions and the recommended temperature range, the basic circuit functions are guaranteed. Within these ranges, ratings for electrical characteristics for conditions other than those stipulated cannot be guaranteed, but the inherent function of the bandpass filter will be maintained.

# (5) Application circuit

Provided the recommended circuit constants are used, the application circuit should function correctly. However, we recommend that you confirm the characteristics of the circuits in actual use and pay due attention to the cautionary notes given below.

If you change the circuit constants, check both the static and transient characteristics of the circuit, and allow sufficient margin to accommodate variations between both ICs and external components. Note, also, that Rohm has not been able to conduct a sufficient study into patent rights.

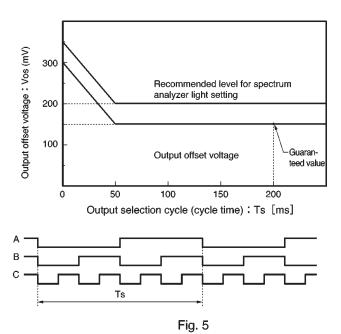

### (6) Output offset voltage

The relationship between the output offset voltage and the output selection cycle (cycle time) for this IC is shown in Fig.5. The maximum output offset voltage of 150mV that is given in the electrical characteristics table is under the condition that Ts = 200ms. When Ts is greater than 50ms, the graph of the output offset voltage is a straight line at 150mV. When Ts is below 50ms, due to transient characteristics of the peak hold circuit, the graph is a line sloping downwards to the right. In other words, the shorter the cycle, the larger the output offset voltage.

Furthermore, the output offset voltage may shift due to soldering or other temperature stresses from the surroundings. Therefore, when setting the spectral analyzer light level, take into consideration the points given above and make sure that it does not light by mistake during quiescent periods. Use the chart below as a guide for this, and, if necessary, leave even a larger margin.

#### Electrical characteristics curves

Fig. 6 BPF frequency characteristics

Fig. 7 Input level vs. output level

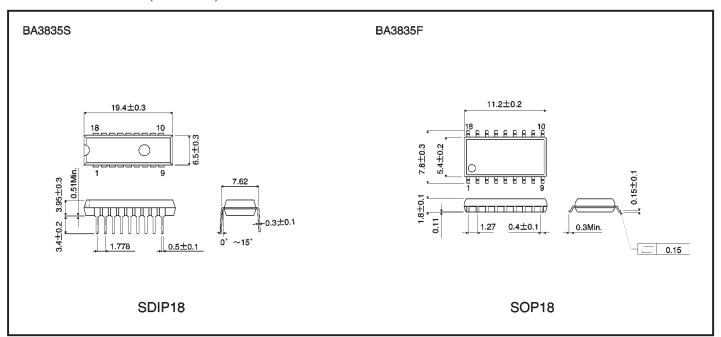

# External dimensions (Units: mm)