# Electronic viewfinder driver BA7149F

The BA7149F is an electronic viewfinder driver for video cameras. It separates the synchronous signal from the input video signal, and outputs the vertical deflection drive output and horizontal deflection signals. HD and VD output signals with guaranteed phase difference are also provided for on-screen displays (OSD). The differences between the BA7149F and the BA7148F are the horizontal blanking, horizontal AFC output, HD output phase and pulse width.

### Applications

Video cameras

### Features

- 1) Operates off a 5V power supply.

- 2) Built-in vertical deflection circuit.

- 3) Built-in wide-bandwidth amplifier.

- 4) Built-in HD and VD output terminals.

- 5) Few attached components required.

- 6) SOP 16pin package.

- 7) Compatible with 10µ sec flyback pulses.

### ● Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol   | Limits              | Unit |

|-----------------------|----------|---------------------|------|

| Applied voltage       | VCC Max. | 8.0                 | V    |

| Power dissipation     | Pd       | 500*                | mW   |

| Operating temperature | Topr     | - 20 ~ <b>+</b> 75  | °C   |

| Storage temperature   | Tstg     | - 55 ~ <b>+</b> 125 | °C   |

<sup>\*</sup> Reduced by 5mW for each increase in Ta of 1°C over 25°C.

### ●Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply voltage | Vcc    | 4.5  | 5.0  | 5.5  | V    |

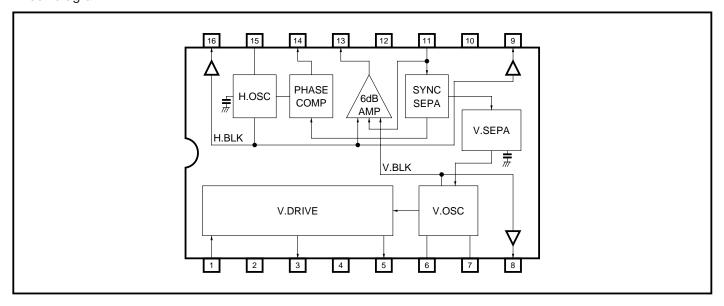

# ●Block diagram

# ●Pin descriptions

| Pin No. | Function                               | Pin No. | Function                                |

|---------|----------------------------------------|---------|-----------------------------------------|

| 1       | Vertical control input                 | 9       | HD output                               |

| 2       | Power supply 1                         | 10      | GND 2                                   |

| 3       | Vertical deflection drive (POS)        | 11      | Video input                             |

| 4       | GND 1                                  | 12      | Power supply 2                          |

| 5       | Vertical deflection drive (NEG)        | 13      | Video output                            |

| 6       | Vertical oscillator external resistor  | 14      | Phase comparator output                 |

| 7       | Vertical oscillator external capacitor | 15      | Horizontal oscillator external resistor |

| 8       | VD output                              | 16      | Horizontal AFC output                   |

# ●Electrical characteristics (unless otherwise noted, Ta = 25°C and Vcc = 5.0V)

| Parameter                       | Symbol              | Min.  | Тур.  | Max.  | Unit              |  |

|---------------------------------|---------------------|-------|-------|-------|-------------------|--|

| Operating current dissipation   | Icc                 | 31.0  | 42.0  | 55.0  | mA                |  |

| ⟨VIDEO AMP⟩                     |                     |       |       |       |                   |  |

| Voltage gain                    | G∨                  | 5.3   | 6.0   | 6.7   | dB                |  |

| D range                         | Drv                 | 3.20  | 3.50  |       | V <sub>P-P</sub>  |  |

| Frequency characteristic        | fc                  | - 2.0 | 0.0   | + 2.0 | dB                |  |

| Minimum sync separation voltage | Vsyn · Min.         | _     | 45    | 120   | mV <sub>P-P</sub> |  |

| Horizontal blanking width       | T <sub>H</sub> ·BL  | 9.6   | 10.7  | 11.4  | μs                |  |

| Vertical blanking width         | T∨⋅BL               | 870   | 970   | 1070  | μs                |  |

| (Horizontal)                    |                     |       |       |       |                   |  |

| Free-running frequency          | <b>f</b> H ⋅ O      | 13.9  | 15.7  | 17.5  | kHz               |  |

| Capture range                   | $\Delta f$ CAP      | ± 2.1 | ± 3.0 | _     | kHz               |  |

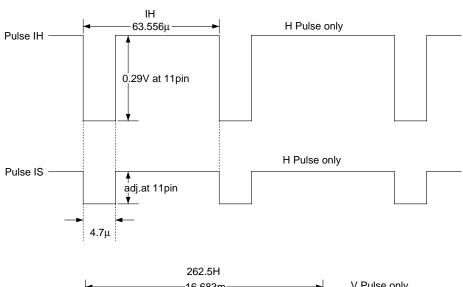

| AFC output pulse width          | Тнр                 | 10.2  | 11.1  | 12.0  | μs                |  |

| AFC lock-in phase               | Тнрн                | - 1.9 | - 1.2 | - 0.5 | μs                |  |

| Pulse voltage low               | VHPL                | 0.5   | 1.1   | 1.7   | V                 |  |

| ⟨Vertical⟩                      |                     |       |       |       |                   |  |

| Free-running frequency          | fv∙o                | 51.3  | 54.8  | 58.2  | Hz                |  |

| Pin 3 maximum output amplitude  | VvP · Max.          | 2.10  | 2.70  | _     | V <sub>P-P</sub>  |  |

| Pin 5 maximum output amplitude  | Vvn · Max.          | 2.10  | 2.70  | _     | V <sub>P-P</sub>  |  |

| $\langle H_D \cdot V_D \rangle$ |                     |       |       |       |                   |  |

| Phase difference                | THVD                | 17.3  | 21.3  | 25.3  | μs                |  |

| H <sub>D</sub> pulse width      | Тно                 | 8.7   | 9.9   | 11.1  | μs                |  |

| V pulse width                   | Tvd                 | 860   | 960   | 1060  | μs                |  |

| Pulse voltage low               | V <sub>HV</sub> · L |       | 0.1   | 0.3   | V                 |  |

| Pulse voltage high              | V <sub>HV</sub> ·H  | 4.7   | 4.9   | _     | V                 |  |

$<sup>\</sup>bigcirc \mbox{Not designed for radiation resistance}.$

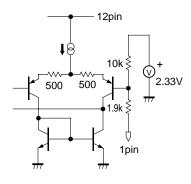

## ●Input / output circuits

1pin

Fig.1

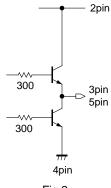

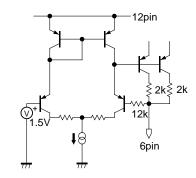

2, 3, 4, 5pin

Fig.2

6pin

Fig.3

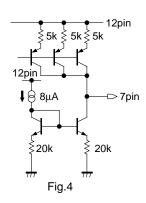

7pin

8pin

Fig.5

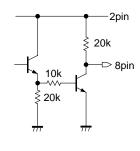

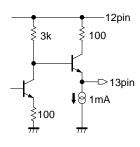

9pin

Fig.6

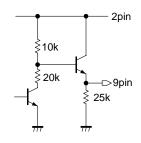

13pin

Fig.7

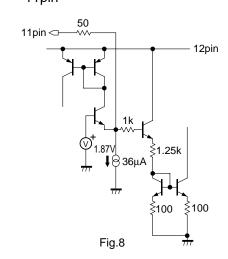

11pin

14pin

Fig.9

Video ICs BA7149F

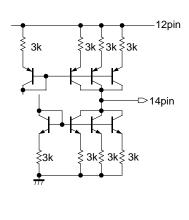

15pin

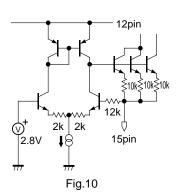

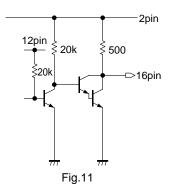

### 16pin

Circuit operationInput signals

Fig.12

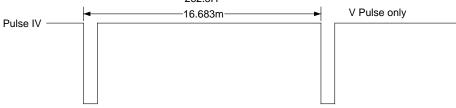

The video signal input to pin 11 is detected by the charging and discharging of an external capacitor. Sync separation is done in the SYNC SEPA block. The H. SYNC signal is sent to the H. OSC, and the V. SYNC signal is sync-separated in the vertical sync pulse interval and supplied to the V. OSC block.

The H. OSC block consists of a PLL that oscillates in sync with the sync-separated H. SYNC signal, and outputs the HD pulse and horizontal deflection pulse.

In the V. OSC block, a direct-control method is used with the sync signal. To synchronize the vertical oscillator circuit, the inherent oscillation period of the oscillation circuit is made slightly larger than the vertical sync signal period, so that the sync signal always enters slightly early.

The oscillator output alone is not enough to ensure stable operation for the vertical deflection output circuit, so it is amplified by the V. DRIVE block.

The horizontal and vertical blanking signals generated in the H. OSC and V. OSC blocks are used to erase the horizontal retrace line from the video signal input to pin 11.

The signal is inverted and amplified by a 6dB inverting amplifier and output as a negative-polarity video signal.

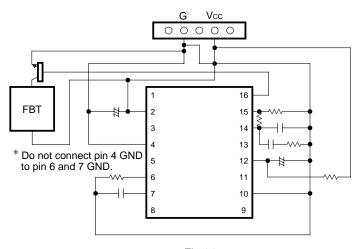

### Application example

- \*1 The resistors connected to pins 6 and 15 should have a tolerance of  $\pm$  2%, and a temperature coefficient of  $\pm$  100ppm or lower.

- \*2 The capacitor connected to pin7 should have a tolerance of  $\pm$  5%, and a temperature coefficient of  $\pm$  250ppm or lower.

### Operation notes

### (1) H.OSC free-run frequency and capture range

The free-run frequency is determined by the  $115k\Omega$  resistor connected between pin 15 and GND. The capture range is varied by the resistors and capacitor connected to pins 14 and 15.

The free-run frequency and capture range for this IC are guaranteed for these circuit constant values, and we recommend that you use them. The resistor  $115k\Omega$  connected between pin15 and GND should have a tolerance of  $\pm$  2%, and a temperature coefficient of  $\pm$  100ppm or lower.

### (2) V.OSC free-run frequency

The V.OSC free-run frequency is determined by the  $15k\Omega$  resistor connected between pin 6 and GND, and the  $0.1\mu F$  capacitor connected between pin 7 and GND.

The free-run frequency and capture range for this IC are guaranteed for these circuit constant values, and we recommend that you use them. The resistor  $15k\Omega$  connected between pin 6 and GND should have a tolerance of  $\pm$  2%, and a temperature coefficient of  $\pm$  100ppm or lower, and the capacitor connected between pin 7 and GND should have a tolerance of  $\pm$  5%, and a temperature coefficient of  $\pm$  250ppm or lower.

# (3) Use with PAL systems

In PAL systems, change the value of the resistor connected between pin 6 and GND to  $18k\Omega$ .

### (4) PCB pattern

The large-signal systems and small-signal systems in the IC have been kept separate, and the external wring must also be done in such a way to prevent interference from occurring. In particular, to prevent the FBT return current from interfering with the V. OSC circuit on pins 6 and 7, do not directly connect the pin 4 GND and pin 6 and 7 GND.

Fig.14

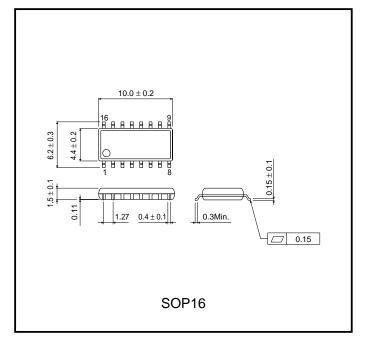

### External dimensions (Units: mm)