ISO-CMOS ST-BUS™ FAMILY MT8950 Data Codec

## Features

- Transparent coding and decoding of 0 to 8, 9.6 and 19.2 kbps data

- Coding compatible to PCM voice channels at 56/64 kbps in ST-BUS format

- Automatic line polarity detection and correction

- Loopback facility for test purposes

- Selectable data formats: RZ or NRZ

- Eight user selectable modes of operation

- Low power ISO-CMOS technology

# Applications

- Transparent coder/decoder for synchronous and asynchronous data

- Data terminal (RS-232C, etc.) to ST-BUS interface

- Data switching on digital PBXs

- Channel banks/TDM multiplexers

November 1990

ISSUE 4 Ordering Information

MT8950AC 24 Pin Ceramic DIP

0°C to 70°C

## Description

The MT8950 is a coder/decoder which uses the Transition Encoded Modulation (TEM) technique for encoding/decoding low speed data to and from a 56/ 64 kbps channel (equivalent to PCM Voice). The coding and decoding scheme is transparent and can accept either synchronous or asynchronous data up to 8 kbps (inclusive); at 9.6 kbps and 19.2 kbps.

The MT8950 is fabricated in MITEL's ISO-CMOS technology.

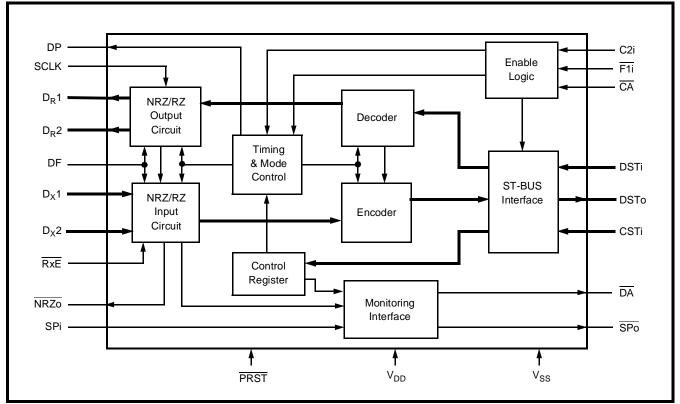

Figure 1 - Functional Block Diagram

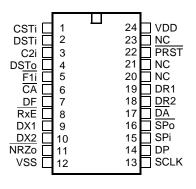

# **Pin Description**

| Pin # | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CSTi             | <b>Control ST-BUS In (TTL Input) -</b> This ST-BUS interface pin accepts a serial input stream which loads the Control Register. The mode of operation <u>of</u> the device, the bits in the Violation word, and, the resetting of Data Activity (DA) and Scan Point output (SPo) are controlled by this register. The contents of the register are updated once every ST-BUS frame when the interface is enabled.                                                                                                                                                                                           |

| 2     | DSTi             | Data ST-BUS In (TTL Input) - Accepts the 8 bits of TEM Data when the ST-BUS interface is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3     | C2i              | 2.048 MHz Clock (TTL Input) - This is the input for the 2.048 MHz clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4     | DSTo             | <b>ST-BUS Output (Three-State Output) -</b> This is the 2.048 Mbps serial output for theTEM encoded word. It is enabled when both F1i and CA are low.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5     | F1i              | <b>Framing Type 1 Input (TTL Input) -</b> This active low input, in conjunction with $\overline{CA}$ , enables the ST-BUS interface (DSTi, DSTo and CSTi). It is internally sampled on every positive edge of the C2i clock and provides frame synchronization.                                                                                                                                                                                                                                                                                                                                              |

| 6     | CA               | <b>Control Address (TTL Input) -</b> This active low input (in conjunction with $\overline{F1i}$ ) enables the ST-BUS interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7     | DF               | <b>Data Format Select (CMOS Input) -</b> When HIGH, the Data Codec accepts and delivers the data in unipolar Return to Zero (RZ) format. When LOW, the data format is unipolar NRZ.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8     | RxE              | <b>Received Energy Signal (Schmitt Input) -</b> When $\overline{\text{RxE}}$ goes LOW it establishes the polarity of the input pins $D_X1$ and $D_X2$ in the RZ mode. The input which received the last pulse before $\overline{\text{RxE}}$ goes LOW is established as the unipolar MARK input. $\overline{\text{RxE}}$ also enables the operation of DA and SPo outputs the loopback modes (Modes 4, 5 and 6) of the codec, $\overline{\text{RxE}}$ is forced to the LOW state internally independent of the pin condition. $\overline{\text{RxE}}$ should be exerted LOW for the duration of a data call. |

| 9     | D <sub>X</sub> 1 | <b>Data Transmit 1 (Schmitt Input) -</b> If DF= LOW, accepts data in the NRZ format.<br>(HIGH = MARK, LOW = SPACE).<br>If DF=HIGH, accepts active low unipolar pulses representing the digital data in the RZ format. MARK or SPACE polarity is established by the RxE input.                                                                                                                                                                                                                                                                                                                                |

# Pin Description (continued)

| Pin # | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10    | D <sub>X</sub> 2 | <b>Data Transmit 2 (Schmitt Input)</b> - If DF = LOW, accepts data pulses which are encoded only if there is no activity on the $D_X1$ pin - the data format and restrictions on the use of this input is explained in the text.<br>If DF= HIGH, accepts active low unipolar pulses representing the digital data in the RZ format. MARK or SPACE polarity is established by the RxE input. |

| 11    | NRZo             | <b>Non-Return to Zero Output (Open Drain Output) -</b> The incoming data, in the RZ format or the NRZ format, is internally converted to inverted NRZ and appears on this open drain output. This output in conjunction with the SPi input can be used for long space detection.                                                                                                            |

| 12    | V <sub>SS</sub>  | Ground (0 Volt).                                                                                                                                                                                                                                                                                                                                                                            |

| 13    | SCLK             | <b>Secondary Clock (TTL Input) -</b> This is an external clock input that determines the timing of the Violation Word and the synchronization pulses. If these features are not to be utilized, this input can be tied to $V_{SS}$ .                                                                                                                                                        |

| 14    | DP               | <b>Drive Point Output (Totem-pole Output) -</b> This output is exerted high when the Control Register bits b7, b6 and b5 are set to 110 (decimal 6). The operation of the Codec is normal in every other respect.                                                                                                                                                                           |

| 15    | SPi              | <b>Uncommitted Scan Point Input</b> (Voltage Comparator Input) - A LOW to HIGH transition on this input causes SPo to be set LOW. This is used to detect a long SPACE condition in conjunction with NRZo (pin 11).                                                                                                                                                                          |

| 16    | SPo              | <b>Uncommitted Scan Point Output (Totem-pole Output ) -</b> This output is set LOW when the SPi input undergoes a LOW to HIGH transition. The SPo is reset by the presence of a logic "1" in bit b0 of Control Register. This function is active at all times except when RxE is false and during power reset conditions.                                                                   |

| 17    | DA               | <b>Data Activity (Totem-pole Output )</b> - The NRZ/RZ input circuitry monitors the input signal (after polarity is established) and activates this output when it detects a SPACE on the input. This output is reset by the presence of a logic "1" in bit 1 of the Control Register. The DA function is active at all times except when RxE is false and during power reset conditions.   |

| 18    | D <sub>R</sub> 2 | <b>Data Receive 2 (Totem-pole Output) -</b> If DF = LOW (NRZ format), outputs the secondary data signal in the NRZ form as explained in the text.<br>If DF = HIGH (RZ format), outputs unipolar, active high MARK pulses.                                                                                                                                                                   |

| 19    | D <sub>R</sub> 1 | <b>Data Receive 1 (Totem-pole Output)</b> - If DF = LOW (NRZ format) , outputs the NRZ data signal. (HIGH = MARK, LOW = SPACE)<br>If DF = HIGH (RZ format), outputs unipolar, active low SPACE pulses.                                                                                                                                                                                      |

| 20    | NC               | No connection.                                                                                                                                                                                                                                                                                                                                                                              |

| 21    | NC               | No connection.                                                                                                                                                                                                                                                                                                                                                                              |

| 22    | PRST             | <b>Power Reset (CMOS Schmitt Input ) -</b> A LOW level on this input evokes the power reset condition for the codec.                                                                                                                                                                                                                                                                        |

| 23    | NC               | No connection.                                                                                                                                                                                                                                                                                                                                                                              |

| 24    | V <sub>DD</sub>  | Positive Supply Voltage +5 volts ± 10% .                                                                                                                                                                                                                                                                                                                                                    |

# Theory of Operation

The MT8950 is an encoder/decoder which operates on low baud rate data (up to 19.2 kbps) to convert it to the ST-BUS format. The data can subsequently be transparently switched or transmitted in a manner identical to PCM encoded voice. In this respect, the functional characteristics of the device are very similar to many industry standard voice codecs. Asynchronous and synchronous data from 0 to 8 kbps and at 9.6 kbps is accepted by the codec without any restrictions. Asynchronous data at 19.2 kbps should have at least two stop bits for the device to encode it properly. The data is encoded by the Codec into an eight bit word which occupies one 64 kbps channel on the ST-BUS. Conversely, it accepts an encoded 8 bit word from an incoming ST-BUS stream and regenerates the original digital signal. Mitel's ST-BUS is a synchronous time division multiplexed serial stream with a bit rate of 2048 kbps. In a telecommunications environment, it is generally divided into 32 channels made up of 8 bits each, with an effective bandwidth of 64 kbps per channel. These channels may carry data or PCM encoded voice.

#### Low Speed Data Format

The Data Codec can accept low speed data in either Non Return to Zero (NRZ) or Return to Zero (RZ) format. The NRZ format requires only one line to carry the data. This format is suitable for interfacing the data codec with RS-232 type terminals and microprocessor peripherals such as UARTS, ACIAs, etc. All signals have to be converted to TTL voltage levels before being input to the codec.

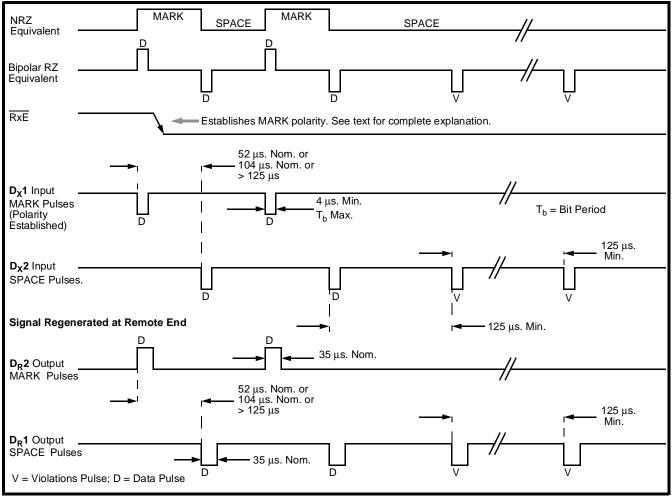

The RZ format requires two separate lines to represent the MARKs and SPACEs in the data as illustrated in Figure 4. This format is useful when the data terminal is located some distance from the codec and the data is to be transmitted over a line as a three level signal (a positive pulse for the beginning of MARKs, negative pulse for the beginning of SPACEs and zero level for no change in the signal). The three level signal is converted to its TTL-Compatible binary form as shown in Figure 4 before being applied to the codec. A pulse appears on one line of the input indicating the beginning of MARKs. This is followed by a pulse on the second line indicating the beginning of SPACEs. If two or more pulses appear consecutively on the same line before the second line of the pair receives or transmits another pulse, then these pulses can be considered to be violating the normal rule of the RZ format and are called "Violation Pulses". The data codec will accept these violations with the restriction that the time difference between a violation pulse

| Data Rate<br>Bits/Sec                 | 0 - 8000 | 9600 | 19200                  |

|---------------------------------------|----------|------|------------------------|

| Asynchronous<br>Restrictions          | None     | None | Minimum<br>2 Stop Bits |

| Synchronous<br>Restrictions           | None     | None | None                   |

| Percentage<br>Distortion <sup>†</sup> | ±3.2     | ±3.8 | ±7.5                   |

Table 1. Summary of Data Codec Capabilities.

† Refers to the maximum distortion in the bit period timing of the regenerated data. (Channel Bandwidth = 64kbps )

Percentage Distortion =  $|T_{BO} - T_{BR}| / T_{BO} \times 100$

where  $T_{BO}$  = Original Data Bit Period  $T_{BR}$  = Regenerated Data Bit Period

and an actual data transition be at least 125µs. The violation pulses can be on the MARK or SPACE line. In a communications system, these violations can be used to carry other information when no data is being transmitted.

#### **Encoding/Decoding Scheme**

The Data Codec uses a Transition Encoded Modulation (TEM) technique to encode low speed data onto a 56 or 64 kbps equivalent PCM voice channel. This coding algorithm significantly reduces data bit distortion. The timing distortion in the regenerated data is summarized in Table 1. A simple sampling method for encoding the data would require a 256 kbps channel to obtain the same low distortion figures.

If the encoded information is to be transmitted over digital T1/DS1 trunks, the maximum percentage distortion in the regenerated data is effectively doubled. This is due to the fact that the least significant bit in specific channels on these trunks is used to transmit signalling information. Thus the bandwidth per channel is reduced to 56 kbps.

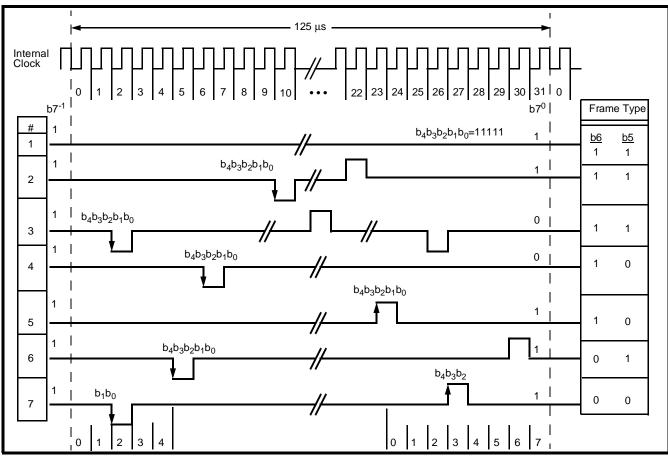

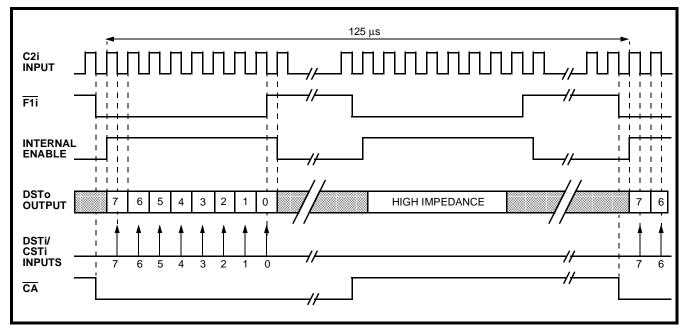

The encoder stage of the Data Codec observes data transitions in discrete timing windows which are 125 $\mu$ s wide. These timing frames are further divided into 32 timeslots of 3.906 $\mu$ s duration each (see Figure 3). The position of the first data transition, the total number of transitions, and, the time period between the transitions in this 125 $\mu$ s frame is encoded as an 8 bit word.

The first five bits (b0 to b4) indicate the position of the first data transition with respect to the 32 timeslots in the window. Bit 7 in the encoded word represents the absolute value of the data in the 31st timeslot. Bits 5 and 6 in conjunction with bit 7 are used to identify the total number of transitions and the time period between the transitions. Due to the fixed bit rate restrictions above 8 kbps, a maximum

# ISO-CMOS MT8950

#### Figure 3 - TEM Coding Scheme

(Note: Waveforms shown are bipolar RZ equivalent of separate RZ/NRZ inputs)

| # | Frame<br>Description                           | Level <sup>†</sup><br>b7 | Frame Type<br>b6 b5 | First Transition<br>b4 b3 b2 b1 b0 | Notes                       |

|---|------------------------------------------------|--------------------------|---------------------|------------------------------------|-----------------------------|

| 1 | No Pulse                                       | 1/0                      | 1 1                 | 1 1 1 1 1                          |                             |

| 2 | 2 Data Pulses (T=52 µs)                        | 1/0                      | 1 1                 | x x x x x                          | X X X X X ≤ 10001 (17)      |

| 3 | 3 Data Pulses (T=52 µs)                        | 1/0                      | 1 1                 | x x x x x x                        | X X X X X ≤ 00100 (4)       |

| 4 | 1 Data Pulse                                   | 1/0                      | 1 0                 | x x x x x                          | X X X X X = 0 to 31         |

| 5 | Violation Pulse                                | 1/0                      | 1 0                 | x x x x x                          | X X X X X = 0 to 31         |

| 6 | 2 Data Pulses (T=104 µs)<br>(Timeslot 4 to 31) | 1/0                      | 0 1                 | x x x x x                          | X X X X X > 00011 (3)       |

| 7 | 2 Data Pulses (T=104 µs)<br>(Timeslot 0 to 3)  | 1/0                      | 0 0                 | ΥΥΥΧΧ                              | XX = 0 to 3<br>YYY = 0 to 7 |

#### Table 2. TEM Coding Summary

† Note: The Level bit (b7) indicates the level (HIGH or LOW) of the input data in timeslot 31 of the current frame.

of seven frames types are possible as shown in Figure 3. In frame type 7, the first five bits (b0 to b4) are used to represent two transitions instead of the normal first transition. Note that the data transitions in Figure 3 are shown as a three level signal. A positive transition indicates the beginning of one or more continuous MARKs and a negative transition indicates the beginning of one or more continuous SPACEs. The decoder stage regenerates the original data from the 8 bit TEM word. The absolute values of the data signal in the present and previous frames as given by b7(n) and b7(n-1) are EX-ORed and the result in combination with the remaining bits of the TEM word is used to reproduce the original data with an accuracy of  $\pm 3.906\mu$ s (see Table 2). Due to the data speed restriction above 8 kbps, the second and third transitions (if any) will be reproduced at intervals which are multiples of 52µs (depending upon the input data baud rate).

# **Functional Description**

The functional block diagram of the data codec is shown in Figure 1. The low speed data to be encoded is accepted by the NRZ/RZ input circuitry and relayed to the encoder. The 8 bit encoded word is transmitted within one channel time period on to the ST-BUS serial output stream. At the same time an 8 bit TEM word is loaded into the decoder via the incoming ST-BUS stream. The low speed data is regenerated and output by the NRZ/RZ output circuitry. The data codec can operate in eight modes. The specific mode of operation is selected by programming the internal Control Register using the CSTi serial input.

#### Transmit Path

The NRZ/RZ input circuitry can be programmed to accept RZ or NRZ data by asserting the appropriate level on the DF pin (HIGH=RZ format; LOW=NRZ format).

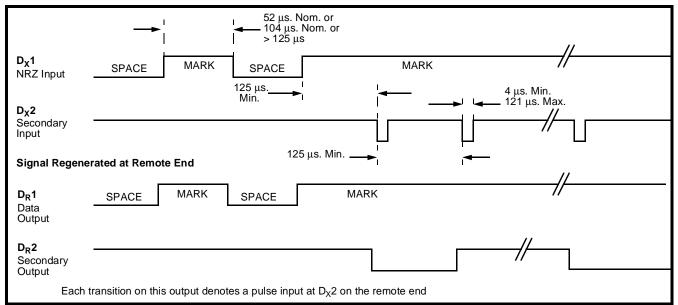

In the RZ format, both  $D_X1$  and  $D_X2$  are used for the input data. MARK pulses are received on one line input and SPACE pulses on the other. The MARK and SPACE polarities of the input pins are fixed by the high to low transition of the  $Rx\overline{E}$  line. The input having the last transition before RxE goes low is selected to be the MARK input. Thus to ensure correct polarity selection, the data codec should be receiving MARK pulses before RxE is taken low. The RxE line must be kept low for the duration of the call. As indicated before, the Data Codec does accept violation pulses. The violation pulses can be input on the MARK or SPACE lines. The time difference between a violation pulse and an actual data pulse must be at least 125µs. Since only one violation pulse is encoded per frame, the minimum time period between consecutive pulses should be 125µs as illustrated in Figure 4.

In the NRZ format, only one line is required for the data. This is input at  $D_X 1$  (Pin 9). The second input,  $D_X 2$ , can be used for transmitting secondary control information. The signal on this input pin is encoded only when there is no activity on the  $D_X 1$  line, i.e., during steady MARK or SPACE condition on the data line. To ensure proper encoder function, the signal to the  $D_X 2$  line should be applied after at least 125µs have elapsed since the last data transition on  $D_X 1$ . The acceptable data format for the  $D_X 2$  input is illustrated in Figure 5. Each pulse on the line is

encoded as a single transition. The minimum time period between consecutive pulses should be 125µs.

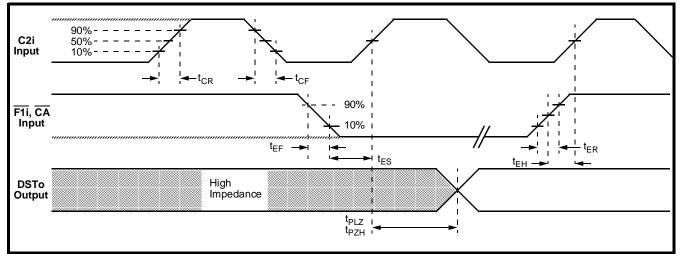

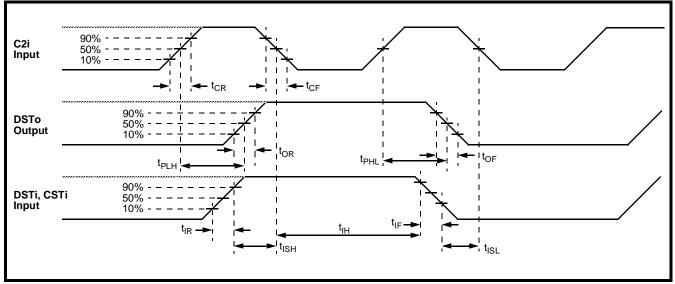

The encoding of the NRZ/RZ data to the TEM format is performed by the encoder. The 8 bit TEM words are transmitted on the outgoing ST-BUS channel via DSTo. This is a three state output which is enabled only when both  $\overrightarrow{CA}$  and  $\overrightarrow{F1i}$  are low (see Figure 11).

#### **Receive Path**

The 8 bit word generated by a data codec at a remote end is shifted in from the incoming ST-BUS stream via the DSTi input. The word is shifted in at the same time as the outgoing word is shifted out, i.e., when both CA and F1i are low as illustrated in Figure 11. The NRZ/RZ low speed data is regenerated by the decoder section and output via  $D_R1$  and  $D_R2$ .

If the chip is operating in the RZ format,  $D_R^2$  transmits MARK pulses and  $D_R^1$  transmits SPACE pulses. The format of the output signal is shown in Figure 4. The width of an output pulse is nominally  $35\mu$ s and cannot be altered by the user. Violation pulses will appear on the line on which they were initially inserted at the remote end.

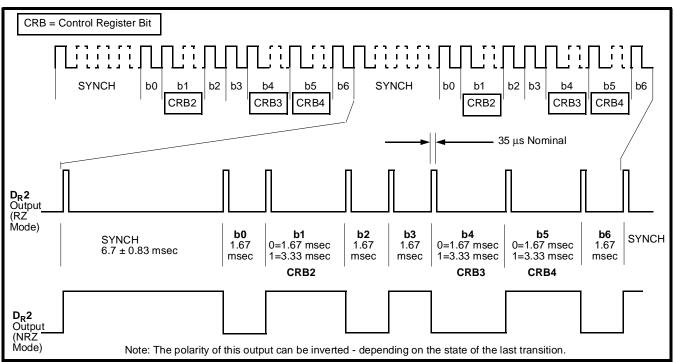

In the NRZ format  $D_R1$  outputs the data. The second output pin  $D_R2$ , transmits the secondary signal. Each transition in this signal represents one data pulse encoded by the remote end. An example of the type of waveform observed is illustrated in Figure 5.

The NRZ/RZ output circuitry also transmits synchronizing pulses if the data decoded from DSTi is idling (i.e., no data transitions) for more than six clock periods of the Secondary Clock (SCLK). This Secondary Clock is typically a 600Hz input to the chip. When the codec is set in the RZ format, these sync pulses will be either MARK or SPACE violation pulses, depending on the last data bit transmitted. If it is operating in the NRZ format, the sync pulses constitutes a squarewave with high and low durations of six SCLK periods. This squarewave appears at the D<sub>R</sub>2 output pin. Synchronization pulses are transmitted until some activity is detected by the decoder or the mode of operation is changed through the Control Register.

#### **Timing Requirements**

The data codec derives all the internal timing from the 2.048 MHz clock input (C2i) and the two enable signals  $\overline{F1i}$  and  $\overline{CA}$ . The DSTo output goes from high impedance to the value of bit 7 of the TEM

ISO-CMOS **MT8950**

Figure 4 - Example Input/Output Waveform in the RZ format (DF=HIGH)

word on the first rising edge of the clock after F1i and CA are taken low. The 8 bit TEM word from the input ST-BUS stream is clocked into the device on the negative edge of the C2i clock. For proper codec operation, the ST-BUS interface (DSTo, DSTi, and CSTi) should be enabled for only 8 clock periods of the C2i clock in any 125µs period (one ST-BUS frame time) as shown in Figure 11. All data input and output at the ST-BUS interface takes place at 2.048 Mbps.

Figure 5 - Example Input/Output Waveform in the NRZ format (DF=LOW)

The Secondary Clock input (SCLK) is normally a 600Hz clock signal. This clock is internally aligned with the 2.048 MHz input. It is used to generate the synchronizing pulses and the violation word timing (when the chip is operating in the local carrier mode). Note that the 600Hz frequency is an exact multiple of the most commonly used baud rates, i.e., 300, 2400, 4800, 9600, and 19200. In synchronous data transmission schemes, the receiver timing circuitry can be kept in sync using the synchronizing pulses or the violation word when no data is being transmitted. Other clock frequencies can be used for specific applications. If this facility is not to be utilized, the SCLK input can be tied to ground.

#### **Control Interface**

An 8 bit word is read into the Control Register via the CSTi input at the same time as the TEM word is being shifted in. The chip functions controlled by the eight bits are summarized in Table 3 and described in subsequent sections.

| Bit   | Function                                                                    |

|-------|-----------------------------------------------------------------------------|

| 7,6,5 | Device mode control bits. These bits select one of eight modes of operation |

| 4,3,2 | Violation word control bits                                                 |

| 1     | Resets the Data Activity Scan point                                         |

| 0     | Resets the Uncommitted Scan point                                           |

Table 3. Summary of Control Register Function

#### **Modes of Operation**

As mentioned earlier, the data codec can operate in eight different modes. The specific mode is selected through bits 7, 6 and 5 in the Control Register. Table 4 summarizes the different modes.

**Mode 0: Normal.** This is the normal transparent conversion mode of the data codec. The NRZ/RZ input signal is directly encoded into the TEM format and output as an ST-BUS channel. The TEM word for the input ST-BUS channel is decoded and the regenerated data is output via the NRZ/RZ output circuitry. Synchronizing pulses are also transmitted as explained in the preceding paragraphs.

**Mode 1: Local Carrier.** In this mode the NRZ/RZ output circuitry transmits an 8 bit word at  $D_R^2$  (Pin 18) by modulating the secondary clock (SCLK). If the chip has been selected to operate in the RZ format, this word is transmitted as MARK Violations. The time interval between consecutive pulses specifies the binary value. A logical zero is

represented by a time interval of one SCLK period between the pulses. A logic "1" is represented by two clock periods. In the NRZ mode, the time interval between consecutive transitions of the signal carries the information. The modulation scheme is illustrated in Figure 6. The 8 bit word consists of a

| Control Register<br>Bits |    |    | Mode of Operation                       |

|--------------------------|----|----|-----------------------------------------|

| b7                       | b6 | b5 |                                         |

| 0                        | 0  | 0  | Normal                                  |

| 0                        | 0  | 1  | Local Carrier                           |

| 0                        | 1  | 0  | Local Synchronization                   |

| 0                        | 1  | 1  | Digital Loopback                        |

| 1                        | 0  | 0  | Data Loopback                           |

| 1                        | 0  | 1  | Data Loopback - Local<br>Violation Word |

| 1                        | 1  | 0  | Normal Mode - Drive Point<br>Set HIGH.  |

| 1                        | 1  | 1  | Idle                                    |

#### Table 4. Modes of Operation

sync bit followed by seven other bits. Bits 1, 4 and 5 in this word reflect the values of bits 2, 3 and 4 in the Control Register. The remaining four bits in the word are fixed as zeros. The sync bit is identified by a time interval equal to four clock periods of SCLK. The NRZ/RZ input circuitry and the encoder stage operates normally in this mode.

**Mode 2: Local Synchronization.** In the local sync mode, the NRZ/RZ output circuitry transmits only sync pulses on  $D_R^2$ . These sync pulses appear as MARK violations in the RZ mode with the time interval between consecutive pulses equal to four SCLK periods. In the NRZ format  $D_R^2$  outputs a squarewave with a period equal to eight cycles of SCLK.  $D_R^1$  output is held at steady MARK. The NRZ/RZ input circuitry and the encoder stage of the chip function normally.

**Mode 3: Digital Loopback.** In this mode an 8 bit word from the incoming ST-BUS (DSTi) is sampled and one ST-BUS frame later, the same word is looped back to the corresponding outgoing channel of the ST-BUS (DSTo). This allows the user to test the ST-BUS transmission path to and from the data codec.

**Mode 4: Data Loopback**. This mode permits the user to test the decoding and encoding operation of the codec. A known TEM word is sent to the data codec from the ST-BUS end. This word is decoded and redirected via the output circuitry to the NRZ/RZ input circuit and subsequently to the encoder stage

for transmission out on the ST-BUS output pin (DSTo). The NRZ/RZ inputs (Pins 9 and 10) are functionally disconnected from the input circuitry. The outputs (pins 18 and 19) are in a non-active state, i.e.,  $D_R1$  is steady LOW and  $D_R2$  is steady HIGH.

**Mode 5: Data Loopback - Local Violation Word.** This mode can be used for testing the operation of the chip in the local carrier mode. The Violation word is generated as in the local carrier mode. However, the modulated signal is not output on  $D_R2$ . It is rerouted to the NRZ/RZ input circuit, encoded into the TEM format and output on DSTo.

**Mode 6: Normal Mode - Drive Point Activated.** The drive point output (Pin 14) is set HIGH in this mode. The codec operation is normal in every other respect. This drive point can be used to control external circuitry. It is reset when the mode of operation is changed.

**Mode 7: Idle.** In the idle mode  $D_R1$  and  $D_R2$  outputs are in a non-active state, i.e.,  $D_R1$  is steady LOW and  $D_R2$  is steady HIGH. The encoder stage and the input circuitry operates normally.

#### **Device Monitoring Features**

There are two output pins which can be used to monitor the codec.

- Data Activity (DA): This output goes from high to low when a SPACE signal, indicating the beginning of data activity, is received by the NRZ/ RZ input circuitry. The level on this pin is reset by setting bit 1 of the Control Register to logic "1".

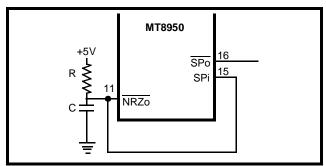

- 2. Scan Point output (SPo): This output is set LOW whenever SPi input undergoes a low to high transition. It is reset by a logic "1" in bit 0 of the Control Register. The SPi input is generally used in conjunction with pin 11 to detect a long SPACE condition in the data. The external circuitry required to utilize this feature is illustrated in Figure 7. Note that Pin 11 (NRZo) is an open drain output. The NRZ/RZ data input to the codec is converted to the NRZ format and output on this pin. The RC time constant for the circuit shown in Figure 7 can be set to detect SPACE conditions of varying time durations. The length of the long SPACE detected is given by

#### T<sub>SP</sub>=0.7RC

Where  $T_{SP}$  is the duration of the SPACE in milliseconds. A long SPACE of 150ms is generated when the BREAK key on a data terminal is depressed. To detect this signal, a value of R equal to 210 k $\Omega$  and C equal to 1.0µF can be used.

Figure 6 - Violation Word Timing in the Local Carrier Mode for a 600Hz input to SCLK

The SPo pin could then be monitored by the system processor to detect a prompt from the peripheral.

Figure 7 - Long Space Detection Circuit

#### **External Power Reset**

When the reset input ( $\overline{\text{PRST}}$ ) is taken low, the data codec circuit goes into reset mode. The conditions present on the output pins are as follows:

| 1. | DSTo             | - | High Impedance |                  |  |  |  |  |  |

|----|------------------|---|----------------|------------------|--|--|--|--|--|

| 2. | SPo              | - | +5V            | (unasserted)     |  |  |  |  |  |

| 3. | DA               | - | +5V            | (unasserted)     |  |  |  |  |  |

| 4. | DP               | - | GND            | (unasserted)     |  |  |  |  |  |

| 5. | D <sub>R</sub> 1 | - | +5V            | (inactive)       |  |  |  |  |  |

| 6. | D <sub>R</sub> 2 | - | GND            | (inactive)       |  |  |  |  |  |

| 7. | NRZo             | - | GND            | (Mark condition) |  |  |  |  |  |

The internal Control Register is loaded with HEX FF.

## **Applications**

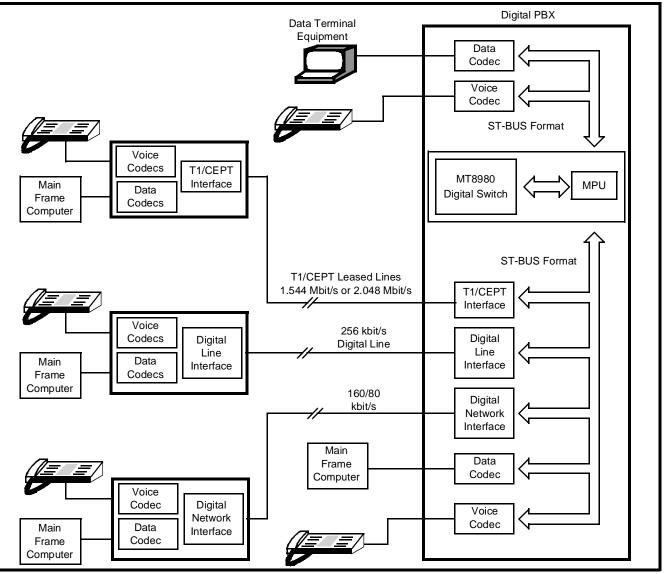

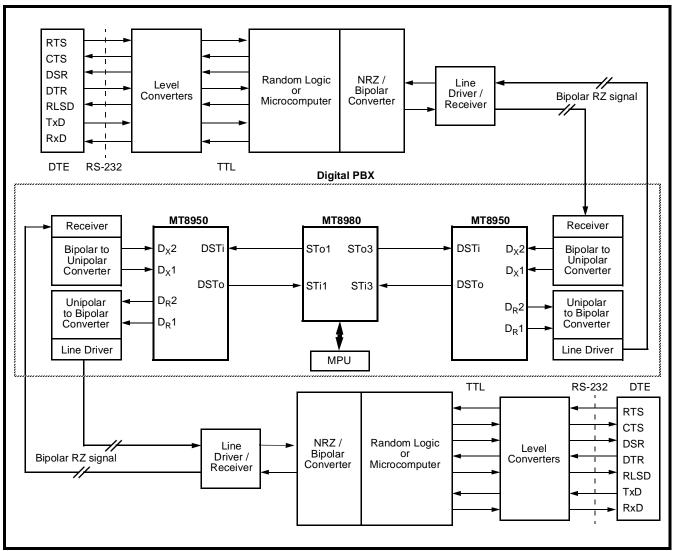

A block diagram schematic of a simple Voice-Data integrated switching system is illustrated in Figure 8. The data terminal can access a number of remote devices via the gateway provided by the Data Codec. In this application, the Data Codec function parallels that of the Voice Codec, i.e., the Voice

Figure 8 - Voice-Data integration using the Data Codec

Codec converts analog signals into the ST-BUS format while the Data Codec does a similar conversion for low speed data. The information in the ST-BUS format can be switched via the Digital Switch to any of the other interfaces and subsequently transmitted over the appropriate lines to the remote destination. At the remote end, the original signal is regenerated by another codec. The remote equipment can be part of a local area network or it may be accessed through leased T1/ CEPT digital lines. Access to remote equipment via the T1/CEPT leased lines is acquired through the T1/ CEPT interface (MT8976). Full duplex transmission at 1.544 or 2.048 Mbps is possible with this interface.

The Digital Network Interface Circuit (DNIC), the MT8972, is capable of providing 160 kbps full duplex transmission over single telephone pair wiring. This device can support two 64 kbps channels, allowing two data codecs to be interfaced to it at the remote end. Simple, low cost data sets can be constructed using the data codec and the DNIC.

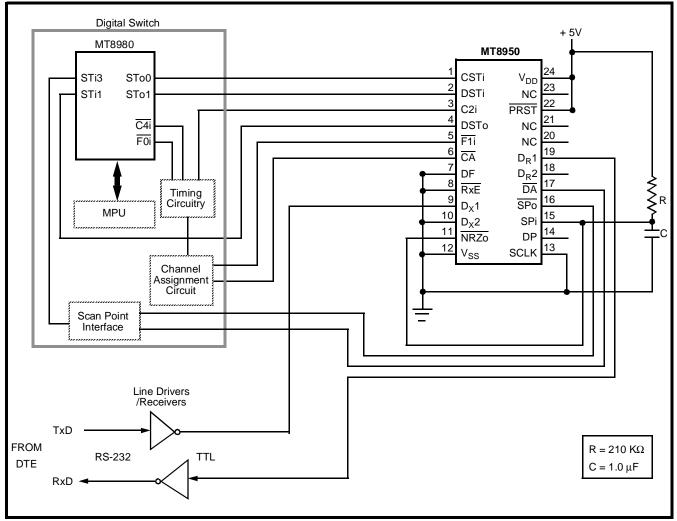

A simplified interface for transmitting and receiving RS-232 data signals is illustrated in Figure 9. The Codec is selected to receive and transmit low speed data in the NRZ format. The data transmitted by the terminal equipment in the RS-232 format is inverted and level shifted to TTL-compatible levels before being fed into the  $D_{\chi}1$  input on the Codec. The signal is converted into the ST-BUS format and transmitted via the DSTo output in one channel timeslot when the ST-BUS interface is enabled by  $\overline{F1i}$  and  $\overline{CA}$ , as dictated by the system channel assignment scheme. During this same time period the Codec accepts the 8 bit data arriving on the incoming ST-BUS stream which is output at the STo1 pin on the MT8980. The data is decoded and the original signal input at the remote end is regenerated and output at the D<sub>R</sub>1 pin. This signal is level shifted, inverted and transmitted to the terminal. The codec in this particular application requires no other programming. Loading of the Control Register via the CSTi input is optional. If this input is tied to ground, the Codec will operate in mode 0 (the normal mode). Note that the SCLK input is tied low. Thus synchronization pulses will not be transmitted and

Figure 9 - Simplified RS-232 Interface using the Data Codec

Figure 10 - Block Diagram Illustration of a Scheme to Submultiplex RS-232 Control Signals

the codec cannot be used in the local carrier mode. If this facility is to be used, an appropriate clock can be input to the device. The long SPACE detection circuitry and the Data Activity output can be used for monitoring the codec if necessary.

Figure 10 shows a block diagram schematic of a circuit which could be used to submultiplex RS-232 control signals with the data. The data and control signals are operated on by the microprocessor or the logic circuitry and subsequently transmitted as a three level signal. The control signals are encoded as bipolar violations. Since the control status does not change very frequently during a call, this information is transmitted only when no data is available. Circuitry near the Codec converts the bipolar signal into a unipolar format and inputs it at  $D_X1$  and  $D_X2$ . Conversely, the low speed data from the Codec output at  $D_R1$  and  $D_R2$  is first converted to the bipolar format before being transmitted.The Data Codec is selected to operate in the RZ format.

The microprocessor or the random logic circuit examines the received signal for violations. If a stream of violations is detected, then the signal is interpreted to be control information. The detected violations are decoded and the appropriate change in the status of the RS-232 control signals is implemented. If no violations are detected then the incoming signal is considered to be the data and it is rerouted to the RxD pin of the RS-232 connector. The microprocessor could also be used in the initial call setup and for error checking of the received control information. This scheme could be used to provide transparent modem capability to any of the ST-BUS based equipment.

|   | Parameter                                                                    | Symbol                           | Min                  | Max                  | Units |

|---|------------------------------------------------------------------------------|----------------------------------|----------------------|----------------------|-------|

| 1 | Supply Voltage                                                               | V <sub>DD</sub>                  | -0.5                 | 7.0                  | V     |

| 2 | DC Input Voltage                                                             | V <sub>IN</sub>                  | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 3 | DC Output Voltage                                                            | V <sub>OUT</sub>                 | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 4 | Input Diode Current ( V <sub>I</sub> <0 or V <sub>I</sub> >V <sub>DD</sub> ) | I <sub>IK</sub>                  |                      | ± 10                 | mA    |

| 5 | Output Diode Current ( $\rm V_O{<}0$ or $\rm V_O{>}V_{DD}$ )                 | I <sub>ОК</sub>                  |                      | ± 20                 | mA    |

| 6 | DC Output Current, per pin                                                   | ۱ <sub>۵</sub>                   |                      | ± 25                 | mA    |

| 7 | DC Supply or Ground Current                                                  | I <sub>DD</sub> /I <sub>SS</sub> |                      | ± 50                 | mA    |

| 8 | StorageTemperature                                                           | T <sub>ST</sub>                  | -65                  | 150                  | °C    |

| 9 | Package Power Dissipation (CERDIP) $T_A = 25^{\circ} C$                      | PD                               |                      | 1.0                  | W     |

#### Absolute Maximum Ratings\*- Voltages are with respect to ground (VSS) unless otherwise stated.

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### Recommended Operating Conditions - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|   | Characteristics       | Sym             | Min | Тур‡  | Max | Units | Test Conditions |

|---|-----------------------|-----------------|-----|-------|-----|-------|-----------------|

| 1 | Supply Voltage        | $V_{DD}$        | 4.5 | 5.0   | 5.5 | V     |                 |

| 2 | Operating Frequency   | f <sub>CK</sub> |     | 2.048 |     | MHz   |                 |

| 3 | Operating Temperature | T <sub>A</sub>  | 0   |       | 70  | °C    |                 |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

### **DC Electrical Characteristics**

V<sub>DD</sub>=5.0V±10%; V<sub>SS</sub>=0V; T<sub>A</sub>=0°C to 70°C - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|   |                  | Characteristics                                                 | Sym                                | Min                    | Тур <sup>‡</sup> | Max                    | Units  | Test Conditions                                                                                                                              |

|---|------------------|-----------------------------------------------------------------|------------------------------------|------------------------|------------------|------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |                  | Quiescent Supply Current                                        | I <sub>QS</sub>                    |                        |                  | 150                    | μA     | All outputs unloaded<br>All inputs @ V <sub>SS</sub>                                                                                         |

| 2 | S<br>U<br>P      | Operating supply current                                        | I <sub>DD</sub>                    |                        |                  | 1.0                    | mA     | All outputs unloaded.<br>Input pins 2 and 3 clocked at 2.048 MHz.<br>Pins 1,8,15,20,21 @ $V_{SS}$<br>Pins 5,6,7,9,10,13 and 22<br>@ $V_{DD}$ |

| 3 |                  | TTL inputs <sup>1</sup><br>HIGH voltage<br>LOW voltage          | V <sub>IH</sub><br>V <sub>IL</sub> | 2.0<br>V <sub>SS</sub> |                  | V <sub>DD</sub><br>0.8 | V<br>V |                                                                                                                                              |

| 4 | I<br>N           | CMOS inputs <sup>2</sup><br>HIGH voltage<br>LOW voltage         | V <sub>IH</sub><br>V <sub>IL</sub> | 3.5<br>V <sub>SS</sub> |                  | V <sub>DD</sub><br>1.5 | V<br>V |                                                                                                                                              |

| 5 | P<br>U<br>T<br>S | CMOS Schmitt inputs <sup>3</sup><br>HIGH voltage<br>LOW voltage | V <sub>IH</sub><br>V <sub>IL</sub> | 3.0<br>V <sub>SS</sub> |                  | V <sub>DD</sub><br>1.0 | > >    |                                                                                                                                              |

| 6 |                  | SPi Comparator ON Voltage                                       | V <sub>T+</sub>                    | 2.25                   | 2.5              | 2.75                   | V      | V <sub>DD</sub> = 5V                                                                                                                         |

| 7 |                  | SPi Comparator OFF Voltage                                      | V <sub>T-</sub>                    | 2.0                    |                  |                        | V      | V <sub>DD</sub> = 5V                                                                                                                         |

| 8 |                  | Input Leakage Current                                           | I <sub>IN</sub>                    |                        | ±1               | ±10                    | μA     | V <sub>DD</sub> = 5V                                                                                                                         |

Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Include DSTi, CSTi, C2i, F1i and SCLK

Include DF

3. Include  $\overline{RxE}$ ,  $D_X1$ ,  $D_X2$  and  $\overline{PRST}$

**DC Electrical Characteristics**  $V_{DD}$ =5.0V±10%;  $V_{SS}$ =0V;  $T_A$ =0°C to 70°C - Voltages are with respect to ground ( $V_{SS}$ ) unless otherwise stated.

|   |             | Characteristics                                     | Sym             | Min   | Тур <sup>‡</sup> | Max  | Units | Test Conditions                               |

|---|-------------|-----------------------------------------------------|-----------------|-------|------------------|------|-------|-----------------------------------------------|

| 1 |             | Output LOW voltage                                  | V <sub>OL</sub> |       |                  | 0.05 | V     | I <sub>O</sub>  < 1.0 μΑ V <sub>DD</sub> = 5V |

| 2 |             | Output HIGH Voltage                                 | V <sub>OH</sub> | 4.95  |                  |      | V     | I <sub>O</sub>  < 1.0 μA V <sub>DD</sub> = 5V |

| 3 | O<br>U      | Output LOW Current (On all<br>outputs except DSTo)  | I <sub>OL</sub> | 2.2   | 2.8              |      | mA    | V <sub>OL</sub> =0.4V                         |

| 4 | T<br>P      | Output HIGH Current (On all<br>outputs except DSTo) | I <sub>ОН</sub> | -3.5  | -4.2             |      | mA    | V <sub>OH</sub> =2.4V                         |

| 5 | U<br>T<br>S | Output LOW Current (On DSTo output)                 | I <sub>OL</sub> | 8.9   | 11.1             |      | mA    | V <sub>OL</sub> =0.4V                         |

| 6 |             | Output HIGH Current (On DSTo output)                | I <sub>ОН</sub> | -14.0 | -16.8            |      | mA    | V <sub>OH</sub> =2.4V                         |

| 7 |             | Output Leakage Current                              | I <sub>OZ</sub> |       | ±1               | ±10  | μA    |                                               |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

AC Electrical Characteristics<sup>†</sup> - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|    | Characteristics                                                | Sym                                  | Min   | Typ <sup>‡</sup> | Max   | Units | Test Conditions |

|----|----------------------------------------------------------------|--------------------------------------|-------|------------------|-------|-------|-----------------|

| 1  | C2i Clock Frequency                                            | f <sub>CK</sub>                      | 2.028 | 2.048            | 2.068 | MHz   |                 |

| 2  | C2i Clock Rise Time                                            | t <sub>CR</sub>                      |       |                  | 50    | ns    |                 |

| 3  | C2i Clock Fall Time                                            | t <sub>CF</sub>                      |       |                  | 50    | ns    |                 |

| 4  | Clock Duty Cycle (C2i & SCLK)                                  |                                      |       | 50               |       | %     |                 |

| 5  | SCLK Clock Frequency                                           | f <sub>SCLK</sub>                    | 0     | 0.6              | 128   | kHz   |                 |

| 6  | SCLK Clock Rise Time                                           | t <sub>SCLKR</sub>                   |       |                  | 50    | ns    |                 |

| 7  | SCLK Clock Fall Time                                           | t <sub>SCLKF</sub>                   |       |                  | 50    | ns    |                 |

| 8  | F1i and CA Rise Time                                           | t <sub>ER</sub>                      |       |                  | 100   | ns    |                 |

| 9  | F1i and CA Fall Time                                           | t <sub>EF</sub>                      |       |                  | 100   | ns    |                 |

| 10 | F1i and CA Setup Time                                          | t <sub>ES</sub>                      | 25    |                  |       | ns    |                 |

| 11 | $\overline{F1i}$ and $\overline{CA}$ Hold Time                 | t <sub>EH</sub>                      | -25   |                  | 25    | ns    |                 |

| 12 | DSTo Rise Time                                                 | t <sub>OR</sub>                      |       |                  | 100   | ns    | Note 1          |

| 13 | DSTo Fall Time                                                 | t <sub>OF</sub>                      |       |                  | 100   | ns    | Note 1          |

| 14 | Propagation Delay From Clock<br>(C2i) To Output (DSTo) enable. | t <sub>PZH</sub><br>t <sub>PZL</sub> |       |                  | 125   | ns    | Note 1          |

| 15 | Propagation Delay From Clock<br>(C2i) To Output (DSTo).        | t <sub>PLH</sub><br>t <sub>PHL</sub> |       |                  | 125   | ns    | Note 1          |

| 16 | Input Rise Time (DSTi, CSTi)                                   | t <sub>IR</sub>                      |       |                  | 100   | ns    |                 |

| 17 | Input Fall Time (DSTi, CSTi)                                   | t <sub>IF</sub>                      |       |                  | 100   | ns    |                 |

| 18 | DSTi, CSTi Setup Time                                          | t <sub>ISH</sub><br>t <sub>ISL</sub> | 0     |                  |       | ns    |                 |

| 19 | DSTi, CSTi Hold Time                                           | t <sub>IH</sub>                      | 90    |                  |       | ns    |                 |

| 20 | PRST Low Time                                                  |                                      | 488   |                  |       | ns    |                 |

† Timing is over recommended temperature & power supply voltages. ‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing. Note 1:  $R_L$ =10KΩ to  $V_{DD}$ ,  $C_L$ =150 pF to  $V_{SS}$

# ISO-CMOS **MT8950**

Figure 12 - Timing Diagram - ST-BUS Interface Enable

Figure 13 - Timing Diagram - ST-BUS Input/Output

NOTES: