# MC14560B

# **NBCD** Adder

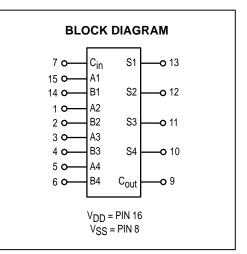

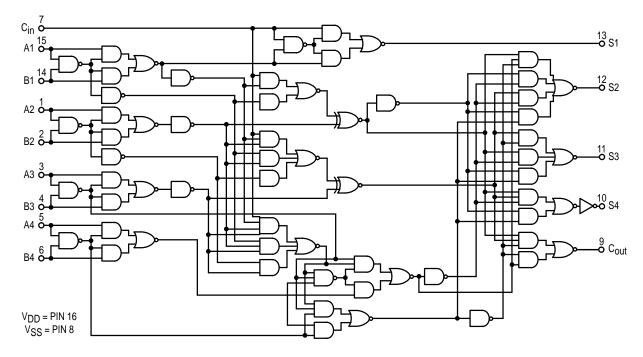

The MC14560B adds two 4–bit numbers in NBCD (natural binary coded decimal) format, resulting in sum and carry outputs in NBCD code.

This device can also subtract when one set of inputs is complemented with a 9's Complementer (MC14561B).

All inputs and outputs are active high. The carry input for the least significant digit is connected to  $V_{SS}$  for no carry in.

- Diode Protection on All Inputs

- Supply Voltage Range = 3.0 Vdc to 18 Vdc

- Capable of Driving Two Low–power TTL Loads or One Low–power Schottky TTL Load Over the Rated Temperature Range

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol                             | Parameter                                          | Value                          | Unit |

|------------------------------------|----------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub>                    | DC Supply Voltage                                  | – 0.5 to + 18.0                | V    |

| V <sub>in</sub> , V <sub>out</sub> | Input or Output Voltage (DC or Transient)          | – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub> , l <sub>out</sub> | Input or Output Current (DC or Transient), per Pin | ± 10                           | mA   |

| PD                                 | Power Dissipation, per Package†                    | 500                            | mW   |

| T <sub>stg</sub>                   | Storage Temperature                                | – 65 to + 150                  | °C   |

| ΤL                                 | Lead Temperature (8–Second Soldering)              | 260                            | °C   |

\* Maximum Ratings are those values beyond which damage to the device may occur. †Temperature Derating:

Plastic "P and D/DW" Packages: – 7.0 mW/°C From  $65^{\circ}$ C To  $125^{\circ}$ C Ceramic "L" Packages: – 12 mW/°C From  $100^{\circ}$ C To  $125^{\circ}$ C

| _  | -     |    |    |    |    |    |    |     |      |       |            |    |    |

|----|-------|----|----|----|----|----|----|-----|------|-------|------------|----|----|

|    | Input |    |    |    |    |    |    |     | 0    | utput |            |    |    |

| A4 | A3    | A2 | A1 | B4 | B3 | B2 | B1 | Cin | Cout | S4    | <b>S</b> 3 | S2 | S1 |

| 0  | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0    | 0     | 0          | 0  | 0  |

| 0  | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 1   | 0    | 0     | 0          | 0  | 1  |

| 0  | 1     | 0  | 0  | 0  | 0  | 1  | 1  | 0   | 0    | 0     | 1          | 1  | 1  |

| 0  | 1     | 0  | 0  | 0  | 0  | 1  | 1  | 1   | 0    | 1     | 0          | 0  | 0  |

| 0  | 1     | 1  | 1  | 0  | 1  | 0  | 0  | 0   | 1    | 0     | 0          | 0  | 1  |

| 0  | 1     | 1  | 1  | 0  | 1  | 0  | 0  | 1   | 1    | 0     | 0          | 1  | 0  |

| 1  | 0     | 0  | 0  | 0  | 1  | 0  | 1  | 0   | 1    | 0     | 0          | 1  | 1  |

| 0  | 1     | 1  | 0  | 1  | 0  | 0  | 0  | 0   | 1    | 0     | 1          | 0  | 0  |

| 1  | 0     | 0  | 1  | 1  | 0  | 0  | 1  | 1   | 1    | 1     | 0          | 0  | 1  |

**TRUTH TABLE\***

\* Partial truth table to show logic operation for representative input values.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ . Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs must be left open.

REV 0 1/94

© Motorola, Inc. 1994

#### ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS)

|                                                                                                                                                       |           |                 | V <sub>DD</sub>        | – 55°C                            |                      |                                   | 25°C                                      |                      |                                   | 125°C                |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|------------------------|-----------------------------------|----------------------|-----------------------------------|-------------------------------------------|----------------------|-----------------------------------|----------------------|------|

| Characteristic                                                                                                                                        |           | Symbol          | Vdc                    | Min                               | Max                  | Min                               | Typ #                                     | Max                  | Min                               | Max                  | Unit |

| Output Voltage<br>V <sub>in</sub> = V <sub>DD</sub> or 0                                                                                              | "0" Level | VOL             | 5.0<br>10<br>15        |                                   | 0.05<br>0.05<br>0.05 | _<br>_<br>_                       | 0<br>0<br>0                               | 0.05<br>0.05<br>0.05 |                                   | 0.05<br>0.05<br>0.05 | Vdc  |

| V <sub>in</sub> = 0 or V <sub>DD</sub>                                                                                                                | "1" Level | VOH             | 5.0<br>10<br>15        | 4.95<br>9.95<br>14.95             |                      | 4.95<br>9.95<br>14.95             | 5.0<br>10<br>15                           |                      | 4.95<br>9.95<br>14.95             |                      | Vdc  |

| Input Voltage<br>$(V_O = 4.5 \text{ or } 0.5 \text{ Vdc})$<br>$(V_O = 9.0 \text{ or } 1.0 \text{ Vdc})$<br>$(V_O = 13.5 \text{ or } 1.5 \text{ Vdc})$ | "0" Level | VIL             | 5.0<br>10<br>15        |                                   | 1.5<br>3.0<br>4.0    |                                   | 2.25<br>4.50<br>6.75                      | 1.5<br>3.0<br>4.0    |                                   | 1.5<br>3.0<br>4.0    | Vdc  |

| (V <sub>O</sub> = 0.5 or 4.5 Vdc)<br>(V <sub>O</sub> = 1.0 or 9.0 Vdc)<br>(V <sub>O</sub> = 1.5 or 13.5 Vdc)                                          | "1" Level | VIH             | 5.0<br>10<br>15        | 3.5<br>7.0<br>11                  |                      | 3.5<br>7.0<br>11                  | 2.75<br>5.50<br>8.25                      |                      | 3.5<br>7.0<br>11                  |                      | Vdc  |

| Output Drive Current<br>$(V_{OH} = 2.5 \text{ Vdc})$<br>$(V_{OH} = 4.6 \text{ Vdc})$<br>$(V_{OH} = 9.5 \text{ Vdc})$<br>$(V_{OH} = 13.5 \text{ Vdc})$ | Source    | IOH             | 5.0<br>5.0<br>10<br>15 | - 3.0<br>- 0.64<br>- 1.6<br>- 4.2 | <br>                 | - 2.4<br>- 0.51<br>- 1.3<br>- 3.4 | - 4.2<br>- 0.88<br>- 2.25<br>- 8.8        |                      | - 1.7<br>- 0.36<br>- 0.9<br>- 2.4 | <br><br>             | mAdc |

| (V <sub>OL</sub> = 0.4 Vdc)<br>(V <sub>OL</sub> = 0.5 Vdc)<br>(V <sub>OL</sub> = 1.5 Vdc)                                                             | Sink      | I <sub>OL</sub> | 5.0<br>10<br>15        | 0.64<br>1.6<br>4.2                |                      | 0.51<br>1.3<br>3.4                | 0.88<br>2.25<br>8.8                       |                      | 0.36<br>0.9<br>2.4                |                      | mAdc |

| Input Current                                                                                                                                         |           | l <sub>in</sub> | 15                     | —                                 | ±0.1                 | —                                 | ±0.00001                                  | ±0.1                 | —                                 | ±1.0                 | μAdc |

| Input Capacitance<br>(V <sub>in</sub> = 0)                                                                                                            |           | C <sub>in</sub> | _                      | _                                 | _                    | _                                 | 5.0                                       | 7.5                  | _                                 | _                    | pF   |

| Quiescent Current<br>(Per Package)                                                                                                                    |           | IDD             | 5.0<br>10<br>15        |                                   | 5.0<br>10<br>20      |                                   | 0.005<br>0.010<br>0.015                   | 5.0<br>10<br>20      |                                   | 150<br>300<br>600    | μAdc |

| Total Supply Current**†<br>(Dynamic plus Quiesce<br>Per Package)<br>(C <sub>L</sub> = 50 pF on all outp<br>buffers switching)                         |           | ŀΤ              | 5.0<br>10<br>15        |                                   |                      | I <sub>T</sub> = (3               | .68 μΑ/kHz)<br>.35 μΑ/kHz)<br>.03 μΑ/kHz) | f + I <sub>DD</sub>  |                                   |                      | μAdc |

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

\*\* The formulas given are for the typical characteristics only at  $25^{\circ}$ C.

†To calculate total supply current at loads other than 50 pF:

$I_T(C_L) = I_T(50 \text{ pF}) + (C_L - 50) \text{ Vfk}$

where: IT is in  $\mu$ A (per package), CL in pF, V = (V<sub>DD</sub> - V<sub>SS</sub>) in volts, f in kHz is input frequency, and k = 0.005.

| PIN ASSIGNMENT    |    |    |       |  |  |  |  |  |  |

|-------------------|----|----|-------|--|--|--|--|--|--|

| A2 [              | 1• | 16 | D VDD |  |  |  |  |  |  |

| B2 [              | 2  | 15 | ] A1  |  |  |  |  |  |  |

| A3 [              | 3  | 14 | ] B1  |  |  |  |  |  |  |

| B3 [              | 4  | 13 | ] S1  |  |  |  |  |  |  |

| A4 [              | 5  | 12 | ] S2  |  |  |  |  |  |  |

| B4 [              | 6  | 11 | ] S3  |  |  |  |  |  |  |

| C <sub>in</sub> [ | 7  | 10 | ] S4  |  |  |  |  |  |  |

| v <sub>ss</sub> E | 8  | 9  | Cout  |  |  |  |  |  |  |

## PIN ASSIGNMENT

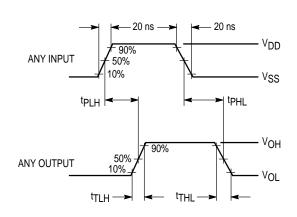

### SWITCHING CHARACTERISTICS\* (CL = 50 pF, TA = $25^{\circ}$ C)

| Characteristic                                                                                                                                                                                                                                | Symbol                                         | V <sub>DD</sub> | Min      | Typ #             | Max                | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|----------|-------------------|--------------------|------|

| Output Rise and Fall Time<br>$t_{TLH}$ , $t_{THL} = (1.5 \text{ ns/pF}) C_{L} + 25 \text{ ns}$<br>$t_{TLH}$ , $t_{THL} = (0.75 \text{ ns/pF}) C_{L} + 12.5 \text{ ns}$<br>$t_{TLH}$ , $t_{THL} = (0.55 \text{ ns/pF}) C_{L} + 9.5 \text{ ns}$ | <sup>t</sup> т∟н, tтн∟                         | 5.0<br>10<br>15 |          | 100<br>50<br>40   | 200<br>100<br>80   | ns   |

| Propagation Delay Time<br>A or B to S<br>tpLH, tpHL = (1.7 ns/pF) CL + 665 ns<br>tpLH, tpHL = (0.66 ns/pF) CL + 297 ns<br>tpLH, tpHL = (0.5 ns/pF) CL + 195 ns                                                                                | <sup>t</sup> PLH <sup>,</sup> <sup>t</sup> PHL | 5.0<br>10<br>15 | <br><br> | 750<br>330<br>220 | 2100<br>900<br>675 | ns   |

| A or B to C <sub>OUt</sub><br>tpLH, tpHL = (1.7 ns/pF) CL + 565 ns<br>tpLH, tpHL = (0.66 ns/pF) CL + 197 ns<br>tpLH, tpHL = (0.5 ns/pF) CL + 145 ns                                                                                           |                                                | 5.0<br>10<br>15 |          | 650<br>230<br>170 | 1800<br>600<br>450 | ns   |

| C <sub>in</sub> to C <sub>OUt</sub><br>tpLH, tpHL = (1.7 ns/pF) CL + 465 ns<br>tpLH, tpHL = (0.66 ns/pF) CL + 187 ns<br>tpLH, tpHL = (0.5 ns/pF) CL + 135 ns                                                                                  |                                                | 5.0<br>10<br>15 |          | 550<br>220<br>160 | 1500<br>600<br>450 | ns   |

| Turn–Off Delay Time<br>$C_{in}$ to S<br>$t_{PLH} = (1.7 \text{ ns/pF}) C_L + 715 \text{ ns}$<br>$t_{PLH} = (0.66 \text{ ns/pF}) C_L + 197 \text{ ns}$<br>$t_{PLH} = (0.5 \text{ ns/pF}) C_L + 215 \text{ ns}$                                 | <sup>t</sup> PLH                               | 5.0<br>10<br>15 |          | 800<br>350<br>240 | 2250<br>975<br>750 | ns   |

| Turn–On Delay Time<br>$C_{in}$ to S<br>$t_{PHL} = (1.7 \text{ ns/pF}) C_L + 565 \text{ ns}$<br>$t_{PHL} = (0.66 \text{ ns/pF}) C_L + 197 \text{ ns}$<br>$t_{PHL} = (0.5 \text{ ns/pF}) C_L + 145 \text{ ns}$                                  | <sup>t</sup> PHL                               | 5.0<br>10<br>15 | <br><br> | 650<br>230<br>170 | 1800<br>600<br>450 | ns   |

\* The formulas given are for the typical characteristics only at  $25^{\circ}$ C.

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

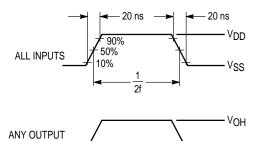

VOL

Duty Cycle = 50%

All outputs connected to respective  $C_L$  loads f = System clock frequency

Figure 2. Switching Time Waveforms

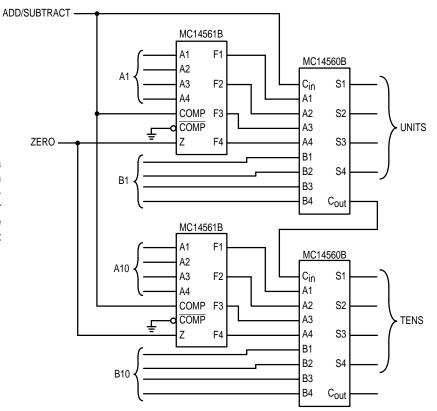

One MC14560B and MC14561B permit a BCD digit to be added to or subtracted from a second digit, such as in this typical configuration. A second MC14561B permits either digit to be added to or subtracted from the other, or either word to appear unmodified at the output.

#### **TRUTH TABLE**

| Zero | Add/Subtract | Result    |

|------|--------------|-----------|

| 0    | 0            | B plus A  |

| 0    | 1            | B minus A |

| 1    | Х            | В         |

X = Don't Care

#### INTRODUCTION

Frequently in small digital systems, simple decimal arithmetic is performed. Decimal data enters and leaves the system arithmetic unit in a binary coded decimal (BCD) format. The adder/subtracter in the arithmetic unit may be required to accept sign as well as magnitude, and generate sign, magnitude, and overflow. In the past, it has been cumbersome to build sign and magnitude adder/subtracters. Now, using Motorola's MSI CMOS functions, the MC14560 NBCD Adders and MC14561 9's Complementers, NBCD adder/ subtracters may be built economically, with surprisingly low package count and moderate speed.

Some background information on BCD arithmetic is presented here, followed by simple circuits for unsigned adder/ subtracters. The final circuit discussed is an adder/subtracter for signed numbers with complete overflow and sign correction logic.

#### DECIMAL NUMBER REPRESENTATION

Because logic elements are binary or two-state devices, decimal digits are generally represented as a group of bits in a weighted format. There are many possible binary codes which can be used to represent a decimal number. One of the most popular codes using 4 binary digits to represent 0 thru 9 is Natural Binary Coded Decimal (NBCD or 8–4–2–1 code).

NBCD is a weighted code. If a value of "0" or "1" is assigned to each of the bit positions, where the rightmost position is  $2^0$  and the leftmost is  $2^3$ , and the values are summed for a given code, the result is equal to the decimal digit represented by the code. Thus, 0110 equals  $0 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 0 \cdot 2^0 = 4 + 2 = 6$ . The 1010, 1011, 1100, 1101, 1110, and 1111 binary codes are not used. Because of these illegal states, the addition and subtraction of NBCD numbers is more complex than similar calculations on straight binary numbers.

#### ADDITION OF UNSIGNED NBCD NUMBERS

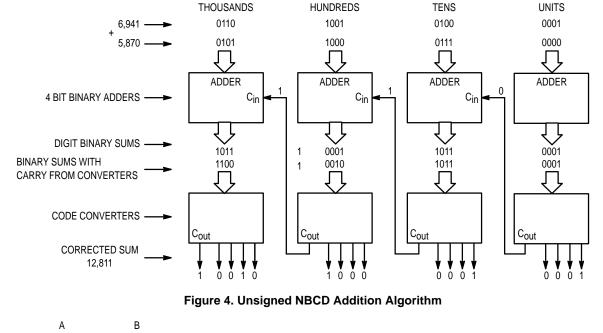

When 2 NBCD digits, A and B, and a possible carry, C, are added, a total of 20 digit sums (A + B + C) are possible as shown in Table 1.

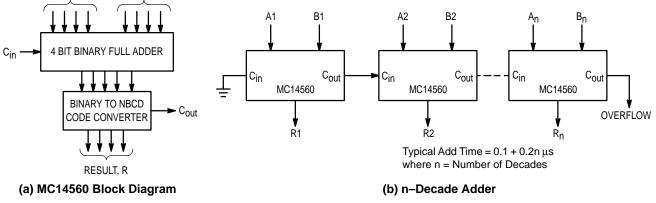

The binary representations for the digit sums 10 thru 19 are offset by 6, the number of unused binary states, and are not correct. An algorithm for obtaining the correct sum is shown in Figure 1. A conventional method of implementing the BCD addition algorithm is shown in Figure 2(a). The NBCD digits, A and B, are summed by a 4 bit binary full adder. The resultant (sum and carry) is input to a binary/BCD code converter which generates the correct BCD code and carry.

An NBCD adder block which performs the above function is available in a single CMOS package (MC14560).

Figure 2(b) shows n decades cascaded for addition of n digit unsigned NBCD numbers. Add time is typically  $0.1 + 0.2n \,\mu s$  for n decades. When the carry out of the most significant decade is a logical "1", an overflow is indicated.

#### **COMPLEMENT ARITHMETIC**

Complement arithmetic is used in NBCD subtraction. That is, the "complement" of the subtrahend is added to the minuend. The complementing process amounts to biasing the subtrahend such that all possible sums are positive. Consider the subtraction of the NBCD numbers, A and B:

$$R = A - B$$

where R is the result. Now bias both sides of the equation by  $10^{N} - 1$  where N is the number of digits in A and B.

Rearranging,

The term  $(10^{N} - 1 - B)$ , -B biased by  $10^{N} - 1$ , is known as the 9's complement of B. When A > B, R +  $10^{N} - 1 > 10^{N} - 1$ ; thus R is a positive number. To obtain R, 1 is added to R +  $10^{N} - 1$ , and the carry term,  $10^{N}$ , is dropped. The addition of 1 is called End Around Carry (EAC).

When A < B, R +  $10^{N} - 1 < 10^{N} - 1$ , no EAC results and R is a negative number biased by  $10^{N} - 1$ ; thus R +  $10^{N} - 1$  is the 9's complement of R.

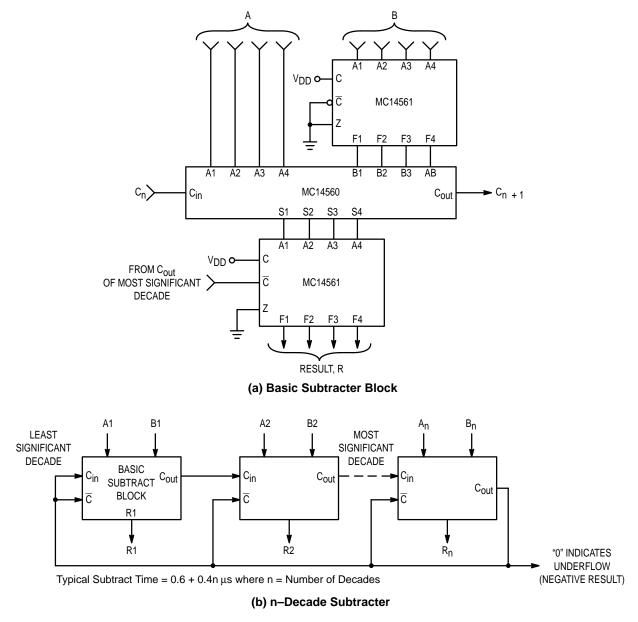

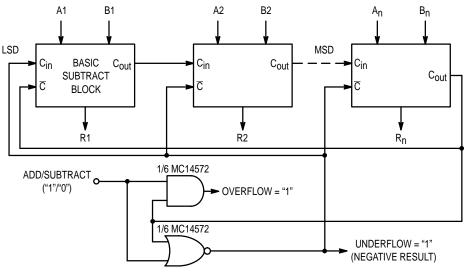

#### SUBTRACTION OF UNSIGNED NBCD NUMBERS

Nine's complement arithmetic requires an element to perform the complementing function. An NBCD 9's complementer may be implemented using a 4 bit binary adder and 4 inverters, or with combinatorial logic. The Motorola MC14561 9's complementer is available in a single package. It has true and inverted complement disable, which allow straightthrough or complement modes of operation. A "zero" line forces the output to "0". Figure 3 shows an NBCD subtracter block using the MC14560 and MC14561. Also shown are n cascaded blocks for subtraction of n digit unsigned numbers. Subtract time is 0.6 + 0.4n µs for n stages. Underflow (borrow) is indicated by a logical "0" on the carry output of the most significant digit. A "0" carry also indicates that the difference is a negative number in 9's complement form. If the result is input to a 9's complementer, as shown, and its mode controlled by the carry out of the most significant digit, the output of the complementer will be the correct negative magnitude. Note that the carry out of the most significant digit (MSD) is the input to carry in of the least significant digit (LSD). This End Around Carry is required because subtraction is done in 9's complement arithmetic.

By controlling the complement and overflow logic with an add/subtract line, both addition and subtraction are performed using the basic subtracter blocks (Figure 4).

Table 1. Sum = A + B + C

| Binary Sums         | Decimal<br>Numbers | Corrected<br>Binary Sums |

|---------------------|--------------------|--------------------------|

| 0000                | 0                  | 0000                     |

| 0001                | 1                  | 0001                     |

| 0010                | 2                  | 0010                     |

| 0011                | 3                  | 0011                     |

| 0100                | 4                  | 0100                     |

| 0101                | 5                  | 0101                     |

| 0110                | 6                  | 0110                     |

| 0111                | 7                  | 0111                     |

| 1000                | 8                  | 1000                     |

| 1001                | 9                  | 1001                     |

| 1010                | 10                 | 0000 + Carry             |

| 1011                | 11                 | 0001 + Carry             |

| 1100 Non valid      | 12                 | 0010 + Carry             |

| 1101 ( BCD          | 13                 | 0011 + Carry             |

| 1110 representation | 14                 | 0100 + Carry             |

| 1111                | 15                 | 0101 + Carry             |

| 0000 + Carry        | 16                 | 0110 + Carry             |

| 0001 + Carry        | 17                 | 0111 + Carry             |

| 0010 + Carry        | 18                 | 1000 + Carry             |

| 0011 + Carry        | 19                 | 1001 + Carry             |

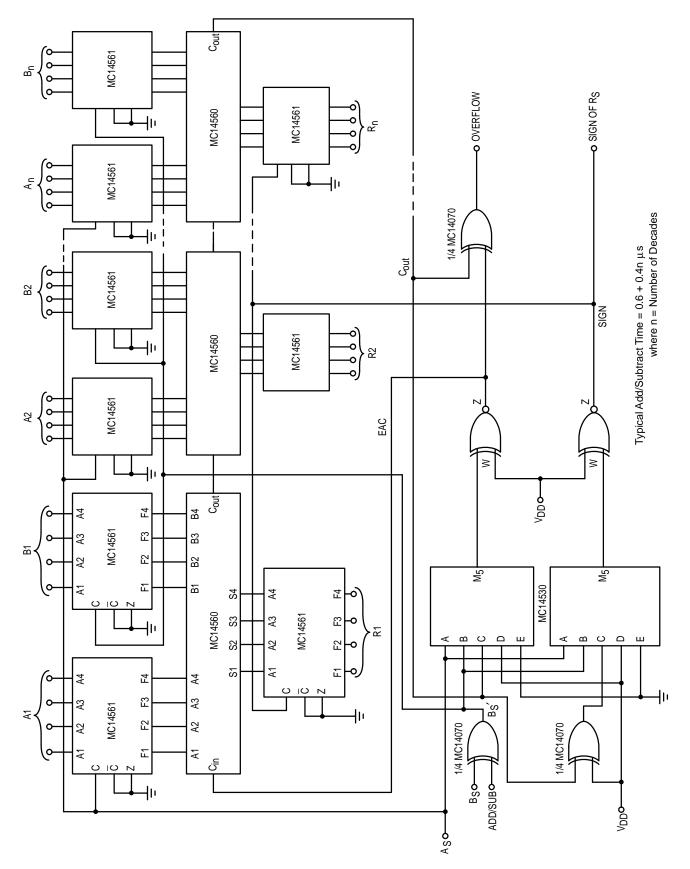

# ADDITION AND SUBTRACTION OF SIGNED NBCD NUMBERS

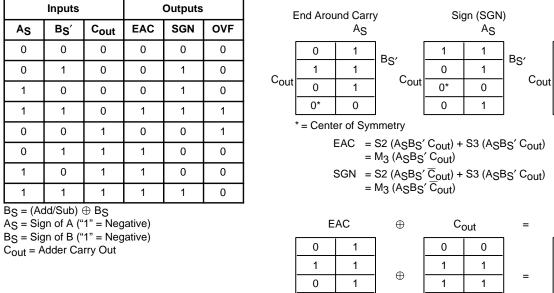

Using MC14560 NBCD Adders and MC14561 9's Complementers, a sign and magnitude adder/subtracter can be configured (Figure 5). Inputs A and B are signed positive (A<sub>S</sub>, B<sub>S</sub> = "0") or negative (A<sub>S</sub>, B<sub>S</sub> = "1"). B is added to or subtracted from A under control of an Add/Sub line (subtraction = "1"). The result, R, of the operation is positive signed, positive signed with overflow, negative signed, or negative signed with overflow. Add/subtract time is typically 0.6 + 0.4n  $\mu$ s for n decades.

An exclusive–OR of Add/Sub line and B<sub>S</sub> produces B', which controls the B complementers. If B<sub>S</sub>, the sign of B, is a logical "1" (B is negative) and the Add/Sub line is a "0" (add B to A), then the output of the exclusive–OR (B<sub>S</sub>') is a logical "1" and B is complemented. If B<sub>S</sub> = "1" and Add/Sub = "1", B is not complemented since subtracting a negative number is the same as adding a positive number. When Add/Sub is a "1" and B<sub>S</sub> = "0", B<sub>S</sub>' is a "1" and B is complemented. The A complementer is controlled by the A sign bit, A<sub>S</sub>. When A<sub>S</sub> = "1", A is complemented.

The truth table and Karnaugh maps for sign, overflow, and End Around Carry are shown in Figures 6 and 7. Note the use of BS' from the exclusive–OR of Add/Sub and BS. BS' eliminates Add/Sub as a variable in the truth table. As an example of truth table generation, consider an n decade adder/ subtracter where  $A_S = "0"$ ,  $B_S = "1"$ , and Add/Sub = "0". B is in 9's complement form,  $10^N - 1 - B$ . Thus  $A + (10^N - 1 - B) = 10^N - 1 + (A - B)$ . There is no carry when  $A \le B$ , and the sign is negative (sign = "1"). When  $A_S$  and  $B_S$  are opposite states and Add/Sub is a "0" (add mode), no overflow can occur (overflow = "0"). The other output states are determined in a similar manner (see Figure 6).

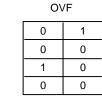

From the Karnaugh maps it is apparent that End Around Carry is composed of the two symmetrical functions S2 and S3 of three variables with  $A_S B_S' C_{out}$  as the center of symmetry. This is the definition of the majority logic function M<sub>3</sub>(ABC). Similarly the Sign is composed of the symmetrical functions S2(3) and S3(3) but with the center of symmetry

translated to  $A_SB_S' C_{Out}$ . This is equivalent to the majority function  $M_3(A_SB_S' \overline{C}_{Out})$ . Further evaluation of the maps and truth table reveal that Overflow can be generated by the exclusive–OR function of End Around Carry and Carry Out. This analysis results in a minimum device count consisting of one exclusive–OR package and one dual Majority Logic package to implement  $B_S'$ , EAC, Sign and Overflow. The logic connections of these devices are shown in Figure 5.

The output sign, R<sub>S</sub>, complements the result of the add/ subtract operation when  $R_S = "1"$ . This is required because the adder performs 9's complement arithmetic. Complementing, when R<sub>S</sub> indicates the result is negative, restores sign and magnitude convention.

Several variations of the adder/subtracter are possible. For example, 9's complement is available at the output of the NBCD adders, and output complementers are eliminated if sign and magnitude output is not required.

MOTOROLA CMOS LOGIC DATA

#### SUMMARY

The concepts of binary code representations for decimal numbers, addition, and complement subtraction were discussed in detail. Using the basic Adder and Complementer MSI blocks, adder/subtracters for both signed and unsigned numbers were illustrated with examples.

#### REFERENCES

- 1. Chu, Y.: *Digital Computer Design Fundamentals*, New York, McGraw–Hill, 1962.

- 2. *McMOS Handbook*, Motorola Inc., 1st Edition.

- 3. Beuscher, H.: *Electronic Switching Theory and Circuits*, New York, Van Nostrand Reinhold, 1971.

- 4. Garrett, L.: CMOS May Help Majority Logic Win Designer's Vote, *Electronics*, July 19, 1973.

- 5. Richards, R.: *Digital Design*, New York, Wiley– Interscience, 1971.

Typical Add/Subtract Time =  $0.6 + 0.4 \text{ n} \mu \text{s}$ where n = Number of Decades

Figure 7. Adder/Subtracter for Unsigned NBCD Numbers

Figure 8. Sign and Magnitude Adder/Subtracter with Overflow

| Inputs          |                  |                                 | Arithmatic Expression<br>for R* (Result)<br>(N = Number of Digits,                                                   | Outputs                                                                             |                                                                                    |                                                                                                                      |  |  |  |

|-----------------|------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| As<br>"1" = Neg | Bs′<br>"1" = Neg | C <sub>out</sub><br>"1" = Carry | 10 <sup>N</sup> = Modulus<br>A, B, R are Positive<br>Magnitudes)                                                     | End Around<br>Carry (EAC)<br>"1" = EAC                                              | Sign of R<br>"1" = Negative                                                        | Overflow<br>"1" = Overflow                                                                                           |  |  |  |

| 0               | 0                | 0                               | R = A + 8                                                                                                            | No EAC ("0")<br>because R is correct<br>result.                                     | Since A and B are<br>positive signed, R is<br>positive signed ("0").               | When $C_{out} = "0"$ , there<br>is no carry (R < $10^{N}$ )<br>and thus no overflow<br>("0").                        |  |  |  |

| 0               | 0                | 1                               |                                                                                                                      |                                                                                     |                                                                                    | When $C_{out} = "1"$ , there is a carry ( $R \ge 10^N$ ) and thus overflow ("1").                                    |  |  |  |

| 0               | 1                | 0                               | R = A - B<br>= A + (10 <sup>N</sup> - 1 - B)<br>= A - B + 10 <sup>N</sup> - 1                                        | No EAC ("0")<br>because 9's<br>complement<br>expression for R is<br>correct result. | $A \leq B$ when $C_{out} =$<br>"0"; thus sign of R<br>must be negative<br>("1").   |                                                                                                                      |  |  |  |

| 0               | 1                | 1                               |                                                                                                                      | EAC = "1" because<br>expression for R is in<br>error by 1.                          | A > B when C <sub>out</sub> =<br>"1"; thus sign of R<br>must be positive<br>("0"). | There is never an overflow when                                                                                      |  |  |  |

| 1               | 0                | 0                               | R = B - A<br>= B + (10 <sup>N</sup> - 1 - A)<br>= B - A + 10 <sup>N</sup> - 1                                        | No EAC ("0")<br>because 9's<br>complement<br>expression for R is<br>correct result. | $B \le A$ when $C_{out} =$<br>"0"; thus sign of R<br>must be negative<br>("1").    | numbers of opposite<br>sign are added.                                                                               |  |  |  |

| 1               | 0                | 1                               |                                                                                                                      | EAC = "1" because<br>expression for R is in<br>error by 1.                          | B > A when C <sub>out</sub> =<br>"1"; thus sign of R<br>must be positive<br>("0"). |                                                                                                                      |  |  |  |

| 1               | 1                | 0                               | R = -A - B<br>= (10 <sup>N</sup> - 1 - A) +<br>(10 <sup>N</sup> - 1 - B)<br>= - (A + B) + 2 x<br>10 <sup>N</sup> - 2 | EAC = "1" because<br>9's complement<br>expression for R is in<br>error by 1.        | Since A and B are<br>negative signed. R is<br>negative signed ("1").               | When $C_{out} = "0"$ , there<br>is no Carry (R < 0N)<br>and (A + B) > $10^N - 1$<br>indicating overflow<br>("1").    |  |  |  |

| 1               | 1                | 1                               | ד איטן – 2                                                                                                           |                                                                                     |                                                                                    | When $C_{out} = $ "1", there is a carry (R $\ge 10^{N}$ ) and (A + B) $\le 10^{N} - 1$ indicating no overflow ("0"). |  |  |  |

\* Output of Adders

Figure 9. Truth Table Generation for EAC, Sign, and Overflow Logic

**TRUTH TABLE**

Cout

Inputs

Bs′

$C_{out} = Adder Carry Out$

As

## **KARNAUGH MAPS**

Overflow (OVF)

AS

B<sub>S′</sub>

Figure 10. Mapping of EAC, Sign and Overflow Logic

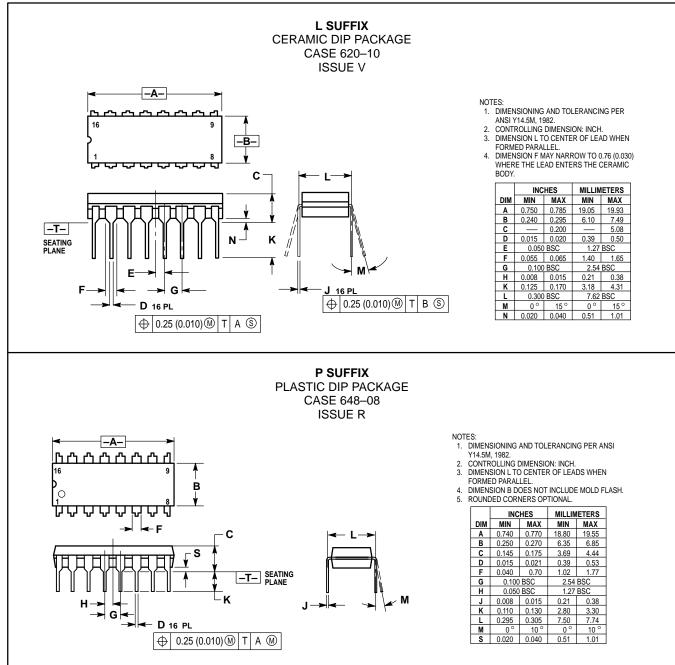

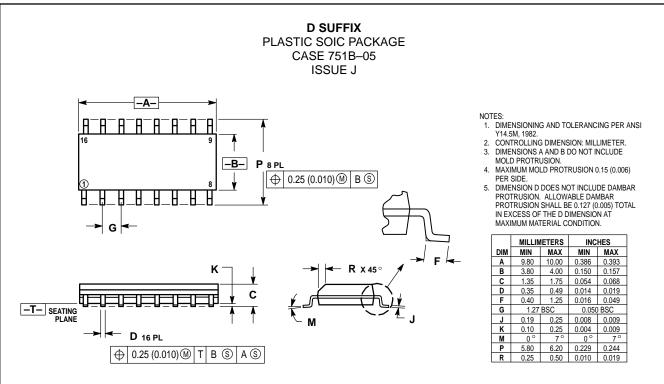

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **...** are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

$\Diamond$

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 INTERNET: http://Design\_NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298