# TMPZ84C00AP-6 / TMPZ84C00AM-6 / TMPZ84C00AT-6 TMPZ84C00AP-8 / TMPZ84C00AM-8 / TMPZ84C00AT-8

TLCS-Z80 MPU: 8-BIT MICROPROCESSOR

# 1. OUTLINE AND FEATURES

The TMPZ84C00A is an 8-bit microprocessor (hereinafter referred to as MPU), which provides low power operation and high performance.

Built into the TMPZ84C00A are bus control, memory control and timing control circuits in addition to paired 6 general purpose registers, accumulator, flag registers and an arithmetic-and-logic unit.

The TMPZ84C00A is fabricated using Toshiba's CMOS Silicon gate Technology.

The pricipal functions and features of the TMPZ84C00A are as follows.

Supply Current (TYP.) Operating Produce Name Frequency **AT RUN** STAND BY TMPZ84C00AP-6MHz 15mA  $0.5 \mu A$ 6/AM-6/AT-6 TMPZ84C00AP-8MHz 20mA  $0.5 \mu A$ 8/AM-8/AT-8

Table 1.1 Operating Frequency and Supply Current

060489

- (1) Commands compatible with the Zilog Z80 MPU.

- (2) Low power consumption

- (3) DC to 8MHz operation (at  $5V \pm 10\%$ )

- (4) Single 5V power supply  $(5V \pm 10\%)$

- (5) Operating temperature ( $-40^{\circ}$ C to 85°C)

- (6) Powerful set of 158 instrucitons available

- (7) Powerful interrupt function

- (a) Non-maskable interrupt terminal (NMI)

- (b) Maskable interrupt terminal (INT)

The following 3 modes are selectable:

- 8080 compatible interrupt mode (interrupt by Non-Z80 family peripheral LSI) (Mode 0)

- Restart interrupt (Mode 1)

- Daisy chain structure interrupt using Z80 family peripheral LSI (Mode 2)

- (8) An auxiliary resister provided to each of general purpose registers

- (9) Two index registers

- (10) 10 addressing modes

- (11) Built-in refresh circuit for dynamic memory

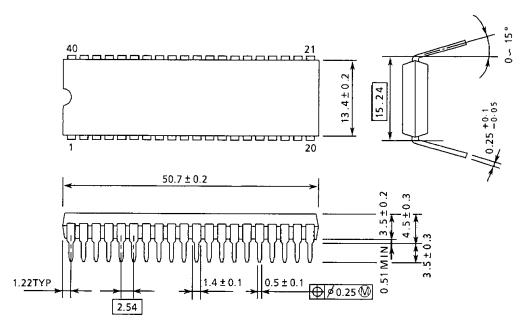

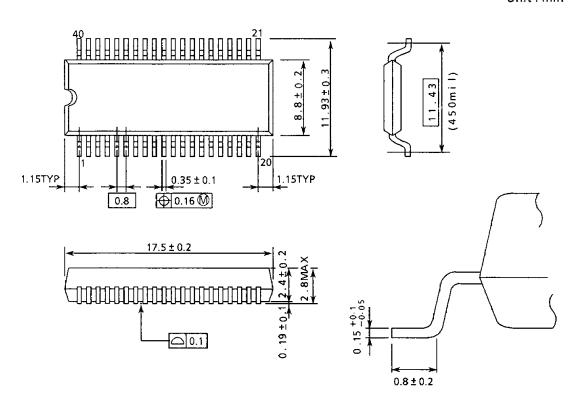

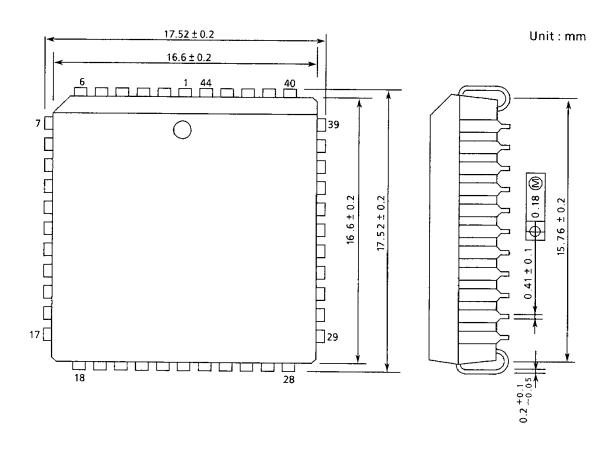

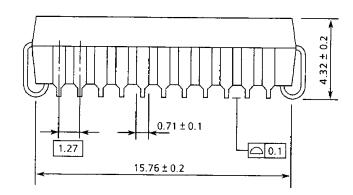

- (12) Molded in 40-pin DIP package (P), 40-pin SOP package (M) and 44-pin PLCC package (T).

Further, in the following text and explanations for charts and tables, hexadecimal numbers are directly used without giving an identification to explanation of address, etc. to the extent not to cause confusions.

Note: Z80 is a trademark of Zilog Inc., U.S.A.

# 2. PIN ASSIGNMENT AND FUNCTIONS

The pin assignment and I/O pin names and brief functions of TMPZ84C00A are shown below.

#### 2.1 PIN ASSIGNMENT (TOP View)

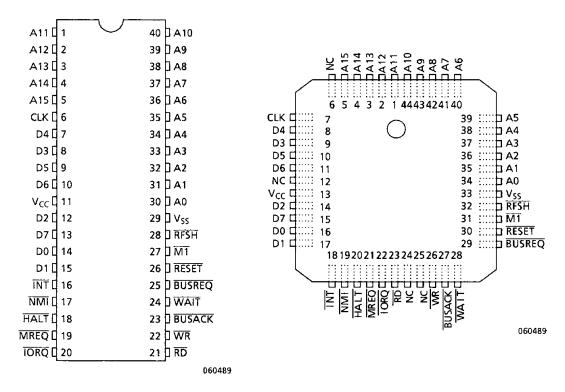

The pin assignment of the TMPZ84C00A are as shown in Figure 2.1 and Figure 2.2.

Figure 2.1 DIP, SOP Pin Assignment

Figure 2.2 PLCC Package Pin Assignment

#### 2.2 PIN NAMES AND FUNCTIONS

I/O pin names and functions are as shown Table 2.1.

Table 2.1 Pin names and Functions

(1/2)

| Pin    | Q'ty<br>(Number) | Туре                    | Function                                                                                                                                                                                                                                                                                                                                 |

|--------|------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7  | 8                | Input/output<br>3-state | The 8-bit bi-directional data bus.                                                                                                                                                                                                                                                                                                       |

| A0-A15 | 16               | Output<br>3-state       | The 16-bit address bus. These pins specify memory and I/O port addresses. During a refresh cycle, the refresh address is output.                                                                                                                                                                                                         |

| M1     | 1                | Output                  | The Machine Cycle 1 signal. In an operation code fetch cycle, this pin goes "0" with the MREQ signal. At the execution of a 2-byte operation code, this pin goes "0" for each operation code fetch. In a maskable interrupt acknowledge cycle, this pin goes "0" with the IORQ signal.                                                   |

| RD     | 1                | Output<br>3-state       | The Read signal. It indicates that the MPU is ready for accepting data from memory or I/O device. The data from the addressed memory or I/O devices is gated by this signal onto the MPU data bus.                                                                                                                                       |

| WR     | 1                | Output<br>3-state       | The Write signal. This signal is output when the data to be stored in the addressed memory or I/O device is on the data bus.                                                                                                                                                                                                             |

| MREQ   | 1                | Output<br>3-state       | The Memory Request signal. When the execution address for memory access is on the address bus, this pin goes "0". During a memory refresh cycle, this pin also goes "0" with RFSH signal.                                                                                                                                                |

| ĪORQ   | 1                | Output<br>3-state       | The Input/Output Request signal. This pin goes "0" when the address for an I/O read or write operation is on the low-order 8 bits (A0 through A7) of the address bus. The IORQ signal is also output with the MT signal at interrupt acknowledge to tell an I/O device that the interrupt response vector can be placed on the data bus. |

| CLK    | 1                | Input                   | The Single-phase Clock Input. When the clock input is placed in the DC state (continued "1" or "0" level), this pin stops operating and holds the state of that time.                                                                                                                                                                    |

(2/2)

|                   | <del>,</del>                          | ·,           | (2/2)                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin               | Q'ty<br>(Number)                      | Туре         | Function                                                                                                                                                                                                                                                                          |

| RESET             | 1                                     | Input        | The Reset signal input. RESET signal is used for initialization MPU and must be kept in active state ("0") for a period of at least 3 clocks.                                                                                                                                     |

| ĪNT               | 1                                     | Input        | The Maskable Interrupt signal. An interrupt is caused by the peripheral LSI. An interrupt is acknowledged when the interrupt enable flipflop (IFF) is set to "1" by software.  The INT pin is normally wire-ORed and requires an external pullup resistor for these applications. |

| WAIT              | 1                                     | Input        | The Wait Request signal. This signal indicates to the MPU that the addressed memory or I/O device is not ready for data transfer. As long as this signal is "0", the MPU is in the Wait state.                                                                                    |

| BUSREQ            | 1                                     | Input        | The bus Request signal. The BUSREQ signal forces the MPU address bus, data bus, and control signals MREQ, IORQ, RD, and WR to be placed in the high-impedance state. This signal is normally Wire-ORed and requires an external pullup resistor for these applications.           |

| BUSACK            | 1                                     | Output       | The Bus Acknowledge signal. In response to the BUSREQ signal, the BUSACK signal indicates to the requesting peripheral LSI that the MPU address bus, data bus, and control signals MREQ, IORQ, RD and WR have been put in the high-impedance state.                               |

| HALT              | 1                                     | Output       | The Halt signal. This pin goes "0" when the MPU has executed a Halt instruction and is in the Halt state.                                                                                                                                                                         |

| RFSH              | 1                                     | Output       | The refresh signal. When the dynamic memory refresh address is on the low-order 8 bits of the address bus, this signal goes "0". At the same time, the MREQ signal also goes active ("0").                                                                                        |

| NMI               | 1                                     | Input        | The Non-maskable Interrupt Request signal. This interrupt request has a higher priority than the maskable interrupt and is not dependent on the interrupt enable flip-flop (IFF) state.                                                                                           |

| NC<br>(PLCC only) | 4                                     | _            | Not connected internaly. Please use by open.                                                                                                                                                                                                                                      |

| V <sub>CC</sub>   | 1                                     | power supply | + 5 V                                                                                                                                                                                                                                                                             |

| Vss               | 1                                     | power supply | 0 V                                                                                                                                                                                                                                                                               |

|                   | · · · · · · · · · · · · · · · · · · · |              |                                                                                                                                                                                                                                                                                   |

TOSHIBA TMPZ84C00A

#### 3. FUNCTIONAL DESCRIPTION

The system configuration, functions and basic operation of the TMPZ84C00A are described here.

#### 3.1 BLOCK DIAGRAM

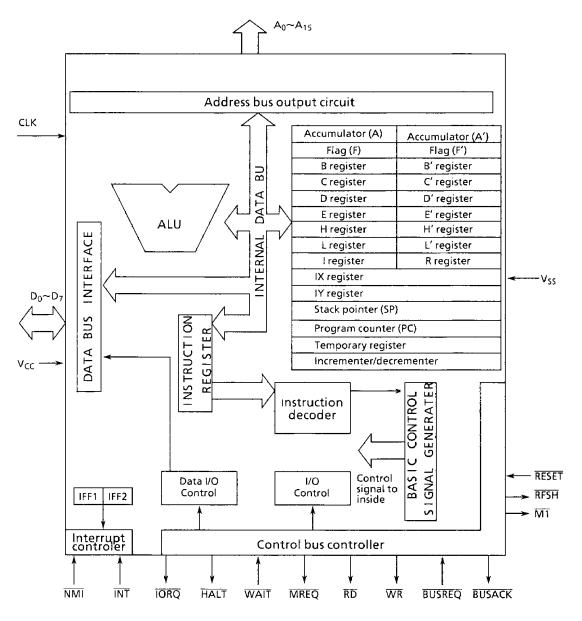

The block diagram of the internal configuration is shown in Figure 3.1.

Figure 3.1 Block Diagram

#### 3.2 SYSTEM CONFIGURATION

The MPU has the configuration shown in Figure 3.1. The address signal is put on the address bus via the address buffer. The data bus is controlled for input or output by the data bus interface. Both the address and data buses are put in the high-impedance state by the BUSEQ signal input to make them available for other peripheral LSIs. The Opcode read from memory via the data bus is written to the instruction register. This Opcode is decoded by the instruction decoder. According to the result of the decoding, control signals are sent to the relevant devices. Receiving these control signals, the ALU performs arithmetic operations. The register array temporarily hold the information required to perform operation.

The following describes the MPU's main components and functions which the user must understand to operate the TMPZ84C00A.

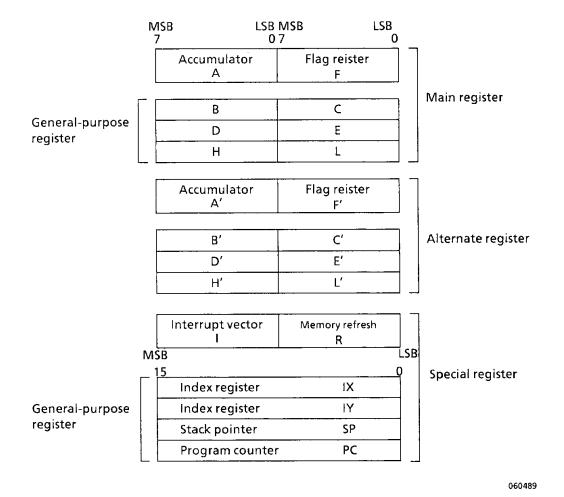

# [1] Internal Register Groups

The configuration of the internal register groups is as follows:

(1) Main registers

(2) Alternate registers

(3) Special purpose registers

Figure 3.3 shows the configuration of the internal register groups. The register groups, each being of a static RAM, consists of eighteen 8-bit registers and four 16-bit registers. The following describes the function of each register:

- (1) Main registers (A, F, B, C, D, E, H, L)

- (a) Accumulator (A)

The accumulator is an 8-bit register used for arithmetic and data transfer operations.

(b) Flag register (F) (see Fig. 3.2)

The flag register is an 8-bit register to hold the result of each arithmetic operation. Actually, the 6 of the 8 bits are set ("1")/reset ("0") according to the condition specified by an instruction.

| MSB |   |   |   |   |     |   | LSB |                 |

|-----|---|---|---|---|-----|---|-----|-----------------|

| 7   | 6 | 5 | 4 | 3 | 2   | 1 | 0   | (* = Undefined) |

| S   | Z | * | Н | * | P/V | N | С   |                 |

|     |   |   |   |   |     |   |     | 060489          |

Figure 3.2 Flag Register Configuration

The following 4 bits are directly available to the programmer for setting the jump, call and return instruction conditions:

Figure 3.3 Flag Register Configuration

#### • Sign flag (S)

When the result of an operation is negative, the S flag is set to "1". Actually, the content of bit 7 of accumulator is stored in this flag.

#### Zero flag (Z)

When all bits turn out to be "0" s after operation, the Z flag is set to "1" . Otherwise, it is set to "0".

With a block search instruction (CPI, CPIR, CPD or CPDR), the Z flag is set to "1" if the source data and the accumulator data match.

With a block I/O instruction (INI, IND, OUTI or OUTD), the Z flag is set to "1" if the content of the B register used as the byte counter is "0" at the end of comparison.

# • Parity/overflow flag (P/V)

This flag has two functions. One is the parity flag (P) that indicates the result of a logical operation (AND A, B etc.). The P flag is set to "1" if the parity is even as a result of the operation on signed values by two's complement. It is reset to "0" if the parity is odd. With a block search instruction (CPI, CPIR, CPD or CPDR) and a block transfer instruction (LDI or LDD), the P flag indicates the state of the byte counter (register pair B and C). It is set to "1" if the byte counter is not "0" and reset to "0" when the byte counter becomes "0" (at the end of comparison or data transfer). The content of the interrupt enable flip-flop (IFF) is saved to the P flag when the contents of the R register or I register are transferred to the accumulator.

The other use of the P/V flag is the overflow flag (V) that indicates whether an overflow has occurred or not as a result of an arithmetic operation. The V flag is set to "1" when the value in the accumulator gets out of a range of the maximum value +127 and the minimum value -128 and therefore cannot be correctly represented as a two's complement notation.

Whether the P/V flag operates as the P flag or V flag is determined by the type of the instruction executed.

# • Carry flag (C)

The C flag is set to "1" if a carry occurs from bit 7 of the accumulator or a borrow occurs as a result of an operation.

The following two flags are not available to the programmer for the test and set ("1")/reset ("0") purposes. They are internally used by the MPU for BCD arithmetic operations.

# • Half carry flag (H)

The H flag is used for holding the carry or borrow from the low-order 4 bits of a BCD operation result. When a DAA instruction (decimal adjust) is executed, the MPU automatically uses the H flag to adjust the result of a decimal addition or subtraction.

# Add/subtract flag (N)

In BCD operation, algorithm is different between addition and subtraction. The N flag indicates whether the executed operation is addition or subtraction.

For change of the flag state depending on the instruction, see 3.4 "TMPZ84C00A Instruction Set".

(c) General-purpose registers (B, C, D, E, H, L)

General-purpose registers consist of 8 bits each. They are used as 16-bit register pairs (BC, DE, HL) as well as independent 8-bit registers to supplement the accumulator. The B register and the register pair BC are used as counters when a block I/O, block transfer, or search instruction is executed. The register pair HL has various memory addressing features as compared with the register pairs BC and DE.

(2) Alternate registers (A', F', B', C', D', E', H', L')

The configuration of the alternate registers is exactly the same as that of the main registers. There is no instruction that handles the alternate registers directly. The data in the alternate registers are processed by moving them into the main registers by means of exchange instructions as shown below:

EX AF, AF'

$$(A \leftrightarrow A', F \leftrightarrow F')$$

EXX  $(B \leftrightarrow B', C \leftrightarrow C', D \leftrightarrow D', E \leftrightarrow E', H \leftrightarrow H', L \leftrightarrow L')$

When a high-speed interrupt response has been requested within the system, these instruction can be used to quickly move the contents of the accumulator, flag registers, and general-purpose registers into the corresponding registers. This eliminates the need for transferring the register contents to/from the external stack during execution of the interrupt handling routine, thereby shortening the interrupt servicing time greatly.

- (3) Special purpose registers (I, R, IX, IY, SP, PC)

- (a) Interrupt page address register (I)

The TMPZ84C00A provides two kinds of interrupts :maskable interrupt (INT) and non-maskable interrupt (NMI). The maskable interrupt provides three modes (0, 1, and 2) in which the interrupt is handled. These modes can be selected by instructions IM0, IM1, and IM2 respectively. In Mode 2, any memory location can be called indirectly depending on the interrupt. For this purpose, the I register stores the high-order 8 bits of the indirect address. The low-order 8 bits are supplied from the interrupting peripheral LSI. This scheme permits calling the interrupt handling routine from any memory location in an extremely short access time. For the details of interrupts, see [4] "Interrupt Capability".

# (b) Memory refresh register (R)

The R register is used as the memory refresh counter when the dynamic RAM is used for memory. This permits using of the dynamic memory in the same manner as the static memory. The Low-order 7 bits of this 8-bit register is automatically incremented for each instruction fetch. While the MPU decodes and executes the fetched instruction, the contents of the R register are synchronized with the refresh signal to place the low-order 8 bits on the address bus. This operation is all performed by the MPU and, therefore, dose not need a special processing by program. The MPU operation is not delayed by this operation. During refresh, the contents of the I register are placed on the high-order 8 bits of the address bus.

# (c) Index registers (IX, IY)

The two independent index registers IX and IY hold the 16-bit base address when used in the index addressing mode. In this addressing mode, the memory address obtained by adding the contents of an index register to the displacement value (for example, LD IX+40H) is specified. This mode is convenient for using data tables. Also these registers can be used separately for memory addressing and data retaining registers.

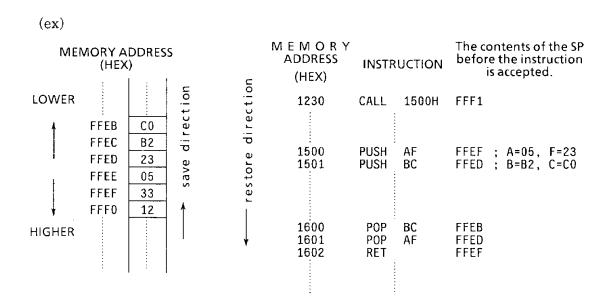

# (d) Stack pointer (SP)

The stack pointer is a 16-bit register to provide the start address information in the stack area in the external RAM. The content of the stack pointer is decremented at the execution of a CALL instruction or PUSH instruction or interrupt handling and is incremented at the execution of a return instruction or POP instruction. At the execution of a CALL instruction or interrupt handling, the current content of the program counter is saved into the stack. At the execution of a return instruction, the content is restored from the stack to the program counter. These operations are all performed by the MPU automatically. However, the other registers are not saved or restored automatically. For the storing of the contents of these registers, an exchange instruction (EX or EXX) for alternate register, a PUSH or a POP instructions must be used. When a PUSH instruction is executed, the contents of the specified register are saved into the stack. When a POP instruction is executed, the contents of the stack are moved to the specified register.

These data are restored on a last-in, first-out basis. Use of the stack permits processing of multiple-level interrupts, deep subroutine nestings, and various data manipulation very easily. The stack pointer is not initialized in the hardware approach. Therefore, it is required to allocate the stack area in RAM to specify initialization (at the highest address of the stack area) in the initial program.

The foregoing example shows the stack pointer and stack operations in which the instructions starting with the CALL at address 1230H and ending with the RET at address 1602H have been executed. However, it is assumed that there is no instruction or interrupt other than shown above that uses the stack during the execution. When the value the stack pointer before executing the CALL instruction at address 1230H indicates address FFF1H, address 1233H is stored at addresses FFF0H and FFEFH because the CALL instruction consists of 3 bytes, then the stack pointer is decremented. Similarly, the data are saved or restored sequentially according to the instructions. These stack and stack pointer operations are all performed automatically.

#### (e) Program counter (PC)

The program counter holds, in 16 bits, the memory address of the instruction to be executed next. The MPU fetches the instruction from the memory location indicated by the program counter. When the content of the program counter is put on the address bus, the program counter is incremented automatically. However, it is not incremented with a jump instruction, a call instruction, or interrupt processing. Instead, the specified new address is set on it. With a return instruction, the content restored from the stack is set on the program counter. These operations are all performed automatically and therefore, no care is required for programming.

#### [2] Halt Capability

When a HALT instruction has been executed, the MPU is put in the halt state. The halt capability can be used to halt the MPU against the external interrupts, thereby reducing the power dissipation. In the halt state the states of MPU's internal registers are retained. The halt state is cleared by reset or when an interrupt is accepted. For the details of halt operation, see [3] "Basic Timing".

#### (1) Halt operation

When a HALT instruction has been executed, the MPU sets the HALT signal to "0" to indicate that the MPU is going to be put in the halt state. Actually, the MPU in the halt state automatically continues executing NOP instructions if there is the system clock input. However, the program counter is not incremented. This keeps the refresh signal generated when the dynamic memory is used. During halt, the MPU's internal states are retained. By using TLCS-Z80's clock generator/controller (TMPZ84C60P or TMPZ84C61AP), the clock input control for these halt operations is realized easily.

#### (2) Releasing the halt state

The halt state is cleared by accepting an interrupt (the  $\overline{\text{INT}}$  or  $\overline{\text{NMI}}$  signal input) or by reset (the  $\overline{\text{RESET}}$  signal input). When an interrupt is accepted, the halt state is cleared and the interrupt handling routine is executed. However, a maskable interrupt (INT) cannot be accepted unless the interrupt enable flip-flop (IFF) is set.

Note that when the halt state is cleared by the RESET signal, the MPU is reset and the program counter is set to "0".

#### [3] RESET Signal

Holding the RESET pin at the low level ("0") under the following conditions, the MPU's internal states are reset:

- (1) The supply voltage level is within the operational voltage range.

- (2) System clock stabilization.

- (3) Holding the RESET signal at the low level ("0") for at least 3 full clock cycles. When the RESET signal goes high ("1"), the MPU starts executing instructions from address 0000H after at least 2T state dummy cycles.

When reset, the MPU performs the following processing:

#### (1) Program counter

0000H is set.

# (2) Interrupt

The interrupt enable flip-flop (IFF) is reset to "0" to disable the maskable interrupt. For the maskable interrupt processing, mode 0 is specified.

#### (3) Control output

All control outputs are made inactive ("1"). Therefore, the halt state is also cleared.

(4) Interrupt page address register (I register)

The content of the R register becomes 00H.

(5) Refresh register (R register)

The content of the R register becomes 00H.

The contents of the registers other than above and the external memory do not change.

Therefore, they must be initialized as required.

# [4] Interrupt Capability

The interrupt capability is used to suspend the execution of the current program and execute the processing of the requested peripheral LSI. Normally, this interrupt processing routine contains the data exchange and transfer of status and control information between the MPU and the peripheral LSI. When this routine has been completed, the MPU returns to the active state before the interrupt has been accepted.

The TMPZ84C00A provides the non-maskable interrupt (NMI) and maskable interrupt (INT) capabilities which are detected by the  $\overline{\text{NMI}}$  and  $\overline{\text{INT}}$  interrupt request signals, respectively. A non-maskable interrupt, when caused by a peripheral LSI, is accepted unconditionally. This interrupt is used to support critical functions such as the protection of the system from unpredictable happening including power failure. A maskable interrupt can be enabled or disabled by program. For example, if the timer is used and, therefore, an interrupt is not desired, the system can be programmed to disable the interrupt. Table 3.1 lists the processing by interrupt source.

#### (1) Interrupt enable/disable

A non-maskable interrupt cannot be disabled by program, while a maskable interrupt can be enabled or disabled by program. The MPU has the interrupt enable flip-flop (IFF). A maskable interrupt can be enabled or disabled by setting this flip-flop to "1" (set) or "0" (reset) through an EI instruction (enable) or a DI instruction (disable) in program. Actually, the IFF consists of two flip-flops IFF1 and IFF2. IFF1 is used to select between the enable and disable of a maskable interrupt. IFF2 holds the state of IFF1 before a maskable interrupt has been accepted. Both IFF1 and IFF2 are reset to "0" when any of the following conditions occurs, disabling an interrupt:

- MPU reset

- Execution of DI instruction

- Acceptance of maskable interrupt

Both IFF1 and IFF2 are set to "1" when the following condition occurs, enabling an interrupt:

#### Execution of EI instruction

Actually, the waiting maskable interrupt request is accepted after the execution of the instruction that follows the EI instruction.

This delay by one instruction is caused by accepting an interrupt after completion of the execution of a return instruction if the instruction following the EI instruction is a return instruction.

In the above operation, the contents of IFF1 and IFF2 are the same.

Table 3.1 Processing by Interrupt Source

| Interrupt Source                                                 | Priority | Programm | ed condition | Vector address                                                           | Interrupt<br>return<br>instruction |

|------------------------------------------------------------------|----------|----------|--------------|--------------------------------------------------------------------------|------------------------------------|

| Non-maskable interrupt (the falling edge of NMI)                 | 1        | No       | one          | Address 66H                                                              | RETN                               |

| Maskable interrupt (INT becomes "0" at instruction's last clock) | 2        | IFF = 1  | Mode 0       | Instruction from peripheral LSI. Normally, CALL or RST instruction.      | (Note)<br>RET I                    |

|                                                                  |          |          | Mode 1       | Address 38H. The address indicated by                                    |                                    |

| ·                                                                |          |          | Mode 2       | at the address specified by I register (high-order 8 bits) and data from |                                    |

|                                                                  |          |          |              | peripheral LSI (low-<br>order 8 bits, LSB = "0").                        |                                    |

060489

Note: Mode 0 applies when the instruction from peripheral LSI is CALL or RST instruction.

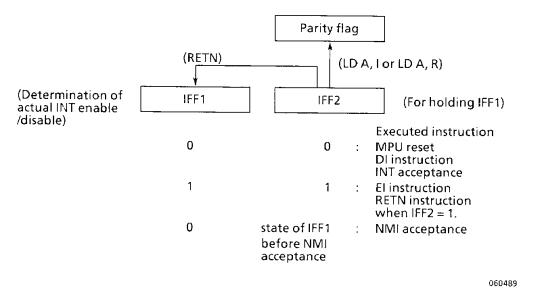

Figure 3.4 Interrupt Enable Flip-Flop (IFF)

When a non-maskable interrupt has been accepted, IFF1 is reset to "0" (interrupt disable) until an EI or RETN instruction is executed, so as to prevent from accepting the next interrupt. For this purpose, the state (interrupt enable/disable) of IFF1 immediately before non-maskable interrupt acceptance must be stored. This state is copied into IFF2 upon acceptance of a non-maskable interrupt. The content of IFF2 is copied into the parity flag at the execution of the following instructions, so that the copied data can be tested or stored:

- The load instruction (LD A, I) to load the contents of the I register into the accumulator.

- The load instruction (LD A, R) to load the contents of the R register into the accumulator.

When the return instruction (RETN) from the non-maskable interrupt is executed, the contents of the current IFF2 are copied back to IFF1. If an operation which changes the contents of IFF2 (due to the execution of EI or DI instruction, for example) has not been performed during interrupt handling, IFF1 automatically returns to the state immediately before the interrupt acceptance. Table 3.2 lists the states of IFF1 and IFF2 after execution of interrupt-related instructions.

Operation sequence IFF1 IFF2 Remarks NPU reset 0 0 1 NMI acceptance 0 Parity flag←IFF2 LD A, I IFF1←IFF2 1 **RETN** 1 Parity flag←IFF2 LDA.R INT acceptance 0 O RETI 1 1 EI 0 NMI acceptance 1 0 DΙ 0 RETN

Table 3.2 State of IFF1 and IFF2

Note: \*= no change

060489

#### (2) Interrupt processing

With a non-maskable interrupt, the internal NMI flip-flop is set to "1" on the falling edge of the interrupt signal,  $\overline{\text{NMI}}$ . The state of this flip-flop is sampled on the rising edge of the last clock of each instruction to accept an interrupt. A maskable interrupt is accepted if the interrupt signal  $\overline{\text{INT}}$  is low ("0") on the rising edge of the last clock of each instruction and the interrupt enable state (IFF=1 and  $\overline{\text{BUSREQ}}$  signal=inactive ("1")) is on. The following is the processing to be performed after a non-maskable interrupt and a maskable interrupt are accepted:

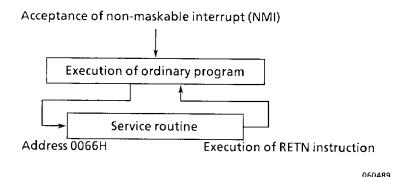

(a) Non-maskable interrupt (NMI)

When a non-maskable interrupt has been accepted, the MPU performs the following processing:

- 1 The internal NMI flip-flop is reset to "0".

- 2 IFF1 is reset to "0", disabling the maskable interrupt.

The contents of the IFF1 immediately before the interrupt acceptance are copied into the IFF2.

- 3 The contents of the current program counter are saved into the stack.

- 4 The instructions starting from non-maskable interrupt vector address 66H are executed.

A non-maskable interrupt processing program terminates after executing the RETN instruction. This return instruction performs the followings:

- The contents of the current IFF2 are copied into IFF1.

- 2 The contents of the program counter are restored from the stack.

Figure 3.5 Non-Maskable Interrupt Processing

(b) Maskable interrupt (INT)

When a maskable interrupt has been accepted, the MPU performs the following processings:

- Both IFF1 and IFF2 are reset to "0", disabling the maskable interrupts.

- 2 The contents of the current program counter are saved into the stack.

- A maskable interrupt is serviced in one of the three modes 0, 1 and 2. A mode is selected by executing the instruction IM0, IM1or IM2 before the interrupt is serviced. The instructions are executed starting from the vector address corresponding to the selected mode.

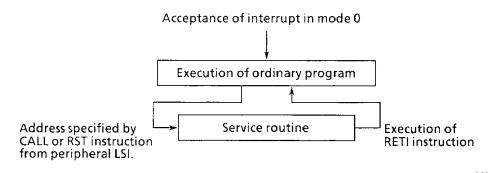

#### Mode 0

In mode 0, the interrupting peripheral LSI puts a restart instruction (RST) or a call instruction (CALL) on the data bus and the MPU executes the interrupt service routine according to that instruction. At reset, this mode is automatically set.

Figure 3.6 Interrupt Processing in Mode 0

060489

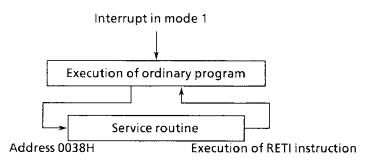

#### Mode 1

When an interrupt is accepted in mode 1, restart is performed from address 0038H. Therefore, the service routine for this interrupt is programmed from the address 0038H.

060489

Figure 3.7 Interrupt Processing in Mode 1

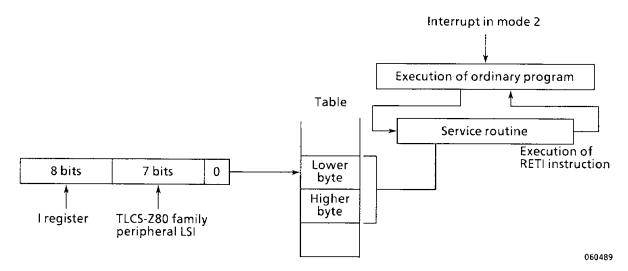

#### • Mode 2

The interrupt processing in mode 2 requires a 16-bit pointer consisting of the high-order 8 bits of the I register and the low-order 8 bits (with the LSB="0") of the data fetched from the TLCS-Z80 family peripheral LSI. Therefore, the necessary value must be loaded in the I register beforehand. This pointer is used to specify the memory address in the table. The contents of the specified address and the next address provide the start address of the service routine. Therefore, use of this mode requires the table of the service routine's start address (16 bits) to be set at appropriate location under software control. This location can be anywhere in memory.

The LSB of the table pointer is set to "0" because a 2-byte data is needed to specify the service routine start address in 16 bits and start that address from an even-number address. In the table, the start address begins with the low-order byte followed by the high-order byte as shown in Figure 3.8.

Figure 3.8 Interrupt Processing in Mode 2

Mode 2 is used in the daisy chain interrupt processing using TLCS-Z80 family LSI. TLCS-Z80 family peripheral LSIs all contain the interrupt priority controller in daisy chain structure. In this interrupt structure, the interrupt request signals are connected one after another and given priorities for processing when two or more maskable interrupt requests occur at a time. Only the interrupt vector from the peripheral LSI having the highest priority is put on the data bus. By receiving the interrupt vector in mode 2, the processing for that peripheral LSI can be performed. When an interrupt requested by a peripheral LSI having a priority higher than that of the current peripheral LSI during the execution of the interrupt processing routine, the higher priority interrupt can be enabled by the EI instruction to form an interrupt nesting.

The maskable interrupt processing program terminates by executing an RETI instruction. This return instruction performs the following processings:

- Restores the content of the program counter from the stack.

- Notifies the requesting peripheral LSI of the termination of interrupt processing.

#### 3.3 MPU STATUS TRANSITION DIAGRAM AND BASIC TIMING

The following describes the MPU status transition and the basic timing of each MPU operation.

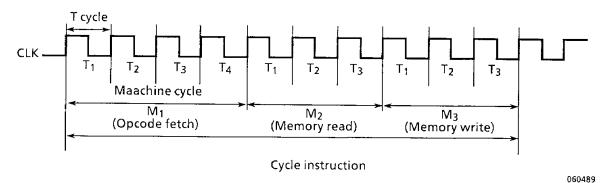

# [1] Instruction Cycle

Each TMPZ84C00A instruction is executed by combining the basic operations of memory read/write, input/output, bus request/acknowledge, and interrupt. These basic operations are performed synchronizing with the system clock (the CLK signal).

One clock period is called a state (T). The smallest unit of each basic operation is called a machine cycle (M). Each instruction consists of 1 to 6 machine cycles and each machine cycle consists of 3 to 6 clock states basically. However, the number of clock states in a machine cycle can be increased by the  $\overline{WAIT}$  signal described later on. Figure 3.9 shows an example of the basic timing of a 3-machine-cycle instruction.

The first machine cycle (M1) of each instruction is the cycle in which the Opcode of the instruction to be executed next is read (this is called the Opcode fetch cycle). The Opcode fetch cycle basically consists of 4 to 6 clock states. In the machine cycle that follows the Opcode fetch cycle, data is transferred between the MPU and the memory or peripheral LSIs. This operation basically consists of 3 to 5 clock states.

Figure 3.9 Example of MPU Basic Timing (3-Machine-Cycle Instruction)

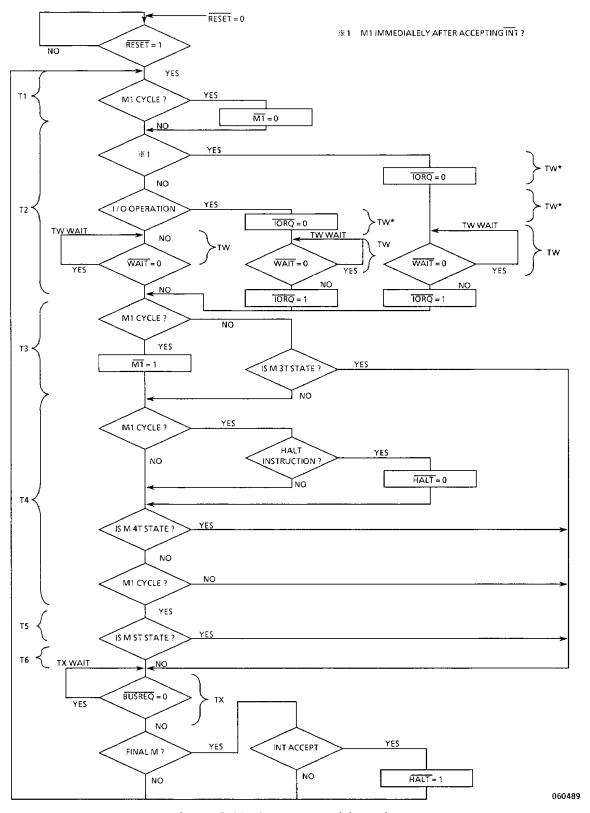

# [2] Status Transition Diagram

Figure 3.10 Status Transition Diagram

#### [3] Basic Timing

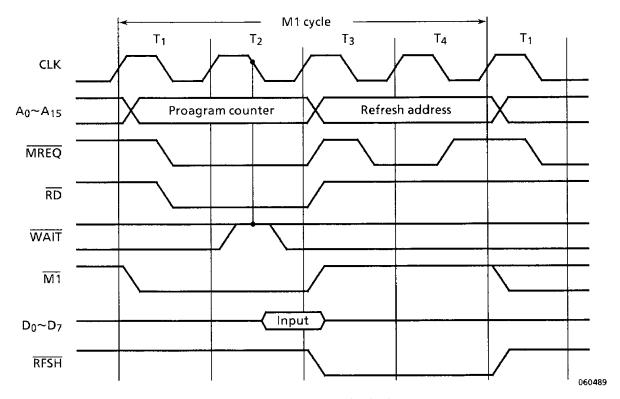

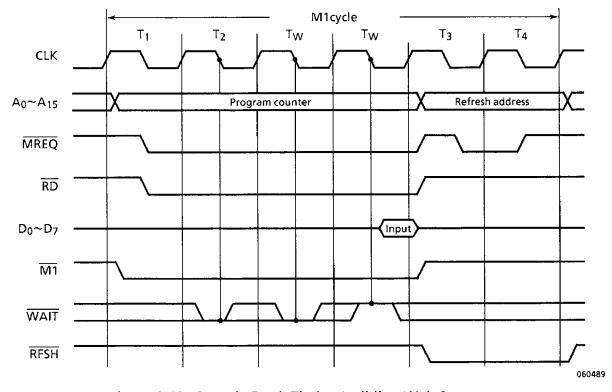

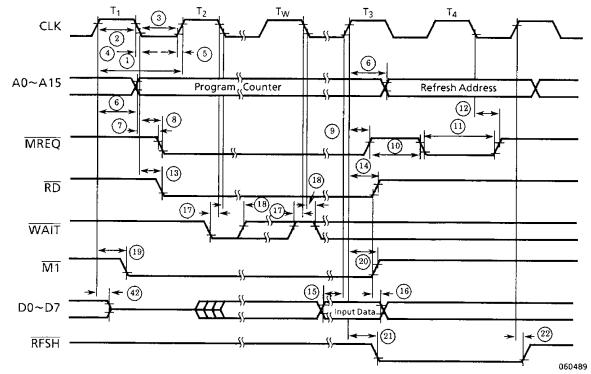

# (1) Opcode fetch cycle (M1)

In the Opcode fetch cycle, MPU fetches an Opcode in the machine-language codes in memory. This is also called the M1 cycle because it is the first machine cycle to execute each instruction.

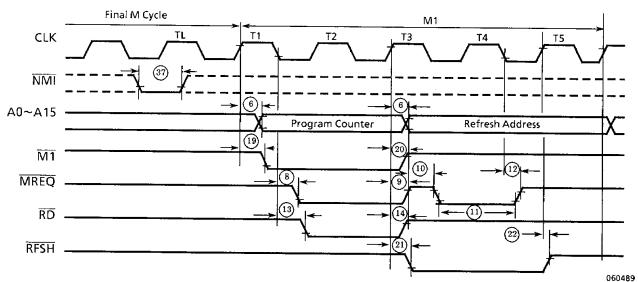

Figure 3.11 shows the basic timing of a basic Opcode fetch cycle.

In clock state T1, the content of the program counter is put on the address bus. The  $\overline{\text{M1}}$  signal goes "0", indicating to the MPU that this is the Opcode fetch cycle. At the same time,  $\overline{\text{MREQ}}$  and  $\overline{\text{RD}}$  signals go "0". When the  $\overline{\text{MREQ}}$  signal goes "0", the address signal has already been stabilized. Therefore, this signal can be used for the memory chip enable signal. The  $\overline{\text{RD}}$  signal indicates that the MPU is ready to accept the data from memory. By these signals, the MPU accesses memory to fetch the Opcode in the instruction register. The MPU samples the  $\overline{\text{WAIT}}$  signal on the falling edge of clock state T2. If the  $\overline{\text{WAIT}}$  signal is "0" on the falling edge of clock state T2 and the following wait state (TW), the next state becomes clock state TW. Figure 3.12 shows the delay state of the Opcode fetch cycle caused by the  $\overline{\text{WAIT}}$  signal.

The data (Opcode) on the data bus is fetched on the rising edge of clock state T3 then, the  $\overline{\text{MREQ}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{MI}}$  signals go "1". In clock state T3, a memory refresh address is put on the low-order 8 bits of the address bus and the  $\overline{\text{RFSH}}$  signal goes "0" and the  $\overline{\text{MREQ}}$  signal goes "0" again. This signal indicates that the memory refresh cycle is on. At this time, the contents of the I register are put on the high-order 8 bits of the address bus and the 8 bits of the R register are put on the low-order 8 bits of the address bus. By using the  $\overline{\text{RFSH}}$  and  $\overline{\text{MREQ}}$  signals, memory refresh is performed in clock state T3 and T4. However, the  $\overline{\text{RD}}$  signal remains "1" because the contents of the memory refresh address are not put on the data bus.

In clock state T4, the  $\overline{\text{MREQ}}$  signal returns to "1". The refresh address is kept output until the rising edge of the clock state T1 in the next machine cycle, keeping the  $\overline{\text{RFSH}}$  signal set to "0". The cycle delay state caused by setting the  $\overline{\text{WAIT}}$  signal to "0" is the same in the memory read/write, input/output, and maskable interrupt acknowledge cycles. The diagram of the cycle delay state caused by the  $\overline{\text{WAIT}}$  signal set to "0" is omitted in the following description.

Figure 3.11 Opcode Fetch Timing

Figure 3.12 Opcode Fetch Timing Incliding Wait State

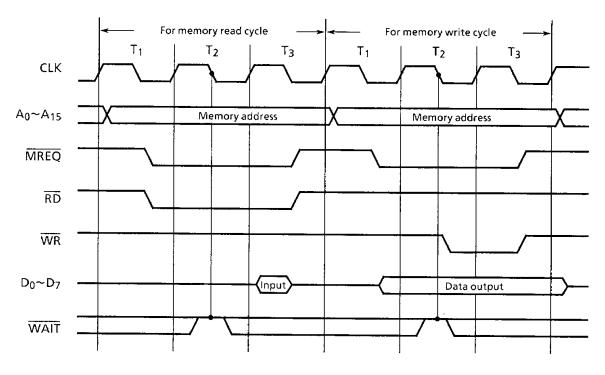

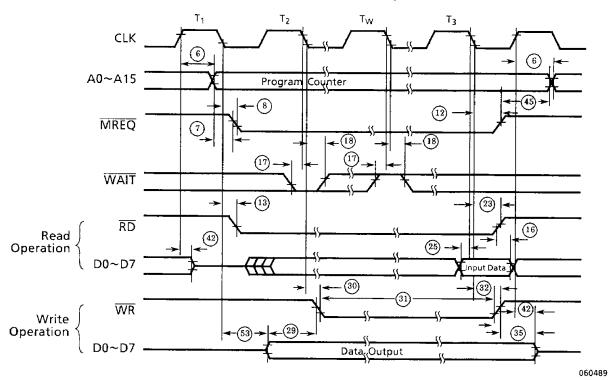

# (2) Memory read/write operations

Figure 3.13 shows the basic timing of memory read/write operations (except for the Opcode fetch cycle) in the same diagram for convenience.

In each operation, the memory address signal to read/write data on the address bus is output in clock clock state T1. The operation in which the WAIT signal is sampled in clock state T2 and the following TW state is the same as the Opcode fetch cycle.

In memory read, memory data is put on the data bus by the address,  $\overline{MREQ}$ , and  $\overline{RD}$  signals. The MPU reads this data.

In memory write, the memory address signal is put on the address bus then the  $\overline{MREQ}$  signal is set to "0" to put the write data onto the data bus. When the data bus has been stabilized, the  $\overline{WR}$  signal is output in clock state T2. The WR signal can be used as the memory write signal.

Figure 3.13 Memory Read/Write Cycle Timing

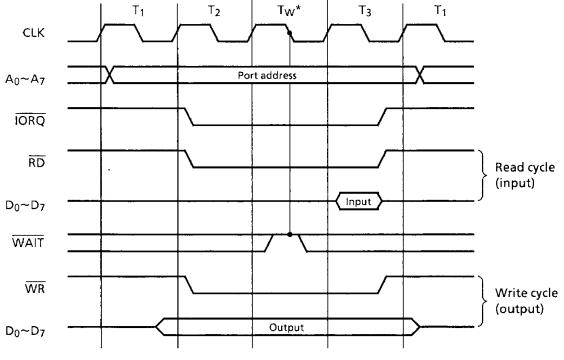

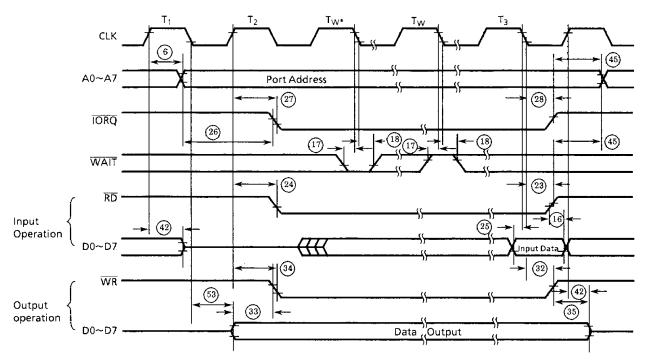

#### (3) Input/output operations

Figure 3.14 shows the basic timing of input/output operations. The feature of the I/O operation timing is that, regardless of the state of the  $\overline{WAIT}$  signal in clock state T2, the I/O cycle automatically goes in the wait state (TW\*) after clock T2. The  $\overline{WAIT}$  signal is sampled on the falling edge of TW\*. If the  $\overline{WAIT}$  signal is "0" on the falling edges of TW\* and the following clock state, the I/O operation enters into clock state TW\*. Clock state TW\* is inserted because the  $\overline{IORQ}$  signal goes "0" in clock state T2, so that it is too late to sample the  $\overline{WAIT}$  signal after decoding the I/O port address. In each of input and output operations, the I/O port address is put on the low-order 8 bits of the address bus in clock state T1. On the high-order 8 bits, the contents of the accumulator or B register are output. In clock state T2, the  $\overline{IORQ}$  signal goes "0" instead of the  $\overline{MREQ}$  signal. The  $\overline{IORQ}$  signal can be used as the chip enable signal for a peripheral LSI.

In an input operation, the contents of the input port are read onto the data bus by the address,  $\overline{IORQ}$ , or  $\overline{RD}$  signals. The MPU reads this data.

In an output operation, the output port address and the output data are respectively put on the address bus and data bus in clock state Tl, then the  $\overline{IORQ}$  and  $\overline{WR}$  signals go "0" in clock state T2. The  $\overline{WR}$  signal can be used as the output port write signal.

Figure 3.14 I/O Operating Timing

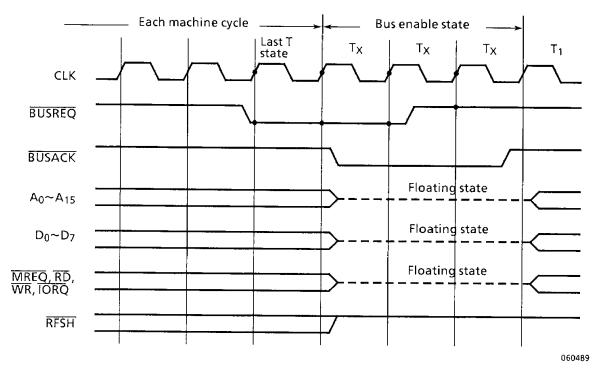

# (4) Bus request and bus acknowledge operations

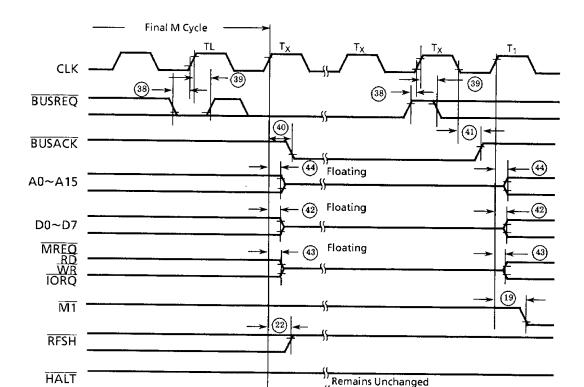

Figure 3.15 shows the basic timing of bus request and bus acknowledge operations.

The address bus (A0 through A15), data bus (D0 through D7),  $\overline{MREQ}$ ,  $\overline{IORQ}$ ,  $\overline{RD}$ , and  $\overline{WR}$  signals controlled by the MPU can be put in the high-impedance state (floating) to electrically disconnect them from the MPU. This operation, after sampling the  $\overline{BUSREQ}$  signal on the rising edge of the last clock of each machine cycle, starts on the rising edge of the next clock if this signal is found "0".

Subsequently, these buses are controlled by external peripheral LSIs. For example, data can be directly transferred between memory and these peripheral LSIs. This state is cleared if the BUSREQ signal is found "1" after sampling it on the rising edge of each subsequent clock state (TX), and enters into the next machine cycle. During the floating state, the BUSACK signal goes "0" to indicate it to the peripheral LSIs.

In this state, however, no memory refresh is performed and, therefore, the  $\overline{\text{RFSH}}$  signal is set to "1". Hence, to maintain this state for a long time with a system using dynamic memory, memory refresh must be performed by the external controller.

Note that, in the floating state, neither maskable interrupt (INT) nor non-maskable interrupt (NMI) can be accepted.

Figure 3.15 Bus Request and Bus Acknowledge Timing

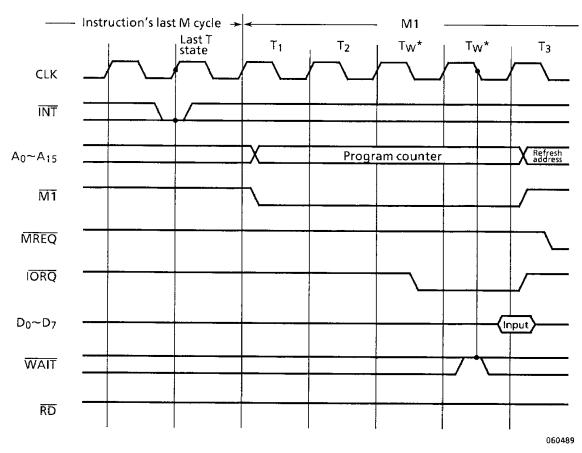

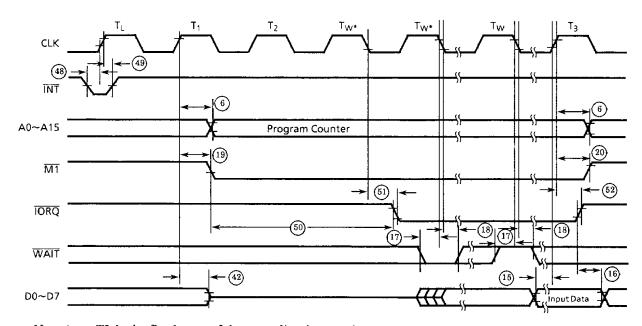

# (5) Maskable interrupt acknowledge operation

Figure 3.16 shows the basic timing of the maskable interrupt acknowledge.

The MPU samples the maskable interrupt request signal ( $\overline{INT}$ ) on the rising edge of the last clock of each instruction execution. If the  $\overline{INT}$  signal is found "0", a maskable interrupt is accepted except in the following cases:

- The interrupt enable flip-flop is reset to "0".

- The BUSREQ signal is "0".

When a maskable interrupt has been accepted, a special Opcode fetch cycle is generated. In this cycle, 2 clock states of wait state (TW\*) is automatically inserted after the clock state T2. The  $\overline{WAIT}$  signal is sampled on the falling edges of the second clock state TW\* and the following clock state TW and, if the  $\overline{WAIT}$  signal is found "0", the instruction cycle enters in the next clock state TW. In this Opcode fetch cycle, the  $\overline{IORQ}$  signal goes "0" in the first TW\* state instead of the  $\overline{MREQ}$  signal while, in a normal Opcode fetch cycle, the  $\overline{MREQ}$  signal goes "0" in clock state T1. This indicates to the maskable interrupt requesting LSI that the 8-bit interrupt vector can be put on the data bus. The MPU reads this data to perform interrupt processing. Therefore, the contents of the program counter put on the address bus are not used. Unlike an ordinary I/O operation, the  $\overline{RD}$  signal does not go "0".

In clock state T3, the memory refresh address signal is put on the address bus for memory refresh like normal Opcode fetch cycle and the  $\overline{RFSH}$  signal goes "0". In the subsequent machine cycles (M2 and M3), the contents of the current program counter are saved into the stack. In machine cycles M4 and M5, the contents of the I register (the high-order 8 bits) and the contents of the address indicated by the address of the vector (the low-order 8 bits) from the peripheral LSI are fetched in the program counter.

Figure 3.16 Maskable Interrupt Acknowledge Timing

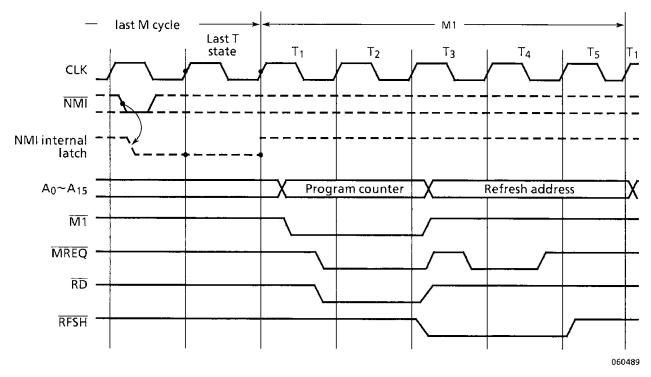

# (6) Non-maskable interrupt acknowledge operation

Figure 3.17 shows the basic timing of non-maskable interrupt acknowledge.

When the non-maskable interrupt request signal ( $\overline{NMI}$ ) goes low, the internal non-maskable flip-flop is set to "1". The  $\overline{NMI}$  signal is detected in any timing of each instruction. However, the internal NMI flip-flop is sampled on the rising edge of the last clock of each instruction. Therefore, the  $\overline{NMI}$  signal should go low by the last clock state of an instruction.

The Opcode fetch cycle for non-maskable interrupt request acknowledge is generally the same as the ordinary Opcode fetch cycle. However, the Opcode on the data bus at the time is ignored. The contents of the current program counter are saved into the stack in the subsequent machine cycles (M2 and M3). In the following machine cycle, the operation jumps to address 0066H, the non-maskable interrupt vector address. The machine cycles after these depend on the contents of the fetched Opcode.

Figure 3.17 Non-Maaskable Inpterrupt Acknowledge Timing

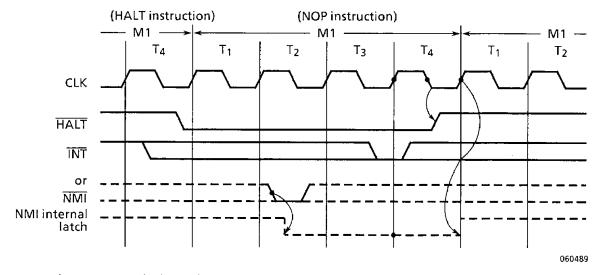

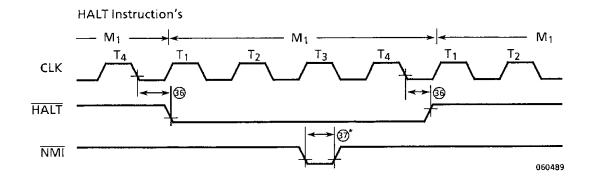

# (7) Halt operation

When a HALT instruction is fetched in the Opcode fetch cycle, the MPU sets the HALT signal to "0" synchronized with the falling edge of clock state T4 to indicate it to the peripheral LSI and stops operating. If the system clock is kept supplied in the halt state, the MPU continues executing NOP instructions. This is done to output refresh signals when the dynamic memory is used. The NOP instruction execution cycle is the same as the ordinary Opcode fetch cycle except the data on the data bus are ignored.

The halt state is cleared when an interrupt is accepted or the RESET signal is set to "0" to reset the MPU. Figure 3.18 shows the halt state clear operation by interrupt acknowledge. An interrupt is sampled on the rising edge of the last clock (clock state T4) of the NOP instruction. A maskable interrupt can be accepted when the INT signal is "0". A non-maskable interrupt is accepted when the internal NMI flip-flop which is set on the falling edge of the NMI signal is set at "1". However, it is required that the interrupt enable flip-flop is set to "1" for a maskable interrupt to be accepted. The interrupt processing for the accepted interrupt starts from the next cycle.

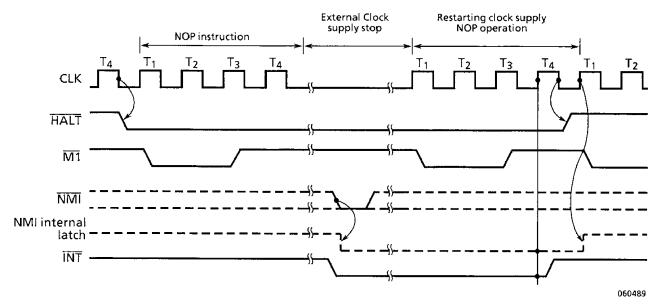

However, when the supply of the system clock has been stopped by the power down operation, it is required to restart the supply of the system clock and input the  $\overline{\text{INT}}$  signal until the execution of one instruction is completed or the  $\overline{\text{RESET}}$  signal until 3 clocks are input. Figure 3.19 shows the timing of clearing the halt state caused by power down. By using TLCS-Z80's clock generator/controller (TMPZ84C60P or TMPZ84C61AP), above-stated operation is realized easily.

For the reset operation, see (8) "Reset operation". Note that the INT and NMI signals are shown on the same diagram in Figures 3.18 and 3.19 for convenience.

Figure 3.18 Timing of Clearing Halt State Caused by Interrupt Acknowledge

Figure 3.19 Timing of Clearing Halt State Caused By Power Down

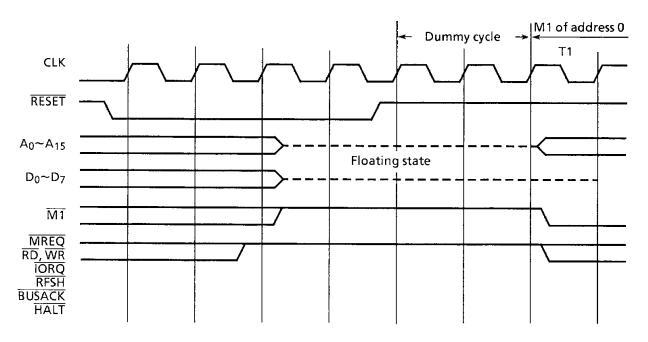

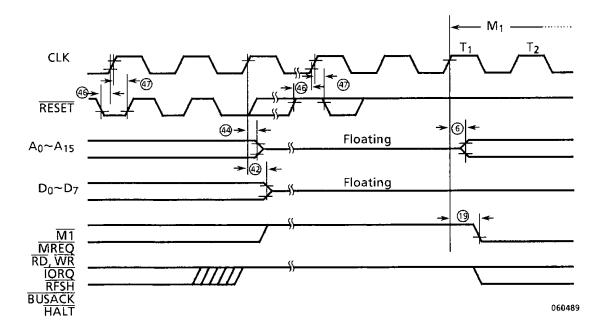

#### (8) Reset operation

Figure 3.20 shows the basic timing of reset operation.

To reset the MPU, the  $\overline{RESET}$  signal must be kept at "0" for at least 3 clocks. When the  $\overline{RESET}$  signal goes "1", instruction execution starts from address 0000H after a dummy cycle of at least 2 clock states.

Figure 3.20 Reset Timing

#### 3.4 TMPZ84C00A INSTRUCTION SET

This subsection lists the TMPZ84C00A instruction codes and their functions. The table below lists the symbols and abbreviations used to describe the instruction set. The symbols which require special attention are described in the locations in which they appear.

#### • Symbols (1/2)

| Classification | Symbol         | Meaning                                       |  |  |  |  |  |  |  |  |

|----------------|----------------|-----------------------------------------------|--|--|--|--|--|--|--|--|

| Register       | r, g           | Register B, C, D, E, H, L, A,                 |  |  |  |  |  |  |  |  |

|                | t              | Register pair BC, DE, HL                      |  |  |  |  |  |  |  |  |

|                |                | Stack pointer SP                              |  |  |  |  |  |  |  |  |

|                | q              | Register pair BC, DE, HL, AF                  |  |  |  |  |  |  |  |  |

|                | р              | Register pair BC, DE                          |  |  |  |  |  |  |  |  |

|                |                | Index register IX                             |  |  |  |  |  |  |  |  |

|                |                | Stack pointer SP                              |  |  |  |  |  |  |  |  |

|                | s              | Register pair BC, DE                          |  |  |  |  |  |  |  |  |

|                |                | Index register IY                             |  |  |  |  |  |  |  |  |

|                |                | Stack pointer SP                              |  |  |  |  |  |  |  |  |

|                | t <sub>H</sub> | Higher register of register pair              |  |  |  |  |  |  |  |  |

|                |                | (B, D, H)                                     |  |  |  |  |  |  |  |  |

|                |                | Higher 8 bits of stack pointer (SP)           |  |  |  |  |  |  |  |  |

|                | qн             | Higher register of register pair              |  |  |  |  |  |  |  |  |

|                |                | (B, D, H, A)                                  |  |  |  |  |  |  |  |  |

|                | IXH            | Higher 8 bits of index register IX            |  |  |  |  |  |  |  |  |

|                | IYH            | Higher 8 bits of index register IY            |  |  |  |  |  |  |  |  |

|                | PCH            | Higher 8 bits of program counter (PC)         |  |  |  |  |  |  |  |  |

|                | tլ             | Lower register of register pair               |  |  |  |  |  |  |  |  |

|                |                | (C, E, L)                                     |  |  |  |  |  |  |  |  |

|                |                | Lower 8 bits of stack pointer (SP)            |  |  |  |  |  |  |  |  |

|                | qL             | Lower register of register pair               |  |  |  |  |  |  |  |  |

|                |                | (C, E, L, F)                                  |  |  |  |  |  |  |  |  |

|                | IXL            | Lower 8 bits of index register IX             |  |  |  |  |  |  |  |  |

|                | IYL            | Lower 8 bits of index register IY             |  |  |  |  |  |  |  |  |

|                | PCL            | Lower 8 bits of program counter (PC)          |  |  |  |  |  |  |  |  |

|                | rb             | Bit b (0-7) of register (B, C, D, E, H, L, A) |  |  |  |  |  |  |  |  |

# • Symbols (2/2)

| Classification     | Symbol                | Meaning                                                                                                                                       |  |  |  |  |  |  |  |  |

|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Memory             | mn                    | Memory address represented in 16 bits. m indicates higher 8 bits and n, lower 8 bits.                                                         |  |  |  |  |  |  |  |  |

|                    | (HL) <sub>b</sub>     | Bit b (0-7) of the contents of the memory address indicated by register pair HL.                                                              |  |  |  |  |  |  |  |  |

|                    | (IX + d) <sub>b</sub> | Bit b (0-7) of the contents of the memory address indicated by the value obtained by adding 8-bit data d to the content of index register IX. |  |  |  |  |  |  |  |  |

|                    | (IY + d) <sub>b</sub> | Bit b (0-7) of the contents of the memory address indicated by the value obtained by adding 8-bit data d to the content of index register IY. |  |  |  |  |  |  |  |  |

| Flag change symbol | 0                     | Reset to "0" by operation.                                                                                                                    |  |  |  |  |  |  |  |  |

|                    | 1                     | Set to "1" by operation.                                                                                                                      |  |  |  |  |  |  |  |  |

|                    | -                     | No change                                                                                                                                     |  |  |  |  |  |  |  |  |

|                    | *                     | Affected by operation                                                                                                                         |  |  |  |  |  |  |  |  |

|                    | X                     | Undefined                                                                                                                                     |  |  |  |  |  |  |  |  |

|                    | Р                     | Handled as parity flag.                                                                                                                       |  |  |  |  |  |  |  |  |

|                    |                       | P = 0: odd parity                                                                                                                             |  |  |  |  |  |  |  |  |

|                    |                       | P = 1: even parity                                                                                                                            |  |  |  |  |  |  |  |  |

|                    | V                     | Handled as overflow flag.                                                                                                                     |  |  |  |  |  |  |  |  |

|                    |                       | V = 0: No overflow                                                                                                                            |  |  |  |  |  |  |  |  |

|                    |                       | V = 1: Overflow                                                                                                                               |  |  |  |  |  |  |  |  |

| Operator           | <b>←</b>              | Transfer                                                                                                                                      |  |  |  |  |  |  |  |  |

|                    | ↔                     | Exchange                                                                                                                                      |  |  |  |  |  |  |  |  |

|                    | +                     | Add                                                                                                                                           |  |  |  |  |  |  |  |  |

|                    | -                     | Subtract                                                                                                                                      |  |  |  |  |  |  |  |  |

|                    | ^                     | Logical and between bits.                                                                                                                     |  |  |  |  |  |  |  |  |

|                    | V                     | Logical or between bits.                                                                                                                      |  |  |  |  |  |  |  |  |

|                    | ⊕                     | Exclusive or between bits                                                                                                                     |  |  |  |  |  |  |  |  |

| Others             | IFF                   | Interrupt enable flip-flop                                                                                                                    |  |  |  |  |  |  |  |  |

|                    | CY                    | Carry flag                                                                                                                                    |  |  |  |  |  |  |  |  |

|                    | Z                     | Zero flag                                                                                                                                     |  |  |  |  |  |  |  |  |

# TMPZ84C00A Instruction Set (1/9)

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ITEMI<br>CLASSI | Assembler    | Object                                  |                                         |                                         |          |          |           | F | ag |           |                  | *** | No.<br>Of | No.<br>OF                               |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------|----------|-----------|---|----|-----------|------------------|-----|-----------|-----------------------------------------|----------------|

| LO r, n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1               | mnemonic     | 76 543 210                              | Hex                                     | Function                                | s        | Z        |           | Н |    | P/V       | N                | С   |           |                                         |                |

| LD r, (IX+d)   Oi rr ii0   A6+rx8   r-(IX+d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              | *                                       | · · · · · · · · · · · · · · · · · · ·   | ······································  |          |          |           |   |    | <u></u>   | ļ <del>.</del> . |     | 1         |                                         | <br>           |

| LU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | [ [ [ ]      | 1                                       |                                         | 1711                                    | _        | -        | X         | - | Х  | -         | -                | -   | 2         | 7                                       | 1 1 1 1 1 1 1  |

| Do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |              |                                         | <b>4</b>                                | • • • • • • • • • • • • • • • • • • • • |          |          |           |   |    | <u> </u>  | <u></u>          | -   | 2         | 7                                       | 1 <del></del>  |

| LD r, (1Y+d)   11 111 101   5D   7+(1Y+d)   X - X 5   19   H   L   L   L   L   L   L   L   L   L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | LU r,(1X+a)  | [                                       |                                         | r+{IX+d}                                | -        | -        | X         | - | Χ  | -         | -                | -   | 5         | 19                                      | 1 1 1 1 1 1 1  |