# Matched Monolithic Quad Transistor

**MAT04**

#### **FEATURES**

Low Offset Voltage: 200  $\mu$ V max High Current Gain: 400 min

**Excellent Current Gain Match: 2% max**

Low Noise Voltage at 100 Hz, 1 mA: 2.5 nV/√Hz max

Excellent Log Conformance: rBE = 0.6  $\Omega$  max Matching Guaranteed for All Transistors

Available in Die Form

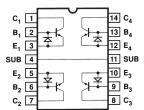

#### PIN CONNECTIONS

14-Lead Cerdip (Y Suffix) 14-Lead Plastic DIP (P Suffix) 14-Lead SO (S Suffix)

#### PRODUCT DESCRIPTION

The MAT04 is a quad monolithic NPN transistor that offers excellent parametric matching for precision amplifier and nonlinear circuit applications. Performance characteristics of the MAT04 include high gain (400 minimum) over a wide range of collector current, low noise (2.5 nV/ $\sqrt{\rm Hz}$  maximum at 100 Hz, I<sub>C</sub> = 1 mA) and excellent logarithmic conformance. The MAT04 also features a low offset voltage of 200  $\mu$ V and tight current gain matching, to within 2%. Each transistor of the MAT04 is individually tested to data sheet specifications. For matching parameters (offset voltage, input offset current, and gain match), each of the dual transistor combinations are

verified to meet stated limits. Device performance is guaranteed at 25°C and over the industrial and military temperature ranges.

The long-term stability of matching parameters is guaranteed by the protection diodes across the base-emitter junction of each transistor. These diodes prevent degradation of beta and matching characteristics due to reverse bias base-emitter current.

The superior logarithmic conformance and accurate matching characteristics of the MAT04 makes it an excellent choice for use in log and antilog circuits. The MAT04 is an ideal choice in applications where low noise and high gain are required.

REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# **MATO4—SPECIFICATIONS**

**ELECTRICAL CHARACTERISTICS** (@  $T_A = 25^{\circ}$ C unless otherwise noted. Each transistor is individually tested. For matching parameters ( $V_{0S}$ ,  $I_{0S}$ ,  $AI_{FE}$ ) each dual transistor combination is verified to meet stated limits. All tests made at endpoints unless otherwise noted.)

|                                           |                               |                                                           | MAT04E |      | MAT04F |     |      |      |                    |

|-------------------------------------------|-------------------------------|-----------------------------------------------------------|--------|------|--------|-----|------|------|--------------------|

| Parameter                                 | Symbol                        | Conditions                                                | Min    | Typ  | Max    | Min | Typ  | Max  | Unit               |

| Current Gain                              | $h_{\mathrm{FE}}$             | $10  \mu\text{A} \le I_{\text{C}} \le 1  \text{mA}$       |        |      |        |     |      |      |                    |

|                                           | 12                            | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^1$ | 400    | 800  |        | 300 | 600  |      |                    |

| Current Gain Match                        | $\Delta h_{ m FE}$            | $I_{\rm C} = 100  \mu A$                                  |        |      |        |     |      |      |                    |

|                                           |                               | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^2$ |        | 0.5  | 2      |     | 1    | 4    | %                  |

| Offset Voltage                            | Vos                           | $10  \mu A \leq I_C \leq 1  mA$                           |        |      |        |     |      |      |                    |

|                                           |                               | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^3$ |        | 50   | 200    |     | 100  | 400  | μV                 |

| Offset Voltage Change vs.                 | $\Delta V_{OS}/\Delta I_{C}$  | $10 \mu A \le I_C \le 1 mA$                               |        |      |        |     |      |      |                    |

| Collector Current                         |                               | $V_{CB} = 0 V^3$                                          |        | 5    | 25     |     | 10   | 50   | μV                 |

| Offset Voltage Change vs. V <sub>CB</sub> | $\Delta V_{OS}/\Delta V_{CB}$ | $10 \mu A \le I_C \le 1 mA$                               |        |      |        |     |      |      |                    |

|                                           |                               | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^3$ |        | 50   | 100    |     | 100  | 200  | μV                 |

| Bulk Emitter Resistance                   | $r_{\mathrm{BE}}$             | $10 \mu A \le I_{C} \le 1 mA$                             |        |      |        |     |      |      |                    |

|                                           |                               | $V_{CB} = 0 V^4$                                          |        | 0.4  | 0.6    |     | 0.4  | 0.6  | Ω                  |

| Input Bias Current                        | I <sub>B</sub>                | $I_{\rm C} = 100  \mu A$                                  |        |      |        |     |      |      |                    |

|                                           |                               | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}$   |        | 125  | 250    |     | 165  | 330  | nA                 |

| Input Offset Current                      | I <sub>OS</sub>               | $I_C = 100 \mu\text{A};  V_{CB} = 0  \text{V}$            |        | 0.6  | 5      |     | 2    | 13   | nA                 |

| Breakdown Voltage                         | BV <sub>CEO</sub>             | $I_C = 10 \mu\text{A}$                                    | 40     |      |        | 40  |      |      | V                  |

| Collector Saturation Voltage              | V <sub>CE(SAT)</sub>          | $I_B = 100  \mu A; I_C = 1  mA$                           |        | 0.03 | 0.06   |     | 0.03 | 0.06 | V.                 |

| Collector-Base Leakage Current            | $I_{CBO}$                     | $V_{CB} = 40 \text{ V}$                                   |        | 5    | 2      |     | 5    |      | pA                 |

| Noise Voltage Density                     | e <sub>n</sub>                | $V_{CB} = 0 \text{ V}; f_{O} = 10 \text{ Hz}$             |        | 2    | 3      |     | 2    | 4    | nV/√ <del>Hz</del> |

|                                           |                               | $I_C = 1 \text{ mA}; f_O = 100 \text{ Hz}$                |        | 1.8  | 2.5    |     | 1.8  | 3    | $nV/\sqrt{Hz}$     |

| O: P 1:11 P 1                             |                               | $f_0 = 1 \text{ kHz}^5$                                   |        | 1.8  | 2.5    |     | 1.8  | 3    | nV/√ <del>Hz</del> |

| Gain Bandwidth Product                    | f <sub>T</sub>                | $I_C = 1 \text{ mA}; V_{CE} = 10 \text{ V}$               |        | 300  |        |     | 300  |      | MHz                |

| Output Capacitance                        | C <sub>OBO</sub>              | $V_{CB} = 15 \text{ V}; I_E = 0$                          |        | 10   |        |     | 10   |      | T                  |

| Imput Compoitones                         |                               | f = 1  MHz                                                |        | 10   |        |     | 10   |      | pF                 |

| Input Capacitance                         | $C_{EBO}$                     | $V_{BE} = 0 \text{ V}; I_{C} = 0$                         |        | 40   |        |     | 40   |      | -F                 |

|                                           |                               | f = 1 MHz                                                 |        | 40   |        |     | 40   |      | pF                 |

#### NOTES

Specifications subject to change without notice.

-2- REV. D

$<sup>^{1}\</sup>text{Current}$  gain measured at  $I_{C}$  = 10  $\mu\text{A},\,100~\mu\text{A}$  and 1 mA.

$<sup>^2</sup>$ Current gain match is defined as:  $\Delta h_{FE} = rac{100(\Delta I_B)(h_{FE}^{~MIN})}{I_C}$

$<sup>^3</sup>$ Measured at  $I_C$  = 10  $\mu$ A and guaranteed by design over the specified range of  $I_C$ .

<sup>&</sup>lt;sup>4</sup>Guaranteed by design.

<sup>&</sup>lt;sup>5</sup>Sample tested.

**ELECTRICAL CHARACTERISTICS** (at  $-25^{\circ}C \le T_A \pm 85^{\circ}C$  for MAT04E,  $-40^{\circ}C \le T_A \pm 85^{\circ}C$  for MAT04F, unless otherwise noted. Each transistor is individually tested. For matching parameters ( $V_{0S}$ ,  $I_{0S}$ ) each dual transistor combination is verified to meet stated limits. All tests made at endpoints unless otherwise noted.)

|                      |                   |                                                           | MAT04E |     | MAT04F |     |     |     |       |

|----------------------|-------------------|-----------------------------------------------------------|--------|-----|--------|-----|-----|-----|-------|

| Parameter            | Symbol            | Conditions                                                | Min    | Typ | Max    | Min | Typ | Max | Unit  |

| Current Gain         | $h_{ m FE}$       | $10 \mu A \le I_C \le 1 mA$                               |        |     |        |     |     |     |       |

|                      |                   | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^1$ | 225    | 625 |        | 200 | 500 |     |       |

| Offset Voltage       | $V_{OS}$          | $10  \mu\text{A} \le I_{\text{C}} \le 1  \text{mA}$       |        |     |        |     |     |     |       |

|                      |                   | $0 \text{ V} \le \text{V}_{\text{CB}} \le 30 \text{ V}^2$ |        | 60  | 260    |     | 120 | 520 | μV    |

| Average Offset       | TCVos             | $I_{\rm C} = 100  \mu A$                                  |        |     |        |     |     |     | ,     |

| Voltage Drift        |                   | $V_{CB} = 0 V^3$                                          |        | 0.2 | 1      |     | 0.4 | 2   | μV/°C |

| Input Bias Current   | $I_{\mathrm{B}}$  | $I_{\rm C} = 100  \mu A$                                  |        |     |        |     |     |     |       |

| _                    |                   | $0 \text{ V} \leq \text{V}_{\text{CB}} \leq 30 \text{ V}$ |        | 160 | 445    |     | 200 | 500 | nA    |

| Input Offset Current | I <sub>OS</sub>   | $I_{\rm C} = 100 \; \mu A$                                |        |     |        |     |     |     |       |

|                      |                   | $V_{CB} = 0 \text{ V}$                                    |        | 4   | 20     |     | 8   | 40  | nA    |

| Average Offset       | TCI <sub>OS</sub> | $I_{\rm C} = 100  \mu A$                                  |        |     |        |     |     |     |       |

| Current Drift        |                   | $V_{CB} = 0 \text{ V}$                                    |        | 50  |        |     | 100 |     | pA/°C |

| Breakdown Voltage    | $BV_{CEO}$        | $I_{\rm C} = 10 \; \mu A$                                 | 40     |     |        | 40  |     |     | V     |

| Collector-Base       | $I_{CBO}$         | $V_{CB} = 40 \text{ V}$                                   |        |     |        |     |     |     |       |

| Leakage Current      |                   |                                                           |        | 0.5 |        |     | 0.5 |     | nA    |

| Collector-Emitter    | I <sub>CES</sub>  | $V_{CE} = 40 \text{ V}$                                   |        |     |        |     |     |     |       |

| Leakage Current      |                   |                                                           |        | 5   |        |     | 5   |     | nA    |

| Collector-Substrate  | $I_{CS}$          | $V_{CS} = 40 \text{ V}$                                   |        |     |        |     |     |     |       |

| Leakage Current      |                   |                                                           |        | 0.7 |        |     | 0.7 |     | nA    |

REV. D -3-

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |

|-------------------------------------------------------|

| Collector-Collector Voltage (BV <sub>CC</sub> ) 40 V  |

| Emitter-Emitter Voltage (BV <sub>EE</sub> ) 40 V      |

| Collector Current                                     |

| Emitter Current                                       |

| Substrate (Pin-4 to Pin-11) Current 30 mA             |

| Operating Temperature Range                           |

| MAT04EY –25°C to +85°C                                |

| MAT04FY, FP, FS40°C to +85°C                          |

| Storage Temperature                                   |

| Y Package65°C to +150°C                               |

| P Package65°C to +125°C                               |

| Lead Temperature (Soldering, 60 sec)+300°C            |

| Package Type                          | $\theta_{\mathrm{JA}}^{2}$ | $\theta_{ m JC}$ | Units        |

|---------------------------------------|----------------------------|------------------|--------------|

| 14-Lead Cerdip<br>14-Lead Plastic DIP | 108<br>83                  | 16<br>39         | °C/W<br>°C/W |

| 14-Lead SO                            | 120                        | 36               | °C/W         |

#### NOTES

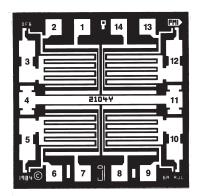

#### **DICE CHARACTERISTICS**

- 1. Q1 COLLECTOR

- 2. Q1 BASE

- 3. Q1 EMITTER

- 4. SUBSTRATE

- 5. Q2 EMITTER

- 6. Q2 BASE

- 7. Q2 COLLECTOR

- 8. Q3 COLLECTOR

- 9. Q3 BASE

- 10. Q3 EMITTER

- 11. SUBSTRATE

- 12. Q4 EMITTER

- 13. Q4 BASE

- 14. Q4 COLLECTOR

Die Size  $0.060 \times 0.060$  Inch, 3600 Sq. mm  $(1.52 \times 1.52$  mm, 2.31 sq. mm)

#### **ORDERING GUIDE**

| Model    | $T_A = 25^{\circ}C$ | Temperature    | Package     | Package |

|----------|---------------------|----------------|-------------|---------|

|          | $V_{OS}$ max        | Range          | Description | Option  |

| MAT04EY* | 200 μV              | -25°C to +85°C | Cerdip      | Q-14    |

| MAT04FY* | 400 μV              | -40°C to +85°C | Cerdip      | Q-14    |

| MAT04FP  | 400 μV              | -40°C to +85°C | P-DIP-14    | N-14    |

| MAT04FS  | 400 μV              | -40°C to +85°C | 14-Lead SO  | SO-14   |

#### NOTES

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the MAT04 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$<sup>^2\</sup>theta_{JA}$  is specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip and P-DIP packages;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SO package.

<sup>\*</sup>Not for new designs; obsolete April 2002.

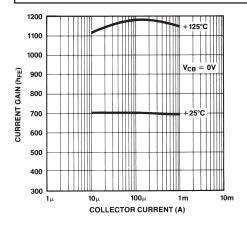

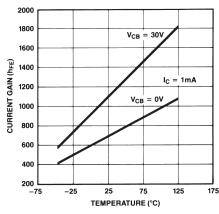

# **Typical Performance Characteristics—MAT04**

TPC 1. Current Gain vs. Collector Current

TPC 2. Current Gain vs. Temperature

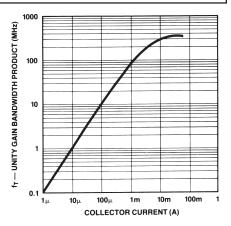

TPC 3. Gain Bandwidth vs. Collector Current

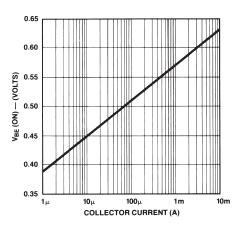

TPC 4. Base-Emitter-On-Voltage vs. Collector Current

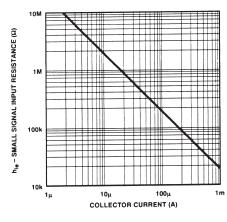

TPC 5. Small Signal Input Resistance  $(h_{ie})$  vs. Collector Current

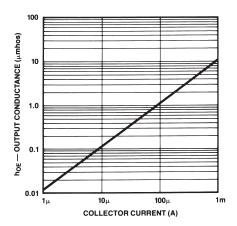

TPC 6. Small Signal Output Conductance vs. Collector Current

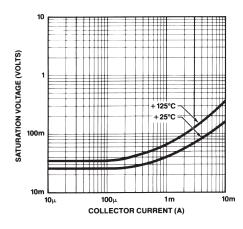

TPC 7. Saturation Voltage vs. Collector Current

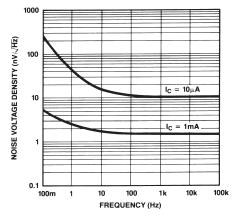

TPC 8. Noise Voltage Density vs. Frequency

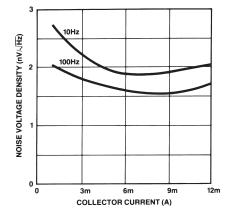

TPC 9. Noise Voltage Density vs. Collector Current

REV. D \_5\_

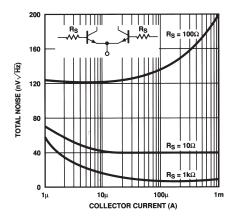

TPC 10. Total Noise vs. Collector Current

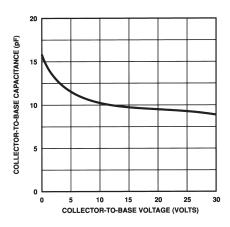

TPC 11. Collector-to-Base Capacitance vs. Collector-to-Base Voltage

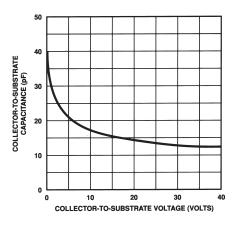

TPC 12. Collector-to-Substrate Capacitance vs. Collector-to-Substrate Voltage

#### **APPLICATION NOTES**

It is recommended that one of the substrate pins (Pins 4 and 11) be tied to the most negative circuit potential to minimize coupling between devices. Pins 4 and 11 are internally connected.

## APPLICATIONS CURRENT SOURCES

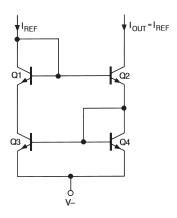

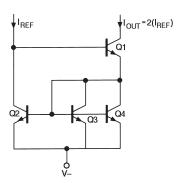

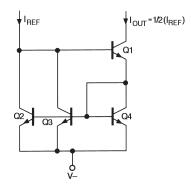

The MAT04 can be used to implement a variety of high impedance current mirrors as shown in Figures 1, 2, and 3. These current mirrors can be used as biasing elements and load devices for amplifier stages.

Figure 1. Unity Gain Current Mirror,  $I_{OUT} = I_{REF}$

The unity-gain current mirror of Figure 1 has an accuracy of better than 1% and an output impedance of over 100 M $\Omega$  at 100  $\mu$ A. Figures 2 and 3 show modified current mirrors designed for a current gain of two, and one-half respectively. The accuracy of these mirrors is reduced from that of the unity-gain source due to base current errors but is still better than 2%.

Figure 2. Current Mirror,  $I_{OUT} = 2(I_{REF})$

Figure 3. Current Mirror,  $I_{OUT} = 1/2(I_{REF})$

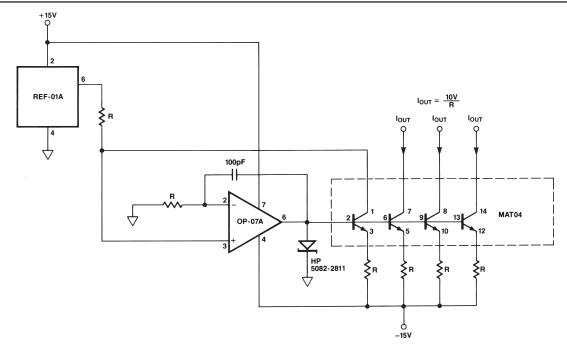

Figure 4 is a temperature independent current sink that has an accuracy of better than 1% at an output current of 100  $\mu$ A to 1 mA. The Schottky diode acts as a clamp to ensure correct circuit start-up at power on. The resistors used in this circuit should be 1% metal-film type.

Figure 4. Temperature Independent Current Sink,  $I_{OUT} = 10 \text{ V/R}\Omega$

#### **NONLINEAR FUNCTIONS**

An application where precision matched-transistors are a powerful tool is in the generation of nonlinear functions. These circuits are based on the transistor's logarithmic property, which takes the following idealized form:

$$V_{BE} = \frac{kT}{q} In \frac{l_C}{l_S}$$

The MAT04, with its excellent logarithmic conformance, maintains this idealized function over many decades of collector current. This, in addition to the stringent parametric matching of the MAT04, enables the implementation of extremely accurate log/antilog circuits.

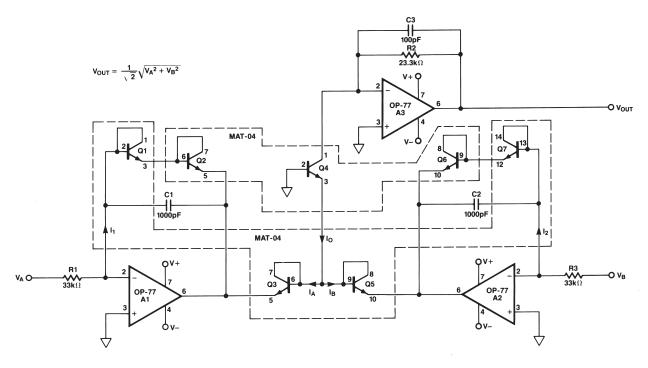

The circuit of Figure 5 is a vector summer that adds and subtracts logged inputs to generate the following transfer function:

$$V_{OUT} = \frac{1}{\sqrt{2}} \sqrt{{V_A}^2 + {V_B}^2}$$

This circuit uses two MAT04 and maintains an accuracy of better than 0.5% over an input range of 10 mV to 10 V. The layout of the MAT04s reduces errors due to matching and temperature differences between the two precision quad matched transistors.

Op amps A1 and A2 translate the input voltages into logarithmic valued currents ( $I_A$  and  $I_B$  in Figure 5) that flow through transistor Q3 and Q5. These currents are summed by transistor Q4

$$(I_O = I_A + I_B = \sqrt{l_1^2 + l_2^2}),$$

which feeds the current-to-voltage converter consisting of op amp A3. To maintain accuracy, 1% metal-film resistors should be used.

REV. D \_\_7\_

Figure 5. Vector Summer

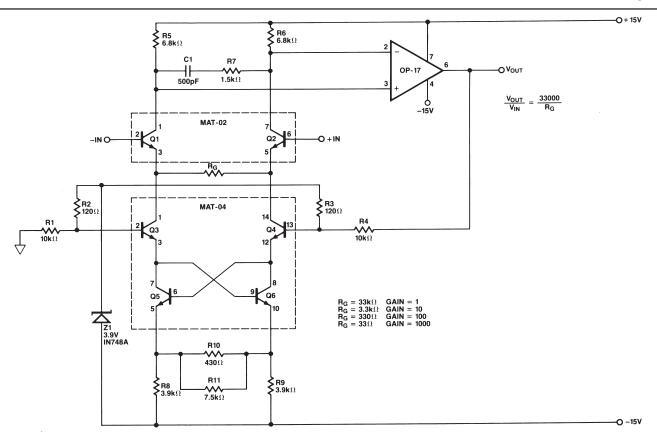

## LOW NOISE, HIGH SPEED INSTRUMENTATION AMPLIFIER

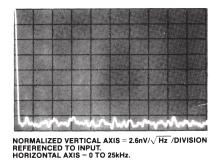

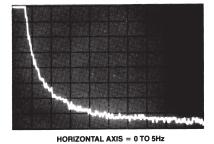

The circuit of Figure 6 is a very low noise, high speed amplifier, ideal for use in precision transducer and professional audio applications. The performance of the amplifier is summarized in Table I. Figure 7 shows the input referred spot noise over the 0-25 kHz bandwidth to be flat at 1.2 nV/ $\overline{\text{Hz}}$ . Figure 20 highlights the low 1/f noise corner at 2 Hz.

The circuit uses a high speed op amp, the OP17, preceded by an input amplifier. This consists of a precision dual matched-transistor, the MAT02, and a feedback V-to-I converter, the MAT04. The arrangement of the MAT04 is known as a "linearized cross quad" which performs the voltage-to-current conversion. The OP17 acts as an overall nulling amplifier to complete the feedback loop. Resistors R1, R2, and R3, R4 form voltage dividers that attenuate the output voltage swing since the "cross quad" arrangement has a limited input range. Biasing for the input stage is set by Zener diode Z1. At low currents, the effective zener voltage is about 3.3 V due to the soft knee characteristic of the Zener diode. This results in a bias current of 530  $\mu\text{A}$  per side for the input stage. The gain of this amplifier with the values shown in Figure 6 is:

$$\frac{V_{OUT}}{V_{IN}} = \frac{33000}{R_G}$$

Table I. Instrumentation Amplifier Characteristics

| G = 1000<br>G = 100<br>G = 10  | $\begin{array}{c} 1.2 \text{ nV/}\sqrt{\overline{\text{Hz}}} \\ 3.6 \text{ nV/}\sqrt{\overline{\text{Hz}}} \\ 30 \text{ nV/}\sqrt{\overline{\text{Hz}}} \end{array}$ |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G = 500<br>G = 100<br>G = 10   | 400 kHz<br>1 MHz<br>1.2 MHz                                                                                                                                          |

|                                | 40 V/μs                                                                                                                                                              |

| G = 1000                       | 130 dB                                                                                                                                                               |

| G = 100<br>f = 20 Hz to 20 kHz | 0.03%                                                                                                                                                                |

| G = 1000                       | 10 μs                                                                                                                                                                |

|                                | 350 mW                                                                                                                                                               |

|                                | G = 100<br>G = 10<br>G = 500<br>G = 100<br>G = 10<br>G = 1000<br>G = 100<br>G = 20 Hz to 20 kHz                                                                      |

Figure 6. Low Noise, High-Speed Instrumentation Amplifier

Figure 7. Spot Noise of the Instrumentation Amplifier from 0–25 kHz, Gain Of 1000

Figure 8. Low Frequency Noise Spectrum Showing Low 2 Hz Noise Corner, Gain = 1000

REV. D \_9\_

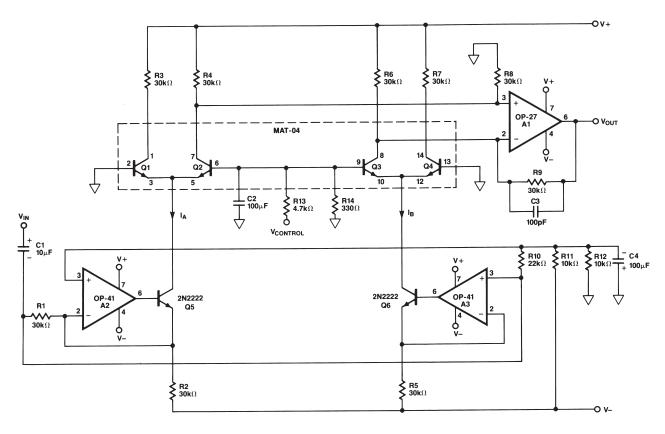

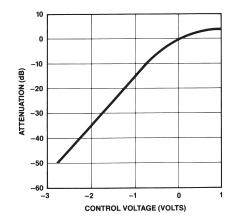

Figure 9. Voltage-Controlled Attenuator

#### **VOLTAGE-CONTROLLED ATTENUATOR**

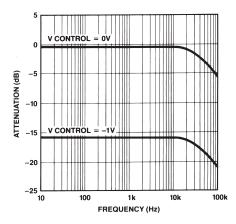

The voltage-controlled attenuator (VCA) of Figure 9, widely used in professional audio circles, can easily be implemented using a MAT04. The excellent matching characteristics of the MAT04 enables the VCA to have a distortion level of under 0.03% over a wide range of control voltages. The VCA accepts a 3 V RMS input and easily handles the full 20 Hz–20 kHz audio bandwidth as shown in Figure 10. Noise level for the VCA is more than 110 dB below maximum output.

In the voltage controlled attenuator, the input signal modulates the stage current of each differential pair. Op amps A2 and A3 in conjunction with transistors Q5 and Q6 form voltage-to-current converters that transform a single input voltage into differential currents which form the stage currents of each differential pair. The control voltage shifts the current between each side of the two differential pairs, regulating the signal level reaching the output stage which consists of op amp A1. Figure 11 shows the increase in signal attenuation as the control voltage becomes more negative.

The ideal transfer function for the voltage-controlled attenuator is:

$$V_{OUT} /_{IN} = \frac{2}{1 + \exp\left((V_{CONTROL}) \left(\frac{R14}{R13 + R14}\right) / \left(\frac{kT}{q}\right)\right)}$$

Where  $k = \text{Boltzman constant } 1.38 \times 10^{-23} \text{J/}^{\circ} \text{K}$

$T = \text{temperature in } ^{\circ}\text{K}$

$q = \text{electronic charge} = 1.602 \times 10^{-19} \text{C}$

From the transfer function it can be seen that the maximum gain of the circuit is 2 (6 dB).

To ensure best performance, resistors R2 through R7 should be 1% metal film resistors. Since capacitor C2 can see small amounts of reverse bias when the control voltage is positive, it may be prudent to use a nonpolarized tantalum capacitor.

Figure 10. Voltage-Controlled Attenuator, Attenuation vs. Frequency

Figure 11. Voltage-Controlled Attenuator, Attenuation vs. Control Voltage

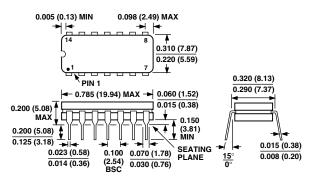

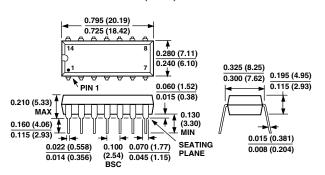

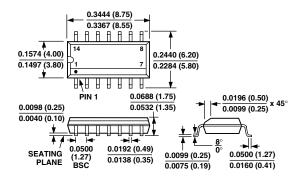

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 14-Lead Cerdip (Q-14)

#### 14-Lead Plastic DIP (N-14)

#### 14-Lead Narrow-Body SO (R-14/SO-14)

REV. D –11–

# **Revision History**

| Location                                     | Page |

|----------------------------------------------|------|

| Data Sheet changed from REV. C to REV. D.    |      |

| Edits to ABSOLUTE MAXIMUM RATINGS            | 1    |

| Deleted ELECTRICAL CHARACTERISTICS for -55°C | 3    |

| Deleted WAFER TEST LIMITS                    | 4    |

| Edits to TPCs                                | 5–6  |

| Added OUTLINE DIMENSIONS                     | 13   |