# **Product Brief**

## Cortina Systems® IXF18105/201/203 10 Gbps Ethernet Media Access Controller

#### **Product Overview**

The Cortina Systems® IXF18105/201/203 family of 10 Gbps Ethernet Media Access Controllers (MACs) (IXF18105/201/203) offer flexible solutions for both high performance and low cost per port systems.

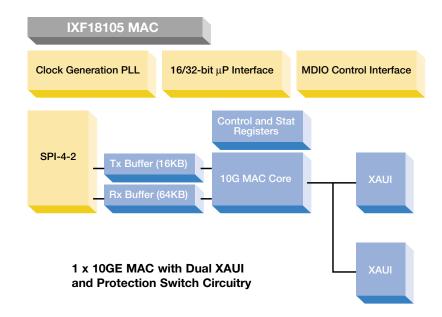

The devices are software compatible and are consistent in pinout, allowing for design re-use between 10 Gbps Ethernet platforms. The IXF18105 10 Gbps Ethernet MAC is a single channel device with two XAUI line interfaces and a System Packet Interface Level 4 (SPI-4) system interface. The XAUI interfaces can be configured in a protection switch mode, where a primary XAUI interface can be switched to a backup XAUI interface in the event the primary goes into a failure mode. The IXF18105 is ideal for a single port 10 Gbps application where bandwidth is expected to be at or near full utilization and network reliability needs to be protected with a backup line interface.

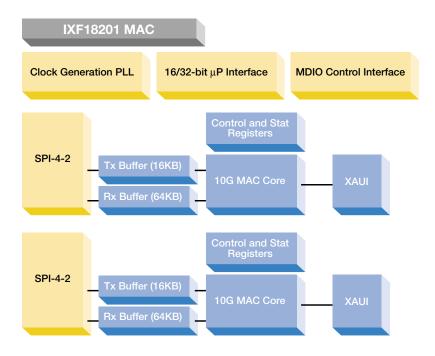

The IXF18201 2-Port 10 Gbps Ethernet MAC is built on a similar architecture as the IXF18105. The device offers two independent 10 Gbps MAC and XAUI ports, versus a single port. Each MAC is linked to its own SPI-4 system interface. The IXF18201 is ideal for higher density applications where multiple 10 Gbps ports are implemented on a line card and bandwidth is at or near full utilization.

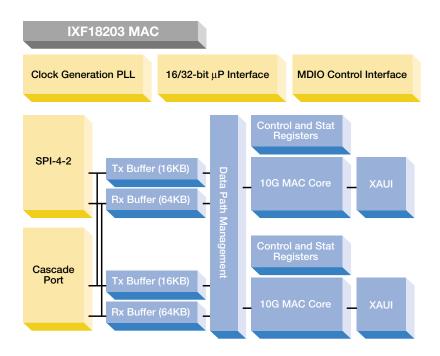

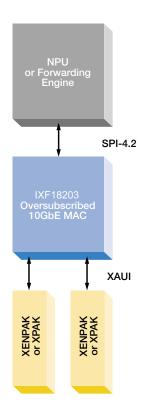

The IXF18203 2-Port Ethernet MAC with Oversubscription is also based on the IXF18105 and IXF18201 architectures, with a critical building block added for Data Path Management (DPM). The IXF18203 has two 10 Gbps MAC channels connected to a single SPI-4.2 interface. The DPM block manages the traffic of the two 10 Gbps data streams and passes packets to the single SPI-4 system interface. This is achieved with a priority scheme that maximizes the efficiency of lower utilized 10 Gbps data paths. With two 10 Gpbs data paths combined to a single system interface, the system complexity is cut in half reducing cost per port. Even more attractive is the cascade port of the IXF18203. Combining two IXF18203 devices together through the cascade port allows up to four 10 Gbps streams to be managed down to a single SPI-4 interface. This cascade configuration enables very high density designs at extremely low cost per port.

#### IXF18201 Block Diagram

## IXF18203 Block Diagram

| General Features                                                                                                                                                                                        | General Benefits                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XAUI Interface                                                                                                                                                                                          | Directly supports XENPAK*, XPAK*, X2 modules and XFP* with external XAUI to 10 Gbps Serial Transceiver                                                                                                                                                                                                                                                     |

| Pause Control                                                                                                                                                                                           | Supports IEEE 802.3x flow control and external pause packet generation                                                                                                                                                                                                                                                                                     |

| • 1.2V IEEE MDIO Interface                                                                                                                                                                              | <ul> <li>Supports XENPAK and XPAK modules with flexible<br/>GPIO pins and RMON statistics counters</li> </ul>                                                                                                                                                                                                                                              |

| SPI-4.2 Interface                                                                                                                                                                                       | <ul> <li>Connects directly to network processors or<br/>custom forwarding engines</li> </ul>                                                                                                                                                                                                                                                               |

| Dedicated Memory Architecture                                                                                                                                                                           | <ul> <li>16 kb Tx FIFO, 64 kb Rx FIFO, 16 kb HPLB FIFO<br/>and 9.6 kB jumbo frame support</li> </ul>                                                                                                                                                                                                                                                       |

| IXF18105 Features                                                                                                                                                                                       | IXF18105 Benefits                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Protection switching between the XA UI interfaces is user controlled</li> </ul>                                                                                                                | <ul> <li>Single 10 Gbps MAC with dual XA UI inputs allows<br/>for switching inputs when a single input fails</li> </ul>                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                            |

| IXF18201 Features                                                                                                                                                                                       | IXF18201 Benefits                                                                                                                                                                                                                                                                                                                                          |

| • Dual MAC Cores in a 672 lead BGA package                                                                                                                                                              | <ul><li>IXF18201 Benefits</li><li>Reduced footprint through higher integration</li></ul>                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                            |

| Dual MAC Cores in a 672 lead BGA package                                                                                                                                                                | Reduced footprint through higher integration                                                                                                                                                                                                                                                                                                               |

| <ul> <li>Dual MAC Cores in a 672 lead BGA package</li> <li>Less than 3.5W per channel</li> </ul>                                                                                                        | <ul><li>Reduced footprint through higher integration</li><li>Low power design</li></ul>                                                                                                                                                                                                                                                                    |

| <ul> <li>Dual MAC Cores in a 672 lead BGA package</li> <li>Less than 3.5W per channel</li> <li>IXF18203 Features</li> </ul>                                                                             | <ul> <li>Reduced footprint through higher integration</li> <li>Low power design</li> <li>IXF18203 Benefits</li> <li>Allows implementation of o versubscription, which</li> </ul>                                                                                                                                                                           |

| <ul> <li>Dual MAC Cores in a 672 lead BGA package</li> <li>Less than 3.5W per channel</li> <li>IXF18203 Features</li> <li>Dual MAC Cores</li> </ul>                                                     | <ul> <li>Reduced footprint through higher integration</li> <li>Low power design</li> <li>IXF18203 Benefits</li> <li>Allows implementation of o versubscription, which ultimately reduces cost per port</li> <li>Allows for controlled data flow to minimiz e loss of</li> </ul>                                                                            |

| <ul> <li>Dual MAC Cores in a 672 lead BGA package</li> <li>Less than 3.5W per channel</li> <li>IXF18203 Features</li> <li>Dual MAC Cores</li> <li>Data Path Management</li> </ul>                       | <ul> <li>Reduced footprint through higher integration</li> <li>Low power design</li> <li>IXF18203 Benefits</li> <li>Allows implementation of o versubscription, which ultimately reduces cost per port</li> <li>Allows for controlled data flow to minimiz e loss of system critical frames</li> <li>Allows two IXF18203 devices to be cascaded</li> </ul> |

| <ul> <li>Dual MAC Cores in a 672 lead BGA package</li> <li>Less than 3.5W per channel</li> <li>IXF18203 Features</li> <li>Dual MAC Cores</li> <li>Data Path Management</li> <li>Cascade Port</li> </ul> | <ul> <li>Reduced footprint through higher integration</li> <li>Low power design</li> <li>IXF18203 Benefits</li> <li>Allows implementation of o versubscription, which ultimately reduces cost per port</li> <li>Allows for controlled data flow to minimiz e loss of system critical frames</li> <li>Allows two IXF18203 devices to be cascaded</li> </ul> |

#### Typical Application of IXF18203

### **Cortina in Communications**

Cortina is a leading supplier of intelligent communication solutions through continuous innovations in advanced port processing and intelligent port connectivity to the Core, Metro , Access and Enterprise Market Segments. With our state-of-the-art high speed analog digital integration, we deliver a wide suite of products that address our customers'

performance, density and flexibility needs enabling faster time-to-market, longer time-in-market, and increased revenue opportunities. Working closely with our customers to understand their system requirements and anticipate their needs, we are creating the foundation ingredients for new generations of services.

${}^{*}\mathrm{Other}$  names and brands may be claimed as the property of others.

Cortina Systems, Inc. 840 W California Ave. Sunnyvale, CA 94086 408-481-2300 sales@cortina-systems.com www.cortina-systems.com