# **STA2064**

# Cartesio<sup>™</sup> family infotainment application processor with embedded GPS

Data brief

#### **Features**

- ARM1176 533 MHz host processor

- Cache: 32 KB instruction, 32 KB data

- Vector floating point unit

- High performance embedded GPS subsystem

- Parallel acquisition engines for 8 GPS satellites or 4 Galileo satellites

- 32 tracking channels for all satellites in view

- 5 correlators per channel for urban canyon robustness

- Multibit signal processing hardware

- Advanced power management

- Separated power islands for ultra low power mode

- Dynamic core frequency scaling

- 512-Byte embedded SRAM for back-up

- System infrastructure

- LP DDR/DDR2 controller: 16 bit data 256 MB addressable (333 MHz DDR2, 200 MHz LPDDR)

- One bank of 32 KB embedded SRAM

- 64-channel vector interrupt controller (VIC)

- 2 DMA controllers, 16 physical channels

- 32 DMA request for each controller

- Two external DMA requests are supported

- Display and graphics

- Color LCD controller for STN,TFT or HR-TFT panels with 18-bit parallel RGB interface

- Integrated touch screen controller and ADC

- 3D advanced graphics acceleration

- JPEG baseline profile decoder

- High throughput interfaces

Downloaded from Elcodis.com electronic components distributor

- 1 ports USB 2.0 OTG with integrated physical layer

- 2 SD/MMC up to 8 bit data, all bootable

- Audio interfaces and features

- Three multichannel serial ports (I2S/TDM)

- SPDIF input interface

- C3 hardware reed-solomon decoder

- Sample rate converter

- Standard interfaces

- Four 16-bit input capture/output compare

- Pulse width light modulator (PWL)

- Four autobaud UART

- Three I<sup>2</sup>C multimaster/slave interfaces

- Two synchronous serial port (SSP, SPI)

- 65 GPIO over 5 ports

- One controller area network (CAN) in automotive version

- Programmable voltage IOs: 1.8 V, 2.5 V, 3.3 V

- V<sub>DDIO\_ON</sub>: 1.8 ±10%V, V<sub>DD\_ON</sub>: V<sub>DD</sub>, 1.25 ±3%V

- TFBGA 289, 0.8 mm pitch package, packing in trav

- Ambient temperature range: -40 / +85 °C

Table 1. Device summary

| Order code | Qualification grade | CPU freq. | CAN |

|------------|---------------------|-----------|-----|

| STA2064N   | Consumer            | 533 MHz   | No  |

| STA2064A   | Automotive          | 533 MHz   | 1x  |

October 2009 Doc ID 16057 Rev 3 1/19

Contents STA2064

# **Contents**

| 1    | Desc | cription |                                     |

|------|------|----------|-------------------------------------|

| 2    | Syst | em des   | cription 5                          |

|      | 2.1  | MCU .    | 5                                   |

|      | 2.2  | Embed    | lded memories                       |

|      |      | 2.2.1    | Embedded SRAM (eSRAM)5              |

|      | 2.3  | System   | n functions                         |

|      | _    | 2.3.1    | System and reset controller (SRC)   |

|      |      | 2.3.2    | PMU                                 |

|      |      | 2.3.3    | DMA                                 |

|      |      | 2.3.4    | Vectored interrupt controller (VIC) |

|      |      | 2.3.5    | GPIOs5                              |

|      |      | 2.3.6    | Real-time clock (RTC)               |

|      |      | 2.3.7    | Real-time timer (RTT)6              |

|      |      | 2.3.8    | Always_ON supply                    |

|      |      | 2.3.9    | Enhanced function timer (EFT)6      |

|      |      | 2.3.10   | Watchdog timer (WDT)6               |

|      | 2.4  | Memor    | y interfaces 6                      |

|      |      | 2.4.1    | SD/MMC                              |

|      |      | 2.4.2    | DDR-SDRAM controller                |

|      | 2.5  | Audio/\  | video functions                     |

|      |      | 2.5.1    | C3                                  |

|      |      | 2.5.2    | Sample rate converter (SaRaC)       |

|      |      | 2.5.3    | JPEG decoder                        |

|      |      | 2.5.4    | Smart graphic accelerator (SGA)     |

|      |      | 2.5.5    | Color LCD controller (CLCD)         |

|      | 2.6  | Comm     | unication interfaces                |

|      |      | 2.6.1    | USB8                                |

|      |      | 2.6.2    | UART8                               |

|      |      | 2.6.3    | I2C                                 |

|      |      | 2.6.4    | MSP 8                               |

|      |      | 2.6.5    | SSP 8                               |

|      |      | 2.6.6    | SPDIF8                              |

|      |      | 2.6.7    | AC97 controller                     |

|      |      |          |                                     |

| 2/19 |      |          | Doc ID 16057 Rev 3                  |

| STA2064             | Content  |

|---------------------|----------|

| STA:206/I           | ( Ontont |

| JIAZUU <del>T</del> | Content  |

|   |      | 2.6.8         | CAN9                                           | ) |

|---|------|---------------|------------------------------------------------|---|

|   | 2.7  | Specifi       | c functions                                    | ) |

|   |      | 2.7.1         | GPS9                                           | ) |

|   |      | 2.7.2         | Touchscreen controller/ADC10                   | ) |

|   |      | 2.7.3         | Multisupply IO ring                            | ) |

|   |      | 2.7.4         | Driving strength and slew rate programmability |   |

| 3 | Syst | em feat       | ures introduction                              | • |

|   | 3.1  | Power         | region partition                               | , |

|   | 3.2  | Freque        | ency region partition                          | , |

|   | 3.3  | Freque        | ency and power range                           | , |

|   | 3.4  | Power         | states                                         | ŀ |

|   | 3.5  | System        | n wakeup and power down                        | , |

|   | 3.6  | IO grou       | ups 16                                         | į |

| 4 | Pack | cage info     | ormation                                       | , |

| 5 | Revi | ision history |                                                |   |

Description STA2064

#### 1 **Description**

STA2064 is a highly integrated SOC application processor combining host capability with high performance embedded GPS.

STA2064 targets vehicle head units and mobile navigation (PND), telematics, infotainment, advanced audio and connectivity systems. The STA2064 provides all the elements that are essential to build a cost effective solution.

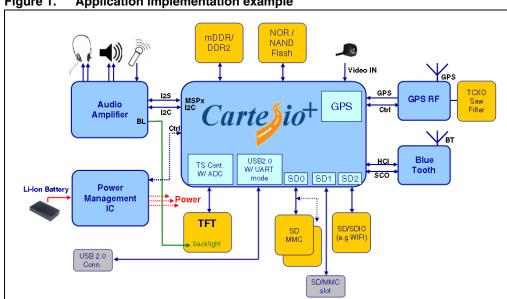

**Application implementation example** Figure 1.

Downloaded from Elcodis.com electronic components distributor

# 2 System description

#### 2.1 MCU

ARM1176-JZF advanced risc machine CPU up to 533 MHz (with Vdd greater or equal to 1.20 V and under process and temperature worst case conditions).

#### 2.2 Embedded memories

#### 2.2.1 Embedded SRAM (eSRAM)

The embedded SRAM is 8K x 32 (32 KB).

## 2.3 System functions

## 2.3.1 System and reset controller (SRC)

This provides a control interface for clock generation components external to the subsystem. It also controls system-wide and peripherals-specific energy management features.

#### 2.3.2 PMU

The power manager module controls the SLEEP to DEEP-SLEEP modes transition, controls the external voltage switches on the Vdd and Vddio, monitors the external power supply (via two signals, Vddok and BATOK), can force the emergency entry of the SDRAM in self-refresh, and controls the wake-up from DEEP-SLEEP mode.

#### 2.3.3 DMA

Direct memory access can be used with DMA peripherals. FIFO fill/empty requests from these peripherals can be serviced immediately by the DMA Controller without CPU interaction. Peripheral-to-peripheral and memory-to-memory DMA are also supported. STA2064 features two DMA engines. Each DMA supports up to 8-channels and up to 32 requests.

## 2.3.4 Vectored interrupt controller (VIC)

The VIC allows the OS interrupt handler to quickly dispatch interrupt service routines in response to peripheral interrupts.

#### 2.3.5 **GPIOs**

Four GPIO ports provide 65 programmable inputs or outputs that can be controlled in two modes:

- software mode through an APB bus interface

- hardware mode through a hardware control interface

System description STA2064

#### 2.3.6 Real-time clock (RTC)

The RTC provides a one second resolution clock. This keeps time when the system is inactive and can be used to wake the system up when a programmed 'alarm' time is reached. It has a clock trimming feature to compensate the drift of the 32.768 kHz crystal.

#### 2.3.7 Real-time timer (RTT)

The RTT has the possibility of being clocked off. This reduces the always\_on domain consumption during Deep Sleep. By default the RTT has its clock enabled.

## 2.3.8 Always\_ON supply

The "Always\_ON" domain retains its two separate supplies, one for the core logic ( $V_{DDON}$ ) and one for the IOs ( $V_{IOON}$ ).

The  $V_{DDON}$  supply is equal to  $V_{DD}$  during normal operation but, with the goal of reaching the lowest consumption possible, can also be configured as low as 1.0  $\pm$ 10%V when the device is in deep-sleep.

## 2.3.9 Enhanced function timer (EFT)

STA2064 features 4 16-bit EFTs. Each of the four EFT timers has a 16-bit free-running counter with 7-bit prescaler, up to two input capture/output compare functions, a pulse counter function, and a PWM channel with selectable frequency.

### 2.3.10 Watchdog timer (WDT)

This OS resource is used to trigger a system reset in the event of software failure.

## 2.4 Memory interfaces

#### 2.4.1 SD/MMC

STA2064 features two SD/SDIO/MMC interfaces up to 52 MHz / one up to 8-bit data, the other up to 4-bit data. The main clock available to the peripherals is:

- PLL2CLK/13 (when PLL2CLK is 624 MHz and SRC\_MMC52 = 0, 48 MHz will be generated)

- PLL2CLK/12 (when PLL2CLK is 624 MHz and SRC\_MMC = 1, 52 MHz will be generated)

- PLL2CLK/9 (when PLL2CLK is 432 MHz, 48 MHz will be generated)

The peripheral is compliant to the following standards:

- MMC 4.4

- SD 2.0/Part 1 Physical Layer

- SD 2.0/Part E1 SDIO Specification

**\_\_\_\_\_**

#### 2.4.2 DDR-SDRAM controller

The SDRAM controller has been designed to support up to 1Gbit over each of the two chip selects (or up to 2 Gbit over a single chip select) of:

- LP DDR-SDRAM

- DDR2

The memory data bus will be 16 or 32-bit wide for LP DDR-SDRAM memories (under software control). This same configuration is also supported for DDR2 type of memories, with two 16-bit devices per chip select.

#### 2.5 Audio/video functions

#### 2.5.1 C3

It is composed of CD-ROM Decoder Block, responsible for performing sector descrambling and 3<sup>rd</sup> level of error correction embedded in the sector specific to CD-ROM mode1 and XA Form1, and Data Filter block supporting frame data filtering and different block layout organization possibilities. The C3 block can take its input data directly from SPDIF or from the memory space, and delivers back its output data to memory, supporting DMA requests.

#### 2.5.2 Sample rate converter (SaRaC)

This block offers a fully digital stereo asynchronous sample rate conversion, using an automatic Digital Ratio Locked Loop. Its main features are:

- Up to 20-bit input and 22-bit output sample size

- DMA optimized 16-bit stereo sample interface

- Input sample rate from selectable MSP or SPDIF interface (32 kHz to 48 kHz)

- Output sample rate from selectable MSP interface (44.1 kHz to 48 kHz)

- Internally generated input sample rate (8 kHz to 48 kHz) for compressed audio decoding

#### 2.5.3 JPEG decoder

The JPEG decoder block performs Baseline DCT sequential decoding up to 16Mpix/sec. JPEG compressed thumbnails are also supported.

#### 2.5.4 Smart graphic accelerator (SGA)

The smart graphic accelerator (SGA) provides an efficient 2D and 3D primitive drawing tool that breaks down the MIPS and power consumption concerns of pixel processing.

#### 2.5.5 Color LCD controller (CLCD)

This interface drives LCD panels. It supports single or dual-panel color and monochrome STN displays and color TFT or HR-TFT displays. The resolution can be 1, 2 or 4 bits-perpixel (bpp) palletized for mono STN, 1, 2, 4 or 8 bpp palletized for color STN and TFT, 16-bpp true-color non palletized for Color STN and TFT, 18-bpp packed or not packed truecolor non palletized for color TFT. It also offers Frame Modulation to deliver enhanced colors on 12, 16 or 18 bits (HR-) TFT panels from up to 18-bpp format.

System description STA2064

#### 2.6 Communication interfaces

#### 2.6.1 USB

STA2064 embeds one USB2.0 OTG high-speed interface, featuring:

- a) High-speed signalling rate at 480 Mbit/s

- b) Support for full-speed (12 Mbit/s) signaling bit rate

- c) Support for session request protocol (SRP) and host negotiation protocol (HNP)

- d) Up to 7 bidirectional endpoints plus control endpoint 0

- e) 8192 bytes maximum FIFO dimension

- f) Dynamic FIFO allocation

To reduce total system cost, it is equipped with a built-in USB 2.0 PHY.

With the goal of reducing the BOM cost for the customer, the USB 2.0 PHY also supports this additional muxing scheme:

- the USB D- wire is used as either the USB D- signal or UART receive data signal

- the USB D+ wire is used as either the USB D+ signal or the UART transmit data signal

#### 2.6.2 UART

STA2064 features four Autobaud UARTs. One offers all modem control/status signals. They are enhanced version of the industry-standard 16C550 UART.

#### 2.6.3 $I^2C$

The I<sup>2</sup>C controller is an interface designed to support the physical and data link layer according to I<sup>2</sup>C standard revision 2.1 (January 2000). The I<sup>2</sup>C bus is a 2-wire serial bus that provides a low-cost interconnection between ICs. STA2064 features three I<sup>2</sup>C interfaces.

#### 2.6.4 MSP

The multichannel serial port (MSP) is a synchronous receive and transmit serial interface. STA2064 features three MSPs.

#### 2.6.5 SSP

STA2064 features two SSPs up to 24Mbit/sec for synchronous serial communication with external peripherals. SPI, MicroWire, T.I. and mono-directional protocols are supported with programmable word length up to 32 bits.

## 2.6.6 SPDIF

Downloaded from Elcodis.com electronic components distributor

This interface takes SPDIF as input and extracts data and other channel information encrypted in SPDIF Frame format as per IEC958 standards. Data can be transferred to memory, using DMA support, or directly to C3 decoder without CPU intervent. SPDIF block supports up to 2X data streams.

8/19 Doc ID 16057 Rev 3

#### 2.6.7 AC97 controller

AC97 audio controller enables SOC to control external AC97 CODECs using SOC AMBA interconnect. It is implemented in a way to minimize audio data handling by SOC processor with dedicated audio DMA engine. AC97 Audio Controller supports AC97 revision 2.3 compliant audio CODECs. External interface supports one external AC97 CODEC with 6 output (3 of them can be Double Rate Audio) and 3 input channels.

#### 2.6.8 CAN

STA2064 features one CAN module that is compliant with the CAN specification V2.0 part B (active). The bit rate can be programmed up to 1 MBaud.

## 2.7 Specific functions

#### 2.7.1 GPS

STA2064 integrates HPGPS\_G2, ST's proprietary GPS IP, which is ST's 2nd generation High-Sensitivity Baseband. The Baseband is fully compliant with GPS and Galileo L1/E1 signal specifications, and is optimised to maximise sensitivity for both acquisition and tracking in difficult environments. Please refer to GPS solution specifications and software release notes for more specific performance details.

The baseband accepts a 3-bit signal at a 4MHz IF from its companion RF chip, the STA5630. It downconverts this to baseband and feeds it to the acquisition engines (for up to 8 satellites simultaneously) and the tracking channels (for up to 32 satellites simultaneously).

The highly parallel correlators in the acquisition engines identify each satellite signal in time and frequency domains, and the results are passed to the tracking channels. The tracking channels fine-tune the lock, then track continuously, providing orbit data and timing measurements to the ARM CPUs.

The management of the hardware for these operations, and the myriad of complex conditions that arise, is performed in a complete GPS software library supplied by ST. This library also takes the resultant measurement data and processes it to maintain satellite databases and calculate the user's position, velocity and time(PVT) solutions.

The PVT solution, and other useful data, is made available to the user's application via an API in the ST GPS library. This runs on a royalty-free real-time kernel (OS20), with ports to industry-standard operating systems also available. In stand-alone mode, the outputs are generated in standard NMEA message format.

Options are also available in the software library to support ST Self-Trained Assisted GPS (ST-AGPS), a complete and scalable solution for assisting GPS start-up with Autonomous Ephemeris prediction when no network is available, and with simple download when a network is available followed by prediction for the following 7 days.

The GPS subsystem is based on an ARM966 processor and is clocked by two clocks:

- MCLK: ARM966 CPU clock

- RFCLK: 16f<sub>0</sub> or 32f<sub>0</sub>, from RF chip

MCLK is derived from the PLL2 clock with a divisor from 3 to 16, giving an ARM966 operating frequency in the range from 208 to 39 MHz, in the case the PLL2 is running at 624

**577**

Doc ID 16057 Rev 3 9/19

System description STA2064

MHz. The same divisor will be from 2 to 16 when the PLL2 is running at 432 MHz, giving an operating frequency in the range from 216 to 27 MHz.

The GPS baseband clock will be derived from the MCLK clock with a divider, internal to the subsytem, by 1, 2,3 or 4, under ARM11 control. RFCLK is the clock received from the RF front-end chip.

#### 2.7.2 Touchscreen controller/ADC

STA2064 embeds a 4-wire Touch Screen Controller. The Touch Screen Controller main characteristics are:

- Active Window Clip

- Movements Tracking

- 12-bit SAR ADC resolution when used for Touch screen (with averaging)

- Measurement oversampling from 2 to 8

- Up to 128 coordinates FIFO, with programmable FIFO threshold

- ADC minimum conversion time of 1 μs

- Capability to support 4 additional analog inputs for auxiliary functions like battery voltage monitoring and accessory control.

The ADC of the Touch Screen Controller can be also used for the conversion of external analog signals. In this case the ADC has a 10-bit resolution (its native resolution).

#### 2.7.3 Multisupply IO ring

STA2064 has multivoltage IOs capable of supporting 1.8V, 2.5V or 3.3V interfaces. The rings are defined as follows:

- A: All peripherals with exception of what belongs to other rings

- B: LCD

- C: DRAM

- E: MMC1 (GPIO40-47, GPIO76-82), CAN0

The default voltage applied to each ring will be at reset time will be:

- A: 1.8V

- B: 1.8V

- C: 1.8V

- E: 3.3V

The "Always ON" ring remains separated as in the current STA2064 and supplied by V<sub>IOON</sub>.

**\_\_\_\_\_**

## 2.7.4 Driving strength and slew rate programmability

The IO Driving Strength is programmable for the following interfaces as follows:

SD/MMC0 (4, 6, 8 mA) (default 8mA)

SD/MMC1 (4, 6, 8 mA) (default 8mA)

LCD (4, 8 mA) (default 8mA)

DRAM (weak 70Ω, strong 50Ω) (default strong, 50Ω)

The Slew Rate is also controllable for the following interface as follows:

SD/MMC0 (Nominal, Fast) (default Nominal slew rate)

SD/MMC1 (Nominal, Fast) (default Nominal slew rate)

LCD (Nominal, Fast) (default Fast slew rate)

DRAM (200, 266, 333 MHz) (default 200 MHz)

MSP0 (Nominal, Fast) (default Nominal slew rate)

MSP1 (Nominal, Fast) (default Nominal slew rate)

# 3 System features introduction

In this chapter, an introduction to the main STA2064 system features is given. These will be explained in detail later in this document.

## 3.1 Power region partition

STA2064 is a device targeted to wide range of applications, starting from handheld battery powered devices thanks to an optimized power management but also addressing in dash automotive power requirements thanks to its flexibile multivoltage IO.

Three main power regions are identified:

- V<sub>dd\_on</sub>: It is the core voltage that powers the RTC (real-time clock), the PMU (Power Management Unit), SRC (System Clock and Reset controller) and the Backup RAM of STA2064. V<sub>dd\_on</sub> remains usually powered even when the device is in DEEP-SLEEP mode. For this reason, the static power consumption of this region stays below 20uA worst case.

- V<sub>dd</sub>: It is the core voltage that powers the overall chip (apart from the IOs). This voltage

is not applied in very low power state condition. When applied, the V<sub>dd\_on</sub> and V<sub>dd</sub> are

at the same voltage. A maximum of 10% variation between the two regions is required.

- V<sub>ddio</sub>: It is the power region dedicated to the IOs. The overall IOs are divided in seven groups and each of them can be powered at different, independent voltages. Some groups may have specific constraint in terms of power voltage range in order to meet specific electrical characteristic compliant to some standards; some of these groups are, for example, in the DDR interface and the 1.1 embedded USB transceiver. There is also a group of IOs called V<sub>ddio\_on</sub> that identifies the IOs that must be always powered (also in the lowest power consumption state of STA2064) in order to make the wake-up possible. The other five regions (called also V<sub>ddiox</sub>) can not be powered while in this state. For more information, please refer to *Chapter 3.6: IO groups on page 16*.

# 3.2 Frequency region partition

STA2064 is designed so that there are two PLLs. PLL1 generates clock frequencies for the ARM core and the internal buses, while the PLL2 generates clock frequencies for each peripheral kernel and also for each peripheral interface. This means that each peripheral receives the clock derived from the PLL1 at its internal interface, then it works with the clock derived from the PLL2. Despite the use of two PLLs, a single system clock input or a single external crystal is needed (in addition to the RTC clock (or crystal)).

## 3.3 Frequency and power range

The core voltage range is 1.25  $\pm 4$  %V while the IO voltage ranges are 1.8  $\pm 10$  %V, 2.5  $\pm$  10 %V and 3.3  $\pm$  10 %V.

Table 2 shows some use cases of STA2064 in NORMAL mode:

Table 2. Frequency and power use cases

| $ m V_{dd}$ and $ m V_{dd_on}$ (V) | Core Freq<br>[MHz] | Bus Freq<br>[MHz] | DDR Freq<br>[MHz] | Sync/Async<br>[S/A] |

|------------------------------------|--------------------|-------------------|-------------------|---------------------|

| 1.2 5(±4%)                         | 533                | 177.67            | 177.67            | S                   |

| 1.2 5(±4%)                         | 533                | 133.25            | 133.25            | S                   |

| 1.2 5(±4%)                         | 533                | 177.67            | 312               | A, DDR2             |

| 1.2 5(±4%)                         | 520                | 208               | 130               | А                   |

| 1.2 5(±4%)                         | 520                | 173.34            | 173.34            | S                   |

| 1.2 5(±4%)                         | 520                | 130               | 130               | S                   |

| 1.2 5(±4%)                         | 520                | 208               | 312               | A, DDR2             |

| 1.2 5(±4%)                         | 494                | 197.6             | 197.6             | S                   |

| 1.2 5(±4%)                         | 494                | 164.67            | 164.67            | S                   |

| 1.2 5(±4%)                         | 494                | 123.5             | 123.5             | S                   |

| 1.2 5(±4%)                         | 494                | 208               | 329.34            | A, DDR2             |

The background of *Table 2* is the maximization of data throughput on the DRAM interface, matching the currently available DRAM speed grades: 133 MHz, 166 MHz and 200 MHz (LP DDR) and 333 MHz (DDR2). Despite this, it is possible to program the ARM core, the internal bus and the DDR to run at different speeds than the ones mentioned in *Table 2* The ARM bus clock and the bus clock are derived from the same common source (VCO of the PLL1) but are asynchronous each other. The DDR frequency can be the same (synchronous) or derived with a different prescaling (1,2,3,4,5,6,8,9 or 10) from the VCO of PLL1 or PLL2 (asynchronous configuration).

STA2064 embeds a complete GPS subsystem where both gate logic and dedicated DSP work together. There are specific constraints in this subsystem in terms of minimum frequency in order to guarantee the target GPS specifications.

In the lowest power consumption state as possible, only  $V_{dd\_on}$  is powered and the target current drawn is 20  $\mu$ A. In this state, the clock is not running and the current leakage is mainly due to the Backup memory. The 20  $\mu$ A current limit has to be considered with Process best (leakage worst case condition),  $V_{dd\_on}$  1.3V (1.25V plus 4% tolerance) and Junction Temperature 50°C (considering, while in this state, the ambient temperature is equal to the junction temperature).

#### 3.4 Power states

The following power states are defined:

- OFF: V<sub>dd\_on</sub> and V<sub>dd</sub> are not applied (all data in the backup RAM is lost): no data retention is kept in the SDRAM

- NORMAL: Each peripheral runs at its nominal speed with the possibility of turning off all the unused peripherals (peripheral kernel clock gated)

- SLOW: PLL1 bypassed. ARM and bus runs at crystal clock. PLL2 runs at its nominal speed. PLL1 can be optionally put in power down

- DOZE: It is like SLOW mode with the ARM running either at 19 MHz or 32 kHz

- STANDBY: PLLs run at their nominal speed. Clocks are gated, ARM in WFI (Wait For Interrupt) state

- DEEP-SLEEP: V<sub>dd</sub> powered off. V<sub>dd\_on</sub> powered (RTC, few GPIOs, backup RAM) and clocked at 32 kHz making the wakeup possible. The context is put in the external SDRAM while in self refresh mode. Only the V<sub>ddio on</sub> region must be powered

- SLEEP: It is like the DEEP-SLEEP mode, with the difference that V<sub>dd</sub> and V<sub>ddio</sub> are also applied and all the PLLs are off (optional for PLL2)

- BACKUP: It is like DEEP-SLEEP, with the difference that the context is not saved in the

external SDRAM. When coming out from Backup to any power state, the ARM core will

execute the first code instruction after 2ms from power on reset release.

While in NORMAL, SLOW AND STANDBY,  $V_{dd\_on}$  and  $V_{dd}$  are the same (10% tolerance between them) and cannot be changed. Also the power to the several IO groups is kept unchanged.

In order to change the  $V_{dd\_on}$  and  $V_{dd}$  values, the system has to transit to either OFF, SLEEP, DEEP-SLEEP or BACKUP and then back to the selected state.

In order to keep the power consumption as low as possible, the target voltage mentioned in DEEP-SLEEP is considered at 1.0V.

A dedicated FSM manages the power state transitions among NORMAL, SLOW, DOZE AND SLEEP. All other states mentioned above are SW variants of the ones managed by the FSM.

Table 3 shows the summary of the power states supported by STA2064.

Table 3. Power mode states

| Power State | 32 kHz | PLL1                             | PLL2                       | V <sub>dd_on</sub>                | V <sub>dd</sub>     | IOs         |

|-------------|--------|----------------------------------|----------------------------|-----------------------------------|---------------------|-------------|

| OFF         | off    | off                              | off                        | off                               | off                 | off         |

| NORMAL      | on     | on                               | on                         | 1.2V to 1.3V                      | =V <sub>dd_on</sub> | 1.7 to 3.6V |

| SLOW        | on     | Off. Bypassed by main oscillator | off (SW can<br>take it on) | 1.2V to 1.3V                      | = <sub>Vdd_on</sub> | 1.7 to 3.6V |

| DOZE        | on     | Off. Bypassed by 32 kHz          | off (SW can<br>take it on) | 1.2V to 1.3V                      | =V <sub>dd_on</sub> | 1.7 to 3.6V |

| STANDBY     | on     | on (clk gated)<br>ARM in WFI     | on (clk gated)             | 1.2V to 1.3V                      | =V <sub>dd_on</sub> | 1.7 to 3.6V |

| SLEEP       | on     | off                              | off (SW can take it on)    | 1.2V to 1.3V<br>(typically 1.25V) | =V <sub>dd_on</sub> | 1.7 to 3.6V |

14/19 Doc ID 16057 Rev 3

| Power State | 32 kHz | PLL1 | PLL2 | $V_{\mathrm{dd\_on}}$             | $V_{dd}$            | IOs               |

|-------------|--------|------|------|-----------------------------------|---------------------|-------------------|

| OFF         | off    | off  | off  | off                               | off                 | off               |

| NORMAL      | on     | on   | on   | 1.2V to 1.3V                      | =V <sub>dd_on</sub> | 1.7 to 3.6V       |

| DEEP-SLEEP  | on     | off  | off  | 1.2V to 1.3V<br>(typically 1.25V) | off                 | Refer section 3.5 |

| BACKUP      | on     | off  | off  | 1.2V to 1.3V<br>(typically 1.25V) | off                 | Refer section 3.5 |

Table 3. Power mode states (continued)

## 3.5 System wakeup and power down

Typically the system using STA2064 will never be powered off, even when the user switches the device off using the main power switch. The main power switch works in a way that puts the device either in Backup or in DEEP-SLEEP mode. In this state, the only blocks within STA2064 that are powered are the RTC, PMU, PWL, SRC and the backup RAM; at system level, only the  $V_{dd\ on}$  is powered.

The following wakeup methods are possible:

- The user presses a button on the unit that causes all of the main power supplies to start. After an appropriate delay, the processor's reset line is lifted and allows the code to start executing

- The internal alarm feature triggers a dedicated signal that will cause all of the main supplies to start. After an appropriate delay, the processor's reset line is lifted and allows the code to start execution

Considering the above mentioned wakeup system, while in DEEP-SLEEP and in BACKUP state also, some dedicated IO lines must be powered:

- POR (input)

- POWEREN (output)

- VDDOK and BATOK (input)

- WAKE (input)

- 32 kHz crystal (SXTALI and SXTALO)

- OSC32KOUT (output)

In order to keep the external DRAM in self refresh while in DEEP-SLEEP, CKE of the DRAM must be kept low. Since all the IOs are not powered in DEEP-SLEEP, in order to make the self refresh working, an external pulldown resistor is needed.

#### 3.6 10 groups

V<sub>ddio</sub> is split into the following groups:

- V<sub>ddio on</sub> (a)

- V<sub>ddiox</sub> (This is split into 5 types: V<sub>ddioA</sub>, V<sub>ddioB</sub>, V<sub>ddioC</sub>, V<sub>ddioD</sub>, V<sub>ddioE</sub>) (b)

- V<sub>USB</sub> (USB 2.0 PHY transceiver)

The IO supply type and corresponding pads details are as follows:

- V<sub>ddio\_on</sub>: Power Supply pins for the IO buffers of the always ON section. It supplies POR, PWREN, VDDOK, BATOK, WAKE, SXTALI, SXTALO, OSC32KOUT

- V<sub>ddioA</sub>: Power Supply pins for the IO buffers. It supplies most GPIOs and dedicated pads for JTAG, MMC0 and GPS

- V<sub>ddioB</sub>: Power Supply pins for the IO buffers. Supplies to the CLCD IOs

- V<sub>ddioC</sub>: Power Supply pins for the IO buffers. Supplies the SDMC IOs

- $V_{ddioD}$ : Power Supply pins for the IO buffers. Supplies the following IOs: GPIO64:67, GPIO96:127 and dedicated pads for TEST (SCANEN, TAPSEL)

- V<sub>ddioE</sub>: Power Supply pins for the IO buffers. Supplies the following IOs: CAN, MSP, GPIOs related to SDMMC functionality

- V<sub>USB</sub>: 3.3V USB PAD power supply

- V<sub>TSC</sub>: 3.3V Touchscreen PAD power supply.

16/19 Doc ID 16057 Rev 3

a. Vddio\_on is always 1.8V.

b. When V<sub>ddio</sub> domain A is powered with 2.5V (its PSW bit = 1), all other V<sub>ddio</sub> domains (B, D, E) should be powered with same voltage level i.e 2.5V.  $V_{ddio}$  domain C and  $V_{ddio\_coreon}$  is always powered with 1.8V. The vice-versa is not true. So for example, application can power voltage bank B with 2.5V (keeping its PSW=1) and V<sub>ddio</sub>A as 1.8V.

STA2064 Package information

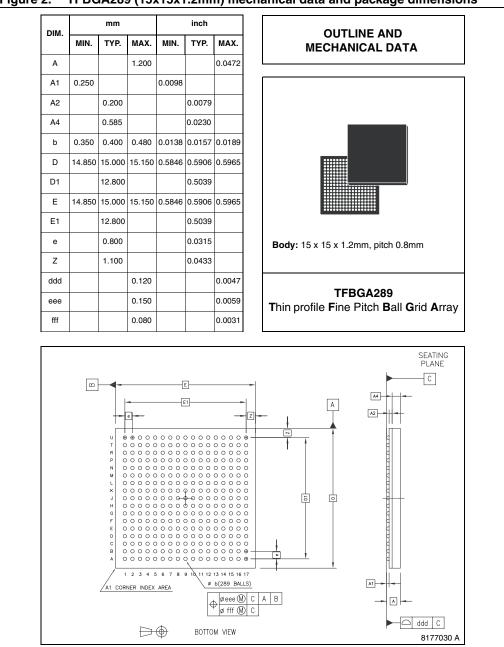

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>.

ECOPACK® is an ST trademark.

Figure 2. TFBGA289 (15x15x1.2mm) mechanical data and package dimensions

57

Doc ID 16057 Rev 3 17/19

Revision history STA2064

# 5 Revision history

Table 4. Document revision history

| Date        | Revision                           | Changes                                                                                     |  |

|-------------|------------------------------------|---------------------------------------------------------------------------------------------|--|

| 22-Jul-2009 | 1                                  | Initial release.                                                                            |  |

| 13-Oct-2009 | 2 Updated features list on page 1. |                                                                                             |  |

| 19-Oct-2009 | 3                                  | Updated "Standard interfaces" feature on cover page. Updated Section 2.6.2: UART on page 8. |  |

18/19 Doc ID 16057 Rev 3

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION). OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16057 Rev 3

19/19