## ARM Cortex<sup>TM</sup>-M0 32-BIT MICROCONTROLLER

# NuMicro<sup>™</sup> NUC100 Series NUC130/NUC140 Technical Reference Manual

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

#### Contents

| 1 |       |                                                            | SCRIPTION                                             |     |  |  |  |  |  |  |

|---|-------|------------------------------------------------------------|-------------------------------------------------------|-----|--|--|--|--|--|--|

| 2 |       |                                                            |                                                       |     |  |  |  |  |  |  |

|   | 2.1   | 2.1 NuMicro <sup>™</sup> NUC130 Features – Automotive Line |                                                       |     |  |  |  |  |  |  |

|   | 2.2   |                                                            | o™ NUC140 Features – Connectivity Line                |     |  |  |  |  |  |  |

| 3 | PARTS | S INFOR                                                    | MATION LIST AND PIN CONFIGURATION                     | 21  |  |  |  |  |  |  |

|   | 3.1   | NuMicr                                                     | NuMicro™ NUC130 Products Selection Guide              |     |  |  |  |  |  |  |

|   |       | 3.1.1                                                      | 3.1.1 NuMicro™ NUC130 Automotive Line Selection Guide |     |  |  |  |  |  |  |

|   | 3.2   | NuMicr                                                     | o™ NUC140 Products Selection Guide                    | 22  |  |  |  |  |  |  |

|   |       | 3.2.1                                                      | NuMicro™ NUC140 Connectivity Line Selection Guide     | .22 |  |  |  |  |  |  |

|   | 3.3   |                                                            | nfiguration                                           |     |  |  |  |  |  |  |

|   |       | 3.3.1                                                      | -<br>NuMicro™ NUC130/NUC140 Pin Diagram               | 23  |  |  |  |  |  |  |

|   | 3.4   |                                                            | scription                                             |     |  |  |  |  |  |  |

|   |       |                                                            | NuMicro™ NUC130/NUC140 Pin Description                |     |  |  |  |  |  |  |

| 4 |       |                                                            | AM                                                    |     |  |  |  |  |  |  |

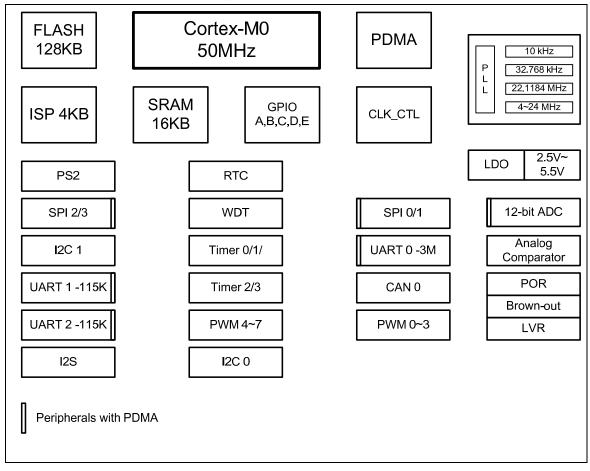

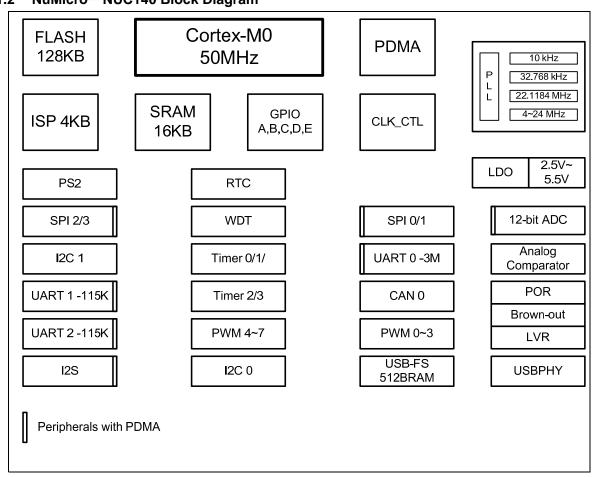

| - | 4.1   | NuMicro™NUC130/NUC140 Block Diagram                        |                                                       |     |  |  |  |  |  |  |

|   |       |                                                            | NuMicro™ NUC130 Block Diagram                         |     |  |  |  |  |  |  |

|   |       |                                                            | NuMicro™ NUC140 Block Diagram                         |     |  |  |  |  |  |  |

| 5 | FUNCT |                                                            | DESCRIPTION                                           |     |  |  |  |  |  |  |

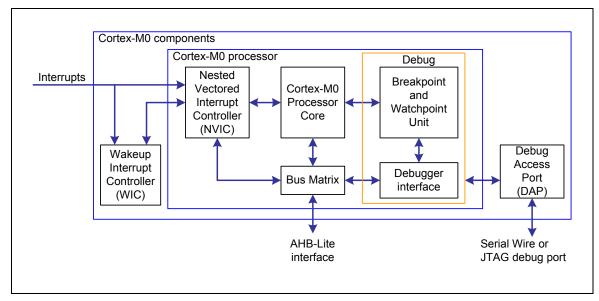

| 0 | 5.1   |                                                            | Cortex™-M0 Core                                       |     |  |  |  |  |  |  |

|   | 5.2   | System Manager                                             |                                                       |     |  |  |  |  |  |  |

|   |       | 5.2.1                                                      | Overview                                              | .48 |  |  |  |  |  |  |

|   |       | 5.2.2                                                      | System Reset                                          | .48 |  |  |  |  |  |  |

|   |       | 5.2.3                                                      | System Power Distribution                             | .49 |  |  |  |  |  |  |

|   |       | 5.2.4                                                      | System Memory Map                                     | .51 |  |  |  |  |  |  |

|   |       |                                                            | System Manager Control Registers                      |     |  |  |  |  |  |  |

|   |       |                                                            | System Timer (SysTick)                                |     |  |  |  |  |  |  |

|   |       |                                                            | Nested Vectored Interrupt Controller (NVIC)           |     |  |  |  |  |  |  |

|   | 5.0   |                                                            | System Control Register                               |     |  |  |  |  |  |  |

|   | 5.3   |                                                            | Controller 1                                          |     |  |  |  |  |  |  |

|   |       |                                                            | Overview                                              |     |  |  |  |  |  |  |

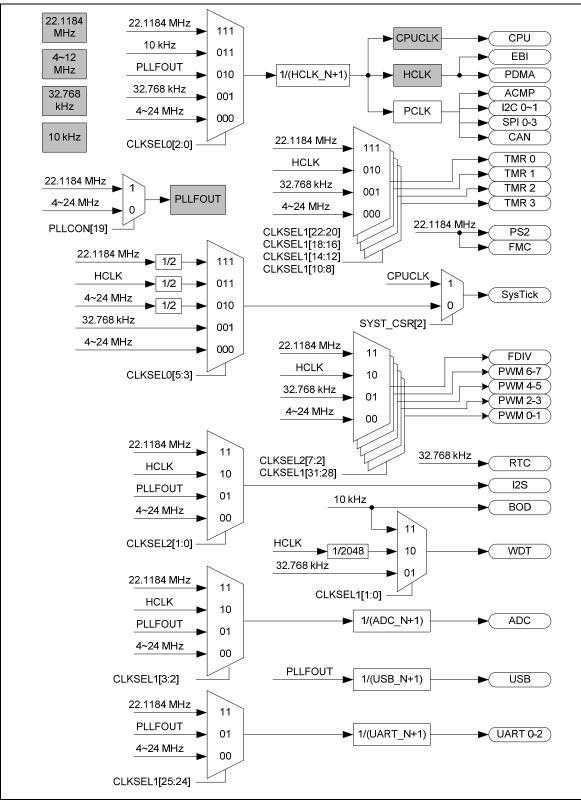

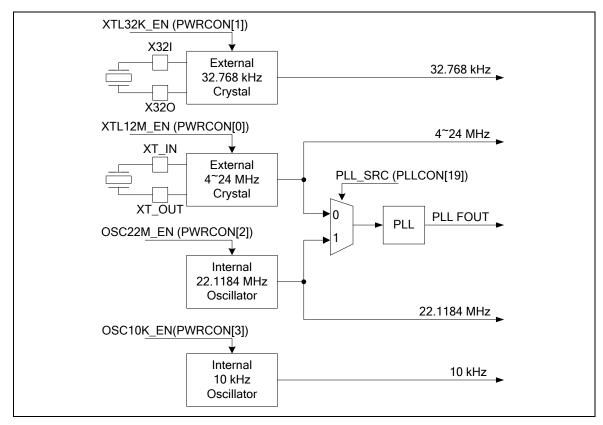

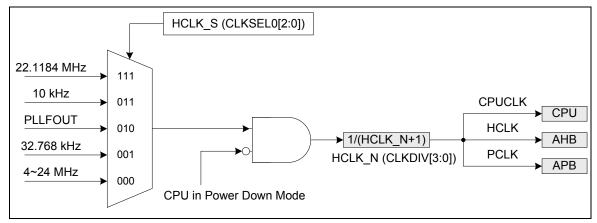

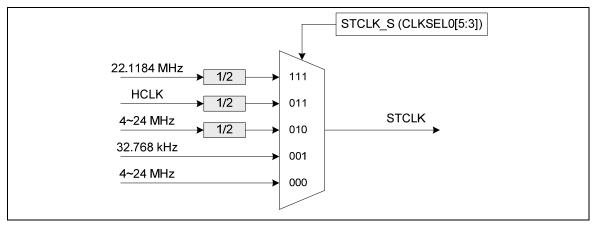

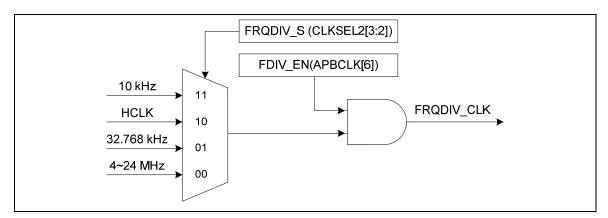

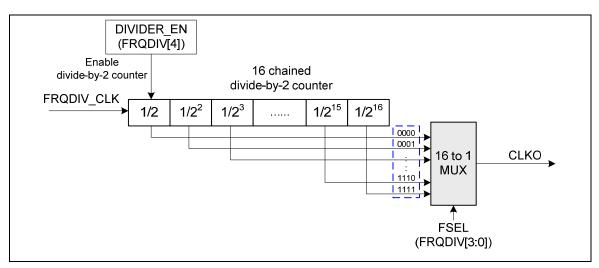

|   |       |                                                            | Clock Generator                                       |     |  |  |  |  |  |  |

|   |       |                                                            | System Clock and SysTick Clock                        |     |  |  |  |  |  |  |

|   |       |                                                            | Peripherals Clock                                     |     |  |  |  |  |  |  |

|   |       |                                                            | Power Down Mode Clock                                 |     |  |  |  |  |  |  |

|   |       |                                                            | Register Map                                          |     |  |  |  |  |  |  |

|   |       |                                                            | Register Description                                  |     |  |  |  |  |  |  |

|   | 5.4   |                                                            | evice Controller (USB)                                |     |  |  |  |  |  |  |

|   |       |                                                            |                                                       |     |  |  |  |  |  |  |

# nuvoton

|      | 5.4.1              | Overview                                                     | 150 |

|------|--------------------|--------------------------------------------------------------|-----|

|      | 5.4.2              | Features                                                     | 150 |

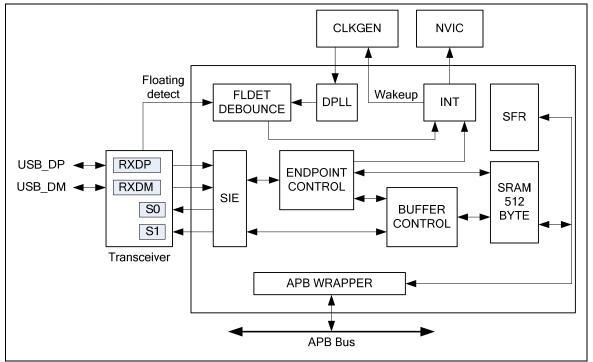

|      | 5.4.3              | Block Diagram                                                | 151 |

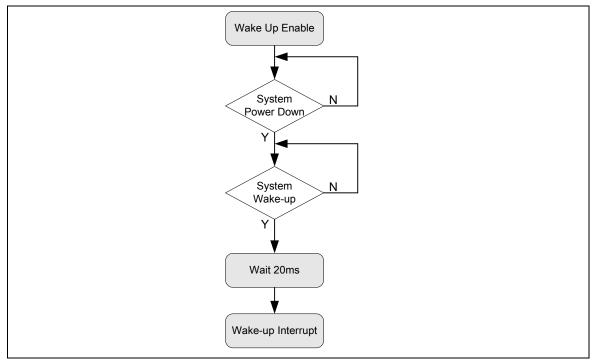

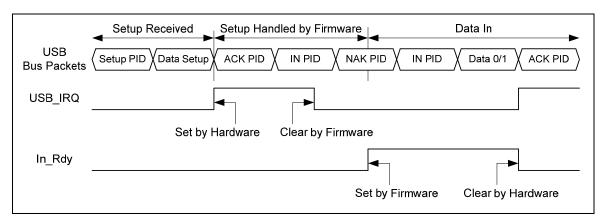

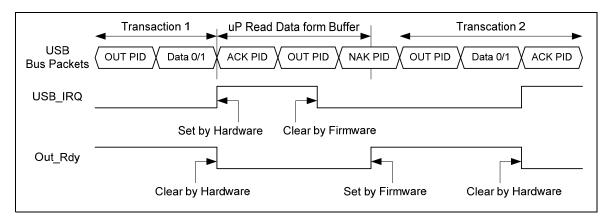

|      | 5.4.4              | Function Description                                         | 152 |

|      | 5.4.5              | Register and Memory Map                                      | 156 |

|      | 5.4.6              | Register Description                                         | 158 |

| 5.5  | Gene               | ral Purpose I/O (GPIO)                                       | 175 |

|      | 5.5.1              | Overview                                                     | 175 |

|      | 5.5.2              | Features                                                     | 175 |

|      | 5.5.3              | Function Description                                         | 176 |

|      | 5.5.4              | Register Map                                                 | 178 |

|      | 5.5.5              | Register Description                                         |     |

| 5.6  | I <sup>2</sup> C S | erial Interface Controller (Master/Slave) (I <sup>2</sup> C) | 195 |

|      | 5.6.1              | Overview                                                     |     |

|      | 5.6.2              | Features                                                     |     |

|      | 5.6.3              | Function Description                                         |     |

|      | 5.6.4              | Protocol Registers                                           |     |

|      | 5.6.5              | Register Map                                                 |     |

|      | 5.6.6              | Register Description                                         |     |

|      | 5.6.7              | Modes of Operation                                           |     |

|      | 5.6.8              | Data Transfer Flow in Five Operating Modes                   |     |

| 5.7  | PWM                | Generator and Capture Timer (PWM)                            |     |

|      | 5.7.1              | Overview                                                     |     |

|      | 5.7.2              | Features                                                     |     |

|      | 5.7.3              | Block Diagram                                                | 221 |

|      | 5.7.4              | Function Description                                         |     |

|      | 5.7.5              | Register Map                                                 | 232 |

|      | 5.7.6              | Register Description                                         |     |

| 5.8  | Real               | Time Clock (RTC)                                             | 257 |

|      | 5.8.1              | Overview                                                     | 257 |

|      | 5.8.2              | Features                                                     |     |

|      | 5.8.3              | Block Diagram                                                |     |

|      | 5.8.4              | Function Description                                         |     |

|      | 5.8.5              | Register Map                                                 |     |

|      | 5.8.6              | Register Description                                         |     |

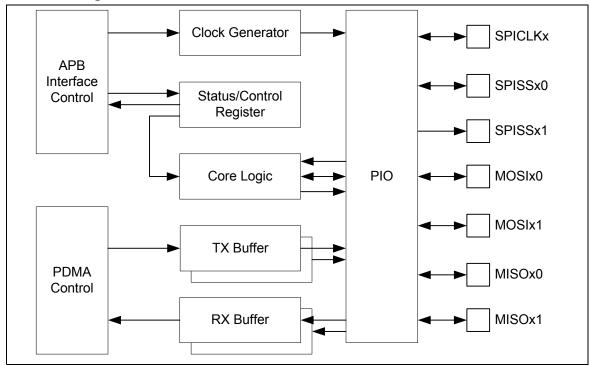

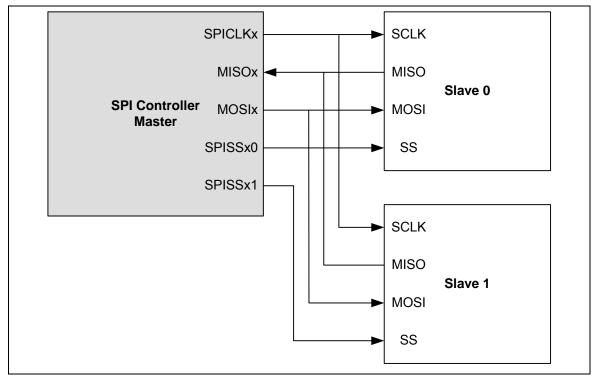

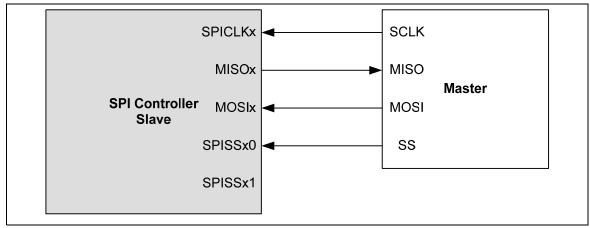

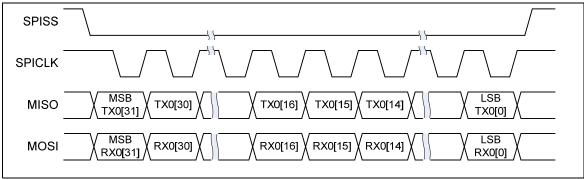

| 5.9  |                    | l Peripheral Interface (SPI)                                 |     |

|      | 5.9.1              | Overview                                                     |     |

|      | 5.9.2              | Features                                                     |     |

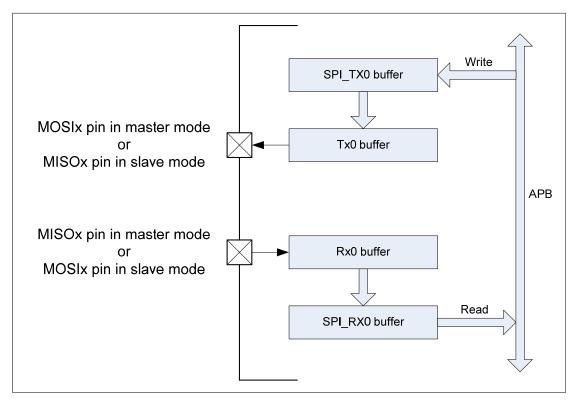

|      | 5.9.3              | Block Diagram                                                |     |

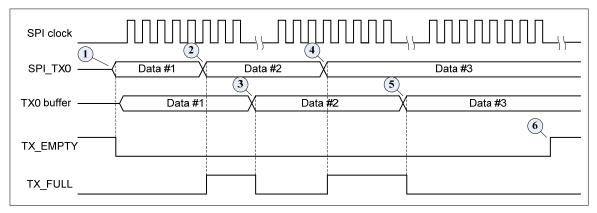

|      | 5.9.4              | Function Description                                         |     |

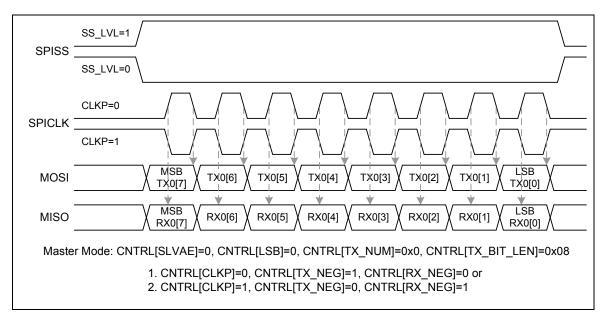

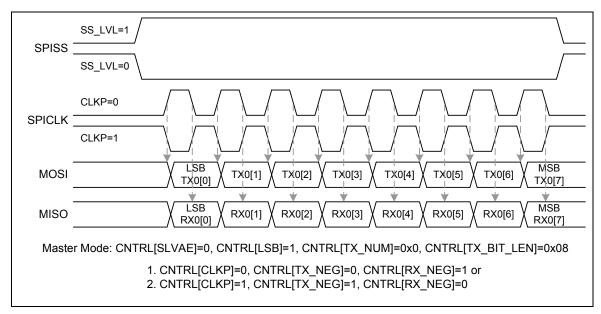

|      | 5.9.5              | Timing Diagram                                               |     |

|      | 5.9.6              | Programming Examples                                         |     |

|      | 5.9.7              | Register Map                                                 |     |

|      | 5.9.8              | Register Description                                         |     |

| 5.10 |                    | <sup>r</sup> Controller (TMR)                                |     |

| 0.10 |                    |                                                              |     |

Publication Release Date: June 14, 2011 Revision V2.01

|      | 5.10.1              | Overview                                |                                         |

|------|---------------------|-----------------------------------------|-----------------------------------------|

|      | 5.10.2              | Features                                |                                         |

|      | 5.10.3              | Block Diagram                           |                                         |

|      | 5.10.4              | -                                       |                                         |

|      | 5.10.5              | ·                                       |                                         |

|      | 5.10.6              |                                         |                                         |

| 5.11 | Watch               | -                                       |                                         |

| 0.11 |                     | ,                                       |                                         |

|      | 5.11.1              |                                         |                                         |

|      | 5.11.2              |                                         |                                         |

|      | 5.11.3              |                                         |                                         |

|      | 5.11.4              | Register Map                            |                                         |

|      | 5.11.5              | Register Description                    |                                         |

| 5.12 | UART                | Interface Controller (UART)             |                                         |

|      | 5.12.1              | Overview                                |                                         |

|      | 5.12.2              | Features                                |                                         |

|      | 5.12.3              |                                         |                                         |

|      | 5.12.4              | -                                       |                                         |

|      | 5.12.5              |                                         | mode                                    |

|      | 5.12.6              |                                         |                                         |

|      | 5.12.7              |                                         |                                         |

|      | 5.12.7              |                                         |                                         |

| E 40 |                     | •                                       |                                         |

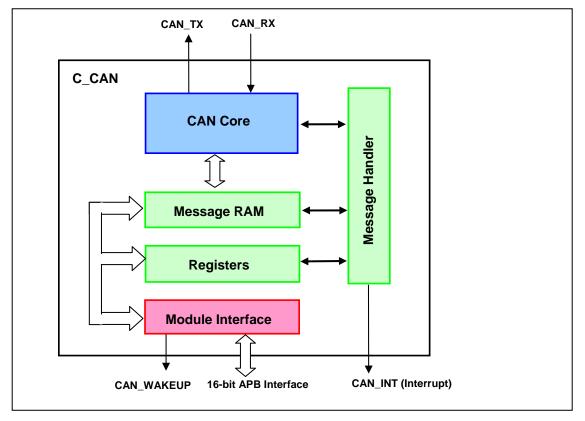

| 5.13 | Contro              |                                         |                                         |

|      | 5.13.1              | Overview                                |                                         |

|      | 5.13.2              | Features                                |                                         |

|      | 5.13.3              | Block Diagram                           |                                         |

|      | 5.13.4              | Functional Description                  |                                         |

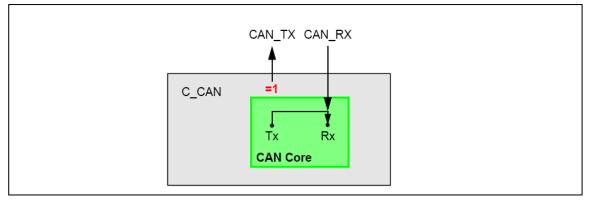

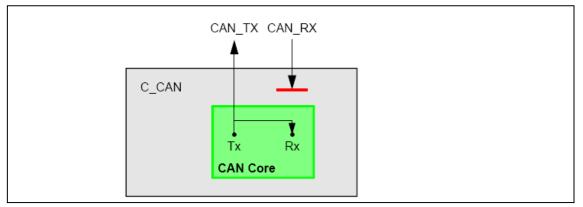

|      | 5.13.5              | Test Mode                               |                                         |

|      | 5.13.6              | CAN Communications                      |                                         |

|      | 5.13.7              | Register Description                    |                                         |

|      | 5.13.8              |                                         |                                         |

|      | 5.13.9              |                                         |                                         |

| 5.14 | PS/2 D              |                                         |                                         |

| 0.11 |                     | ( , , , , , , , , , , , , , , , , , , , |                                         |

|      |                     |                                         |                                         |

|      | 5.14.2              |                                         |                                         |

|      | 5.14.3              | C C                                     |                                         |

|      | 5.14.4              | •                                       |                                         |

|      | 5.14.5              |                                         |                                         |

|      | 5.14.6              | -                                       |                                         |

| 5.15 | I <sup>2</sup> S Co | ntroller (I <sup>2</sup> S)             |                                         |

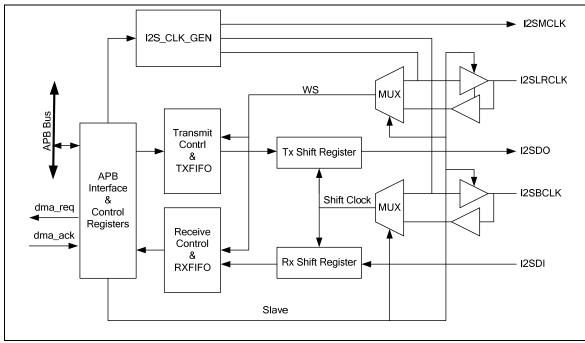

|      | 5.15.1              | Overview                                |                                         |

|      | 5.15.2              | Features                                |                                         |

|      | 5.15.3              | Block Diagram                           |                                         |

|      | 5.15.4              | •                                       |                                         |

|      | 5.15.5              |                                         |                                         |

|      | 5.15.6              | •                                       |                                         |

| 5.16 |                     | -                                       |                                         |

| 5.10 | Analog              |                                         | Publication Release Date: June 14, 2011 |

|      |                     | - 4 -                                   | Revision V2.01                          |

# nuvoTon

6

7

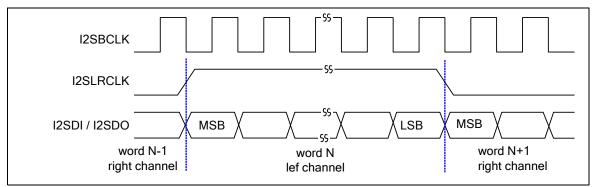

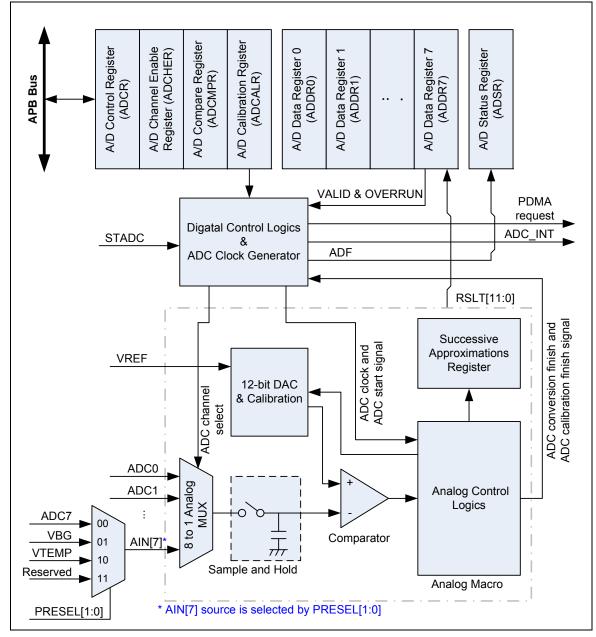

|      | 5.16.1 Overview                                                            | 466 |

|------|----------------------------------------------------------------------------|-----|

|      | 5.16.2 Features                                                            | 466 |

|      | 5.16.3 Block Diagram                                                       | 467 |

|      | 5.16.4 Functional Description                                              |     |

|      | 5.16.5 Register Map                                                        |     |

|      | 5.16.6 Register Description                                                |     |

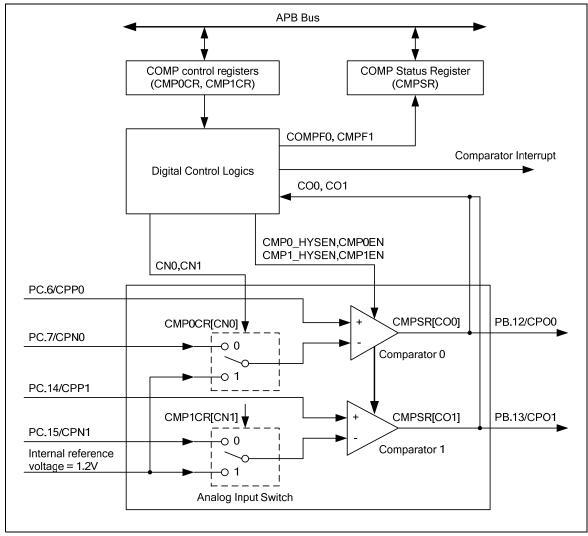

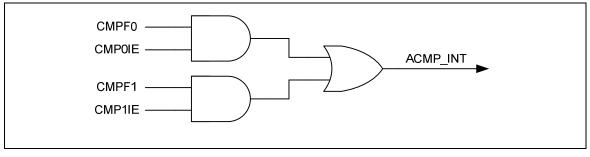

| 5.17 | Analog Comparator (CMP)                                                    |     |

|      | 5.17.1 Overview                                                            |     |

|      | 5.17.2 Features                                                            |     |

|      | 5.17.3 Block Diagram                                                       |     |

|      | 5.17.4 Functional Description                                              |     |

|      | 5.17.5 Register Map                                                        |     |

| 5 40 | 5.17.6 Register Description                                                |     |

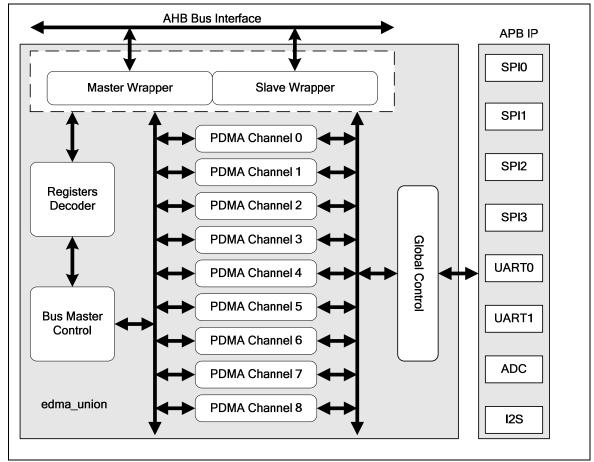

| 5.18 | PDMA Controller (PDMA)                                                     |     |

|      | 5.18.1 Overview                                                            |     |

|      | 5.18.2 Features                                                            |     |

|      | 5.18.3 Block Diagram                                                       |     |

|      | 5.18.4 Function Description                                                |     |

|      | 5.18.5 Register Map                                                        |     |

| E 10 | 5.18.6 Register Description                                                |     |

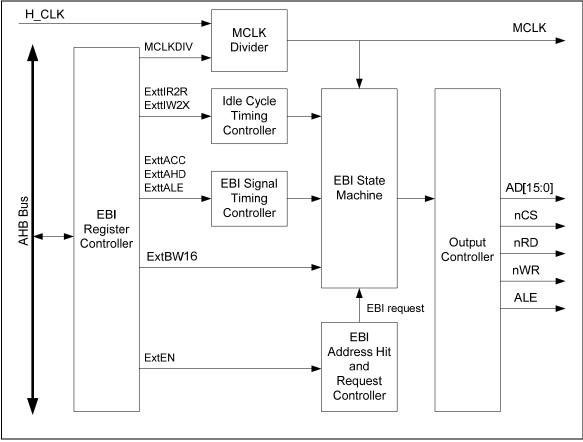

| 5.19 | External Bus Interface (EBI)                                               |     |

|      | 5.19.1 Overview                                                            |     |

|      | 5.19.2 Features<br>5.19.3 Block Diagram                                    |     |

|      | <ul><li>5.19.3 Block Diagram</li><li>5.19.4 Function Description</li></ul> |     |

|      | 5.19.5 Register Map                                                        |     |

|      | 5.19.6 Register Description                                                |     |

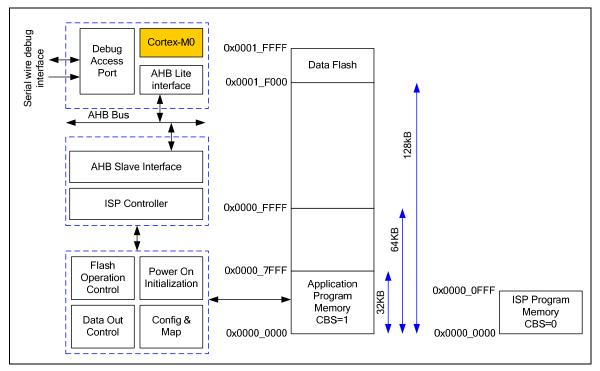

| FLAS | H MEMORY CONTROLLER (FMC)                                                  |     |

| 6.1  | Overview                                                                   |     |

| 6.2  | Features                                                                   |     |

| 6.3  | Block Diagram                                                              |     |

| 6.4  | Flash Memory Organization                                                  |     |

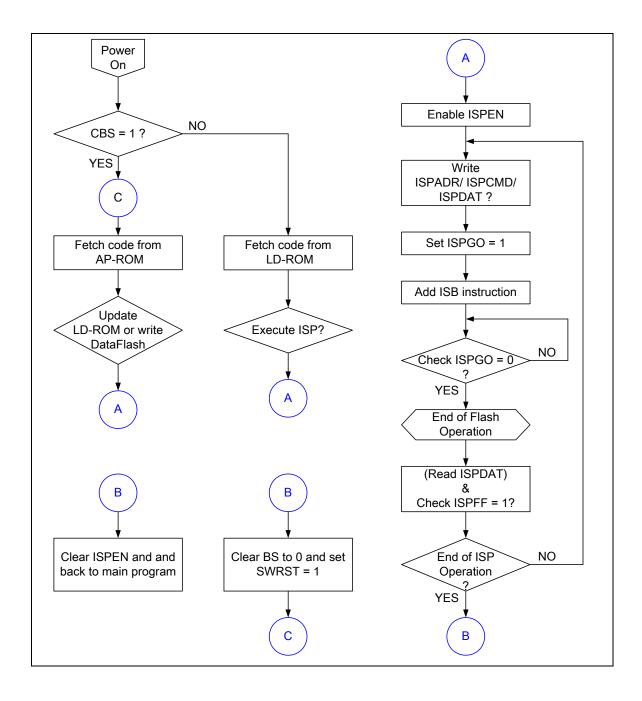

| 6.5  | Boot Selection                                                             |     |

| 6.6  | Data Flash                                                                 |     |

| 6.7  | User Configuration                                                         |     |

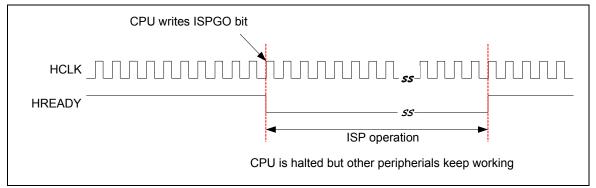

| 6.8  | In System Program (ISP)                                                    |     |

|      | 6.8.1 ISP Procedure                                                        | 539 |

| 6.9  | Flash Control Register Map                                                 |     |

| 6.10 | Flash Control Register Description                                         |     |

| ELEC | TRICAL CHARACTERISTICS                                                     | 552 |

| 7.1  | Absolute Maximum Ratings                                                   |     |

| 7.2  | DC Electrical Characteristics                                              | 553 |

|      |                                                                            |     |

|   |       | 7.2.1   | NuMicro™ NUC130/NUC140 DC Electrical Characteristics | .553 |

|---|-------|---------|------------------------------------------------------|------|

|   | 7.3   | AC Ele  | ectrical Characteristics                             | 557  |

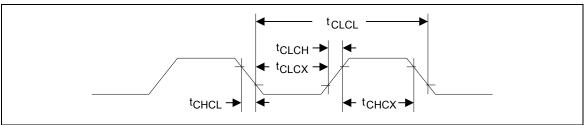

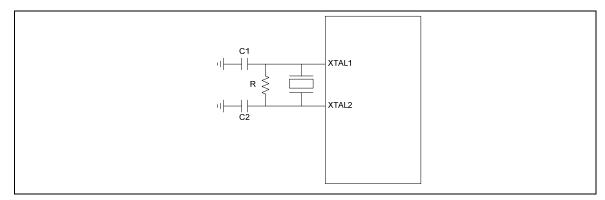

|   |       | 7.3.1   | External 4~24 MHz High Speed Oscillator              | .557 |

|   |       | 7.3.2   | External 4~24 MHz High Speed Crystal                 | .557 |

|   |       | 7.3.3   | External 32.768 kHz Low Speed Crystal                | .559 |

|   |       | 7.3.4   | Internal 22.1184 MHz High Speed Oscillator           | .559 |

|   |       | 7.3.5   | Internal 10 kHz Low Speed Oscillator                 | .559 |

|   | 7.4   | Analog  | g Characteristics                                    | 560  |

|   |       | 7.4.1   | Specification of 12-bit SARADC                       | .560 |

|   |       | 7.4.2   | Specification of LDO and Power management            | .561 |

|   |       | 7.4.3   | Specification of Low Voltage Reset                   | .562 |

|   |       | 7.4.4   | Specification of Brown-Out Detector                  | .562 |

|   |       | 7.4.5   | Specification of Power-On Reset (5 V)                | .562 |

|   |       | 7.4.6   | Specification of Temperature Sensor                  | .563 |

|   |       | 7.4.7   | Specification of Comparator                          | .563 |

|   |       | 7.4.8   | Specification of USB PHY                             | .564 |

|   | 7.5   | SPI Dy  | namic Characteristics                                | 565  |

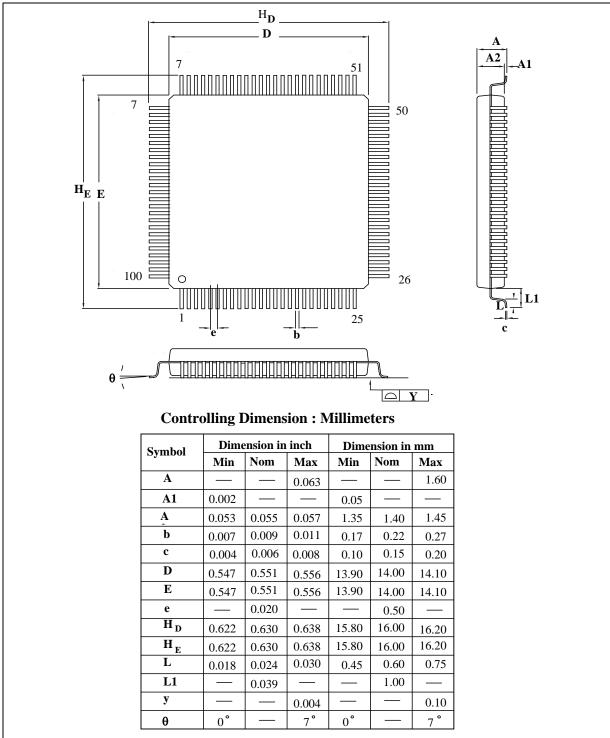

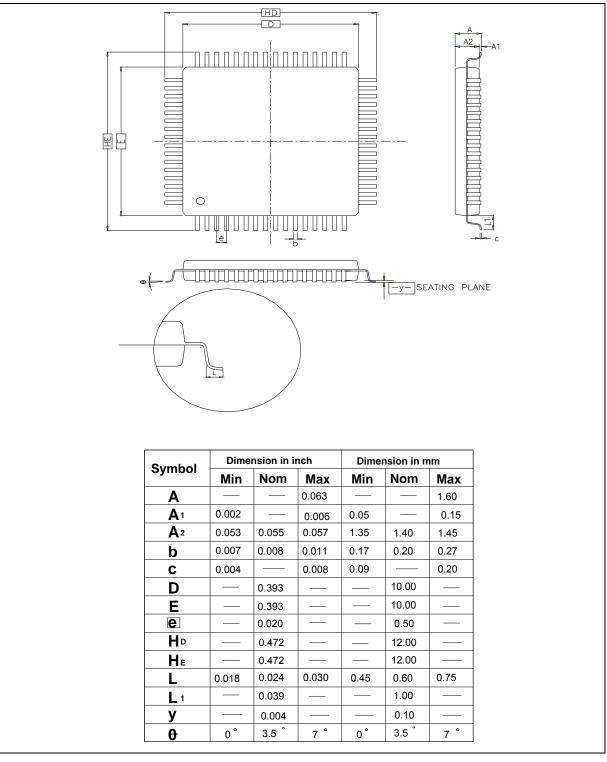

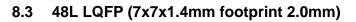

| 8 | PACKA | AGE DI  | MENSIONS                                             | 567  |

|   | 8.1   | 100L L  | .QFP (14x14x1.4 mm footprint 2.0mm)                  | 567  |

|   | 8.2   | 64L L0  | QFP (10x10x1.4mm footprint 2.0 mm)                   | 568  |

|   | 8.3   | 48L L0  | QFP (7x7x1.4mm footprint 2.0mm)                      | 569  |

| 9 | REVIS | ION HIS | STORY                                                | 570  |

### Figures

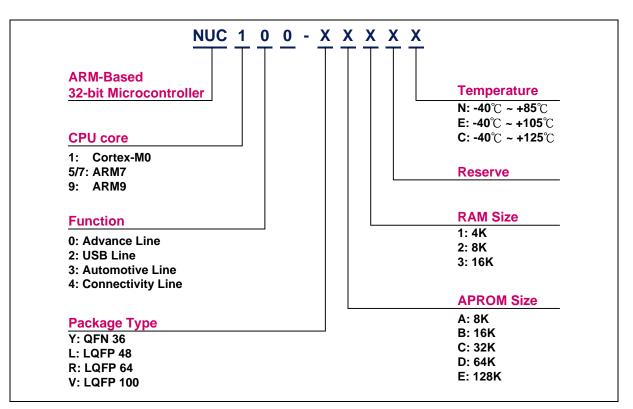

| Figure 3-1 NuMicro™ NUC100 Series selection code              | 22    |

|---------------------------------------------------------------|-------|

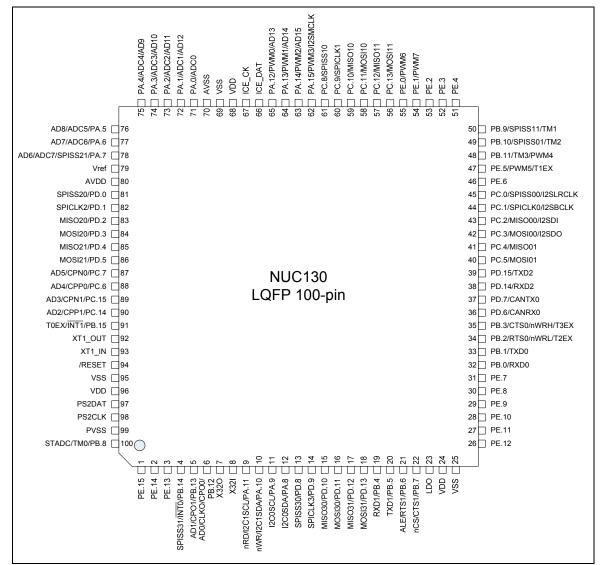

| Figure 3-2 NuMicro™ NUC130 LQFP 100-pin Pin Diagram           | 23    |

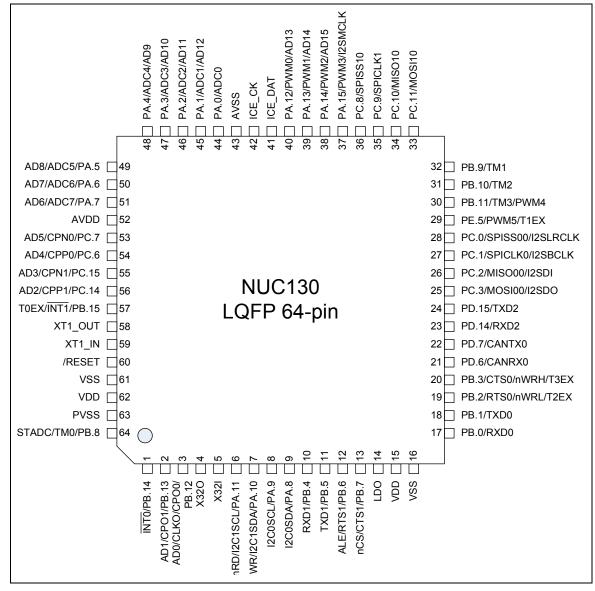

| Figure 3-3 NuMicro™ NUC130 LQFP 64-pin Pin Diagram            | 24    |

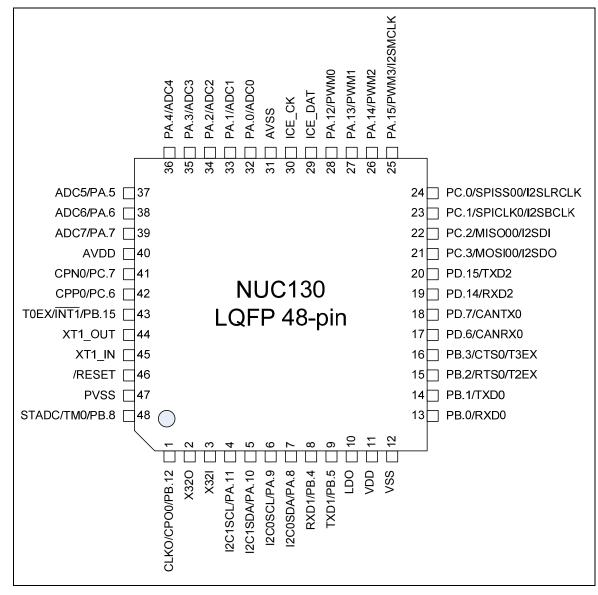

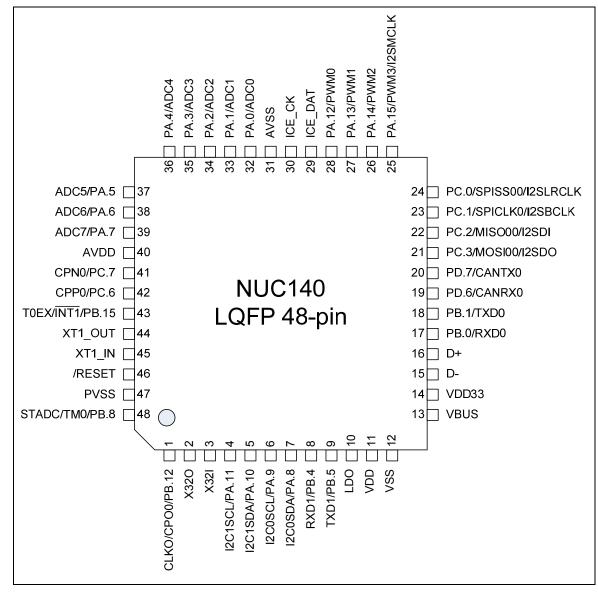

| Figure 3-4 NuMicro™ NUC130 LQFP 48-pin Pin Diagram            | 25    |

| Figure 3-5 NuMicro™ NUC140 LQFP 100-pin Pin Diagram           | 26    |

| Figure 3-6 NuMicro™ NUC140 LQFP 64-pin Pin Diagram            | 27    |

| Figure 3-7 NuMicro™ NUC140 LQFP 48-pin Pin Diagram            | 28    |

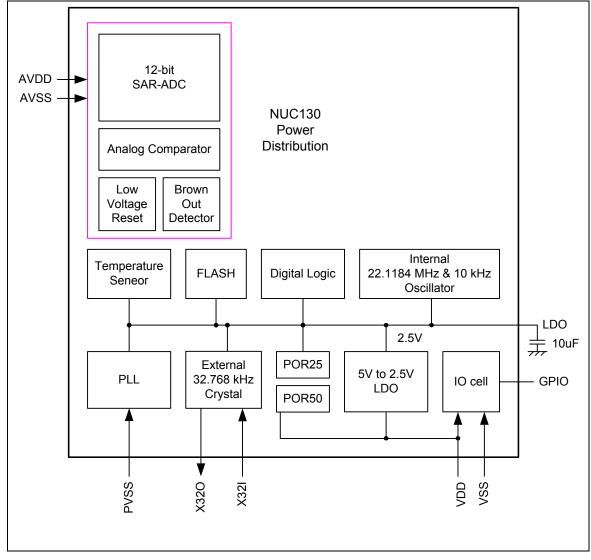

| Figure 4-1 NuMicro™ NUC130 Block Diagram                      | 44    |

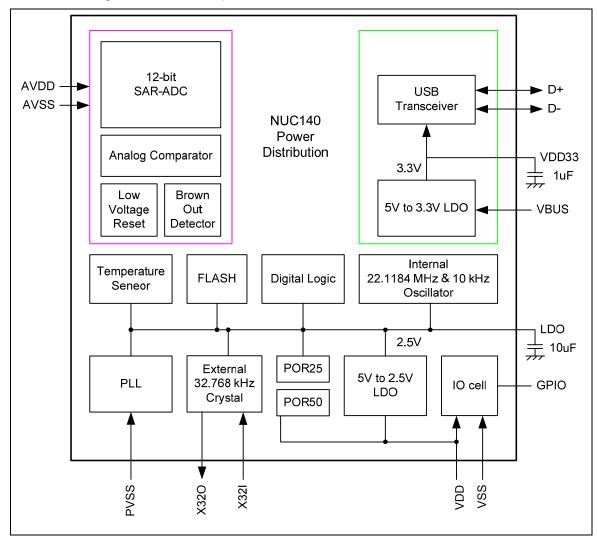

| Figure 4-2 NuMicro™ NUC140 Block Diagram                      | 45    |

| Figure 5-1 Functional Controller Diagram                      | 46    |

| Figure 5-2 NuMicro™ NUC140 Power Distribution Diagram         | 49    |

| Figure 5-3 NuMicro™ NUC130 Power Distribution Diagram         | 50    |

| Figure 5-4 Clock generator global view diagram                | . 126 |

| Figure 5-5 Clock generator block diagram                      | . 127 |

| Figure 5-6 System Clock Block Diagram                         | . 128 |

| Figure 5-7 SysTick Clock Control Block Diagram                | . 128 |

| Figure 5-8 Clock Source of Frequency Divider                  | . 130 |

| Figure 5-9 Block Diagram of Frequency Divider                 | . 130 |

| Figure 5-10 USB Block Diagram                                 | . 151 |

| Figure 5-11 Wake-up Interrupt Operation Flow                  | . 153 |

| Figure 5-12 Endpoint SRAM Structure                           | . 154 |

| Figure 5-13 Setup Transaction followed by Data in Transaction | . 155 |

| Figure 5-14 Data Out Transfer                                 | . 156 |

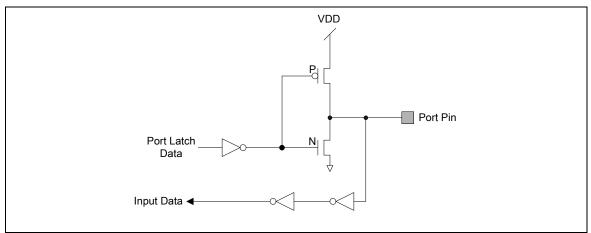

| Figure 5-15 Push-Pull Output                                  | . 176 |

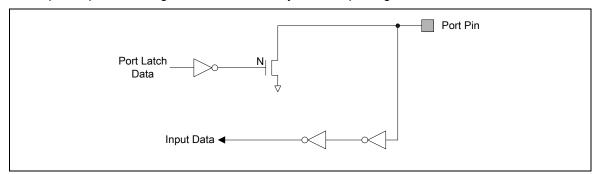

| Figure 5-16 Open-Drain Output                                 | . 177 |

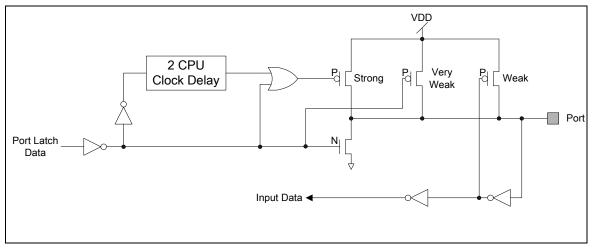

| Figure 5-17 Quasi-bidirectional I/O Mode                      | . 177 |

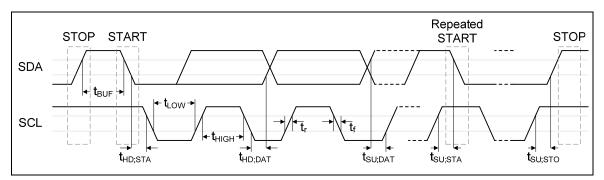

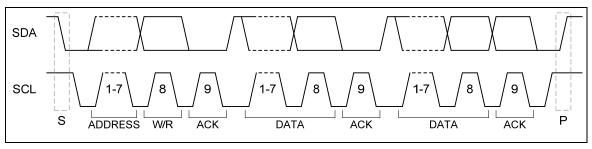

| Figure 5-18 I <sup>2</sup> C Bus Timing                       |       |

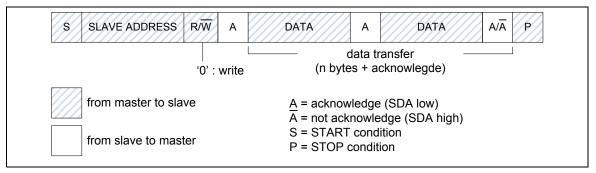

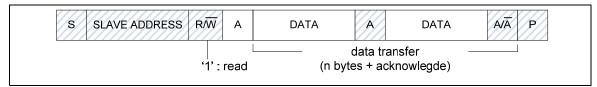

| Figure 5-19 I <sup>2</sup> C Protocol                         | . 197 |

| Figure 5-20 Master Transmits Data to Slave                    | . 197 |

| Figure 5-21 Master Reads Data from Slave                      | . 197 |

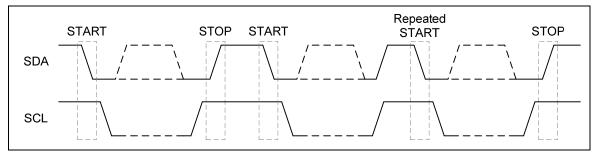

| Figure 5-22 START and STOP condition                          |       |

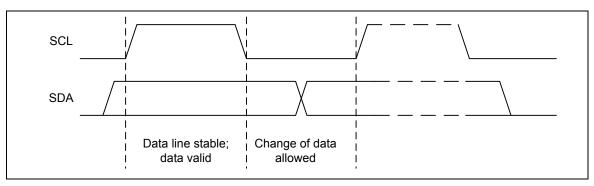

| Figure 5-23 Bit Transfer on the I <sup>2</sup> C bus          | . 199 |

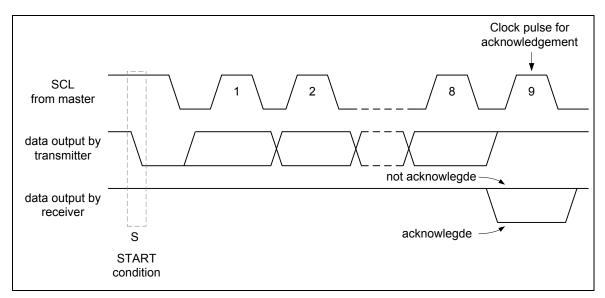

| Figure 5-24 Acknowledge on the I <sup>2</sup> C bus           |       |

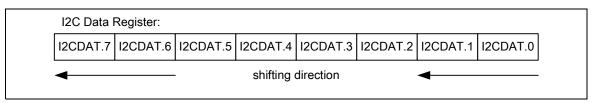

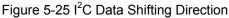

| Figure 5-25 I <sup>2</sup> C Data Shifting Direction          |       |

| Publication Release Date: June 14.                            | 2011  |

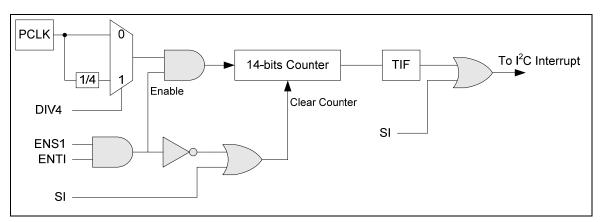

| Figure 5-26: I <sup>2</sup> C Time-out Count Block Diagram        | 202 |

|-------------------------------------------------------------------|-----|

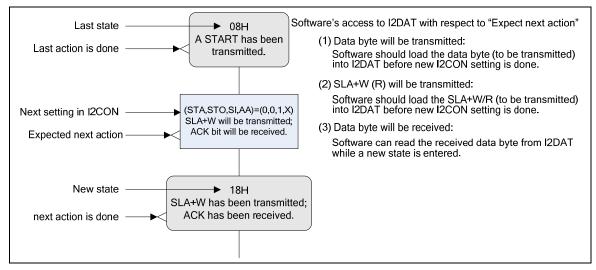

| Figure 5-27 Legend for the following five figures                 | 213 |

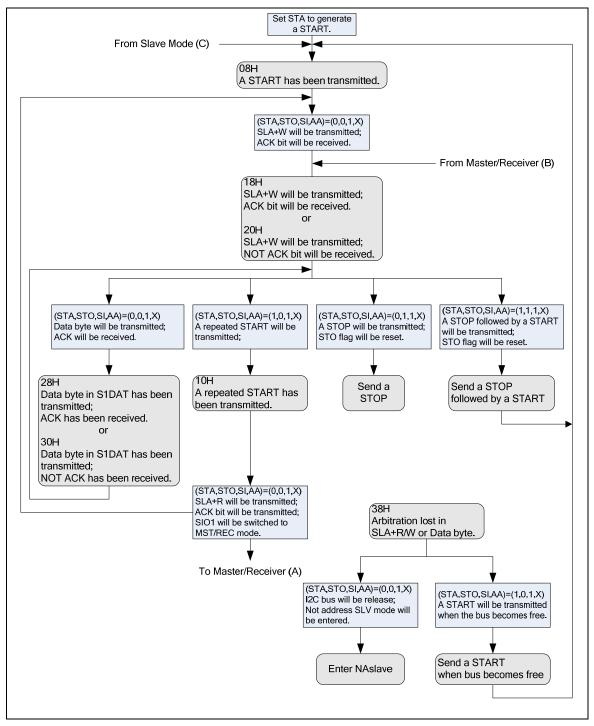

| Figure 5-28 Master Transmitter Mode                               |     |

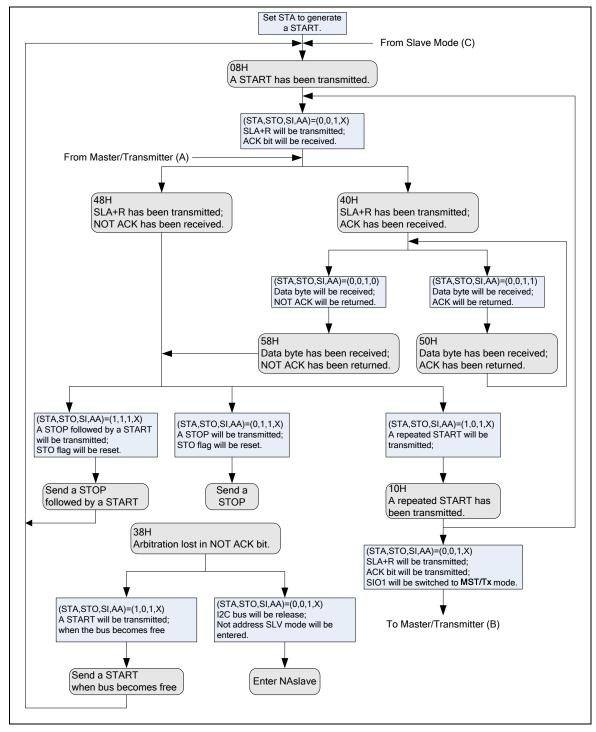

| Figure 5-29 Master Receiver Mode                                  | 215 |

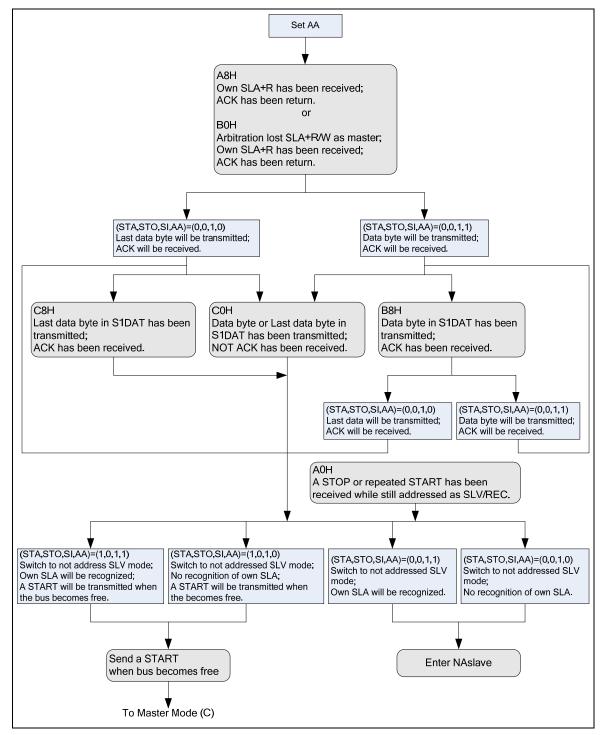

| Figure 5-30 Slave Transmitter Mode                                | 216 |

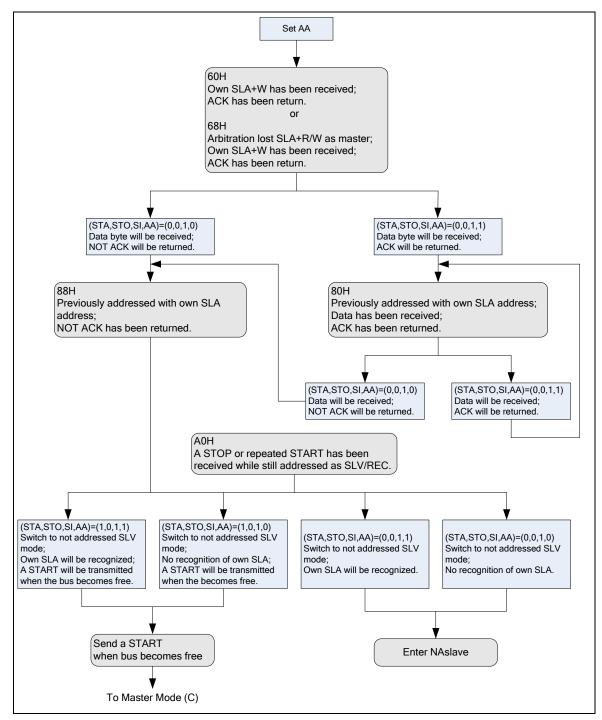

| Figure 5-31 Slave Receiver Mode                                   | 217 |

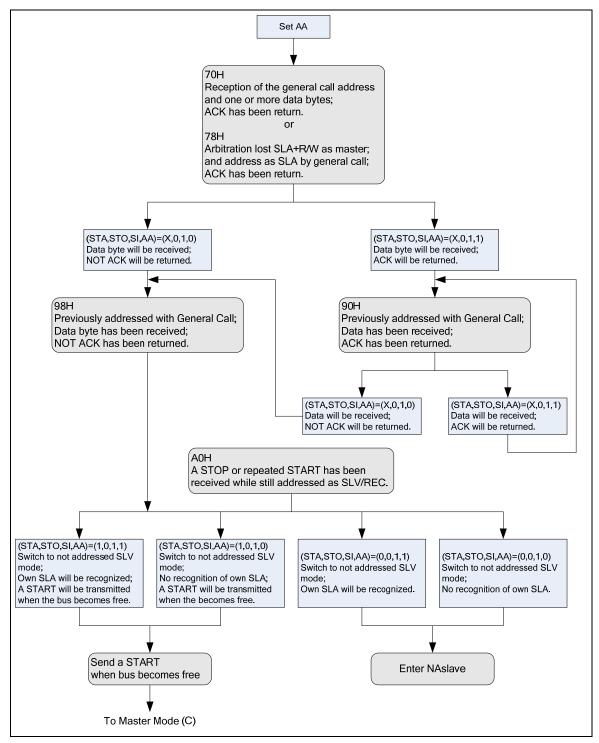

| Figure 5-32 GC Mode                                               | 218 |

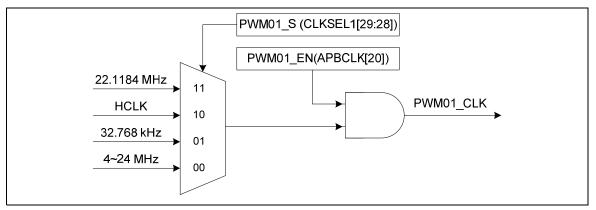

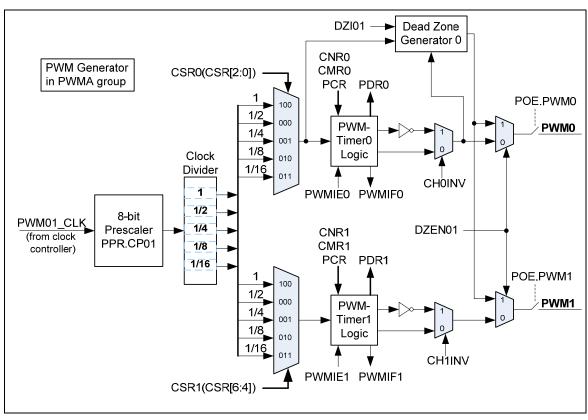

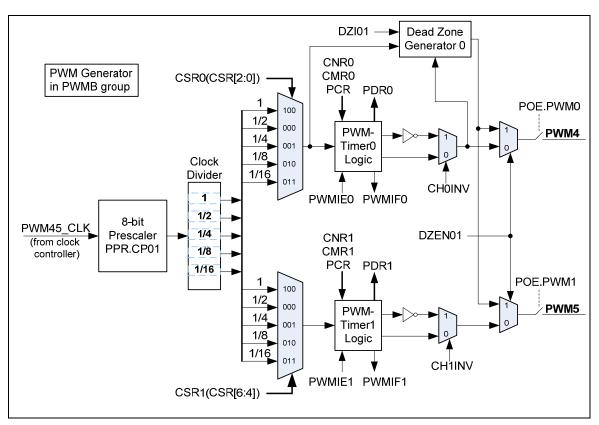

| Figure 5-33 PWM Generator 0 Clock Source Control                  | 221 |

| Figure 5-34 PWM Generator 0 Architecture Diagram                  | 221 |

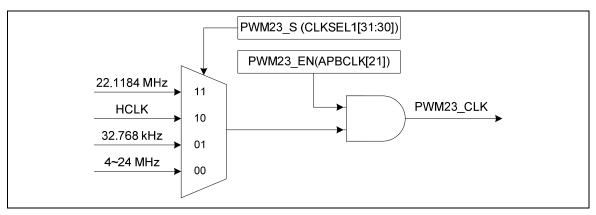

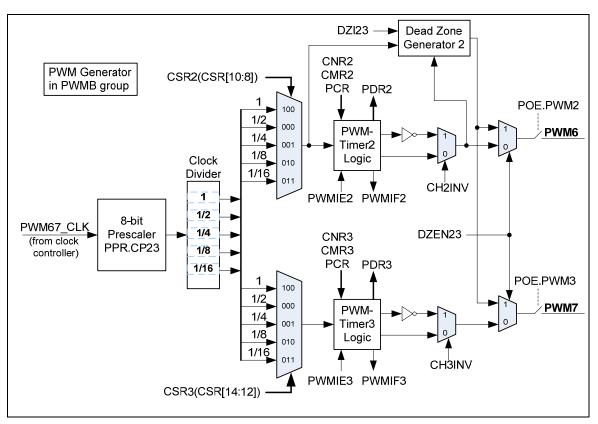

| Figure 5-35 PWM Generator 2 Clock Source Control                  | 222 |

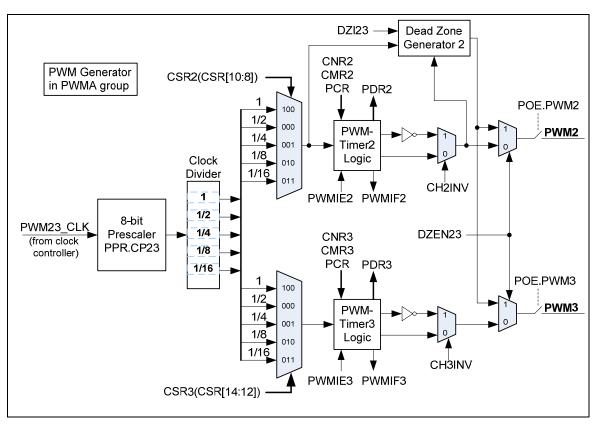

| Figure 5-36 PWM Generator 2 Architecture Diagram                  | 222 |

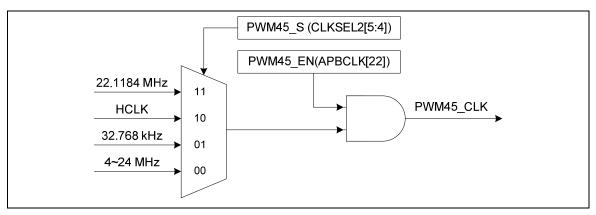

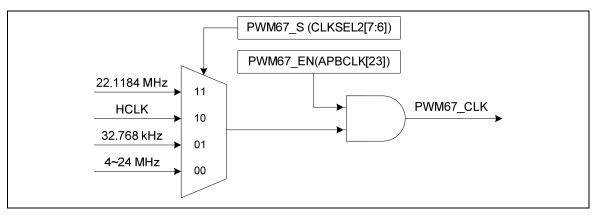

| Figure 5-37 PWM Generator 4 Clock Source Control                  | 223 |

| Figure 5-38 PWM Generator 4 Architecture Diagram                  | 223 |

| Figure 5-39 PWM Generator 6 Clock Source Control                  | 224 |

| Figure 5-40 PWM Generator 6 Architecture Diagram                  | 224 |

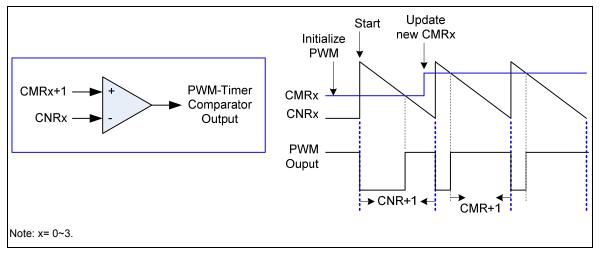

| Figure 5-41 Legend of Internal Comparator Output of PWM-Timer     | 225 |

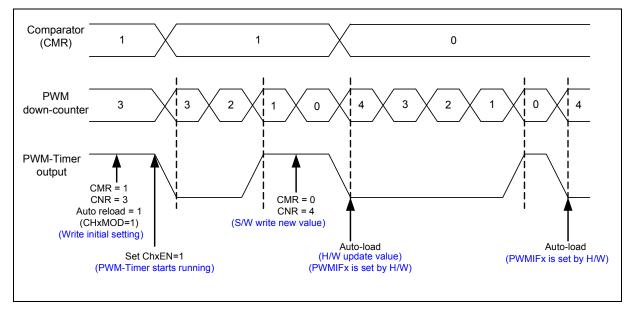

| Figure 5-42 PWM-Timer Operation Timing                            | 226 |

| Figure 5-43 PWM Double Buffering Illustration                     | 226 |

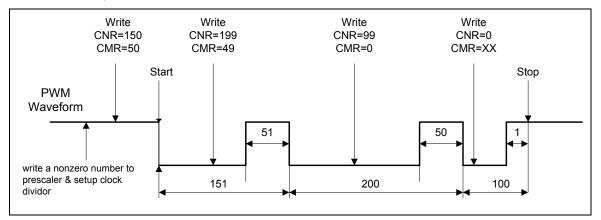

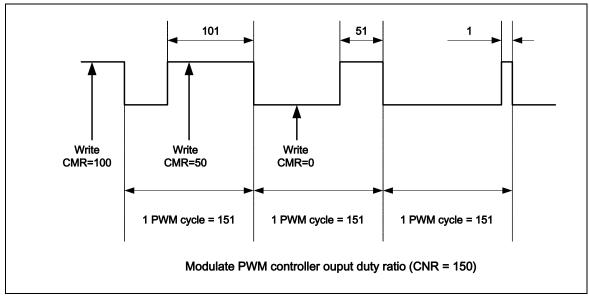

| Figure 5-44 PWM Controller Output Duty Ratio                      | 227 |

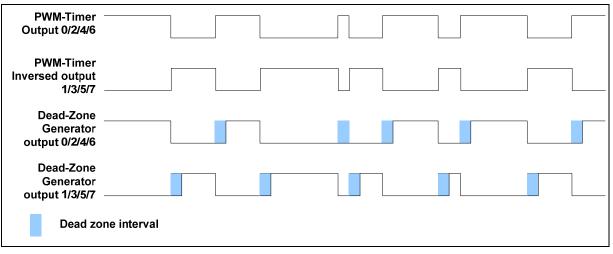

| Figure 5-45 Paired-PWM Output with Dead Zone Generation Operation | 227 |

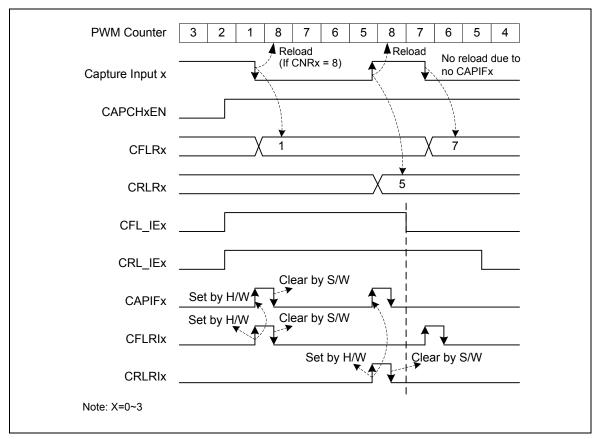

| Figure 5-46 Capture Operation Timing                              | 228 |

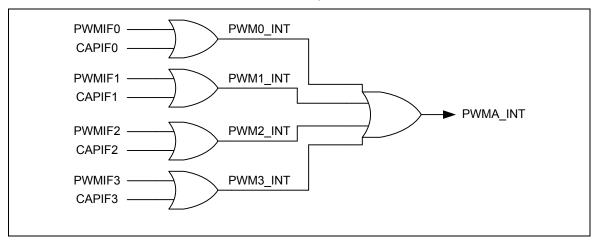

| Figure 5-47 PWM Group A PWM-Timer Interrupt Architecture Diagram  | 229 |

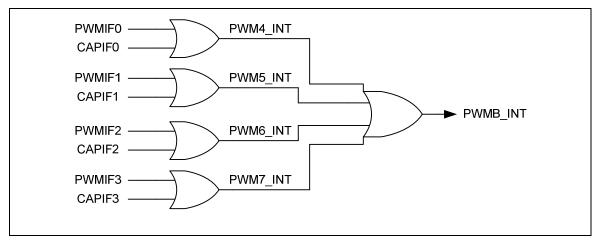

| Figure 5-48 PWM Group B PWM-Timer Interrupt Architecture Diagram  | 229 |

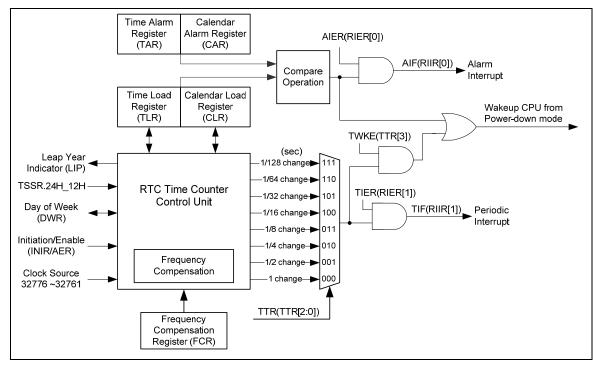

| Figure 5-49 RTC Block Diagram                                     | 258 |

| Figure 5-50 SPI Block Diagram                                     | 277 |

| Figure 5-51 SPI Master Mode Application Block Diagram             | 278 |

| Figure 5-52 SPI Slave Mode Application Block Diagram              | 278 |

| Figure 5-53 Variable Serial Clock Frequency                       | 280 |

| Figure 5-54 32-Bit in one Transaction                             | 280 |

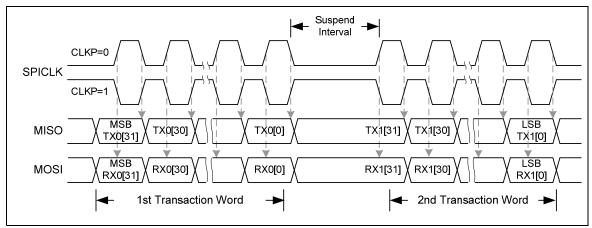

| Figure 5-55 Two Transactions in One Transfer (Burst Mode)         | 281 |

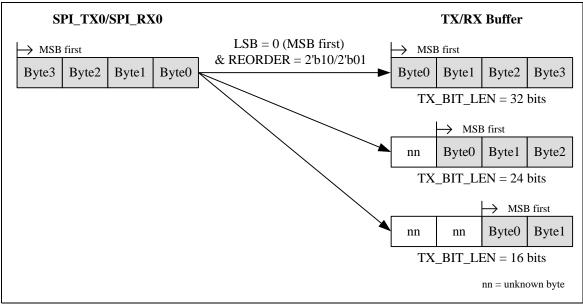

| Figure 5-56 Byte Reorder                                          | 282 |

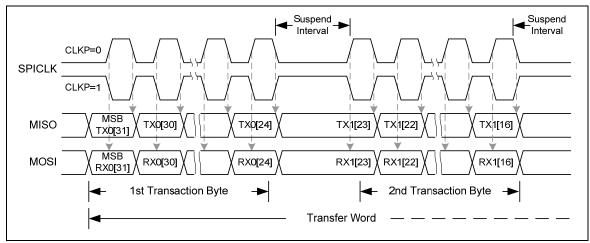

| Figure 5-57 Timing Waveform for Byte Suspend                      | 283 |

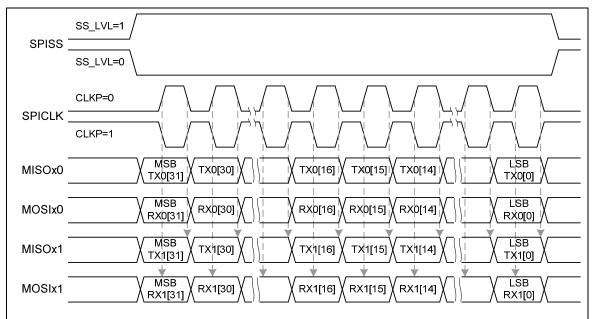

| Figure 5-58 Two Bits Transfer Mode (slave mode)                   |     |

| Figure 5-59 FIFO mode Block Diagram                               |     |

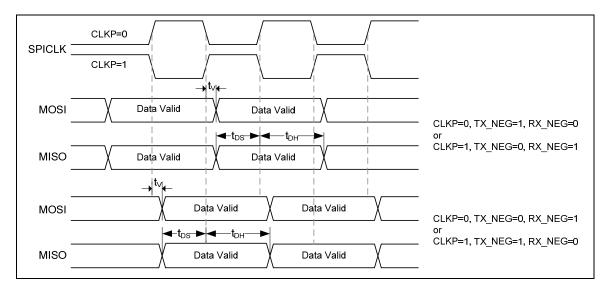

| Figure 5-60 SPI Timing in Master Mode                             | 287 |

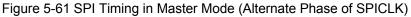

| Figure 5-61 SPI Timing in Master Mode (Alternate Phase of SPICLK) |     |

|                                                                   |     |

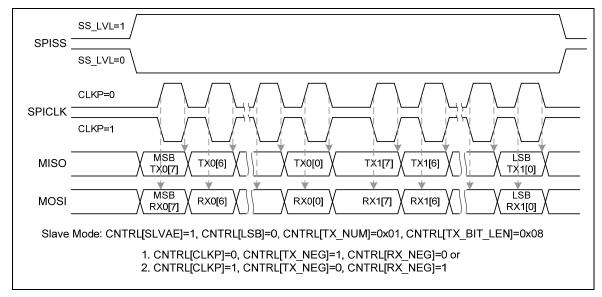

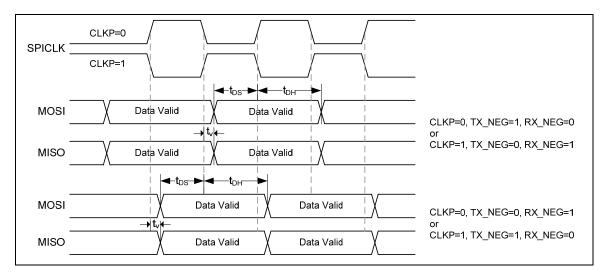

| Figure 5-62 SPI Timing in Slave Mode                             |     |

|------------------------------------------------------------------|-----|

| Figure 5-63 SPI Timing in Slave Mode (Alternate Phase of SPICLK) | 289 |

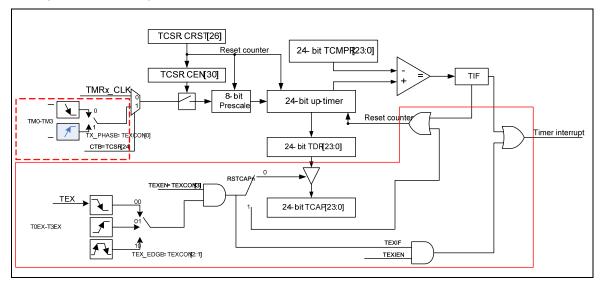

| Figure 5-64 Timer Controller Block Diagram                       | 308 |

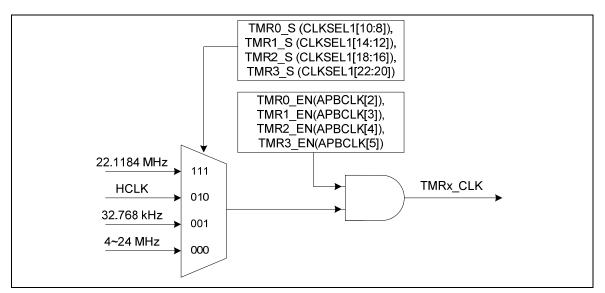

| Figure 5-65 Clock Source of Timer Controller                     | 308 |

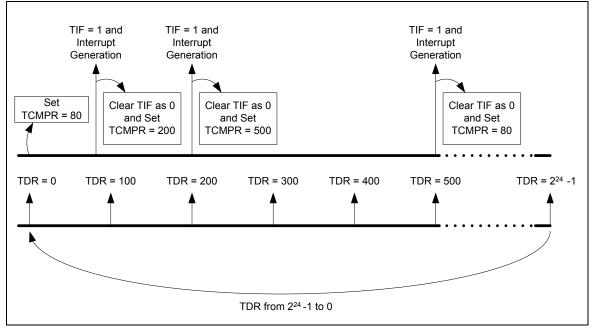

| Figure 5-66 Continuous Counting Mode                             | 310 |

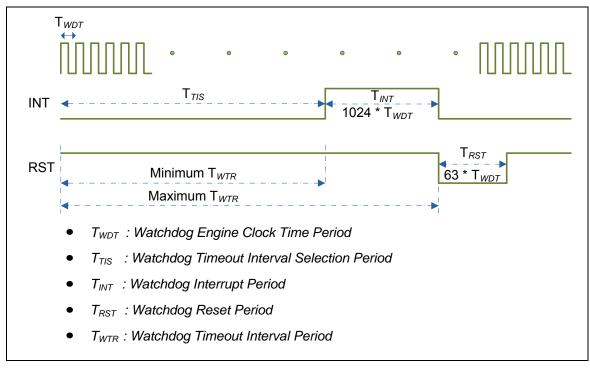

| Figure 5-67 Timing of Interrupt and Reset Signal                 | 325 |

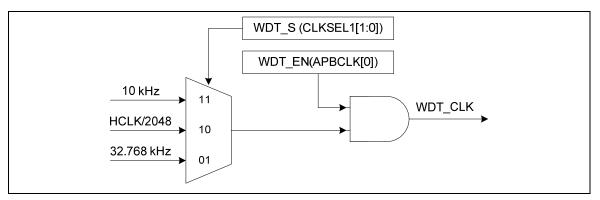

| Figure 5-68 Watchdog Timer Clock Control                         | 326 |

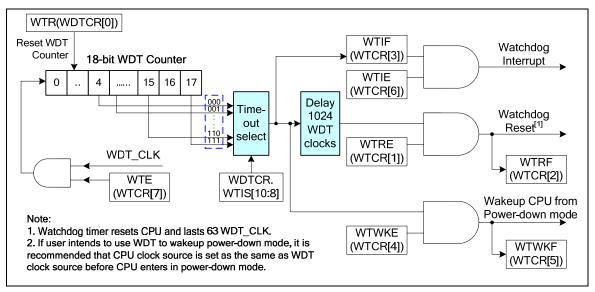

| Figure 5-69 Watchdog Timer Block Diagram                         | 326 |

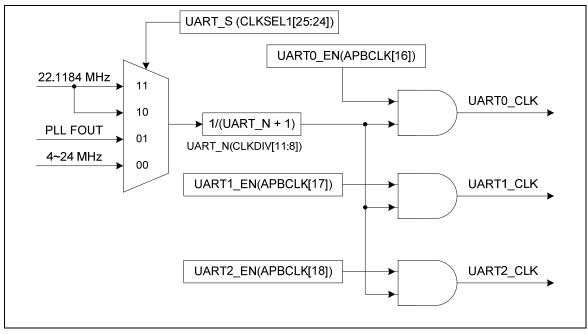

| Figure 5-70 UART Clock Control Diagram                           | 334 |

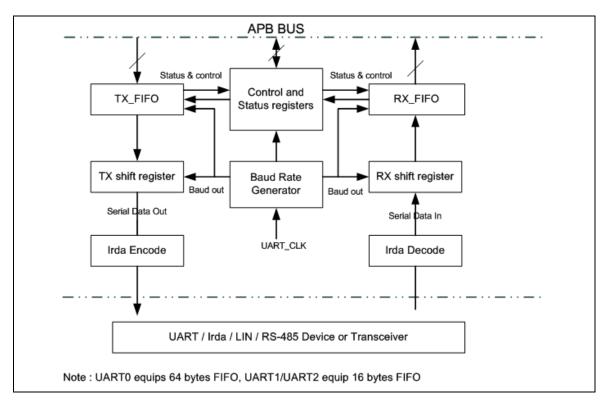

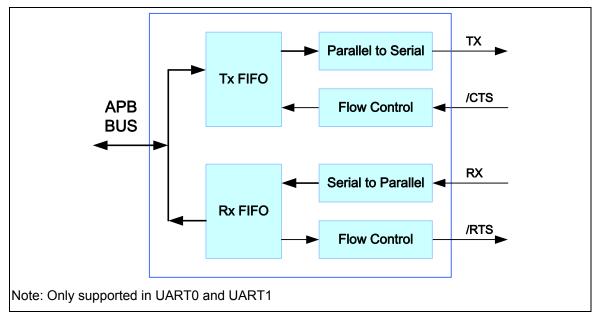

| Figure 5-71 UART Block Diagram                                   | 335 |

| Figure 5-72 Auto Flow Control Block Diagram                      | 336 |

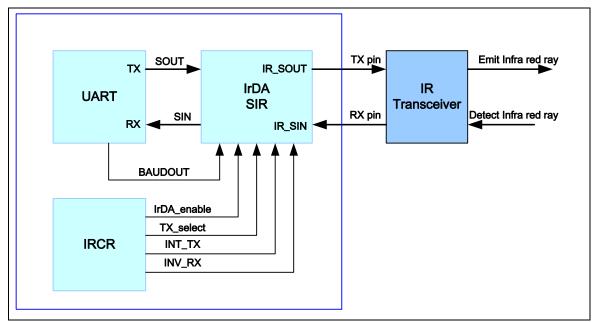

| Figure 5-73 IrDA Block Diagram                                   | 337 |

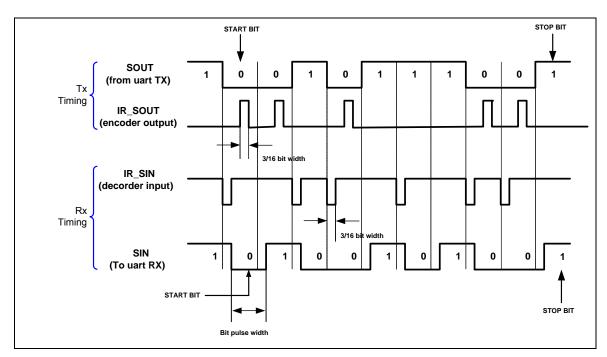

| Figure 5-74 IrDA TX/RX Timing Diagram                            | 338 |

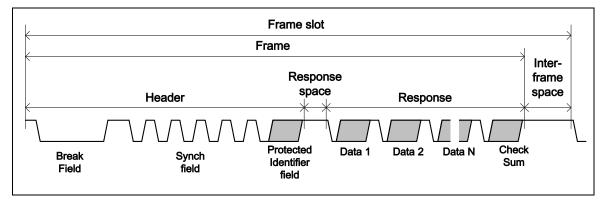

| Figure 5-75 Structure of LIN Frame                               | 339 |

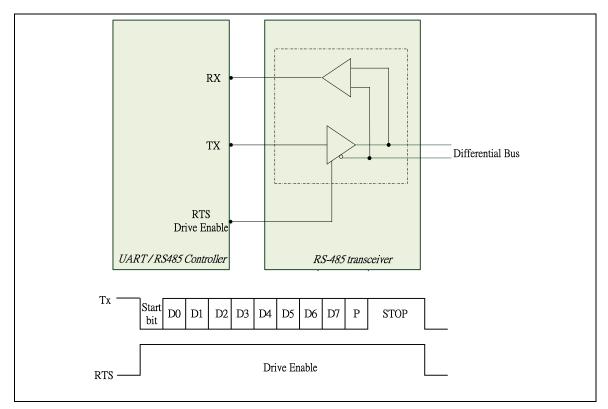

| Figure 5-76 Structure of RS-485 Frame                            | 341 |

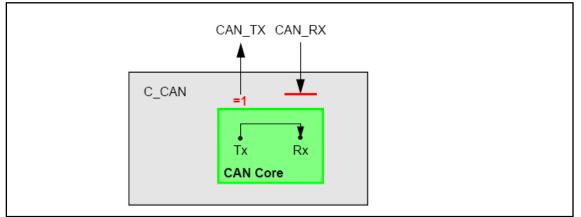

| Figure 5-77 CAN Peripheral Block Diagram                         | 370 |

| Figure 5-78 CAN Core in Silent Mode                              | 372 |

| Figure 5-79 CAN Core in Loop Back Mode                           | 373 |

| Figure 5-80 CAN Core in Loop Back Mode Combined with Silent Mode | 373 |

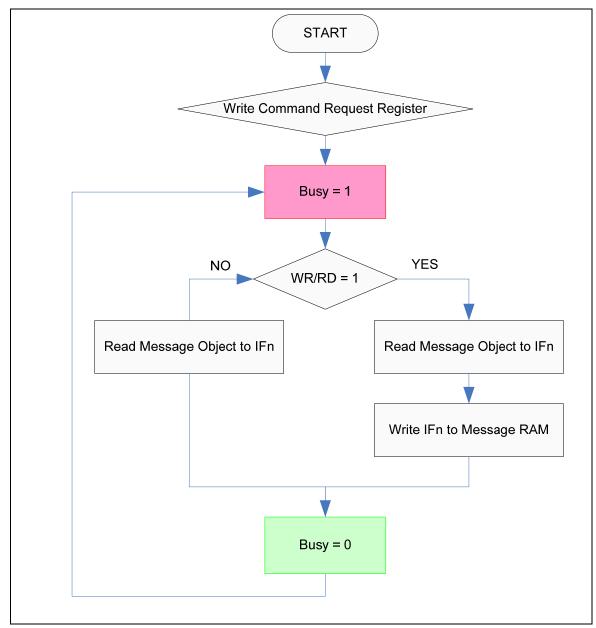

| Figure 5-81 Data transfer between IFn Registers and Message      | 376 |

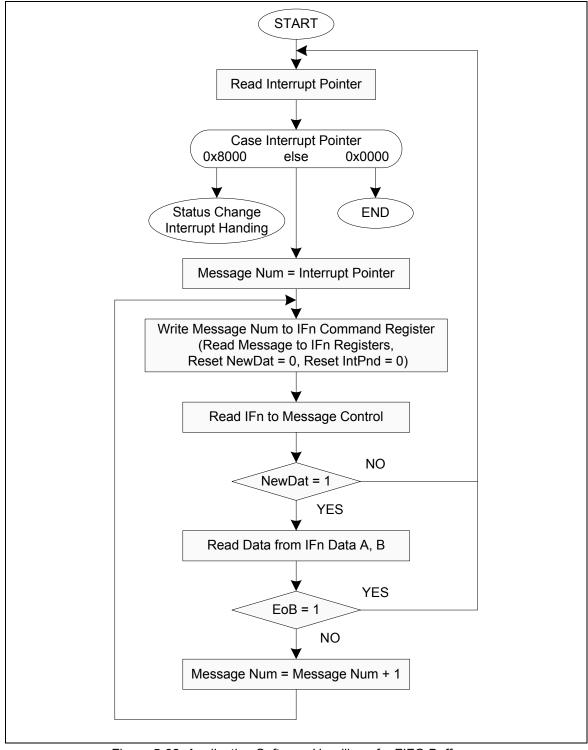

| Figure 5-82 Application Software Handling of a FIFO Buffer       | 381 |

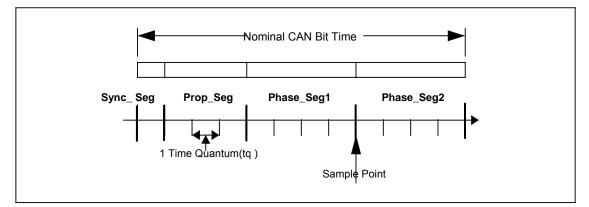

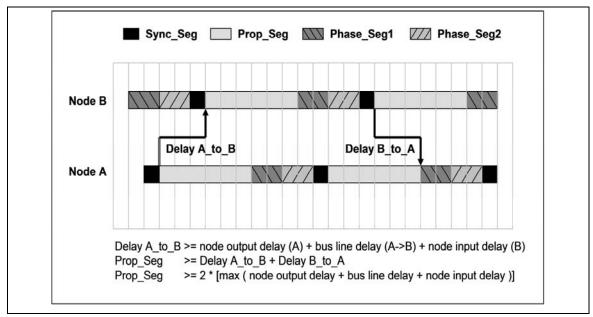

| Figure 5-83 Bit Timing                                           | 383 |

| Figure 5-84 Propagation Time Segment                             | 385 |

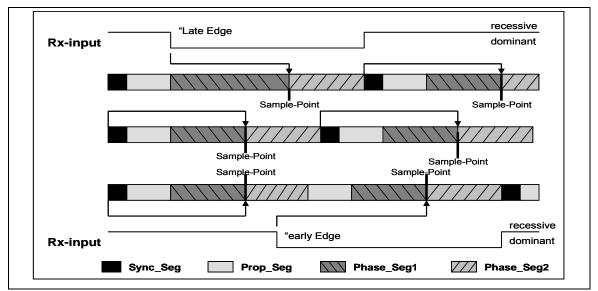

| Figure 5-85 Synchronization on "late" and "early" Edges          | 387 |

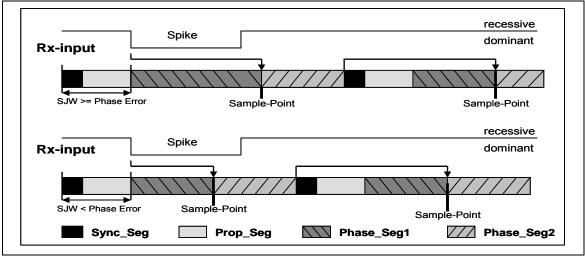

| Figure 5-86 Filtering of Short Dominant Spikes                   | 388 |

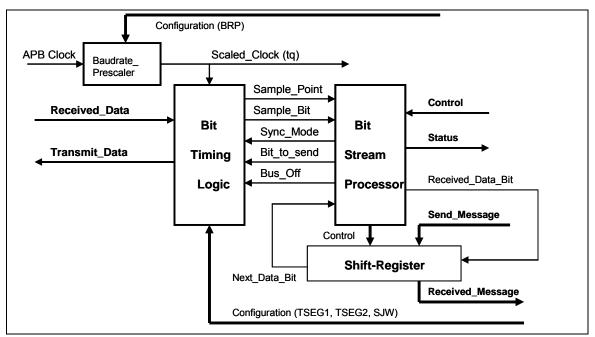

| Figure 5-87 Structure of the CAN Core's CAN Protocol Controller  | 390 |

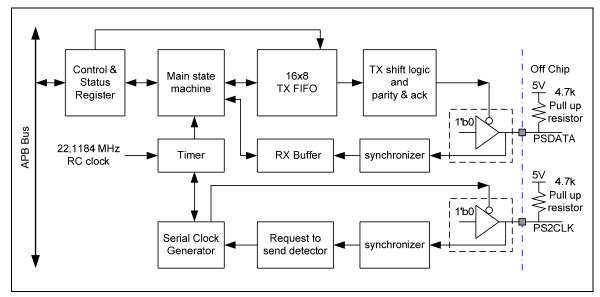

| Figure 5-88 PS/2 Device Block Diagram                            | 435 |

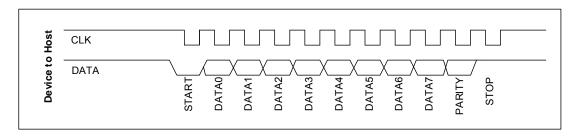

| Figure 5-89 Data Format of Device-to-Host                        | 437 |

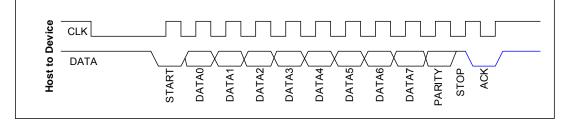

| Figure 5-90 Data Format of Host-to-Device                        | 437 |

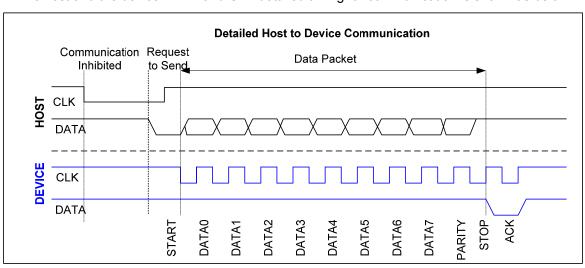

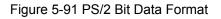

| Figure 5-91 PS/2 Bit Data Format                                 | 438 |

| Figure 5-92 PS/2 Bus Timing                                      | 438 |

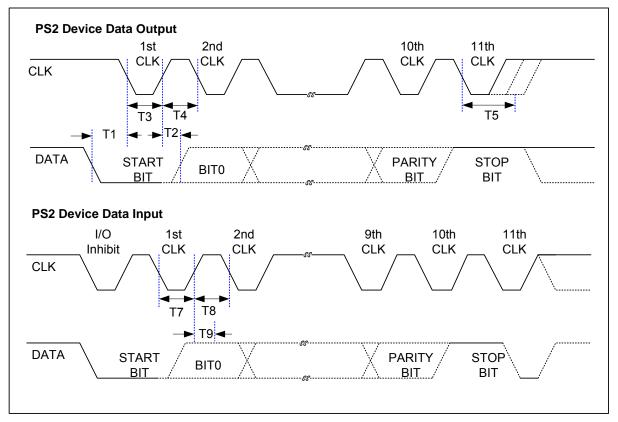

| Figure 5-93 PS/2 Data Format                                     | 440 |

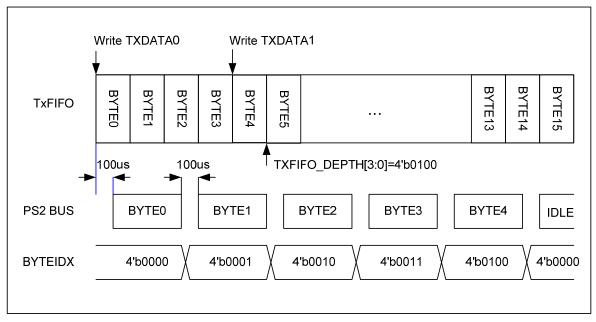

| Figure 5-94 I <sup>2</sup> S Clock Control Diagram               | 450 |

| Figure 5-95 I <sup>2</sup> S Controller Block Diagram            | 450 |

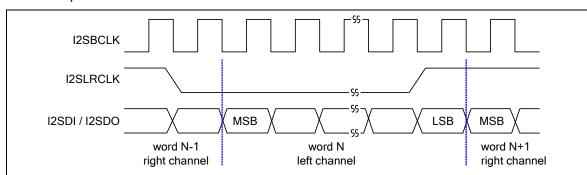

| Figure 5-96 I <sup>2</sup> S Bus Timing Diagram (Format =0)      | 451 |

| Figure 5-97 MSB Justified Timing Diagram (Format=1)              | 451 |

|                                                                  |     |

| Figure 5-98 FIFO contents for various I <sup>2</sup> S modes                                 |

|----------------------------------------------------------------------------------------------|

| Figure 5-99 ADC Controller Block Diagram                                                     |

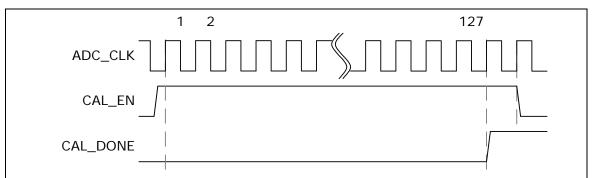

| Figure 5-100 ADC Converter Self-Calibration Timing Diagram                                   |

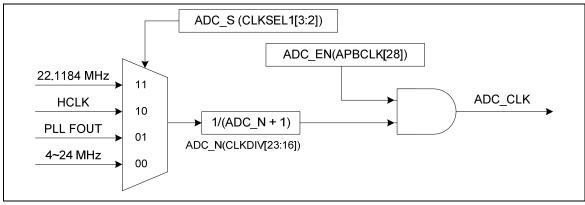

| Figure 5-101 ADC Clock Control                                                               |

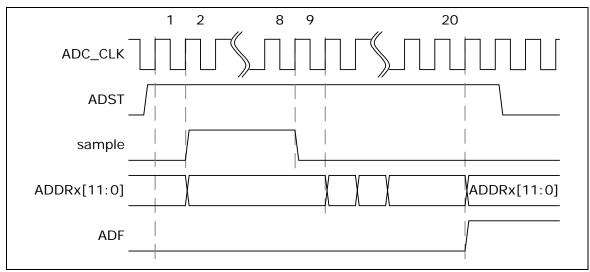

| Figure 5-102 Single Mode Conversion Timing Diagram                                           |

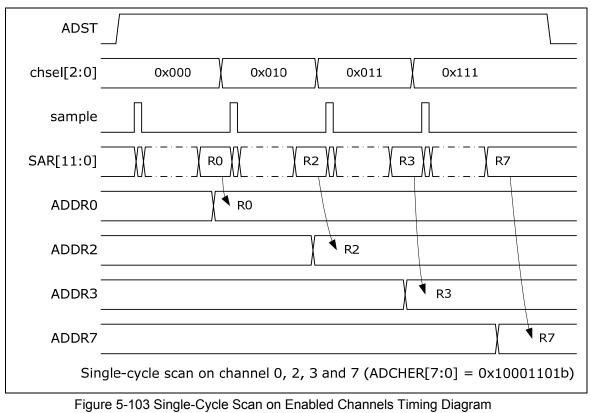

| Figure 5-103 Single-Cycle Scan on Enabled Channels Timing Diagram                            |

| Figure 5-104 Continuous Scan on Enabled Channels Timing Diagram                              |

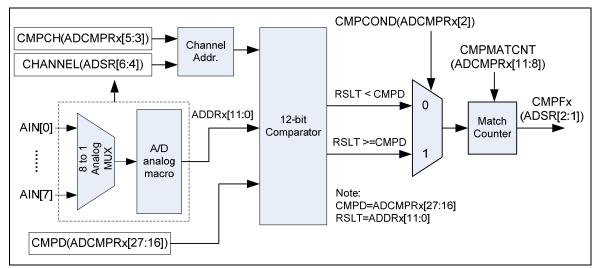

| Figure 5-105 A/D Conversion Result Monitor Logics Diagram                                    |

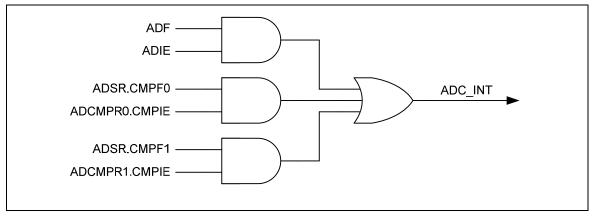

| Figure 5-106 A/D Controller Interrupt                                                        |

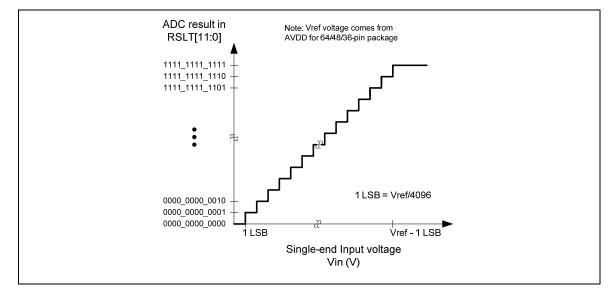

| Figure 5-107 ADC single-end input conversion voltage and conversion result mapping diagram   |

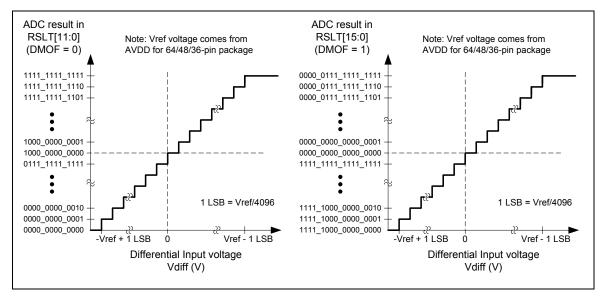

| Figure 5-108 ADC differential input conversion voltage and conversion result mapping diagram |

| Figure 5-109 Analog Comparator Block Diagram                                                 |

| Figure 5-110 Comparator Controller Interrupt Sources                                         |

| Figure 5-111 PDMA Controller Block Diagram                                                   |

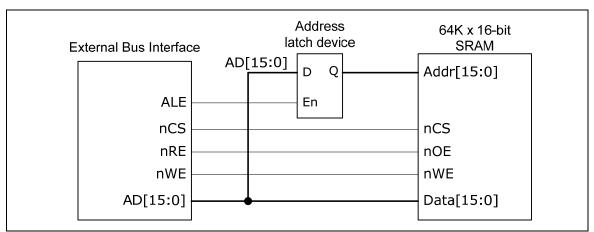

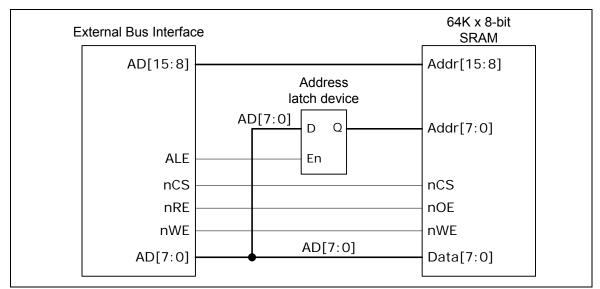

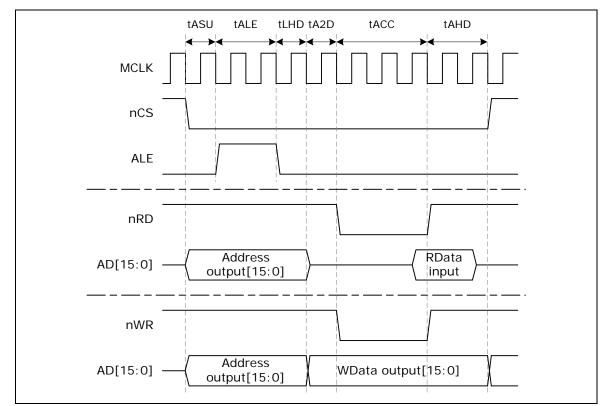

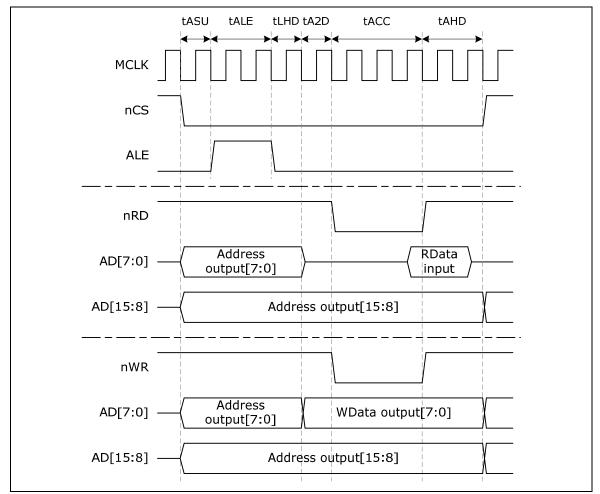

| Figure 5-112 EBI Block Diagram                                                               |

| Figure 5-113 Connection of 16-bit EBI Data Width with 16-bit Device                          |

| Figure 5-114 Connection of 8-bit EBI Data Width with 8-bit Device                            |

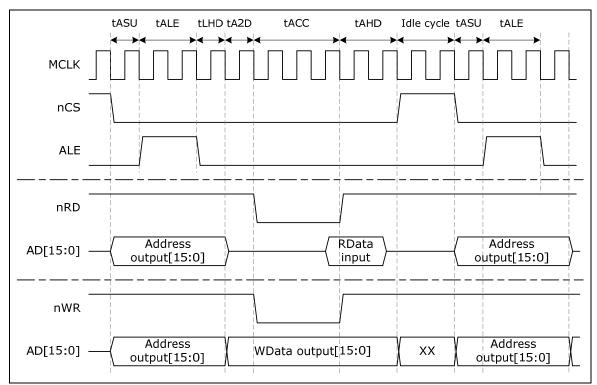

| Figure 5-115 Timing Control Waveform for 16-bit Data Width                                   |

| Figure 5-116 Timing Control Waveform for 8-bit Data Width                                    |

| Figure 5-117 Timing Control Waveform for Insert Idle Cycle                                   |

| Figure 6-1 Flash Memory Control Block Diagram                                                |

| Figure 6-2 Flash Memory Organization                                                         |

| Figure 6-3 Flash Memory Structure 535                                                        |

| Figure 7-1 Typical Crystal Application Circuit                                               |

| Figure 7-2 SPI Master dynamic characteristics tiMINg                                         |

| Figure 7-3 SPI Slave dynamic characteristics timing                                          |

#### Tables

| Table 1-1 Connectivity Supported Table                             | 12  |

|--------------------------------------------------------------------|-----|

| Table 5-1 Address Space Assignments for On-Chip Controllers        | 52  |

| Table 5-2 Exception Model                                          | 94  |

| Table 5-3 System Interrupt Map                                     | 95  |

| Table 5-4 Vector Table Format                                      | 96  |

| Table 5-5 Power Down Mode Control Table                            | 134 |

| Table 5-6 Byte Order and Byte Suspend Conditions                   | 283 |

| Table 5-7 Watchdog Timeout Interval Selection                      | 324 |

| Table 5-8 UART Baud Rate Equation                                  | 331 |

| Table 5-9 UART Baud Rate Setting Table                             | 332 |

| Table 5-10 UART Interrupt Sources and Flags Table In DMA Mode      | 361 |

| Table 5-11 UART Interrupt Sources and Flags Table In Software Mode | 361 |

| Table 5-12 Baud rate equation table                                | 364 |

| Table 5-13 Initialization of a Transmit Object                     | 378 |

| Table 5-14 Initialization of a Receive Object                      | 379 |

| Table 5-15 CAN Bit Time Parameters                                 | 384 |

| Table 5-16 CAN Register Map for Each Bit Function                  | 398 |

| Table 5-17 Error Codes                                             | 402 |

| Table 5-18 Source of Interrupts                                    | 405 |

| Table 5-19 IF1 and IF2 Message Interface Register                  | 409 |

| Table 5-20 Structure of a Message Object in the Message Memory     | 423 |

| Table 6-1 Memory Address Map                                       | 533 |

| Table 6-2 ISP Mode                                                 | 541 |

#### 1 GENERAL DESCRIPTION

The NuMicro<sup>™</sup> NUC100 Series is 32-bit microcontrollers with embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core for industrial control and applications which need rich communication interfaces. The Cortex<sup>™</sup>-M0 is the newest ARM<sup>®</sup> embedded processor with 32-bit performance and at a cost equivalent to traditional 8-bit microcontroller. NuMicro<sup>™</sup> NUC100 Series includes NUC100, NUC120, NUC130 and NUC140 product line.

The NuMicro<sup>™</sup> NUC130 Automotive Line with CAN function embeds Cortex<sup>™</sup>-M0 core running up to 50 MHz with 32K/64K/128K-byte embedded flash, 4K/8K/16K-byte embedded SRAM, and 4K-byte loader ROM for the ISP. It also equips with plenty of peripheral devices, such as Timers, Watchdog Timer, RTC, PDMA, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, LIN, CAN, PS/2, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-out Detector.

The NuMicro<sup>™</sup> NUC140 Connectivity Line with USB 2.0 full-speed and CAN functions embeds Cortex<sup>™</sup>-M0 core running up to 50 MHz with 32K/64K/128K-byte embedded flash, 4K/8K/16K-byte embedded SRAM, and 4K-byte loader ROM for the ISP.. It also equips with plenty of peripheral devices, such as Timers, Watchdog Timer, RTC, PDMA, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, LIN, CAN, PS/2, USB 2.0 FS Device, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-out Detector.

| Product Line | UART | SPI | I <sup>2</sup> C | USB | LIN | CAN | PS/2 | I <sup>2</sup> S |

|--------------|------|-----|------------------|-----|-----|-----|------|------------------|

| NUC100       | •    | ٠   | •                |     |     |     | •    | •                |

| NUC120       | •    | ٠   | •                | •   |     |     | •    | •                |

| NUC130       | •    | ٠   | •                |     | •   | •   | •    | •                |

| NUC140       | •    | •   | •                | •   | •   | •   | •    | •                |

Table 1-1 Connectivity Supported Table

#### 2 FEATURES

The equipped features are dependent on the product line and their sub products.

#### 2.1 NuMicro<sup>™</sup> NUC130 Features – Automotive Line

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Build-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 4KB flash for ISP loader

- Support In-system program (ISP) application code update

- 512 byte page erase for flash

- Configurable data flash address and size for 128KB system, fixed 4KB data flash for the 32KB and 64KB system

- Support 2 wire ICP update through SWD/ICE interface

- Support fast parallel programming mode by external programmer

- SRAM Memory

- 4K/8K/16K bytes embedded SRAM

- Support PDMA mode

- PDMA (Peripheral DMA)

- Support 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed OSC for system operation

- Trimmed to  $\pm$  1 % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm$  3 % at -40  $^\circ$ C ~ +85  $^\circ$ C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 KHz low speed OSC for Watchdog Timer and Wake-up operation

- Support one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for precise timing operation

- External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

- Timer

### NuMicro™ NUC130/NUC140 Technical Reference Manual

- Support 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Support event counting function

- Support input capture function

- Watchdog Timer

- Multiple clock sources

- 8 selectable time out period from 1.6ms ~ 26.0sec (depends on clock source)

- WDT can wake-up from power down or idle mode

- Interrupt or reset selectable on watchdog time-out

- RTC

- Support software compensation by setting frequency compensate register (FCR)

- Support RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Support Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Support periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Support wake-up function

- PWM/Capture

- Built-in up to four 16-bit PWM generators provide eight PWM outputs or four complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one 8-bit prescaler and one Dead-Zone generator for complementary paired PWM

- Up to eight 16-bit digital Capture timers (shared with PWM timers) provide eight rising/falling capture inputs

- Support Capture interrupt

- UART

- Up to three UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0 with 64-byte FIFO is for high speed

- UART1/2(optional) with 16-byte FIFO for standard device

- Support IrDA (SIR) and LIN function

- Support RS-485 9-bit mode and direction control.

- Programmable baud-rate generator up to 1/16 system clock

- Support PDMA mode

- SPI

- Up to four sets of SPI controller

- Master up to 32 MHz, and Slave up to 10 MHz (chip working @ 5V)

- Support SPI master/slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 1 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- 2 slave/device select lines when it is as the master, and 1 slave/device select line when it is as the slave

- Support byte suspend mode in 32-bit transmission

- Support PDMA mode

- Support three wire, no slave select signal, bi-direction interface

## nuvoTon

• I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C device

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow versatile rate control

- Support multiple address recognition (four slave address with mask option)

•I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either master or slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Mono and stereo audio data supported

- I<sup>2</sup>S and MSB justified data format supported

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive

- Generates interrupt requests when buffer levels cross a programmable boundary

- Support two DMA requests, one for transmit and one for receive

- PS/2 Device Controller

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

- CAN 2.0

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1M bit/s

- 32 Message Objects

- Each Message Object has its won identifier mask

- Programmable FIFO mode (concatenation of Message Object)

- Maskable interrupt

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications

- Support power down wake-up function

- EBI (External bus interface) support (100-pin and 64-pin Package Only)

- Accessible space: 64KB in 8-bit mode or 128KB in 16-bit mode

- Support 8-/16-bit data width

- Support byte write in 16-bit data width mode

- ADC

- 12-bit SAR ADC with 700K SPS

- Up to 8-ch single-end input or 4-ch differential input

- Single scan/single cycle scan/continuous scan

- Each channel with individual result register

- Scan on enabled channels

- Threshold voltage detection

- Conversion start by software programming or external input

- Support PDMA mode

- Analog Comparator

- Up to two analog comparator

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- $\bullet$  One built-in temperature sensor with 1  $^\circ\!\mathrm{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin

### NuMicro™ NUC130/NUC140 Technical Reference Manual

## nuvoTon

#### 2.2 NuMicro<sup>™</sup> NUC140 Features – Connectivity Line

#### • Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Build-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 4KB flash for ISP loader

- Support In-system program (ISP) application code update

- 512 byte page erase for flash

- Configurable data flash address and size for 128KB system, fixed 4KB data flash for the 32KB and 64KB system

- Support 2 wire ICP update through SWD/ICE interface

- Support fast parallel programming mode by external programmer

- SRAM Memory

- 4K/8K/16K bytes embedded SRAM

- Support PDMA mode

- PDMA (Peripheral DMA)

- Support 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed OSC for system operation

- Trimmed to  $\pm$  1 % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm$  3 % at -40  $^\circ$ C ~ +85  $^\circ$ C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 KHz low speed OSC for Watchdog Timer and Wake-up operation

- Support one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for USB and precise timing operation

- External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

- Timer

- Support 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

### NuMicro™ NUC130/NUC140 Technical Reference Manual

## nuvoTon

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Support event counting function

- Support input capture function

- Watchdog Timer

- Multiple clock sources

- 8 selectable time out period from 1.6ms ~ 26.0sec (depends on clock source)

- WDT can wake-up from power down or idle mode

- Interrupt or reset selectable on watchdog time-out

RTC

- Support software compensation by setting frequency compensate register (FCR)

- Support RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Support Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Support periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Support wake-up function

- PWM/Capture

- Built-in up to four 16-bit PWM generators provide eight PWM outputs or four complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one 8-bit prescaler and one Dead-Zone generator for complementary paired PWM

- Up to eight 16-bit digital Capture timers (shared with PWM timers) provide eight rising/falling capture inputs

- Support Capture interrupt

• UART

- Up to three UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0 with 64-byte FIFO is for high speed

- UART1/2(optional) with 16-byte FIFO for standard device

- Support IrDA (SIR) and LIN function

- Support RS-485 9-bit mode and direction control.

- Programmable baud-rate generator up to 1/16 system clock

- Support PDMA mode

• SPI

- Up to four sets of SPI controller

- Master up to 32 MHz, and Slave up to 10 MHz (chip working @ 5V)

- Support SPI master/slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 1 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- 2 slave/device select lines when it is as the master, and 1 slave/device select line when it is as the slave

- Support byte suspend mode in 32-bit transmission

- Support PDMA mode

- Support three wire, no slave select signal, bi-direction interface

# nuvoTon

• I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C device

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow versatile rate control

- Support multiple address recognition (four slave address with mask option)

•I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either master or slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Mono and stereo audio data supported

- I<sup>2</sup>S and MSB justified data format supported

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive

- Generates interrupt requests when buffer levels cross a programmable boundary

- Support two DMA requests, one for transmit and one for receive

- CAN 2.0

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1M bit/s

- 32 Message Objects

- Each Message Object has its won identifier mask

- Programmable FIFO mode (concatenation of Message Object)

- Maskable interrupt

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications

- Support power down wake-up function

- PS/2 Device Controller

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

- USB 2.0 Full-Speed Device

- One set of USB 2.0 FS Device 12Mbps

- On-chip USB Transceiver

- Provide 1 interrupt source with 4 interrupt events

- Support Control, Bulk In/Out, Interrupt and Isochronous transfers

- Auto suspend function when no bus signaling for 3 ms

- Provide 6 programmable endpoints

- Include 512 Bytes internal SRAM as USB buffer

- Provide remote wake-up capability

- EBI (External bus interface) support (100-pin and 64-pin Package Only)

- Accessible space: 64KB in 8-bit mode or 128KB in 16-bit mode

- Support 8-/16-bit data width

## nuvoTon

Support byte write in 16-bit data width mode

• ADC

- 12-bit SAR ADC with 700K SPS

- Up to 8-ch single-end input or 4-ch differential input

- Single scan/single cycle scan/continuous scan

- Each channel with individual result register

- Scan on enabled channels

- Threshold voltage detection

- Conversion start by software programming or external input

- Support PDMA Mode

- Analog Comparator

- Up to two analog comparators

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- $\bullet$  One built-in temperature sensor with 1  $^\circ\!\mathbb{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin

#### **3 PARTS INFORMATION LIST AND PIN CONFIGURATION**

#### 3.1 NuMicro<sup>™</sup> NUC130 Products Selection Guide

| Part number | APROM  | APROM | APROM     | APROM | APROM    | RAM      | Data | ISP<br>Loader | 1/0              | Timer |     | (   | Conne | ctivity |   |          | I <sup>2</sup> S | Comp. | PWM | ADC      | RTC | EBI | ISP | Package |

|-------------|--------|-------|-----------|-------|----------|----------|------|---------------|------------------|-------|-----|-----|-------|---------|---|----------|------------------|-------|-----|----------|-----|-----|-----|---------|

|             |        |       | Flash     | ROM   |          | -        | UART | SPI           | I <sup>2</sup> C | USB   | LIN | CAN |       |         |   |          |                  |       | ICP | . uonugo |     |     |     |         |

| NUC130LC1CN | 32 KB  | 4 KB  | 4 KB      | 4 KB  | up to 35 | 4x32-bit | 3    | 1             | 2                | -     | 2   | 1   | 1     | 1       | 4 | 8x12-bit | v                | -     | v   | LQFP48   |     |     |     |         |

| NUC130LD2CN | 64 KB  | 8 KB  | 4 KB      | 4 KB  | up to 35 | 4x32-bit | 3    | 1             | 2                | -     | 2   | 1   | 1     | 1       | 4 | 8x12-bit | v                | -     | v   | LQFP48   |     |     |     |         |

| NUC130LE3CN | 128 KB | 16 KB | Definable | 4 KB  | up to 35 | 4x32-bit | 3    | 1             | 2                | -     | 2   | 1   | 1     | 1       | 4 | 8x12-bit | v                | -     | v   | LQFP48   |     |     |     |         |

| NUC130RC1CN | 32 KB  | 4 KB  | 4 KB      | 4 KB  | up to 49 | 4x32-bit | 3    | 2             | 2                | -     | 2   | 1   | 1     | 2       | 6 | 8x12-bit | v                | v     | v   | LQFP64   |     |     |     |         |

| NUC130RD2CN | 64 KB  | 8 KB  | 4 KB      | 4 KB  | up to 49 | 4x32-bit | 3    | 2             | 2                | -     | 2   | 1   | 1     | 2       | 6 | 8x12-bit | v                | v     | v   | LQFP64   |     |     |     |         |

| NUC130RD3CN | 128 KB | 16 KB | Definable | 4 KB  | up to 49 | 4x32-bit | 3    | 2             | 2                | -     | 2   | 1   | 1     | 2       | 6 | 8x12-bit | v                | v     | v   | LQFP64   |     |     |     |         |

| NUC130VE3CN | 128 KB | 16 KB | Definable | 4 KB  | up to 80 | 4x32-bit | 3    | 4             | 2                | -     | 2   | 1   | 1     | 2       | 8 | 8x12-bit | v                | v     | v   | LQFP100  |     |     |     |         |

#### 3.1.1 NuMicro<sup>™</sup> NUC130 Automotive Line Selection Guide

#### 3.2 NuMicro™ NUC140 Products Selection Guide

| Part number | APROM  | RAM   | Data      | ISP<br>Loader | 1/0      | Timer    |      | (   | Conne            | ctivity |     |     | I <sup>2</sup> S | Comp. | PWM | ADC      | RTC | EBI | ISP<br>ICP | Package |

|-------------|--------|-------|-----------|---------------|----------|----------|------|-----|------------------|---------|-----|-----|------------------|-------|-----|----------|-----|-----|------------|---------|

|             |        |       | Flash     | ROM           |          |          | UART | SPI | I <sup>2</sup> C | USB     | LIN | CAN |                  |       |     |          |     |     |            |         |

| NUC140LC1CN | 32 KB  | 4 KB  | 4 KB      | 4 KB          | up to 31 | 4x32-bit | 2    | 1   | 2                | 1       | 2   | 1   | 1                | 1     | 4   | 8x12-bit | v   | -   | v          | LQFP48  |

| NUC140LD2CN | 64 KB  | 8 KB  | 4 KB      | 4 KB          | up to 31 | 4x32-bit | 2    | 1   | 2                | 1       | 2   | 1   | 1                | 1     | 4   | 8x12-bit | v   | -   | v          | LQFP48  |

| NUC140LE3CN | 128 KB | 16 KB | Definable | 4 KB          | up to 31 | 4x32-bit | 2    | 1   | 2                | 1       | 2   | 1   | 1                | 1     | 4   | 8x12-bit | v   | -   | v          | LQFP48  |

| NUC140RC1CN | 32 KB  | 4 KB  | 4 KB      | 4 KB          | up to 45 | 4x32-bit | 3    | 2   | 2                | 1       | 2   | 1   | 1                | 2     | 4   | 8x12-bit | v   | v   | v          | LQFP64  |

| NUC140RD2CN | 64 KB  | 8 KB  | 4 KB      | 4 KB          | up to 45 | 4x32-bit | 3    | 2   | 2                | 1       | 2   | 1   | 1                | 2     | 4   | 8x12-bit | v   | v   | v          | LQFP64  |

| NUC140RE3CN | 128 KB | 16 KB | Definable | 4 KB          | up to 45 | 4x32-bit | 3    | 2   | 2                | 1       | 2   | 1   | 1                | 2     | 4   | 8x12-bit | v   | v   | v          | LQFP64  |

| NUC140VE3CN | 128 KB | 16 KB | Definable | 4 KB          | up to 76 | 4x32-bit | 3    | 4   | 2                | 1       | 2   | 1   | 1                | 2     | 8   | 8x12-bit | v   | v   | v          | LQFP100 |

#### 3.2.1 NuMicro™ NUC140 Connectivity Line Selection Guide

Figure 3-1 NuMicro™ NUC100 Series selection code

#### 3.3 Pin Configuration

#### 3.3.1 NuMicro™ NUC130/NUC140 Pin Diagram

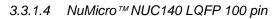

3.3.1.1 NuMicro™NUC130 LQFP 100 pin

Figure 3-2 NuMicro™ NUC130 LQFP 100-pin Pin Diagram

# nuvoTon

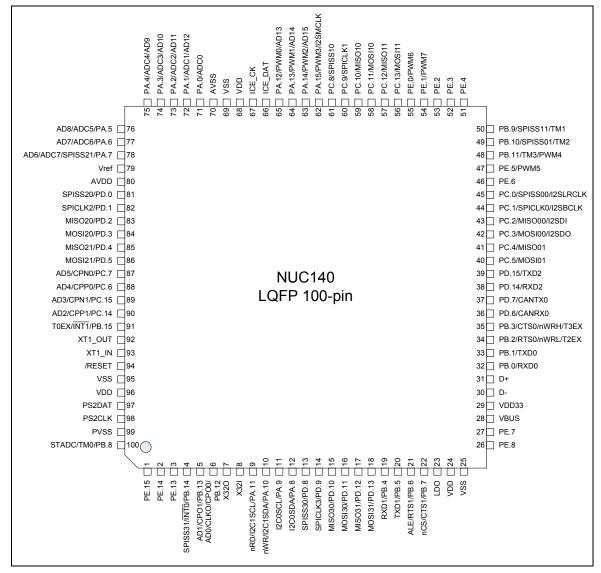

#### 3.3.1.2 NuMicro™ NUC130 LQFP 64 pin

Figure 3-3 NuMicro™ NUC130 LQFP 64-pin Pin Diagram

# nuvoTon

#### 3.3.1.3 NuMicro™ NUC130 LQFP 48 pin

Figure 3-4 NuMicro™ NUC130 LQFP 48-pin Pin Diagram

Figure 3-5 NuMicro™ NUC140 LQFP 100-pin Pin Diagram

Figure 3-6 NuMicro™ NUC140 LQFP 64-pin Pin Diagram

# nuvoTon

#### 3.3.1.6 NuMicro™ NUC140 LQFP 48 pin

Figure 3-7 NuMicro™ NUC140 LQFP 48-pin Pin Diagram

#### 3.4 Pin Description

#### 3.4.1 NuMicro™ NUC130/NUC140 Pin Description

3.4.1.1 NuMicro™NUC130 Pin Description

|             | Pin No.    |            |          |          |                                                  |

|-------------|------------|------------|----------|----------|--------------------------------------------------|

| LQFP<br>100 | LQFP<br>64 | LQFP<br>48 | Pin Name | Pin Type | Description                                      |

| 1           |            |            | PE.15    | I/O      | General purpose input/output digital pin         |

| 2           |            |            | PE.14    | I/O      | General purpose input/output digital pin         |

| 3           |            |            | PE.13    | I/O      | General purpose input/output digital pin         |

|             |            |            | PB.14    | I/O      | General purpose input/output digital pin         |

| 4           | 1          |            | /INT0    | I        | /INT0: External interrupt1 input pin             |

|             |            |            | SPISS31  | I/O      | SPISS31: SPI3 2 <sup>nd</sup> slave select pin   |

|             |            |            | PB.13    | I/O      | General purpose input/output digital pin         |

| 5           | 2          |            | CPO1     | 0        | Comparator1 output pin                           |

|             |            |            | AD1      | I/O      | EBI Address/Data bus bit1                        |

|             |            |            | PB.12    | I/O      | General purpose input/output digital pin         |

| 6           | 3          | 1          | CPO0     | 0        | Comparator0 output pin                           |

| 0           | 5          | I          | CLKO     | 0        | Frequency Divider output pin                     |

|             |            |            | AD0      | I/O      | EBI Address/Data bus bit0                        |

| 7           | 4          | 2          | X32O     | 0        | External 32.768 kHz low speed crystal output pin |

| 8           | 5          | 3          | X32I     | I        | External 32.768 kHz low speed crystal input pin  |

|             |            | 4          | PA.11    | I/O      | General purpose input/output digital pin         |

| 9           | 6          | 4          | I2C1SCL  | I/O      | I2C1SCL: I <sup>2</sup> C1 clock pin             |

|             |            |            | nRD      | 0        | EBI read enable output pin                       |

|             |            | F          | PA.10    | I/O      | General purpose input/output digital pin         |

| 10          | 7          | 5          | I2C1SDA  | I/O      | I2C1SDA: I <sup>2</sup> C1 data input/output pin |

|             |            |            | nWR      | 0        | EBI write enable output pin                      |

| 4.4         | 6          | 6          | PA.9     | I/O      | General purpose input/output digital pin         |

| 11          | 8          | 6          | I2C0SCL  | I/O      | I2C0SCL: I <sup>2</sup> C0 clock pin             |

| 40          |            |            | PA.8     | I/O      | General purpose input/output digital pin         |

| 12          | 9          | 7          | I2C0SDA  | I/O      | I2C0SDA: I <sup>2</sup> C0 data input/output pin |

| Pin No.     |            |            |          |          |                                                                                 |

|-------------|------------|------------|----------|----------|---------------------------------------------------------------------------------|

| LQFP<br>100 | LQFP<br>64 | LQFP<br>48 | Pin Name | Pin Type | Description                                                                     |

| 13          |            |            | PD.8     | I/O      | General purpose input/output digital pin                                        |

| 15          |            |            | SPISS30  | I/O      | SPISS30: SPI3 slave select pin                                                  |

| 14          |            |            | PD.9     | I/O      | General purpose input/output digital pin                                        |

| 14          |            |            | SPICLK3  | I/O      | SPICLK3: SPI3 serial clock pin                                                  |

| 15          |            |            | PD.10    | I/O      | General purpose input/output digital pin                                        |

| 15          |            |            | MISO30   | I/O      | MISO30: SPI3 MISO (Master In, Slave Out) pin                                    |

| 16          |            |            | PD.11    | I/O      | General purpose input/output digital pin                                        |

| 10          |            |            | MOSI30   | I/O      | MOSI30: SPI3 MOSI (Master Out, Slave In) pin                                    |

| 17          |            |            | PD.12    | I/O      | General purpose input/output digital pin                                        |

| 17          |            |            | MISO31   | I/O      | MISO31: SPI3 2 <sup>nd</sup> MISO (Master In, Slave Out) pin                    |

| 18          |            |            | PD.13    | I/O      | General purpose input/output digital pin                                        |

| 10          |            |            | MOSI31   | I/O      | MOSI31: SPI3 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin                    |

| 19          | 10         | 8          | PB.4     | I/O      | General purpose input/output digital pin                                        |

| 19          | 10         | 0          | RXD1     |          | RXD1: Data receiver input pin for UART1                                         |

| 20          | 11         | 9          | PB.5     | I/O      | General purpose input/output digital pin                                        |

| 20          |            | 9          | TXD1     | 0        | TXD1: Data transmitter output pin for UART1                                     |

|             |            |            | PB.6     | I/O      | General purpose input/output digital pin                                        |

| 21          | 12         |            | RTS1     | 0        | RTS1: Request to Send output pin for UART1                                      |

|             |            |            | ALE      | 0        | EBI address latch enable output pin                                             |

|             |            |            | PB.7     | I/O      | General purpose input/output digital pin                                        |

| 22          | 13         |            | CTS1     | Ι        | CTS1: Clear to Send input pin for UART1                                         |

|             |            |            | nCS      | 0        | EBI chip select enable output pin                                               |

| 23          | 14         | 10         | LDO      | Р        | LDO output pin                                                                  |

| 24          | 15         | 11         | VDD      | Р        | Power supply for I/O ports and LDO source for internal PLL and digital function |

| 25          | 16         | 12         | VSS      | Р        | Ground                                                                          |

| 26          |            |            | PE.12    | I/O      | General purpose input/output digital pin                                        |

| 27          |            |            | PE.11    | I/O      | General purpose input/output digital pin                                        |

| 28          |            |            | PE.10    | I/O      | General purpose input/output digital pin                                        |

| 29          |            |            | PE.9     | I/O      | General purpose input/output digital pin                                        |

| Pin No.     |            |            |          |          |                                                              |      |     |                                          |

|-------------|------------|------------|----------|----------|--------------------------------------------------------------|------|-----|------------------------------------------|

| LQFP<br>100 | LQFP<br>64 | LQFP<br>48 | Pin Name | Pin Type | Description                                                  |      |     |                                          |

| 30          |            |            | PE.8     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 31          |            |            | PE.7     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 32          | 17         | 13         | PB.0     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 52          | 17         | 10         | RXD0     | I        | RXD0: Data receiver input pin for UART0                      |      |     |                                          |

| 33          | 18         | 14         | PB.1     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 55          | 10         | 14         | TXD0     | 0        | TXD0: Data transmitter output pin for UART0                  |      |     |                                          |

|             |            |            | PB.2     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 34          | 19         | 15         | RTS0     | 0        | RTS0: Request to Send output pin for UART0                   |      |     |                                          |

| 54          | 19         | 15         | nWRL     | 0        | EBI low byte write enable output pin                         |      |     |                                          |

|             |            |            | T2EX     | I        | Timer2 external capture input pin                            |      |     |                                          |

|             |            |            |          |          |                                                              | PB.3 | I/O | General purpose input/output digital pin |

| 35          | 20         | 16         | CTS0     | I        | CTS0: Clear to Send input pin for UART0                      |      |     |                                          |

| 30          | 20         | 10         | nWRH     | 0        | EBI high byte write enable output pin                        |      |     |                                          |

|             |            |            | T3EX     | I        | Timer3 external capture input pin                            |      |     |                                          |

| 36          | 21         | 17         | PD.6     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| - 50        | 21         |            | CANRX0   | I        | CAN Bus0 RX Input                                            |      |     |                                          |

| 37          | 22         | 18         | PD.7     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 57          | 22         | 10         | CANTX0   | 0        | CAN Bus0 TX Output                                           |      |     |                                          |

| 38          | 23         | 19         | PD.14    | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 50          | 20         | 15         | RXD2     | Ι        | RXD2: Data receiver input pin for UART2                      |      |     |                                          |

| 39          | 24         | 20         | PD.15    | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 39          | 24         | 20         | TXD2     | 0        | TXD2: Data transmitter output pin for UART2                  |      |     |                                          |

| 40          |            |            | PC.5     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 40          |            |            | MOSI01   | I/O      | MOSI01: SPI0 2 <sup>nd</sup> MOSI (Master Out, Slave In) pin |      |     |                                          |

| 41          |            |            | PC.4     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 41          |            |            | MISO01   | I/O      | MISO01: SPI0 2 <sup>nd</sup> MISO (Master In, Slave Out) pin |      |     |                                          |

|             |            |            | PC.3     | I/O      | General purpose input/output digital pin                     |      |     |                                          |

| 42          | 25         | 21         | MOSI00   | I/O      | MOSI00: SPI0 MOSI (Master Out, Slave In) pin                 |      |     |                                          |

|             |            |            | I2SDO    | 0        | I2SDO: I <sup>2</sup> S data output                          |      |     |                                          |

| Pin No.     |            |            |              |          |                                                     |  |  |  |

|-------------|------------|------------|--------------|----------|-----------------------------------------------------|--|--|--|

| LQFP<br>100 | LQFP<br>64 | LQFP<br>48 | Pin Name     | Pin Type | Description                                         |  |  |  |

|             |            |            | PC.2         | I/O      | General purpose input/output digital pin            |  |  |  |

| 43          | 26         | 22         | MISO00       | I/O      | MISO00: SPI0 MISO (Master In, Slave Out) pin        |  |  |  |

|             |            |            | I2SDI        | I        | I2SDI: I <sup>2</sup> S data input                  |  |  |  |

|             |            |            | PC.1         | I/O      | General purpose input/output digital pin            |  |  |  |

| 44          | 27         | 23         | SPICLK0      | I/O      | SPICLK0: SPI0 serial clock pin                      |  |  |  |

|             |            |            | I2SBCLK      | I/O      | I2SBCLK: I <sup>2</sup> S bit clock pin             |  |  |  |

|             |            |            | PC.0         | I/O      | General purpose input/output digital pin            |  |  |  |

| 45          | 28         | 24         | SPISS00      | I/O      | SPISS00: SPI0 slave select pin                      |  |  |  |

|             |            |            | I2SLRCL<br>K | I/O      | I2SLRCLK: I <sup>2</sup> S left right channel clock |  |  |  |

| 46          |            |            | PE.6         | I/O      | General purpose input/output digital pin            |  |  |  |

|             |            |            | PE.5         | I/O      | General purpose input/output digital pin            |  |  |  |

| 47          | 29         |            | PWM5         | I/O      | PWM5: PWM output/Capture input                      |  |  |  |

|             |            |            | T1EX         | I        | Timer1 external capture input                       |  |  |  |

|             |            |            | PB.11        | I/O      | General purpose input/output digital pin            |  |  |  |

| 48          | 30         |            | ТМ3          | I/O      | TM3: Timer3 event counter input / toggle output     |  |  |  |

|             |            |            | PWM4         | I/O      | PWM4: PWM output/Capture input                      |  |  |  |