### Le9502

### Ringing Subscriber Line Interface Circuit VE950 Series

### **APPLICATIONS**

- Short/Medium Loop: approximately 2000 ft. of 26 AWG, and 5 REN loads

- Voice over IP/DSL Integrated Access Devices, Smart Residential Gateways, Home Gateway/Router

- Cable Telephony NIU, Set-Top Box, Home Side Box, Cable Modem, Cable PC

- Fiber–Fiber In The Loop (FITL), Fiber to the Home (FTTH)

- Wireless Local Loop, Intelligent PBX, ISDN NT1/TA

### **FEATURES**

### ■ Integrated Dual-Channel Device

- Built-in boost switching power supply tracks line voltage minimizing power dissipation

- Only +3.3 V and +12 V (nominal) required

- Wide range of input voltages (+8 V to +40 V) supported

- Minimal external discrete components

- 44-pin eTQFP package

### Ringing

- 70 Vpk into 5REN

- 90 Vpk capable

- Sinusoidal or trapezoidal capability

- DC offset support

- Common differential interface for both channels

### ■ World Wide programmability:

- Two-wire AC impedance

- Dual Current Limit

- Loop closure and ring trip thresholds

### ■ Five SLIC States, including:

- Low power Standby state

- Reverse Polarity

### RELATED LITERATURE

- 081189 Le9500 RSLIC Device Data Sheet

- 081208 Le9501 RSLIC Device Data Sheet

- 080696 Le77D11 VoSLIC™ Device Data Sheet

- 080697 Le78D11 VoSLAC™ Device Sheet

- 080716 Le77D11 /Le78D11 Chip Set User's Guide

- 080780 Layout Considerations for the Le77D11 and Le9502 Devices Application Note

### ORDERING INFORMATION

| Device    | Package <sup>1</sup>         | Packing <sup>2</sup> |

|-----------|------------------------------|----------------------|

| Le9502BTC | 44-pin eTQFP (Green Package) | Tray                 |

- The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

- For delivery using a tape and reel packing system, add a "T" suffix to the OPN (Ordering Part Number) when placing an order.

### DESCRIPTION

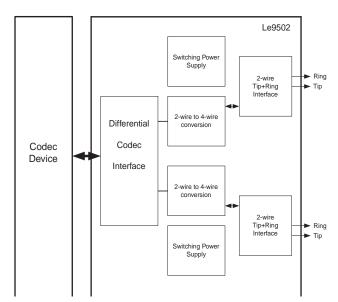

The Zarlink Le9502 Ringing Subscriber Line Interface Circuit (RSLIC) device from the VE950 series has enhanced and optimized features to directly address the requirements of Voice over Broadband applications. Its goal is to reduce system level costs, space, and power through higher levels of integration, and to reduce the total cost of ownership by offering better quality of service. The Le9502 RSLIC device provides a totally configurable solution to the BORSCHT functions for two lines. The resulting system is less complex, smaller, and denser, yet cost effective with minimal external components.

The Le9502 RSLIC device requires only two power supplies: +3.3 VDC and nominally +12 VDC. The latter power supply can range from +8 VDC to +40 VDC, depending on the application. A single TTL-level clock source drives an external transistor which controls the ramp voltage that in turn feeds the switching regulators. Five programmable states are available: Active, Reverse Polarity, Ringing, Standby, and Disconnect. The DC feed, two-wire AC input impedance, hook-switch threshold, and ring trip threshold are programmable via external discrete components. Binary fault detection is provided upon application of fault conditions or thermal overload.

### **BLOCK DIAGRAM**

### **TABLE OF CONTENTS**

| Applications1                         |

|---------------------------------------|

| Features                              |

| Related Literature1                   |

| Ordering Information1                 |

| Description                           |

| Block Diagram1                        |

| Product Description3                  |

| Block Descriptions3                   |

| Two-Wire Interface                    |

| Switcher Controller                   |

| Signal Transmission                   |

| Fault Detection9                      |

| Signal Conditioning                   |

| Reference Current Generator           |

| Control Logic                         |

| Connection Diagram                    |

| Pin Descriptions                      |

| Absolute Maximum Ratings              |

| Operating Ranges                      |

| Electrical Characteristics            |

| Supply Currents and Power Dissipation |

| Specifications                        |

| Device Specifications                 |

| Test Circuit                          |

| Application Circuit                   |

| Line Card Parts List                  |

| Physical Dimensions                   |

| 44-Pin eTQFP                          |

| Revision History                      |

| Revision A1 to B1                     |

| Revision B1 to C1                     |

| Revision C1 to D1                     |

| Revision D1 to E1                     |

| Revision E1 to F1                     |

| Revision F1 to G1                     |

| Revision G1 to G2                     |

| Revision G2 to G3                     |

### PRODUCT DESCRIPTION

The VE950 series Le9502 RSLIC device uses reliable, dielectrically isolated, fully complementary bipolar technology to implement BORSCHT functions for short loop applications. Internal power dissipation is minimized by two independent line voltage tracking, buck-boost switching regulators. Two power supplies are required: 3.3 V and a positive supply ( $V_{SW}$ ). A TTL-level clock is required to drive the switching regulator. Five programmable states control loop signaling, transmission, and ringing. The Le9502 RSLIC device DC current feed limit ( $I_{SC}$ ) is resistor-programmable up to 45 mA.

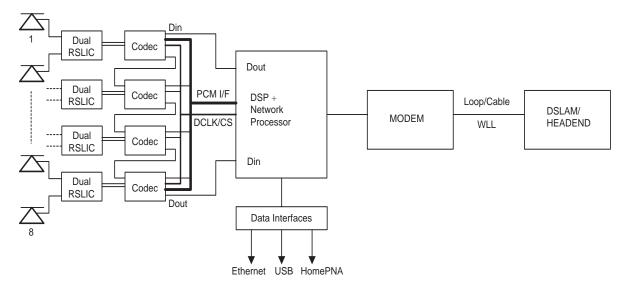

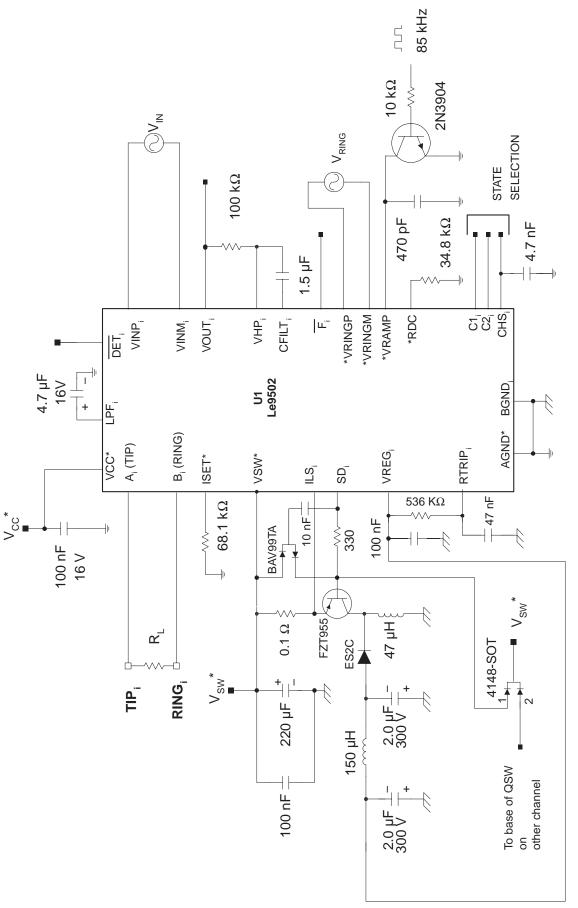

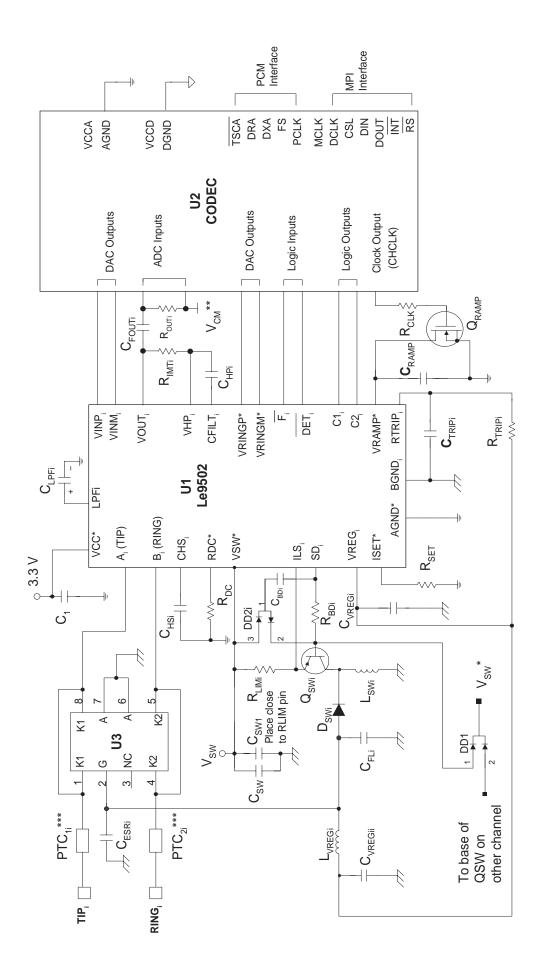

Figure 1. Typical Le9502 RSLIC/Codec Application in an 8-Port Integrated Access Device in Customer Premises

### **BLOCK DESCRIPTIONS**

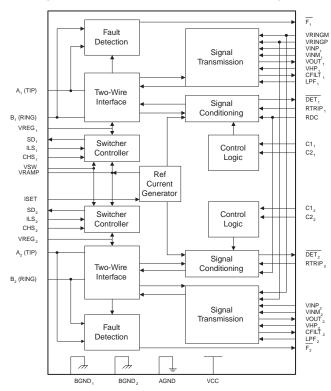

Figure 2. Le9502 RSLIC Device Block Diagram

### Two-Wire Interface

The two-wire interface block provides DC current and sends/receives voice signals to a telephone connected via the  $A_i(Tip)$  and  $B_i(Ring)$  pins. The  $A_i(Tip)$  and  $B_i(Ring)$  pins are also used to send the ringing signal to the telephone. The Le9502 RSLIC device can also be programmed in Disconnect state to place the  $A_i$  and  $B_i$  pins at high impedance with the Switching Regulator disabled.

### DC Feed

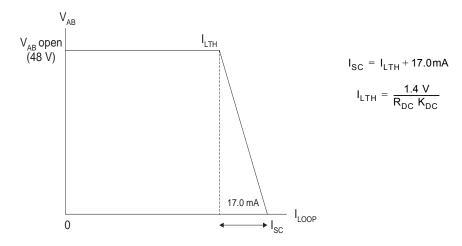

DC feed is controlled in the Le9502 RSLIC device. Only the current limit threshold (I<sub>LTH</sub>) can be set via the RDC pin. The current limit threshold can be set from 0 to 30 mA.

Referring to Figure 3, the DC feed curve consists of two distinct regions. The first region is a flat anti-sat region that supplies a constant Tip-Ring voltage ( $V_{AB}$  open). The second region is a constant current region that begins when the loop current reaches the programmed current limit threshold ( $I_{LTH}$ ). This region looks like a constant current source with 3.2 k $\Omega$  shunt resistor. The short circuit current is nominally 17.0 mA greater than  $I_{LTH}$ .

A block diagram of the DC feed control circuit is shown in Figure 4. In the anti-sat region, current source CS1 creates a constant reference current, which is limited to sub-voice frequencies by  $C_{LPFi}$ . This filtered current is then steered by the Polarity Control, depending on whether the SLIC mode is Standby, Normal Active, or Reverse Polarity. The steered current then takes one of two paths to the Level Shift block, where it is used to set  $V_A$  (TIP) and  $V_B$  (RING). This voltage from the Level Shift block is buffered by the output amplifiers and appears at  $A_i$  (TIP) and  $B_i$  (RING).

When  $I_{LOOP}/500$  becomes greater than  $I_{LTH}/500$ , the difference is subtracted from CS1, and again filtered by  $C_{LPFi}$ . This reduced current causes a reduced DC feed voltage. In Standby and Normal Active,  $A_i$  (TIP) is held constant, while  $B_i$  (RING) is changed to reduce the feed voltage. In Reverse Polarity,  $A_i$  (TIP) and  $B_i$  (RING) are swapped. When  $(I_{LOOP}-I_{LTH})/500$  = CS1, all of the current from CS1 is subtracted, making the TIP-RING voltage = 0 V. This is the short circuit condition. At least 100  $\Omega$  loop and fuse resistance are required to ensure stability of the  $A_i$  (TIP) and  $B_i$  (RING) output amplifiers.

The capacitor  $C_{LPFi}$ , in conjunction with an internal 25 k $\Omega$  resistor (not shown), is used to create a low pass filter for the DC feed loop. This capacitor should nominally be 4.7  $\mu$ F, setting a 1.4 Hz pole. The purpose of this capacitor is to stabilize the DC feed and filter any AC components.

Figure 3. DC Feed Curve

### Note:

- 1.  $R_{DC}$  = external resistor from RDC to AGND

- 2.  $V_{AB} = V_{Ai} V_{Bi}$  Tip-Ring differential voltage

- 3.  $K_{DC}$  = Le9502 RSLIC device DC current gain, which is:  $K_{DC} = \frac{1}{500}$

- 4.  $I_{SC}$  = Loop short circuit current limit.

- 5.  $I_{LTH} = Loop current limit threshold.$

RDC Current Mirrors

CLPFi

Current Mirrors

CLPFi

Current Mirrors

Rs A<sub>i</sub> (TIP)

RDC

Roc\*

Rs A<sub>i</sub> (TIP)

Roco

Rs B<sub>i</sub> (RING)

Figure 4. DC Feed Block Diagram, Active and Standby Modes

Note:

\* denotes external components.

### Ringing

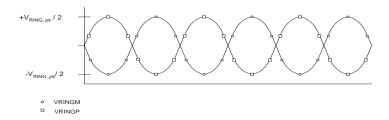

The Le9502 RSLIC device only provides a method for creating internal ringing. Internal ringing is accomplished by applying a single or differential ringing waveform using the VRINGP and VRINGM pins, and placing the Le9502 RSLIC device into the ringing state via the device's control bits. When the Le9502 RSLIC device is in the Ringing state, the gain from the Le9502 RSLIC device's differential ringing input pin to the output, is  $K_R$  (the ringing voltage gain). The output waveform is a quasi-balanced waveform as shown below in Figure 5). On the positive half cycle of the input waveform, the  $A_i$  (TIP) lead of the Le9502 RSLIC device is near -4 V, and the  $B_i$  (RING) lead is brought negative. Likewise, on the negative half cycle of the input waveform, the  $B_i$  (RING) lead of the Le9502 RSLIC device is held near -4 V, while the  $A_i$  (TIP) lead is brought more negative. The low cost regulator solution, shown in the application circuit on page 20, incorporates the use of a higher power PNP bipolar switching transistor in the switching circuit that enables the Le9502 to provide a 90 Vpk ringing signal into a lower REN load. The waveform can be either sinusoidal or trapezoidal under the control of the codec device.

Figure 5. Ringing Waveforms

A. Voltage Applied to VRING Input (VRINGP, VRINGM)

B. Voltage Output at A (TIP) (dashed line) and B (RING) (solid line) Pins

Le9502 Data Sheet

For the reference schematic, Zetex part FZT955 in a SOT-223 package is used. Its  $V_{CEO}$  rating is 140 V. The switching efficiency and overhead voltage of the regulator allows a robust 70 Vpk ringing signal into a 5 REN load with  $V_{SW}$  = 12 V.

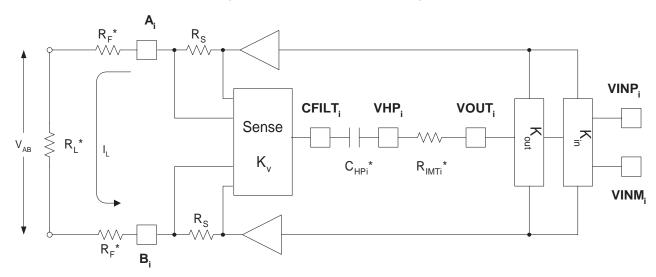

### Switcher Controller

The switcher controller's main function is to provide a negative power supply ( $V_{REG}$ ) that tracks Tip and Ring voltage for the 2-wire interface. As the Tip and Ring voltage decreases, the switcher will likewise lower  $V_{REG}$ . In doing so, the switcher saves power because the device is not forced to maintain static supply voltage in all states.

The switching power supply controller uses a discontinuous mode, buck-boost voltage converter topology. The frequency of operation is set by the ISET resistor and the VRAMP capacitor values. An external clock with approximately a 10% duty cycle drives the gate (base) of a small-signal FET which is used to reset the VRAMP capacitor voltage, creating the ramp voltage used internally by the switching power supply control circuitry. This clock signal controls the switching supply's operating frequency. The switcher circuit is nominally designed for 85 kHz operation based on the *Application Circuit* on page 20.

The duty cycle of the switching transistors is continuously variable up to 90% depending on the magnitude of the error voltage on the compensation (CHS) pin. The error signal on CHS is compared to the ramp signal. The ramp rate of the VRAMP signal is set by the ISET resistor ( $R_{SET}$ ) and the VRAMP capacitor ( $R_{CRAMP}$ ). A 1%  $R_{CRAMP}$  resistor should be chosen first (see <u>Signal Conditioning on page 9</u>) before using the following equation to calculate  $R_{CRAMP}$

$$C_{RAMP\_max} = I_{RAMP\_min} \bullet [(100\% - t_{CHCLK\_max}) / (f_{CHCLK} \bullet R_{SET\_max})]$$

where  $I_{RAMP\_min}$  is the current going through  $C_{RAMP}$ ,  $t_{CHCLK\_max}$  is maximum duration of Chopper Clock High Duty Cycle provided in the specification section,  $f_{CHCLK}$  is the frequency of the chopper clock, and  $R_{SET\_max}$  is  $R_{SET\_nom}$  \* 1.01. The calculated value for  $C_{RAMP}$  is the maximum value that can guarantee the switcher to operate. A NPO dielectric capacitor is recommended for  $C_{RAMP}$

When the external clock signal goes from a logic Low to a logic High, it will pull VRAMP voltage low which causes internal clock (from the square wave converter) to go Low, turning on the external power switch. When the external clock signal goes from High to Low, C<sub>RAMP</sub> will charge up. When the VRAMP voltage exceeds internal voltage threshold, the rising edge of the internal clock from the square wave converter will reset the current limit latch getting it ready for the next cycle and turn off the external power switch. Also on a cycle-by-cycle basis, one of the following three events will shut off the power switch, depending on which event occurs first:

- a) The VRAMP voltage exceeds the error voltage that is integrated on the CHS node (normal voltage feedback operation.)

- b) The VRAMP voltage exceeds the internal voltage threshold.

- c) The power switch current limit threshold is reached (set by R<sub>LIM</sub>).

Cycle-by-cycle current limiting is provided by the current sense  $ILS_i$  pin which senses the external power switch current through the resistor  $R_{LIM}$ . If this pin exceeds  $VT_{ILS}$ , nominally -0.28 V with respect to  $V_{SW}$ , the switching supply will set the current limit latch and shut off the external switch drive until the next time the VRAMP pin is pulled Low to reset the latch. Thus the peak inductor current, and also peak switching converter power output can be controlled on a cycle-by-cycle basis and set by the equation  $I_{LIM} = (VT_{ILS})/R_{LIM}$ .

This sensing configuration has the added benefit that if the clock signal is removed for some reason, the power switch cannot be left on indefinitely. Leaving the ILS<sub>i</sub> pin unconnected or shorting this pin to VSW will disable current limiting, but is not recommended.

A leading edge blanking filter is added at the output of the latch to ignore the first 150 ns of a current limit event. This feature is used to ignore a false current trip that may be caused by the power switch driving the reverse recovery charge  $(Q_{RR})$  of the external power rectifier.

The on chip driver is designed to drive either an external PNP or a PMOS power device. Its output drive is clamped between 7-9 V below  $V_{SW}$ , and can source or sink approximately 100 mA. The driver has approximately 50  $\Omega$  of source resistance. The additional resistance should be added from the  $SD_i$  pin to the base of the external power device if a PNP is used to limit base drive for optimal efficiency.

When using a PMOS power switch, the  $SD_i$  pin will be able to drive approximately 100 mA of drive current to the gate of the PMOS device, and an internal clamp will limit the drive between 7-9 V. To keep system losses to a minimum, it is recommended that low gate charge be given higher consideration over low  $r_{DS(on)}$  when selecting a power PMOS device for your application.

vsw LEADING EDGE BLANKING FILTER LATCH in active 800K OUTPUT ILS,  $I = \frac{8 \text{ V}}{800 \text{K}}$  in ringing V<sub>REF</sub> SDir CHS COMPARATOR Ref. Current Generator ISET internal clock 91 square wave converter 85 kHz VRAMP 10% High Duty Cycle 800 k VREG,

Figure 6. Switching Power Supply Block Diagram

### Note:

<sup>\*</sup> Denotes external components.

<sup>\*\*</sup> Generated internally by band gap  $\cong$  1.4 V.

<sup>\*\*\*</sup>  $V_{RING} = V_{RINGP} - V_{RINGM}$

<sup>\*\*\*\*</sup> Preferably, the external clock should be Low in startup. For a system (codec) which has a high impedance at the clock output in start up, the additional  $R_{\text{Base}}$  and  $R_{\text{BG}}$  resistors are recommended with values of 10 k $\Omega$  and 100 k $\Omega$  respectively.

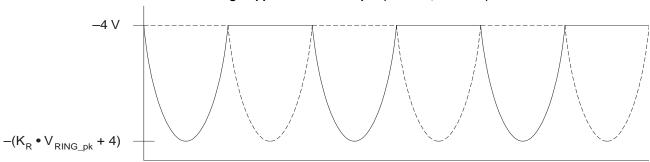

### Signal Transmission

In Normal Active and Reverse Polarity states, the AC line current is sensed across the  $R_S$  resistors (see Figure 7), summed and attenuated, and converted to voltage at the  $CFILT_i$  pin. The voltage then goes through a high pass filter implemented using the external  $C_{HPi}$  capacitor, is amplified, and sent to the codec device at the  $VOUT_i$  pin. This output is proportional to the AC metallic component of the line voltage. Additionally, the signal transmission block receives the analog signal from the codec device. The analog signal is amplified and sent to the line. Finally, a proportion of the signal at  $V_{OUT}$  is fed back to the line.

There are three parameters which define the AC characteristics of the Le9502 RSLIC device. First is the input impedance presented to the line or 2-wire ( $V_{AB}$ ) side ( $Z_{2WIN}$ ), second is the gain from the 4-wire ( $V_{IN}$ ) to the 2-wire ( $V_{AB}$ ) side ( $G_{42}$ ), and third is the gain from the 2-wire ( $V_{AB}$ ) side to the 4-wire ( $V_{OUT}$ ) side ( $G_{24}$ ).

### Input Impedance (Z<sub>2WIN</sub>)

Z<sub>2WIN</sub> is the impedance presented to the line at the 2-wire side and is defined by:

$$Z_{2WIN} = 2R_F + K_V K_{OUT} R_{IMT}$$

where 2 •  $R_F$  is the total resistance of the external fuse resistors in the circuit,  $R_{IMT}$  is the impedance setting resistor for return loss purpose,  $K_{OUT}$  is the gain from  $V_{OUT}$  to  $V_{AB}$ , and  $K_V$  is the voice current gain defined in the Transmission Specifications Table. Note that the equation reveals that  $Z_{2WIN}$  is a function of the selectable resistors,  $R_{IMT}$  and  $R_F$ . For example, if  $R_F = 0~\Omega$  and  $R_{IMT}$  is 100 k, the terminating impedance is 600  $\Omega$ . This is the configuration used in this data sheet for defining the device specifications. However, in a real application,  $R_F = 50~\Omega$  is recommended, and RIMT is set to 80.6  $K\Omega$  to provide an approximate 600  $\Omega$  input impedance.

### 2-Wire to 4-Wire Gain (G<sub>24</sub>)

The 2-wire to 4-wire gain is the gain from the phone line to the VOUT output of the Le9502 RSLIC device. To solve for  $G_{24}$ , set  $V_{IN} = V_{INP} - V_{INM} = 0$  V (see Figure 7).

$$\frac{V_{OUT}}{V_{AB}} = G_{24} = \frac{1}{\frac{2R_F}{K_V R_{IMT}} + K_{OUT}}$$

or

$$G_{24} = -20\log\left(K_{OUT} + \frac{2R_F}{K_V R_{IMT}}\right) \text{ in dB}$$

### 4-Wire to 2-Wire Gain (G<sub>42</sub>)

$G_{42}$  is the gain from the VIN input to the line. This gain is defined as  $V_{AB}/V_{IN}$ . For the analysis of  $G_{42}$ , substitute the load resistor  $R_L$  in place of the test voltage source  $V_T$  (see <u>Figure 7</u>).

$$\frac{V_{AB}}{V_{IN}} = G_{42} = \frac{K_{IN} \left(\frac{R_L}{R_L + 2R_F}\right)}{\left(1 + \frac{K_{OUT}R_{IMT}K_V}{R_L + 2R_F}\right)}$$

or

$$G_{42} = -20 log \left( \frac{K_{IN} \left( \frac{R_L}{R_L + 2R_F} \right)}{\left( 1 + \frac{K_{OUT} R_{IMT} K_V}{R_L + 2R_F} \right)} \right) \quad \text{in dB}$$

where  $K_{IN}$  is the gain from VIN to  $V_{AB}$ .

Le9502 Data Sheet

Figure 7. Transmission Block Diagram

Note:

### **Fault Detection**

Each channel of the Le9502 RSLIC device has a fault detection pin,  $\overline{F}_1$  or  $\overline{F}_2$ . These pins are driven low when a longitudinal current fault or foreign voltage fault occurs. When not in Disconnect state, there are three conditions that will cause the  $\overline{F}_i$  pin to indicate a fault condition:

- |I<sub>A</sub> I<sub>B</sub>| > I<sub>LONG</sub>

- In Normal Active and Standby state, a foreign voltage fault occurs in which V<sub>A</sub> is above ground or V<sub>B</sub> is close to V<sub>REG</sub>.

- In Reverse Polarity state, a foreign voltage fault occurs in which V<sub>B</sub> is above ground or V<sub>A</sub> is close to V<sub>REG</sub>.

In the Disconnect state, fault detection is not supported.

### **Signal Conditioning**

The  $\overline{\text{DET}}_{i}$  outputs are used for both off-hook and ring trip detection. The threshold for each of these functions is set by external components.

If the Le9502 RSLIC device is in Low Power Standby or Normal Active modes, the  $\overline{DET_i}$  output is used to indicate an off-hook condition. The following equation will set the off-hook threshold:

$$R_{SET} = \frac{500 \bullet V_{REF}}{I_{offhook threshold}}$$

where  $I_{offhook\_threshold}$  is a user-chosen off-hook current threshold.  $R_{SET}$  is 68.1 k $\Omega$  as specified in the <u>Application Circuit on page 20</u>. This value produces a nominal off-hook threshold of 10.3 mA.

If the SLIC device is in the Ringing state, the  $\overline{DET_i}$  output will indicate the ring trip condition. The threshold for ring trip detection is set with an external resistor,  $R_{TRIP}$ , from the RTRIP<sub>i</sub> to VREG<sub>i</sub> pins. The ring trip threshold is set on a per-channel basis. To select the value of  $R_{TRIP}$ , the following equation is used:

$$R_{TRIP} = \frac{500 \bullet (V_{RING PK} + 10 V)}{I_{trip\_threshold}}$$

where

For Zarlink's application, the ring trip current threshold is  $7\underline{4.6}$  mA which results in a R  $_{TRIP}$  value of 536 k $\Omega$ .  $C_{TRIP}$  is used as a transient filter to debounce the output ring trip signal at the  $\overline{DET_i}$  pin. The value for  $C_{TRIP}$  is nominally 47 nF as in the  $\underline{Application}$   $\underline{Circuit}$  on page 20.

The RDC<sub>i</sub> pin is used to set the DC feed current limit, as described in <u>DC Feed on page 4</u>.

<sup>\*</sup> denotes external components.

### **Thermal Overload**

When the die temperature around the power amplifier of a Le9502 RSLIC device channel reaches approximately 160° C, the  $\overline{F}_i$  pins are pulled Low and  $V_{REG}$  will collapse. At the same time, all the blocks controlling that channel of the device are shut off, except for the logic interface block. The SLIC channel goes into a state similar to Disconnect, making the line current zero. When the temperature drops below 145° C, the SLIC channel returns to its previous state. It is important to recognize that even while a channel experiences thermal overload, the state of the device can be modified.

### **Reference Current Generator**

To set the hook switch threshold for both channels, an external resistor ( $R_{SET}$ ) from ISET to AGND pins is used. For  $R_{SET}$  value, please refer to <u>Line Card Parts List on page 21</u>.

Moreover, internally this block generates I<sub>RAMP</sub> which is used to help set the frequency of operation desired for the switcher.

### **Control Logic**

Each channel of the Le9502 RSLIC device has three input pins from a codec device (CHS, C2, and C1). The inputs set the operational state of each channel. There are five operational SLIC device states (See Table 1): Low Power Standby, Disconnect, Normal Active, Reverse Polarity, and Ringing

Table 1. SLIC Device Operating States

| CHS           | C2 | C1 | Operating State   | Description                                                                                                                                                                                                  |

|---------------|----|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Float         | 0  | 0  | Low Power Standby | Voice Transmission Disabled. Loop current capability is reduced.                                                                                                                                             |

| Float         | 0  | 1  | Reverse Polarity  | Similar to normal active, but DC polarity is reversed so that the Ring lead is more positive than the Tip. Supports on hook transmission.                                                                    |

| Float         | 1  | 0  | Normal Active     | SLIC device fully operational. Supports on hook transmission.                                                                                                                                                |

| Float         | 1  | 1  | Ringing           | Ringing state with $V_{AB}$ set to $K_{R^{\bullet}}(V_{RINGP} - V_{RINGM})$ . The switching supply maintains minimum headroom for the sourcing and sinking amplifiers in order to maximize power efficiency. |

| Pull<br>Low * | 0  | 0  | Disconnect**      | SLIC device is shut down. Mainly used if a line fault is detected or to shut down a line.                                                                                                                    |

### Note:

<sup>\*</sup> See CHS Specifications on page 17.

<sup>\*\*</sup> Standby state with switcher turned off.

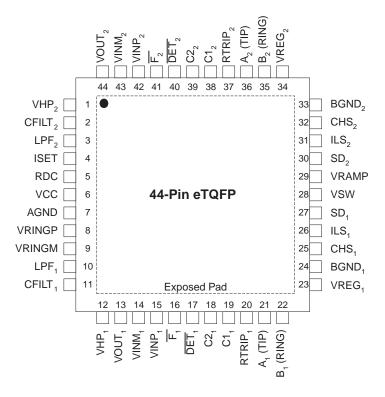

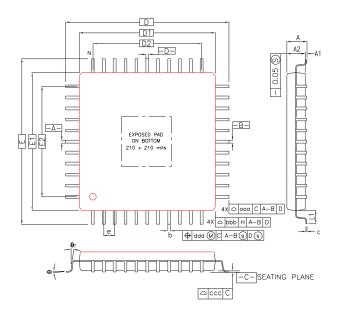

### **CONNECTION DIAGRAM**

Note:

1. Pin 1 is marked for orientation.

### **PIN DESCRIPTIONS**

| Pin Name                          | Туре     | Description                                                                                                                                                                                                                                                                    |

|-----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND                              | Ground   | Analog and digital ground return for VCC circuitry (common to both channels).                                                                                                                                                                                                  |

| A <sub>1,2</sub> (TIP)            | Output   | A (TIP lead) power amplifier output for channels 1 and 2.                                                                                                                                                                                                                      |

| BGND <sub>1,2</sub>               | Ground   | Battery ground return for power amplifiers on channel 1 and 2.                                                                                                                                                                                                                 |

| B <sub>1,2</sub> (RING)           | Output   | B (RING lead) power amplifier output for channels 1 and 2.                                                                                                                                                                                                                     |

| C1 <sub>1</sub> , C2 <sub>1</sub> | Input    | Logic control inputs to control channel 1 state.                                                                                                                                                                                                                               |

| C1 <sub>2</sub> , C2 <sub>2</sub> | Input    | Logic control inputs to control channel 2 state.                                                                                                                                                                                                                               |

| CFILT <sub>1,2</sub>              | Output   | AC coupling pin for 4-wire amplifier                                                                                                                                                                                                                                           |

| CHS <sub>1,2</sub>                | Input    | Compensation node for switching power supply channels 1 and 2.                                                                                                                                                                                                                 |

| DET <sub>1,2</sub>                | Output   | Loop detector or ring trip detector output, depending on state of control bits. If the SLIC device is in Ringing state then ring trip indication is given, if the SLIC device is in Low Power Standby, Normal Active or Reverse Polarity then hook switch indication is given. |

| F <sub>1,2</sub>                  | Output   | Fault detect pin for channels 1 and 2. A low indicates a fault for the respective channel, which can be triggered by large longitudinal current, ground key, or thermal overload.                                                                                              |

| ILS <sub>1,2</sub>                | Input    | Voltage sense pin to limit peak current in external switching power supply transistor (channels 1 and 2).                                                                                                                                                                      |

| ISET                              | Input    | Dual purpose pin: 1. sets the hook switch detection threshold (for both channels); 2. sets the current source for triangle wave generation for the switching power supply.                                                                                                     |

| LPF <sub>1,2</sub>                | Output   | A capacitor tied to from this pin to AGND stabilizes the DC feed loop, and lowers Idle Channel Noise.                                                                                                                                                                          |

| RDC                               | Input    | Resistor connection to GND. Sets DC feed current limit, I <sub>LTH</sub> (common to both channels).                                                                                                                                                                            |

| RTRIP <sub>1,2</sub>              | Input    | Network tied from RTRIP to VREG. Sets the ring trip threshold detection level.                                                                                                                                                                                                 |

| SD <sub>1,2</sub>                 | Output   | Base (gate) drive for switching power supply transistor (channels 1 and 2).                                                                                                                                                                                                    |

| VCC                               | Supply   | Positive supply for internal VCC circuitry (common to both channels).                                                                                                                                                                                                          |

| VHP <sub>1,2</sub>                | Output   | High pass invert summing node of the VOUT amplifier driven by the AC current coming from CFILT <sub>1</sub> and CFILT <sub>2</sub> .                                                                                                                                           |

| VOUT <sub>1,2</sub>               | Output   | Analog (4-wire side) VOUT amplifier transmit output                                                                                                                                                                                                                            |

| VINM <sub>1,2</sub>               | Input    | Differential (P-M) analog (4-wire side) voice signal input.                                                                                                                                                                                                                    |

| VINP <sub>1,2</sub>               | прис     | Dinerential (F-IVI) allalog (4-Wire Slue) voice signal iliput.                                                                                                                                                                                                                 |

| VRAMP                             | Input    | Switching power supply ramp voltage that sets the frequency of the switcher and the maximum duty cycle (common to both channels).                                                                                                                                              |

| VREG <sub>1,2</sub>               | Supply   | Negative power supply generated by SLIC device Switching Regulator. (channels 1 and 2)                                                                                                                                                                                         |

| VRINGP, VRINGM                    | Input    | Differential ringing input (common to both channels).                                                                                                                                                                                                                          |

| vsw                               | Supply   | Positive supply used by the SLIC device to generate the negative regulated supplies of VREG <sub>1</sub> , VREG <sub>2</sub> (common to both channels).                                                                                                                        |

| Exposed Pad                       | Isolated | Exposed pad on underside of device must be connected to a heat spreading area. The AGND plane is recommended.                                                                                                                                                                  |

### **ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage temperature                                              | –55 to +150°C                    |

|------------------------------------------------------------------|----------------------------------|

| Ambient temperature, under bias                                  | -40° to +85°C                    |

| V <sub>CC</sub> with respect to AGND                             | -0.4 to +6.5 V                   |

| V <sub>REG</sub> with respect to BGND                            | +0.4 to –115 V                   |

| BGND with respect to AGND                                        | -100 to 100 mV                   |

| A (TIP) or B (RING) to BGND:                                     |                                  |

| Continuous                                                       | V <sub>REG</sub> –1 to BGND +1   |

| 10 ms (F = 0.1 Hz)                                               | V <sub>REG</sub> –5 to BGND +5   |

| 1 μs (F = 0.1 Hz)                                                | V <sub>REG</sub> –10 to BGND +10 |

| 250 ns (F = 0.1 Hz)                                              | V <sub>REG</sub> –15 to BGND +15 |

| Current from A (TIP) or B (RING)                                 | ±150 mA                          |

| C1 and C2 with respect to AGND                                   | -0.4 to VCC + 0.4 V              |

| CHCLK                                                            | AGND to VCC                      |

| $V_{SW}$                                                         | BGND to +44 V                    |

| Maximum power dissipation,<br>T <sub>A</sub> = 85° C (See notes) | 1.8 W                            |

| Thermal Data:                                                    | $\theta_{JA}$                    |

| In 44-pin eTQFP package                                          | 32° C/W                          |

| Thermal Data:                                                    | θ <sub>JC</sub>                  |

| In 44-pin eTQFP package                                          | 9.2° C/W                         |

| ESD Immunity (Human Body Model)                                  | JESD22 Class 1C compliant        |

### Note:

Thermal limiting circuitry on chip will shut down the circuit at a junction temperature of about 160°C. Continuous operation above 145°C junction temperature may degrade device reliability.

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Specified performance requires that the exposed thermal pad be soldered to an equally sized exposed copper surface, which, in turn, conducts heat through 16 0.3 mm diameter vias on a 1.27 mm pitch to a large (> 500 mm²) internal copper plane. (Refer to Zarlink application note Layout Considerations for the Le77D112 and Le9502 RSLIC devices, document ID# 081013).

### Package Assembly

Green package devices are assembled with enhanced environmental, compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly.

Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

### OPERATING RANGES

Zarlink guarantees the performance of this device over commercial (0° to 70°C) and industrial (-40° to 85°C) temperature ranges by conducting electrical characterization over each range, and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

### **Environmental Ranges**

| Ambient Temperature | -40° to +85° C |

|---------------------|----------------|

|---------------------|----------------|

### **Electrical Ranges**

| V <sub>CC</sub>  | 3.3 V ± 5%                            |

|------------------|---------------------------------------|

| V <sub>SW</sub>  | 8 to 40 V                             |

| V <sub>REG</sub> | -7 to -110 (0 V in Disconnect state). |

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, test conditions are:  $V_{CC} = 3.3 \text{ V}$ ,  $V_{SW} = 12.0 \text{ V}$ , AGND = BGND, no fuse resistors,  $R_L = 600 \Omega$ , 85 kHz CHCLK,  $I_{LTH}$ =20 mA ( $R_{DC} = 34.8 \text{ k}\Omega$ ). Ringing configuration is  $V_{RING} = V_{RINGP} - V_{RINGM} = 0.7 \text{ Vpk}$ . 20 Hz sinusoidal. Please refer to  $\overline{\textit{Test Circuit on page 19}}$  for all other component values.

# **Supply Currents and Power Dissipation**

|                  |                                                     |          | •                             |         |         |                                      |          |         |                        |         |         |                                 |         |                         |          |

|------------------|-----------------------------------------------------|----------|-------------------------------|---------|---------|--------------------------------------|----------|---------|------------------------|---------|---------|---------------------------------|---------|-------------------------|----------|

| Operation States | Condition                                           | 3.3 V V( | 3.3 V VCC Supply Current (mA) | Current | VREG SI | VREG Supply Current (mA)<br>(Note 4) | ent (mA) | VREG SI | VREG Supply Power (mW) | er (mW) | SLIC De | SLIC Device Power (mW) (Note 5) | ır (mW) | VSW Pin<br>Current (mA) | Note     |

|                  |                                                     | Min      | Тур                           | Max     | Min     | Тур                                  | Max      | Min     | Тур                    | Мах     | Min     | Тур                             | Max     | Тур                     |          |

| Standby          | $R_L = open$<br>$V_{IN} = 0 V$                      | 3.0      | 5.5                           | 8.0     | 0.25    | 1.0                                  | 3.5      | 15.0    | 50.0                   | 130.0   | 20.0    | 75.0                            | 130.0   | 2.0                     | -        |

| Disconnect       | $R_L = open$<br>$V_{IN} = 0 V$                      | 2.0      | 5.0                           | 7.5     | I       | 0.1                                  | I        | 0.0     | 0.5                    | 3.0     | 5.0     | 15.0                            | 25.0    | 0.1                     | ~        |

|                  | $R_L = open$<br>$V_{IN} = 0 V$                      | 4.0      | 0.7                           | 10.0    | 1.0     | 3.0                                  | 5.0      | 90.09   | 200.0                  | 360.0   | 100.0   | 215.0                           | 320.0   | 2.5                     | <b>~</b> |

| Active           | $R_L = 300 \Omega$<br>$V_{IN} = 0 V$                | 4.0      | 7.5                           | 10.0    | 28.0    | 38.0                                 | 48.0     | 500.0   | 850.0                  | 1150.0  | 250.0   | 475.0                           | 650.0   | 1.4                     | ~        |

|                  | $R_L = 900 \Omega$<br>$V_{IN} = 0 V$                | I        | 7.0                           | I       | I       | 26.0                                 | I        | I       | 820.0                  | 1       | 1       | 360.0                           | I       | 4.6                     | 1,2      |

|                  | $R_L = open$<br>$V_{IN} = 0 V$                      | 4.0      | 0.7                           | 10.0    | 1.0     | 3.0                                  | 5.0      | 50.0    | 200.0                  | 360.0   | 100.0   | 215.0                           | 320.0   | 2.5                     | 2,1      |

| Pol Rev          | $R_L = 300 \Omega$<br>$V_{IN} = 0 V$                | 4.0      | 7.5                           | 10.0    | 28.0    | 38.0                                 | 48.0     | 500.0   | 850.0                  | 1150.0  | 250.0   | 525.0                           | 650.0   | 1.4                     | ~        |

|                  | $R_L = 900 \Omega$<br>$V_{IN} = 0 V$                | I        | 0.7                           | _       | I       | 26.0                                 | -        | -       | 833.0                  | 1       | I       | 360.0                           | I       | 4.6                     | 1,2      |

| Ringing          | $R_L = open$<br>$V_{RING} = 0.7 \text{ Vac}$        | I        | 0.7                           | _       | I       | 3.0                                  |          | _       | 152.0                  | I       | I       | 180.0                           | I       | 2.1                     | 1,2      |

| D<br>D<br>D      | $R_L = 1400 \Omega$<br>$V_{RING} = 0.7 \text{ Vac}$ | 4.0      | 7.5                           | 10.0    | 33.0    | 38.0                                 | 42.0     | 2000.0  | 2500.0                 | 2900.0  | 500.0   | 800.0                           | 1010.0  | 5.7                     | 1, 3     |

Notes:

Values shown are for one channel only but are tested with both channels in the same state. Not tested in production. Parameter is guaranteed by characterization or correlation to other tests. Production test forces Vin=0.5Vdc which is equivalent to  $V_{\rm RING}$ =0.7Vac. က

$I_{VSW} = \frac{V_{REG} \bullet I_{VREG}}{n \bullet v}$ , where  $\eta =$  efficiency. For our recommended circuit, an efficiency of 0.6 can be assumed under heavy loads. η • V<sub>SW</sub> 4.

SLIC device power is defined as the power delivered through the VCC and VREG pins minus the power delivered to the load. It does not include any power associated with the VSW pin and the external switcher. δ.

### **SPECIFICATIONS**

### **Device Specifications**

| Specification                                                     | Condition                                                   | Min                  | Тур                                   | Max                  | Unit | Note      |

|-------------------------------------------------------------------|-------------------------------------------------------------|----------------------|---------------------------------------|----------------------|------|-----------|

| Line Characteristics                                              |                                                             |                      |                                       |                      |      |           |

| V <sub>A</sub> , Active<br>V <sub>B</sub> , Reverse Polarity      | R <sub>L</sub> = open                                       |                      | -4                                    |                      |      |           |

| V <sub>A</sub>                                                    | Standby, R <sub>L</sub> = open                              |                      | <b>–</b> 1                            |                      | -    |           |

| V <sub>AB</sub>                                                   | Active or Reverse Polarity,<br>R <sub>L</sub> = open        | 45                   | 48                                    | 53                   | V    | <u>1.</u> |

|                                                                   | Standby, R <sub>L</sub> = open                              | 45                   | 48                                    | 54.5                 | -    |           |

| $V_{REG}$                                                         | Active or Reverse Polarity,<br>R <sub>L</sub> = open        | -50                  | -63                                   | -69                  |      | <u>4.</u> |

|                                                                   | Standby, R <sub>L</sub> = open                              | -48                  | -58                                   | -64                  | 1    |           |

| Current limit threshold, I <sub>LTH</sub> accuracy                | Active or Reverse Polarity and Standby                      | 17.5                 | 20                                    | 22.5                 |      | <u>4.</u> |

| I <sub>SC</sub>                                                   | $R_L$ = 100 Ω, Active or Reverse Polarity; $I_{LTH}$ =20mA. | I <sub>LTH</sub> +10 | I <sub>LTH</sub> +17                  | I <sub>LTH</sub> +29 |      |           |

| 'SC                                                               | $R_L$ = 100 Ω, Standby;<br>$I_{LTH}$ =20mA.                 | I <sub>LTH</sub> +10 | I <sub>LTH</sub> +17                  | I <sub>LTH</sub> +25 | mA   |           |

| Loop Current                                                      | $R_L$ = 600 Ω, Active or Reverse Polarity; $I_{LTH}$ =20mA. | I <sub>LTH</sub> +7  | I <sub>LTH</sub> +11                  | I <sub>LTH</sub> +20 |      |           |

| I <sub>L</sub> accuracy                                           | $R_L$ = 600 Ω, Standby;<br>$I_{LTH}$ =20mA.                 | I <sub>LTH</sub> +7  | I <sub>LTH</sub> +11                  | I <sub>LTH</sub> +20 |      |           |

|                                                                   | Output impedance                                            |                      | 25                                    |                      | kΩ   |           |

| LPF <sub>i</sub>                                                  | Bias voltage with respect to GND                            |                      | 2.2                                   |                      | V    |           |

|                                                                   | Leakage current for capacitor value of 4.7 µF ± 20%         |                      |                                       | 0.1                  | μА   | <u>3.</u> |

| RDC                                                               | Input impedance                                             |                      | 10                                    |                      | Ω    |           |

|                                                                   | Input voltage tolerance                                     | 1.33                 | 1.4                                   | 1.47                 | V    |           |

| Hook Switch detection threshold programming range                 |                                                             | 5                    |                                       | 15                   |      | <u>4.</u> |

| Loop detect threshold tolerance (I <sub>offhook_threshold</sub> ) | Standby, Active and Reverse Polarity                        | 8.8                  | 11.5                                  | 14.5                 | mA   |           |

| Ring trip current accuracy (I <sub>trip_threshold</sub> )         | V <sub>REG</sub> i = -85V                                   | 59.7                 | 80                                    | 89.5                 |      |           |

| Ringing                                                           |                                                             | <u> </u>             |                                       | Į                    |      | I.        |

| V <sub>A</sub> , V <sub>B</sub>                                   | $V_{RING}$ = 0 V, $R_L$ = 1400 $\Omega$                     |                      | -4                                    |                      |      | <u>3.</u> |

| V <sub>AB</sub> offset                                            | $V_{RING}$ = 0 V, $R_L$ = 1400 $\Omega$                     | -2                   |                                       | +2                   | V    |           |

| Ringing voltage gain (K <sub>R</sub> )                            | Ringing, $K_R = \frac{V_{AB}}{V_{RING}}$ ,                  | 95                   | 100                                   | 105                  | V/V  | <u>1.</u> |

|                                                                   | Vin = 0.7Vpk, $R_L$ = 1400 $\Omega$                         |                      |                                       |                      |      |           |

| VRINGP, VRINGM Input Range                                        |                                                             | -0.3                 |                                       | 2.4                  | V    | <u>4.</u> |

| (VRINGP - VRINGM) Differential Input Impedance                    |                                                             | 200                  |                                       |                      | kΩ   | <u>3.</u> |

| Ringing Current Limit, I <sub>RSC</sub>                           | Ringing, $R_L = 100 \Omega$                                 | 90                   | 135                                   | 180                  | mApk | <u>4.</u> |

| Ringing distortion                                                | Vin = 0.7Vpk, $R_L = 1400\Omega$                            |                      | 0.5                                   | 3.5                  | %    |           |

| Switching Power Supply                                            |                                                             |                      | · · · · · · · · · · · · · · · · · · · |                      |      |           |

| f <sub>CHCLK</sub>                                                |                                                             | 80                   | 85                                    | 90                   | kHz  |           |

| Chopper Clock High Duty Cycle $(t_{\text{CHCLK}})$                |                                                             | 7.5                  | 10                                    | 12.5                 | %    | <u>3.</u> |

Le9502 Data Sheet

| Specification                                           | Condition                                                                                                                                | Min                   | Тур                   | Max             | Unit   | Note      |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------|--------|-----------|

| VT <sub>ILS</sub> (current limit sense threshold)       |                                                                                                                                          | 0.25                  | 0.28                  | 0.31            | V      |           |

| ILS <sub>i</sub>                                        | Input impedance                                                                                                                          |                       | 7000                  |                 | Ω      |           |

| ico <sub>i</sub>                                        | Bias current                                                                                                                             | -1                    |                       | +1              | μA     |           |

|                                                         | Output impedance                                                                                                                         |                       | 50                    |                 | Ω      | 1         |

|                                                         | Slew Rate negative                                                                                                                       | 3                     |                       |                 | V/µsec |           |

|                                                         | Slew Rate positive                                                                                                                       | 25                    |                       |                 | V/μ3ec |           |

| SD <sub>i</sub>                                         | $V_{OH}$ where $V_{SW} \ge 12 \text{ V}$ , $R_{BD} = 330 \Omega$                                                                         | V <sub>SW</sub> - 0.4 | V <sub>SW</sub> - 0.3 | V <sub>SW</sub> | V      | <u>3.</u> |

|                                                         | $V_{OL}$ where $V_{SW} \ge 12 \text{ V}$ , $R_{BD}$ = 330 $\Omega$                                                                       |                       | V <sub>SW</sub> - 8.0 |                 |        |           |

|                                                         | Input impedance                                                                                                                          |                       | 1                     |                 | MΩ     |           |

| CHS <sub>i</sub>                                        | Ringing                                                                                                                                  |                       |                       | 180             |        |           |

| Ci io <sub>i</sub>                                      | Standby and Active                                                                                                                       |                       |                       | 75              |        |           |

|                                                         | Disconnect                                                                                                                               |                       |                       | 1               | μA     |           |

| I <sub>RAMP</sub>                                       | C <sub>RAMP</sub> current                                                                                                                | 72.0                  | 82.2                  | 92.9            |        |           |

| IOET                                                    | Input impedance                                                                                                                          |                       | 10                    |                 | Ω      |           |

| ISET                                                    | Input voltage tolerance                                                                                                                  | 1.33                  | 1.4                   | 1.47            | V      | <u>3.</u> |

| Power Supply Rejection Ratio at                         | the 2-wire Interface                                                                                                                     | 1                     |                       | 1               |        | 1         |

| V                                                       | 200 to 4000 Hz, 50 mVrms                                                                                                                 | 25                    | 45                    |                 |        |           |

| V <sub>CC</sub>                                         | 4k to 50 kHz                                                                                                                             | 20                    | 40                    |                 | dB     | <u>4.</u> |

| V <sub>REG</sub> to V <sub>AB</sub>                     | 200 to 4000 Hz, 100 mVrms                                                                                                                | 25                    | 45                    |                 | dB     |           |

|                                                         | 4k to 50 kHz                                                                                                                             | 20                    | 40                    |                 |        | <u>4.</u> |

|                                                         | 50k to 100k                                                                                                                              | 15                    | 30                    |                 |        | <u>4.</u> |

| Longitudinal Capability                                 |                                                                                                                                          | J. J.                 |                       | JI.             | 1.     | •         |

| Longitudinal balance                                    | R <sub>L</sub> = $600 \Omega$ , $300 \text{ to } 3400 \text{ Hz}$ , 0 dBm, Active and Reverse Polarity                                   | 46                    | 63                    |                 | dB     |           |

| T-L balance                                             | 1 kHz, 0 dBm                                                                                                                             | 40                    | 50                    |                 | dB     |           |

| Longitudinal current per pin                            | A(TIP) or B(RING)                                                                                                                        | 30                    |                       |                 | mA     | <u>4.</u> |

| Longitudinal impedance                                  | A(TIP) or B(RING),<br>0 to 100 Hz                                                                                                        |                       | 1                     | 5               | Ω/pin  | 4.        |

| Longitudinal current detect, I <sub>LONG</sub>          | $\overline{F}_{i}low$                                                                                                                    | 18                    | 26                    | 35              | mA     |           |

| Transmission Performance                                |                                                                                                                                          | • •                   |                       | •               | •      | •         |

| 2WRL                                                    | 300 to 3400 Hz, for 600 $\Omega$                                                                                                         | 26                    |                       |                 |        | <u>4.</u> |

| V <sub>IN</sub> to V <sub>AB</sub> (K <sub>IN</sub> )   | R <sub>L</sub> = open, 0dBm, 2-wire                                                                                                      | 9.34                  | 9.54                  | 9.74            | 1      |           |

| V <sub>OUT</sub> to V <sub>AB</sub> (K <sub>OUT</sub> ) |                                                                                                                                          | 9.34                  | 9.54                  | 9.74            | 4D     | <u>4.</u> |

| Gain Accuracy, 2-Wire to 4-Wire                         | 0dBm, 1 kHz                                                                                                                              | -9.74                 | -9.54                 | -9.34           | dB     |           |

| Gain Accuracy, 4-Wire to 2-Wire                         | 0dBm, 1 kHz                                                                                                                              | 3.32                  | 3.52                  | 3.72            | 1      |           |

| Gain Accuracy, 4-Wire to 4-Wire                         | 0dBm, 1 kHz                                                                                                                              | -6.42                 | -6.02                 | -5.62           | 1      |           |

| K <sub>V</sub> , Voice Current gain                     | Line Test:, Standby,<br>$I_L <  20 \text{ mA} $<br>Active or Rev. Pol.L,<br>$I_L <  80 \text{ mA} $<br>Ringing, $I_L <  100 \text{ mA} $ | <u>1</u><br>520       | <u>1</u><br>500       | 1/480           | A/A    | <u>3.</u> |

| Specification                             | Condition                                       | Min                          | Тур             | Max                          | Unit  | Note                  |

|-------------------------------------------|-------------------------------------------------|------------------------------|-----------------|------------------------------|-------|-----------------------|

| Gain Accuracy over frequency              | Relative to gain at 1 kHz<br>300 to 3400 Hz     | -0.1                         |                 | +0.1                         |       |                       |

| Gain tracking at 1 kHz,                   | -30 dBm to +3 dBm, 2-Wire                       | -0.1                         |                 | +0.1                         |       |                       |

| relative to 0 dBm                         | -55 dBm to -30 dBm, 2-Wire                      | -0.1                         |                 | +0.1                         |       | <u>4.</u>             |

| Gain tracking, On Hook, relative to 0 dBm | 0 to -30 dBm, 2-wire                            | -0.15                        |                 | +0.15                        | dB    | 4.5                   |

| relative to 0 dBm                         | +3 to 0 dBm, 2-wire                             | -0.35                        |                 | +0.35                        |       | <u>4.,5.</u>          |

| THD (Total Harmonic Distortion)           | 0 dBm, 2-wire, 1 kHz                            |                              | -64             | -50                          |       |                       |

| THE (Total Harmonic Distortion)           | +7 dBm, 2-wire, 1 kHz                           |                              | -55             | -40                          |       |                       |

| THD, On hook                              | 0 dBm, 2-wire, 1 kHz                            |                              |                 | -36                          |       | <u>5.</u>             |

| Overload Level, 2-Wire                    | Active or Polarity Reversal                     | 2.5                          |                 |                              | V     | <u>2.</u>             |

| ICN                                       | C-message                                       |                              | 12              | 15                           | dBrnC | <u>4.</u>             |

| ICN                                       | Psophmetric                                     |                              | -78             | <b>-75</b>                   | dBmP  |                       |

| CFILT <sub>i</sub>                        | Output impedance                                |                              | 8000            |                              | Ω     |                       |

| 3. 12.1                                   | Drive capability, Active State                  | -150                         |                 | +150                         | μA    | <u>3.</u> , <u>6.</u> |

|                                           | Input impedance                                 |                              | 5               |                              | Ω     |                       |

| VHP <sub>i</sub>                          | Offset voltage with respect to V <sub>REF</sub> | -20                          |                 | +20                          | mV    | <u>3.,7.</u>          |

|                                           | Offset voltage with respect to V <sub>REF</sub> | -40                          |                 | +40                          | mV    | <u> </u>              |

|                                           | Capacitive load on VOUT to AGND                 |                              |                 | 100                          | pF    | 2                     |

| VOUTi                                     | Resistive load on VOUT to AGND                  | 20                           |                 |                              | kΩ    | <u>3.</u>             |

|                                           | Drive capability, $R_L = 20 \text{ k}\Omega$    | V <sub>REF</sub> – 1<br>20 k |                 | V <sub>REF</sub> + 1<br>20 k | μΑ    | <u>3.,7.</u>          |

|                                           | VOUT Output Range                               | 0.4                          |                 | 2.4                          | \/    |                       |

|                                           | VOUT Common Mode                                |                              | 1.4             |                              | V     |                       |

|                                           | Offset voltage voice                            | -20                          |                 | +20                          | V     | <u>3.</u>             |

| VINP – VINM                               | Differential Input Impedance                    | 200                          |                 |                              | kΩ    | <u> </u>              |

| VIIVI — VIIVIVI                           | Differential Mode Input                         | -1                           |                 | 1                            | V     |                       |

|                                           | VINP, VINM Input Range                          | -0.3                         |                 | 2.4                          |       |                       |

| Motoring gain                             | $R_L = 300 \Omega$ , 12.0 kHz, Active           | 0                            | 0.25            | 0.5                          | dВ    | <u>4.</u>             |

| Metering gain                             | $R_L = 300 \Omega$ , 16.0 kHz, Active           |                              | 0.25            | 0.5                          | dB    |                       |

| Metering distortion,                      | Frequency = 12 kHz, Active                      |                              | 45              | 40                           | -ID   | <u>4.</u>             |

| $R_L = 300 \Omega, V_{AB} = 1.5 Vpk$      | Frequency = 16 kHz, Active                      |                              | <del>-4</del> 5 | -40                          | dB    |                       |

| Crosstalk Between Channels                |                                                 |                              |                 | L                            | I     | 1                     |

| Crosstalk coupling loss                   | F = 200 Hz to 3.4 kHz                           |                              |                 | -75                          | dB    |                       |

| Logic Interface                           |                                                 | <u> </u>                     |                 | <u> </u>                     | I.    |                       |

| Inputs (C1, C2)                           |                                                 |                              |                 |                              |       |                       |

| V <sub>IL</sub>                           |                                                 |                              |                 | 8.0                          | .,    |                       |

| V <sub>IH</sub>                           |                                                 | 2.0                          |                 |                              | V     |                       |

| I <sub>IL</sub>                           | V <sub>IN</sub> = 0.4 V                         | -100                         | 0               | 100                          |       | <u> </u>              |

| I <sub>IH</sub>                           | V <sub>IN</sub> = 2.4 V                         | -100                         | 30              | 100                          | μΑ    |                       |

| CHS <sub>IL</sub>                         | V <sub>IN</sub> = 50 mV                         |                              | 90              |                              |       | <u>4.</u>             |

| CHS <sub>Float_Leakage</sub>              | IIV                                             | -1                           |                 | +1                           | μА    |                       |

| U Ploat_Leakage                           |                                                 | -1                           |                 | 71                           |       | <u>4.</u>             |

Le9502 Data Sheet

| Specification                              | Condition                 | Min | Тур | Max | Unit  | Note |

|--------------------------------------------|---------------------------|-----|-----|-----|-------|------|

| Outputs $(\overline{F}_1, \overline{F}_2)$ |                           |     |     |     |       |      |

| V <sub>OH</sub>                            | I <sub>OUT</sub> = -25 μA | 2.4 | 2.8 |     | V     |      |

| V <sub>OL</sub>                            | I <sub>OUT</sub> = 25 μA  |     | 0.2 | 0.4 | ] ' [ |      |

| DET Pin Characteristics                    |                           |     |     |     |       |      |

| V <sub>OH</sub>                            | I <sub>OUT</sub> = -165μA | 2.4 | 2.8 |     | V     |      |

| V <sub>OL</sub>                            | I <sub>OUT</sub> = 165 μA |     | 0.2 | 0.4 | v     |      |

### Note:

- 1.  $V_{AB}$  = Voltage between the  $A_i$  (TIP) and  $B_i$  (RING) pins.

- 2. Overload level is defined when THD = 1%.

- 3. Guaranteed by design.

- 4. Not tested in production. Parameter is guaranteed by characterization or correlation to other tests.

- 5. When On hook,  $R_{LDC}$  is open circuit,  $R_{LAC}$  = 600  $\Omega$ .

- 6. Layout should have less than 10 pF from pin to ground.

- 7.  $V_{REF}$  is an internal value of typically  $V_{REF} = 1.4V$ .

### **TEST CIRCUIT**

Per Channel

Note:

\* Denotes pins that are common to both channels.

i = per channel component/pin

6

Zarlink Semiconductor Inc.

Le9502

### APPLICATION CIRCUIT

Note:

\* Denotes pins that are common to both channels.

\*\*  $V_{CM}$  is the bias voltage, which is  $\geq$  (maximum ADC input voltage / 2)

\*\*\* Total fuse resistance =  $100\Omega$  guarantees a minimum DC load.

0

Zarlink Semiconductor Inc.

### **LINE CARD PARTS LIST**

The following list defines the parts and part values required to meet target specification limits for channel i of the line card (i = 1, 2). The protection circuit is included.

| Item                                     | Quantity<br>(see note 1) | Туре                | Value                  | Tol.  | Rating | Comments                            | Note |

|------------------------------------------|--------------------------|---------------------|------------------------|-------|--------|-------------------------------------|------|

| C <sub>1</sub>                           | 1                        | Capacitor           | 100 nF                 | 10%   | 16 V   | Panasonic / ECJ-1VB1C104K, 0603     |      |

| C <sub>BDi</sub>                         | 2                        | Capacitor           | 27 nF                  | 10%   | 16 V   | Panasonic / ECJ-1VB1C273K, 0603     |      |

| C <sub>ESRi,</sub><br>C <sub>VREGi</sub> | 4                        | Capacitor           | 0.1uF                  | 10%   | 200 V  | CalChip / GMB31X7R104K200NT, 1206   |      |

| C <sub>FOUTi</sub>                       | 2                        | Capacitor           | 1 μF                   | 10%   | 50 V   | Panasonic / ECJ-1VC1H100D, 0603     |      |

| C <sub>HSi</sub>                         | 2                        | Capacitor           | 1 nF                   | 10%   | 50 V   | Panasonic / ECJ-1VC1H102J, 0603     |      |

| C <sub>HPi</sub>                         | 2                        | Capacitor           | 1.5 µF                 | 10%   | 6.3 V  | Panasonic / ECJ-2YB0J155K, 0805     |      |

| C <sub>LPFi</sub>                        | 2                        | Capacitor           | 4.7 μF<br>Tantalum     | 10%   | 6.3 V  | Panasonic / ECS-T0JY475R, 1206      |      |

| C <sub>RAMP</sub>                        | 1                        | Capacitor           | 470 pF                 | 5%    | 50 V   | Panasonic / ECJ-1VC1H471J, 0603     |      |

| C <sub>TRIPi</sub>                       | 2                        | Capacitor           | 47 nF                  | 10%   | 50 V   | Panasonic / ECJ-1VB1C473K, 0603     |      |

| C <sub>SW</sub>                          | 1                        | Capacitor           | 220 µF<br>Alum. Elect. | 20%   | 25 V   | Panasonic / ECE-V1EA221UP, 8mmCan   |      |

| C <sub>SW1</sub>                         | 1                        | Capacitor           | 100 nF                 | 10%   | 50 V   | Panasonic / ECJ-2YB1H104K, 0805     |      |

| C <sub>FLi,</sub>                        | 2                        | Capacitor           | 2.2 µF                 | 20%   | 200 V  | United Chemi / THCR70E2D225MT, 3025 |      |

| C <sub>VREGii</sub>                      | 2                        | Capacitor           | 1.0 µF                 | 10%   | 300 V  | Tecate / CMC-300/105KX1825T060      |      |

| D <sub>SWi</sub>                         | 2                        | Diode               | ES2C                   |       | 2 A    | General Semi. / ES2C, DO-214AA      |      |

| DD1                                      | 1                        | Diode               | 4148CC                 |       | 200 mA | Fairchild / MMBD4148CC, SOT-23      |      |

| DD2i                                     | 2                        | Diode               | BAV99                  |       | 200 mA | Fairchild / BAV99, SOT-23           |      |