# SHARP

|                  | Date Dec. 11. 2001                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

| PRELIMINARY DAT  | ACUEET                                                                                                           |

| I NCCIMINANT DAI |                                                                                                                  |

|                  | DATASHEET                                                                                                        |

| <b>PRODUCT</b> : | 16M (x16) Flash + 4M (x16) SRAM                                                                                  |

| MODEL NO :       | LRS1331C                                                                                                         |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  |                                                                                                                  |

|                  | oject to change without notice.<br>rights reserved. No reproduction or republication without written permission. |

|                  | ales office to obtain the latest datasheet.                                                                      |

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- •Office electronics

- •Instrumentation and measuring equipment

- •Machine tools

- •Audiovisual equipment

- •Home appliance

- •Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment <u>which demands high reliability</u>, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- •Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- •Mainframe computers

- •Traffic control systems

- •Gas leak detectors and automatic cutoff devices

- •Rescue and security equipment

- •Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely <u>high performance</u> in terms of functionality, reliability, or accuracy.

- Aerospace equipment

- •Communications equipment for trunk lines

- •Control equipment for the nuclear power industry

- •Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

| 1. Description                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2. Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                            | 3                |

| 3. Truth Table                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                |

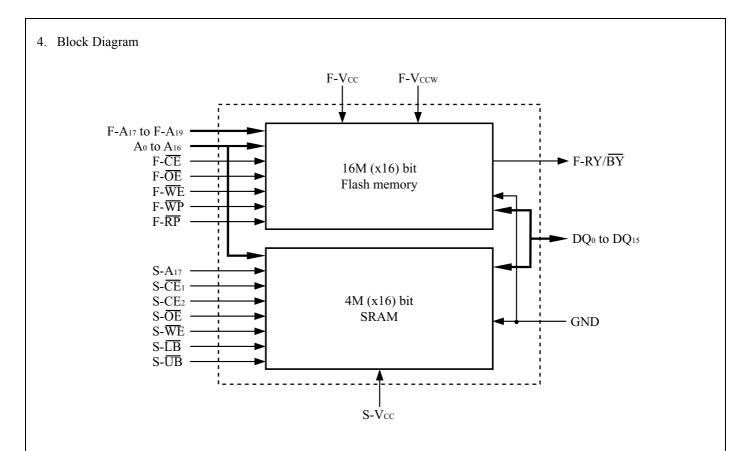

| 4. Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                | 6                |

| 5. Command Definitions for Flash Memory     7       5.1 Command Definitions     7       5.2. Identifier Codes     8       5.3. Write Protection Alternatives     8                                                                                                                                                                                                                                                              | 7<br>8           |

| 6. Status Register Definition                                                                                                                                                                                                                                                                                                                                                                                                   | 9                |

| 7. Memory Map for Flash Memory 10                                                                                                                                                                                                                                                                                                                                                                                               | 0                |

| 8. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                     | 1                |

| 9. Recommended DC Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                          | 1                |

| 10. Pin Capacitance                                                                                                                                                                                                                                                                                                                                                                                                             | 1                |

| 11. DC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                               | 2                |

| 12. AC Electrical Characteristics for Flash Memory     14       12.1 AC Test Conditions     14       12.2 Read Cycle     14       12.3 Write Cycle (F-WE Controlled)     14       12.4 Write Cycle (F-WE Controlled)     15       12.5 Block Erase, Full Chip Erase, Word Write and Lock-Bits Configuration Performance     17       12.6 Flash Memory AC Characteristics Timing Chart     16       12.7 Reset Operations     2 | 4<br>5<br>6<br>7 |

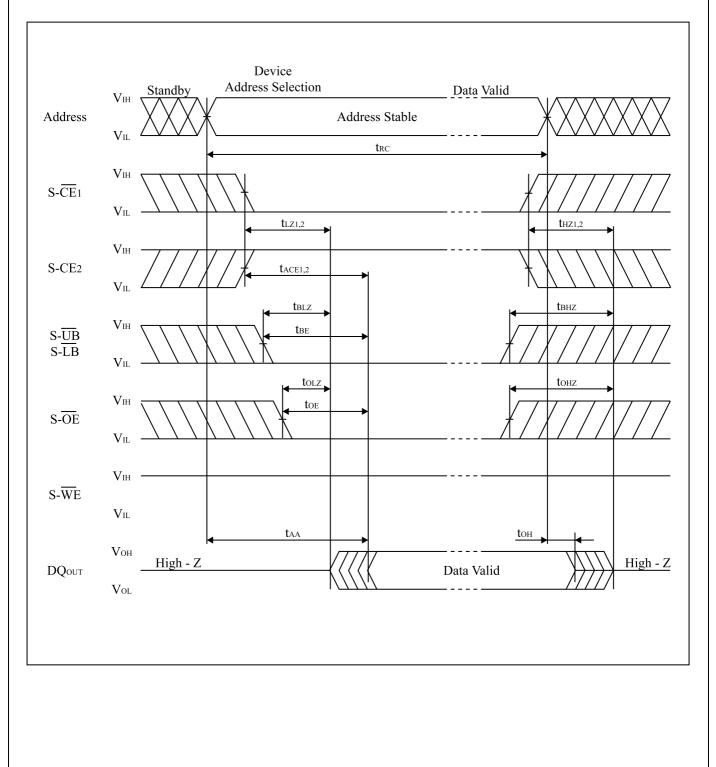

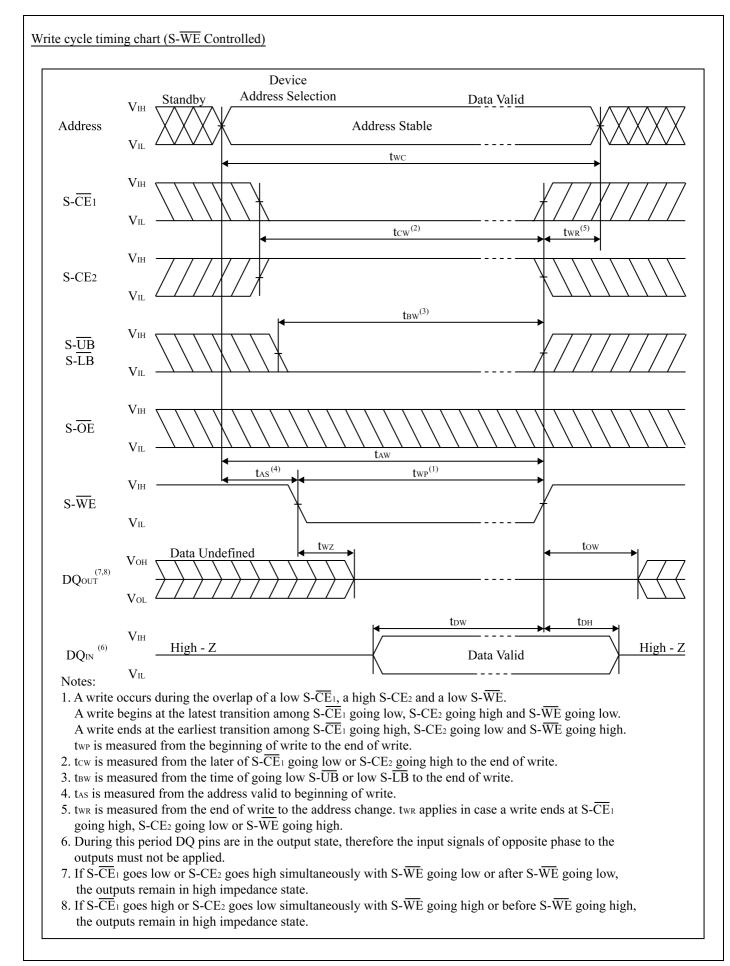

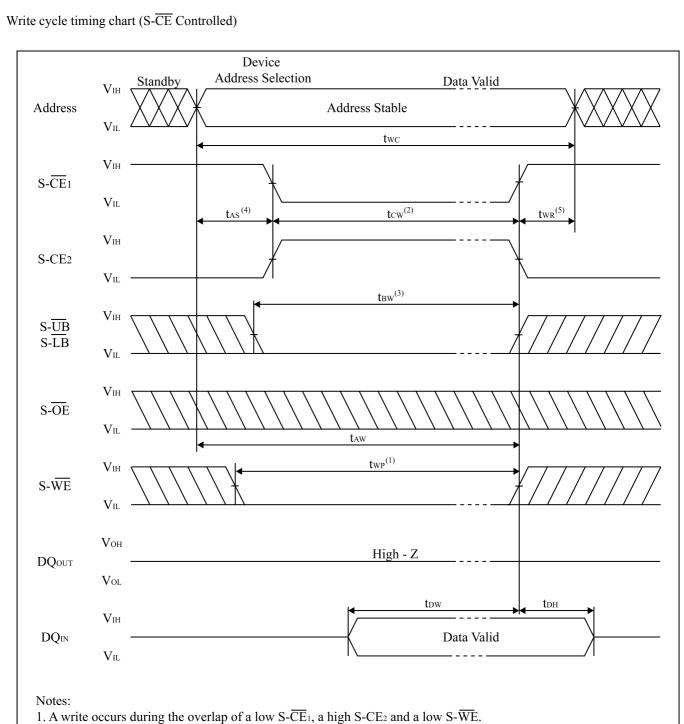

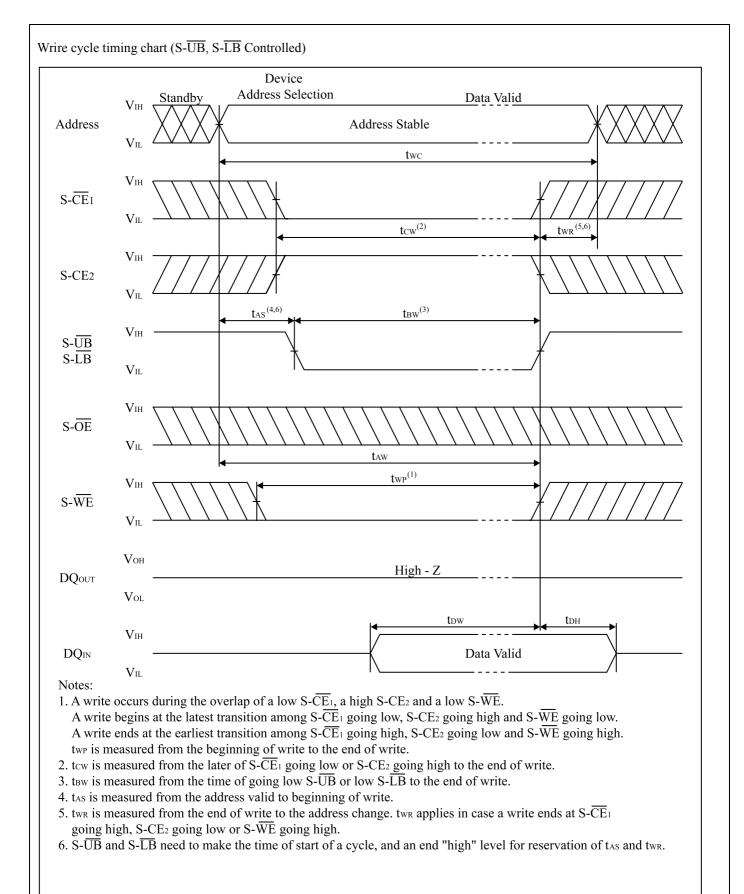

| 13. AC Electrical Characteristics for SRAM2213.1 AC Test Conditions2213.2 Read Cycle2213.3 Write Cycle2213.4 SRAM AC Characteristics Timing Chart22                                                                                                                                                                                                                                                                             | 22<br>22<br>23   |

| 14. Data Retention Characteristics for SRAM                                                                                                                                                                                                                                                                                                                                                                                     | 28               |

| 15. Notes                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                |

| 16. Flash Memory Data Protection                                                                                                                                                                                                                                                                                                                                                                                                | 0                |

| 17. Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                       | 51               |

| 18. Related Document Information 3.                                                                                                                                                                                                                                                                                                                                                                                             | 51               |

| 19. Package and Packing Specification  3.                                                                                                                                                                                                                                                                                                                                                                                       | 2                |

## 1. Description

The LRS1331C is a combination memory organized as  $1,048,576 \times 16$  bit flash memory and  $262,144 \times 16$  bit static RAM in one package.

| Features                                                              |                       |                |                                                                 |

|-----------------------------------------------------------------------|-----------------------|----------------|-----------------------------------------------------------------|

| - Power supply                                                        | • • • •               | 2.7V to 3.3    | V                                                               |

| - Operating temperature                                               | • • • •               | -25°C to +8    | 35°C                                                            |

| - Not designed or rated as radiation hardened                         |                       |                |                                                                 |

| - 72 pin CSP (LCSP072-P-0811) plastic package                         |                       |                |                                                                 |

| - Flash memory has P-type bulk silicon, and SRAM has P-               | type bulk sil         | icon           |                                                                 |

|                                                                       | • •                   |                |                                                                 |

| Flash Memory                                                          |                       |                |                                                                 |

| - Access Time                                                         | • • • •               | 90 ns          | (Max.)                                                          |

| - Power Supply current (The current for $F-V_{CC}$ pin and $F-V_{CC}$ | V <sub>CCW</sub> pin) |                |                                                                 |

| Read                                                                  | • • • •               | 25 mA          | (Max. t <sub>CYCLE</sub> = 200ns, CMOS Input)                   |

| Word write                                                            | • • • •               | 57 mA          | (Max.)                                                          |

| Block erase                                                           | • • • •               | 42 mA          | (Max.)                                                          |

| Reset Power-Down                                                      | • • • •               | 20 µA          | (Max. F- $\overline{RP}$ = GND ± 0.2V,                          |

|                                                                       |                       |                | $I_{OUT} (F-RY/\overline{BY}) = 0mA)$                           |

| Standby                                                               | • • • •               | 30 µA          | (Max. $F-\overline{CE} = F-\overline{RP} = F-V_{CC} \pm 0.2V$ ) |

| - Optimized Array Blocking Architecture                               |                       |                |                                                                 |

| Two 4k-word Boot Blocks                                               |                       |                |                                                                 |

| Six 4k-word Parameter Blocks                                          |                       |                |                                                                 |

| Thirty-one 32k-word Main Blocks                                       |                       |                |                                                                 |

| Bottom Boot Location                                                  |                       |                |                                                                 |

| - Extended Cycling Capability<br>100,000 Block Erase Cycles           | (F V -                | - 2 7 to 2 2 V |                                                                 |

|                                                                       | $(\Gamma - V_{CCW} -$ | = 2.7 to 3.3V) | )                                                               |

| - Enhanced Automated Suspend Options                                  |                       |                |                                                                 |

| Word Write Suspend to Read<br>Block Erase Suspend to Word Write       |                       |                |                                                                 |

| Block Erase Suspend to Read                                           |                       |                |                                                                 |

| block Elase Suspend to Read                                           |                       |                |                                                                 |

| SRAM                                                                  |                       |                |                                                                 |

| - Access Time                                                         | • • • •               | 85 ns          | (Max.)                                                          |

| - Power Supply current                                                |                       |                |                                                                 |

| Operating current                                                     |                       | 45 mA          | (Max. $t_{RC}$ , $t_{WC}$ = Min.)                               |

|                                                                       | • • • •               | 8 mA           | (Max. $t_{RC}, t_{WC} = 1 \mu s$ , CMOS Input)                  |

| Standby current                                                       | • • • •               | 15 µA          | (Max.)                                                          |

| Data retention current                                                |                       | 15 μA          | (Max. $S-V_{CC} = 3.0V$ )                                       |

|                                                                       |                       | ·              |                                                                 |

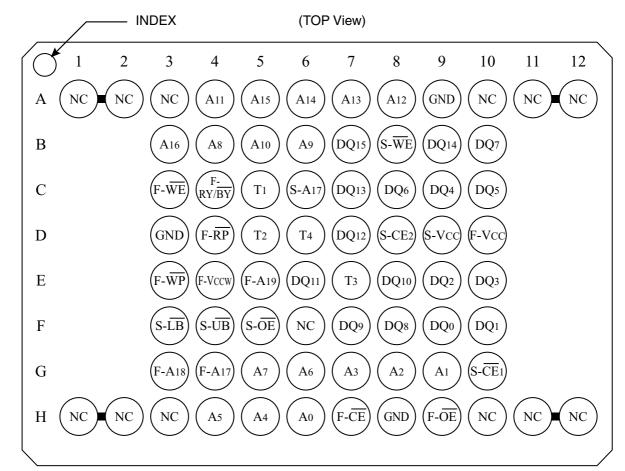

2. Pin Configuration

Note) From T1 to T4 pins are needed to be open. Two NC pins at the corner are connected. Do not float any GND pins.

| Pin                                                                                                                     | Description                                                                                                                                                        | Туре                 |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $A_0$ to $A_{16}$                                                                                                       | Address Inputs (Common)                                                                                                                                            | Input                |

| $F-A_{17}$ to $F-A_{19}$                                                                                                | Address Inputs (Flash)                                                                                                                                             | Input                |

| S-A <sub>17</sub>                                                                                                       | Address Inputs (SRAM)                                                                                                                                              | Input                |

| F-CE                                                                                                                    | Chip Enable Inputs (Flash)                                                                                                                                         | Input                |

| $S-\overline{CE}_1$ , $S-CE_2$                                                                                          | Chip Enable Inputs (SRAM)                                                                                                                                          | Input                |

| F-WE                                                                                                                    | Write Enable Input (Flash)                                                                                                                                         | Input                |

| S-WE                                                                                                                    | Write Enable Input (SRAM)                                                                                                                                          | Input                |

| F-OE                                                                                                                    | Output Enable Input (Flash)                                                                                                                                        | Input                |

| $S-\overline{OE}$                                                                                                       | Output Enable Input (SRAM)                                                                                                                                         | Input                |

| $S-\overline{LB}$                                                                                                       | SRAM Byte Enable Input ( $DQ_0$ to $DQ_7$ )                                                                                                                        | Input                |

| $S-\overline{UB}$                                                                                                       | SRAM Byte Enable Input ( $DQ_8$ to $DQ_{15}$ )                                                                                                                     | Input                |

| $F-\overline{RP} Reset Power Down Input (Flash) Block erase and Write : V_{IH} Read : V_{IH} Reset Power Down : V_{IL}$ |                                                                                                                                                                    | Input                |

| F-WP                                                                                                                    | Write Protect Input (Flash)<br>Two Boot Blocks Locked : V <sub>IL</sub>                                                                                            | Input                |

| F-RY/BY                                                                                                                 | Ready/Busy Output (Flash)<br>During an Erase or Write operation : V <sub>OL</sub><br>Block Erase and Write Suspend : High-Z (High impedance)                       | Open Drain<br>Output |

| DQ <sub>0</sub> to DQ <sub>15</sub>                                                                                     | Data Inputs and Outputs (Common)                                                                                                                                   | Input / Output       |

| F-V <sub>CC</sub>                                                                                                       | Power Supply (Flash)                                                                                                                                               | Power                |

| S-V <sub>CC</sub>                                                                                                       | Power Supply (SRAM)                                                                                                                                                | Power                |

| F-V <sub>CCW</sub>                                                                                                      | Write, Erase Power Supply (Flash)<br>Block Erase and Write : F-V <sub>CCW</sub> = V <sub>CCWH</sub><br>All Blocks Locked : F-V <sub>CCW</sub> < V <sub>CCWLK</sub> | Power                |

| GND                                                                                                                     | GND (Common)                                                                                                                                                       | Power                |

| NC                                                                                                                      | Non Connection                                                                                                                                                     | -                    |

| $T_1$ to $T_4$                                                                                                          | Test pins (Should be all open)                                                                                                                                     | _                    |

| 3. Truth Tabl       |                   | r       |      |      |      |      |          |          |         |      |      |      | 1                   |    |

|---------------------|-------------------|---------|------|------|------|------|----------|----------|---------|------|------|------|---------------------|----|

| Flash               | SRAM              | Notes   | F-CE | F-RP | F-OE | F-WE | $S-CE_1$ | $S-CE_2$ | S-OE    | S-WE | S-LB | S-UB | $DQ_0$ to $DQ_{15}$ |    |

| Read                |                   | 3,5     |      |      | L    |      |          |          |         |      |      |      | D <sub>OUT</sub>    |    |

| Output<br>Disable   | Standby           | 5       | L    | Н    | Н    | Н    | ((       | 5)       | Х       | Х    | (0   | 5)   | High-Z              |    |

| Write               |                   | 2,3,4,5 |      |      |      | L    |          |          |         |      |      |      | D <sub>IN</sub>     |    |

|                     | Read              | 5       |      |      |      | x x  |          |          |         | L    | Н    |      | (7)                 |    |

| Standby             | Output<br>Disable | 5       | Н    | Н    | v    |      | L        | Н        | Н       | Н    | Х    | Х    | High-Z              |    |

|                     |                   | 5       | 11   | 11   | Λ    | л    | L        | 11       | Х       | Х    | Н    | Н    | Ingii-Z             |    |

|                     | Write             | 5       |      |      |      |      |          |          | Х       | L    | (7)  |      | 7)                  |    |

|                     | Read              | 5       |      |      |      |      | L        |          |         | L    | Н    |      | (                   | 7) |

| Reset Power         | Output            | 5       | Х    | L    | Х    | Х    |          | н        | H H X X | Н    | Х    | Х    | High-Z              |    |

| Down                | Disable           | 5       | Л    |      |      |      | L        | 11       |         | Х    | Н    | Н    | Ingii-Z             |    |

|                     | Write             | 5       |      |      |      |      |          |          |         | L    |      | (    | 7)                  |    |

| Standby             |                   | 5       | Н    | Н    |      |      |          |          |         |      |      |      |                     |    |

| Reset Power<br>Down | er Standby        | 5       | Х    | L    | Х    | Х    | (6)      |          | Х       | Х    | (6   | 5)   | High-Z              |    |

Notes:

L = V<sub>IL</sub>, H = V<sub>IH</sub>, X = H or L, High-Z = High impedance. Refer to DC Characteristics.

Command Writes involving block erase, full chip erase, word write, or lock-bit configuration are reliably executed when F-V<sub>CCW</sub> = V<sub>CCWH</sub> and F-V<sub>CC</sub> = 2.7V to 3.3V. Block erase, full chip erase, word write, or lock-bit configuration with F-V<sub>CCW</sub> < V<sub>CCWH</sub> (Min.) produce spurious results and should not be attempted.

- 3. Never hold  $F-\overline{OE}$  low and  $F-\overline{WE}$  low at the same timing.

- 4. Refer Section 5. Command Definitions for Flash Memory valid D<sub>IN</sub> during a write operation.

- 5.  $F-\overline{WP}$  set to  $V_{IL or} V_{IH}$ .

| 0. 51               | KAM Sta           | ndby Mic | bde  |

|---------------------|-------------------|----------|------|

| $S-\overline{CE}_1$ | S-CE <sub>2</sub> | S-LB     | S-UB |

| Н                   | Х                 | Х        | Х    |

| Х                   | L                 | Х        | Х    |

| Х                   | Х                 | Н        | Н    |

7. S-UB, S-LB Control Mode

| S-LB | S-UB | $DQ_0$ to $DQ_7$                                     | DQ <sub>8</sub> to DQ <sub>15</sub> |

|------|------|------------------------------------------------------|-------------------------------------|

| L    | L    | $D_{OUT}/D_{IN}$                                     | D <sub>OUT</sub> /D <sub>IN</sub>   |

| L    | Н    | $\mathrm{D}_{\mathrm{OUT}}/\mathrm{D}_{\mathrm{IN}}$ | High-Z                              |

| Н    | L    | High-Z                                               | D <sub>OUT</sub> /D <sub>IN</sub>   |

5

5. Command Definitions for Flash Memory<sup>(1)</sup>

#### 5.1 Command Definitions

|                                       | Bus Cycles | NT ( | F                   | irst Bus Cycl          | e             | Second Bus Cycle    |                        |                     |  |

|---------------------------------------|------------|------|---------------------|------------------------|---------------|---------------------|------------------------|---------------------|--|

| Command                               | Required   | Note | Oper <sup>(2)</sup> | Address <sup>(3)</sup> | Data          | Oper <sup>(2)</sup> | Address <sup>(3)</sup> | Data <sup>(3)</sup> |  |

| Read Array / Reset                    | 1          |      | Write               | XA                     | FFH           |                     |                        |                     |  |

| Read Identifier Codes                 | ≥ 2        | 4    | Write               | XA                     | 90H           | Read                | IA                     | ID                  |  |

| Read Status Register                  | 2          |      | Write               | XA                     | 70H           | Read                | XA                     | SRD                 |  |

| Clear Status Register                 | 1          |      | Write               | XA                     | 50H           |                     |                        |                     |  |

| Block Erase                           | 2          | 5    | Write               | XA                     | 20H           | Write               | BA                     | D0H                 |  |

| Full Chip Erase                       | 2          | 5    | Write               | XA                     | 30H           | Write               | XA                     | D0H                 |  |

| Word Write                            | 2          | 5    | Write               | XA                     | 40H or<br>10H | Write               | WA                     | WD                  |  |

| Block Erase and Word Write<br>Suspend | 1          | 5,9  | Write               | XA                     | B0H           |                     |                        |                     |  |

| Block Erase and Word Write<br>Resume  | 1          | 5,9  | Write               | XA                     | D0H           |                     |                        |                     |  |

| Set Block Lock Bit                    | 2          | 7    | Write               | XA                     | 60H           | Write               | BA                     | 01H                 |  |

| Clear Block Lock Bits                 | 2          | 6,7  | Write               | XA                     | 60H           | Write               | XA                     | D0H                 |  |

| Set Permanent Lock Bit                | 2          | 8    | Write               | XA                     | 60H           | Write               | XA                     | F1H                 |  |

Notes:

1. Commands other than those shown above are reserved by SHARP for future device implementations and should not be used.

2. Bus operations are defined in 3. Truth Table.

- 3. XA = Any valid address within the device.

- IA = Identifier code address.

BA = Address within the block being erased, set block lock bit.

WA = Address of memory location to be written.

SRD = Data read from status register (See 6. Status Register Definition).

WD = Data to be written at location WA. Data is latched on the rising edge of  $F-\overline{WE}$  or  $F-\overline{CE}$  (whichever goes high first). ID = Data read from identifier codes (See 5.2 Identifier Codes).

- 4. See Identifier Codes at next page.

- 5. See Write Protection Alternatives in section 5.3.

- 6. The clear block lock-bits operation simultaneously clears all block lock-bits.

- 7. If the permanent lock-bit is set, Set Block Lock-Bit and Clear Block Lock-Bits commands can not be done.

- 8. Once the permanent lock-bit is set, it cannot be cleared.

- 9. If the time between writing the Block Erase Resume command and writing the Block Erase Suspend command is shorter than t<sub>ERES</sub> and both commands are written repeatedly, a longer time is required than standard block erase until the completion of the operation.

| 5.2 Identifier Codes <sup>(3)</sup>         |                                             |                                              |

|---------------------------------------------|---------------------------------------------|----------------------------------------------|

| Codes                                       | Address [A <sub>19</sub> - A <sub>0</sub> ] | Data [DQ <sub>15</sub> - DQ <sub>0</sub> ]   |

| Manufacture Code                            | 00000H                                      | 00B0H                                        |

| Device Code                                 | 00001H                                      | 00E9H                                        |

| Block Lock Configuration <sup>(2)</sup>     | $BA^{(1)} + 2$                              | $DQ_0 = 0$ : Unlocked<br>$DQ_0 = 1$ : Locked |

| Permanent Lock Configuration <sup>(2)</sup> | 00003H                                      | $DQ_0 = 0$ : Unlocked<br>$DQ_0 = 1$ : Locked |

Notes:

- 1. BA selects the specific block lock configuration code to be read.

- 2.  $DQ_{15} DQ_1$  are reserved for future use.

- 3. Read Identifier Codes command is defined in 5.1 Command Definitions.

- 5.3 Write Protection Alternatives

| Operation                    | F-V <sub>CCW</sub>                 | F-RP            | F-WP            | Permanent<br>Lock-Bit | Block<br>Lock-Bit | Effect                                                                             |

|------------------------------|------------------------------------|-----------------|-----------------|-----------------------|-------------------|------------------------------------------------------------------------------------|

|                              | ≤V <sub>CCWLK</sub>                | Х               | Х               | Х                     | Х                 | All Blocks Locked.                                                                 |

|                              |                                    | V <sub>IL</sub> | Х               | Х                     | Х                 | All Blocks Locked.                                                                 |

| Block Erase or<br>Word Write |                                    |                 | V <sub>IL</sub> |                       | 0                 | 2 Boot Blocks Locked.                                                              |

|                              | >V <sub>CCWLK</sub> <sup>(1)</sup> | $V_{IH}$        | V <sub>IH</sub> | Х                     | 0                 | Block Erase and Word Write Enabled.                                                |

|                              |                                    | ▼ IH            | V <sub>IL</sub> | Λ                     | 1                 | Block Erase and Word Write Disabled.                                               |

|                              |                                    |                 | V <sub>IH</sub> |                       | 1                 | Block Erase and Word Write Disabled.                                               |

|                              | ≤V <sub>CCWLK</sub>                | Х               | Х               | Х                     | Х                 | All Blocks Locked.                                                                 |

|                              |                                    | V <sub>IL</sub> | Х               | Х                     | Х                 | All Blocks Locked.                                                                 |

| Full Chip Erase              | >V <sub>CCWLK</sub> <sup>(1)</sup> | V <sub>IH</sub> | V <sub>IL</sub> | Х                     | Х                 | All Unlocked Blocks are Erased.<br>2 Boot Blocks and Locked Blocks are Not Erased. |

|                              |                                    |                 | V <sub>IH</sub> | Λ                     |                   | All Unlocked Blocks are Erased.<br>Locked Blocks are Not Erased.                   |

|                              | ≤V <sub>CCWLK</sub>                | Х               | Х               | Х                     | Х                 | Set Block Lock-Bit Disabled.                                                       |

| Set Block                    | >V <sub>CCWLK</sub> <sup>(1)</sup> | V <sub>IL</sub> | Х               | Х                     | Х                 | Set Block Lock-Bit Disabled.                                                       |

| Lock-Bit                     |                                    | V               | Х               | 0                     | Х                 | Set Block Lock-Bit Enabled.                                                        |

|                              |                                    | V <sub>IH</sub> | Х               | 1                     | Х                 | Set Block Lock-Bit Disabled.                                                       |

|                              | ≤V <sub>CCWLK</sub>                | Х               | Х               | Х                     | Х                 | Clear Block Lock-Bits Disabled.                                                    |

| Clear Block                  |                                    | V <sub>IL</sub> | Х               | Х                     | Х                 | Clear Block Lock-Bits Disabled.                                                    |

| Lock-Bits                    | >V <sub>CCWLK</sub> <sup>(1)</sup> | V               | Х               | 0                     | Х                 | Clear Block Lock-Bits Enabled.                                                     |

|                              |                                    | $V_{IH}$        | Х               | 1                     | Х                 | Clear Block Lock-Bits Disabled.                                                    |

|                              | ≤V <sub>CCWLK</sub>                | Х               | Х               | Х                     | Х                 | Set Permanent Lock-Bit Disabled.                                                   |

| Set Permanent<br>Lock-Bit    | <b>&gt;V</b> (1)                   | $V_{IL}$        | Х               | Х                     | Х                 | Set Permanent Lock-Bit Disabled.                                                   |

|                              | $>V_{CCWLK}^{(1)}$                 | V <sub>IH</sub> | Х               | Х                     | Х                 | Set Permanent Lock- Bit Enabled.                                                   |

Note:

1. F-V $_{\rm CCW}$  is guaranteed only with the nominal voltages.

| WSI    | MS                          | BESS                                 | ECBLBS                                                     | WWSLBS         | VCCWS                                                               | WWSS                                                                      | DPS                                                                                     | R                                                                         |

|--------|-----------------------------|--------------------------------------|------------------------------------------------------------|----------------|---------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 7      |                             | 6                                    | 5                                                          | 4              | 3                                                                   | 2                                                                         | 1                                                                                       | 0                                                                         |

| 1=     | WRITE<br>Ready<br>Busy      | E STATE MAC                          | CHINE STATUS                                               | (WSMS)         | Notes:<br>Check SR.7 or<br>Erase, Word Wr                           |                                                                           |                                                                                         |                                                                           |

| 1=     | Block H                     | Erase Suspend                        | SPEND STATUS<br>ed<br>ess/Completed                        | S (BESS)       | SR.6 - SR.1 are                                                     |                                                                           | e                                                                                       | I                                                                         |

|        | STATU                       | S (ECBLBS)<br>Block Erase,           | R BLOCK LOCI<br>Full Chip Erase                            |                | If both SR.5 an<br>Erase or Lock-<br>mand sequence                  | Bit configuration                                                         |                                                                                         |                                                                           |

| SR.4=  | Block I<br>WORD<br>STATU    | Lock-Bits<br>WRITE ANI<br>S (WWSLBS) | rase, Full Chip<br>O SET LOCK-BI<br>)<br>or Set Block/Perr | Т              | SR.3 does not<br>level. The WSM<br>indicates the F-<br>Erase, Word  | 4 (Write State M<br>V <sub>CCW</sub> level on<br>Write, or Lock           | lachine) interrog<br>ly after Block E<br>-Bit Configura                                 | gates and<br>Crase, Full Ch<br>tion comman                                |

| 0=     | Lock-B<br>Success<br>Lock-B | ful Word Wri                         | te or Set Block/P                                          | ermanent       | sequences. SR.3<br>only when F-V <sub>0</sub>                       | -                                                                         | ed to reports ac                                                                        | curate feedba                                                             |

| 1=     |                             | •                                    | CCWS)<br>Operation Abor                                    | t              | SR.1 does not<br>and block lock<br>the permanent                    | -bit and $F-\overline{WP}$                                                | values. The WS                                                                          | SM interrogat                                                             |

| 1=     | Word V                      | Vrite Suspende                       | END STATUS (<br>ed<br>ss/Completed                         | WWSS)          | Block Erase, Fr<br>figuration comming on the atte<br>permanent lock | ull Chip Erase,<br>nand sequences,<br>mpted operatio<br>t-bit is set and/ | Word Write, or<br>It informs the s<br>n, if the block<br>for $F-\overline{WP}$ is $V_I$ | Lock-Bit Co<br>system, dependent<br>lock-bit is set<br>$_L$ . Reading the |

| 1=     | Block                       | Lock-Bit, Per etected, Opera         | STATUS (DPS)<br>manent Lock-Bation Abort                   | it and/or F-WP | block lock and<br>ing the Read Id<br>and block lock-                | lentifier Codes                                                           |                                                                                         |                                                                           |

| SP 0 = | DECED                       | VED FOR FU                           |                                                            |                | SR.0 is reserved                                                    | d for future use a                                                        | and should be m                                                                         | asked out whe                                                             |

### 7. Memory Map for Flash Memory

|                         | Bottom Boot                                      |

|-------------------------|--------------------------------------------------|

| $[A19 \sim A0]$         |                                                  |

| FFFFF<br>F8000          | 32K-word Main Block 30                           |

| F7FFF<br>F0000          | 32K-word Main Block 29                           |

| EFFFF<br>E8000          | 32K-word Main Block 28                           |

| E7555<br>E0000          | 32K-word Main Block 27                           |

| DFFFF<br>D8000          | 32K-word Main Block 26                           |

| D3000<br>D7FFF<br>D0000 | 32K-word Main Block 25                           |

| CFFFF                   | 32K-word Main Block 24                           |

| C8000<br>C7FFF          | 32K-word Main Block 23                           |

| C0000<br>BFFFF          | 32K-word Main Block 22                           |

| B8000<br>B7FFF          | 32K-word Main Block 21                           |

| B0000<br>AFFFF          | 32K-word Main Block 20                           |

| A8000<br>A7FFF          | 32K-word Main Block 19                           |

| A0000<br>9FFFF          | 32K-word Main Block 18                           |

| 98000<br>97FFF          | 32K-word Main Block 17                           |

| 90000<br>8FFFF          | 32K word Main Block 17<br>32K-word Main Block 16 |

| 88000<br>87FFF          | 32K word Main Block 16<br>32K-word Main Block 15 |

| 80000<br>7FFFF          | 32K-word Main Block 14                           |

| 78000<br>77FFF          | 32K-word Main Block 13                           |

| 70000<br>6FFFF          |                                                  |

| 68000<br>67FFF          | 32K-word Main Block 12                           |

| 60000<br>5FFFF          | 32K-word Main Block 11                           |

| 58000<br>57FFF          | 32K-word Main Block 10                           |

| 50000<br>4FFFF          | 32K-word Main Block 9                            |

| 48000<br>47FFF          | 32K-word Main Block 8                            |

| 40000<br>3FFFF          | 32K-word Main Block 7                            |

| 38000<br>37FFF          | 32K-word Main Block 6                            |

| 30000<br>2FFFF          | 32K-word Main Block 5                            |

| 28000                   | 32K-word Main Block 4                            |

| 27FFF<br>20000          | 32K-word Main Block 3                            |

| 1FFFF<br>18000          | 32K-word Main Block 2                            |

| 17FFF<br>10000          | 32K-word Main Block 1                            |

| 0FFFF<br>08000          | 32K-word Main Block 0                            |

| 07FFF<br>07000          | 4K-word Parameter Block 5                        |

| 06FFF<br>06000          | 4K-word Parameter Block 4                        |

| 05FFF<br>05000          | 4K-word Parameter Block 3                        |

| 04FFF<br>04000          | 4K-word Parameter Block 2                        |

| 03FFF<br>03000          | 4K-word Parameter Block 1                        |

| 02FFF<br>02000          | 4K-word Parameter Block 0                        |

| 01FFF<br>01000          | 4K-word Boot Block 1                             |

| 00FFF<br>00000          | 4K-word Boot Block 0                             |

#### 8. Absolute Maximum Ratings

| Symbol             | Parameter                  | Notes   | Ratings                | Unit |

|--------------------|----------------------------|---------|------------------------|------|

| V <sub>CC</sub>    | Supply voltage             | 1,2     | -0.2 to +4.0           | V    |

| V <sub>IN</sub>    | Input voltage              | 1,2,3,4 | -0.2 to $V_{CC}$ + 0.3 | V    |

| T <sub>A</sub>     | Operating temperature      |         | -25 to +85             | °C   |

| T <sub>STG</sub>   | Storage temperature        |         | -55 to +125            | °C   |

| F-V <sub>CCW</sub> | F-V <sub>CCW</sub> voltage | 1,3     | -0.3 to +4.0           | V    |

Notes:

1. The maximum applicable voltage on any pins with respect to GND.

2. Except F-V<sub>CCW</sub>.

3. -1.0V undershoot and  $V_{CC}$  + 1.0V overshoot are allowed when the pulse width is less than 20 nsec. 4.  $V_{IN}$  should not be over + 4.0V.

#### 9. Recommended DC Operating Conditions

$(T_A = -25^{\circ}C \text{ to } +85^{\circ}C)$ Symbol Parameter Notes Max. Min. Тур. Unit V<sub>CC</sub> 2 2.7 3.3 V Supply Voltage 3.0  $V_{CC}+0.2$  $\mathrm{V}_{\mathrm{IH}}$ V Input Voltage 1 2.2  $V_{IL}$ -0.2 0.4 V Input Voltage

Notes:

1.  $V_{CC}$  is the lower one of F-V<sub>CC</sub> and S-V<sub>CC</sub>.

2.  $V_{CC}$  includes both F-V<sub>CC</sub> and S-V<sub>CC</sub>.

## 10. Pin Capacitance<sup>(1)</sup>

Symbol Parameter Condition Notes Min. Тур. Max. Unit  $V_{IN} = 0V$ C<sub>IN</sub> 15 Input capacitance pF  $V_{I/O} = 0V$ C<sub>I/O</sub> I/O capacitance 25 pF

Note:

1. Sampled but not 100% tested.

$(T_A = 25^{\circ}C, f = 1MHz)$

|                                          | L                                                                                   | DC Elec |      |                     |      | $(T_A =$ | = $-25^{\circ}$ C to $+85^{\circ}$ C, V <sub>CC</sub> = 2.7V to 3.3V                                                                                         |

|------------------------------------------|-------------------------------------------------------------------------------------|---------|------|---------------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                   | Parameter                                                                           | Notes   | Min. | Тур. <sup>(1)</sup> | Max. | Unit     | Conditions                                                                                                                                                   |

| I <sub>LI</sub>                          | Input Leakage Current                                                               |         |      |                     | ±1.5 | μΑ       | V <sub>IN</sub> =V <sub>CC</sub> or GND                                                                                                                      |

| $I_{LO}$                                 | Output Leakage Current                                                              |         |      |                     | ±1.5 | μΑ       | $V_{OUT} = V_{CC}$ or GND                                                                                                                                    |

| Laga                                     | F-V <sub>CC</sub> Standby Current                                                   | 2,4     |      | 2                   | 15   | μΑ       | $\frac{\text{CMOS Input}}{\text{F-CE} = \text{F-RP}} = \text{F-V}_{\text{CC}} \pm 0.2\text{V}$                                                               |

| I <sub>CCS</sub>                         |                                                                                     | ∠,4     |      | 0.2                 | 2    | mA       | $\begin{array}{l} \text{TTL Input} \\ \text{F-}\overline{\text{CE}} = \text{F-}\overline{\text{RP}} = V_{\text{IH}} \end{array}$                             |

| I <sub>CCAS</sub>                        | F-V <sub>CC</sub> Auto Power-Save Current                                           | 3,4     |      | 2                   | 15   | μΑ       | $\frac{\text{CMOS Input}}{\text{F-CE}} = \text{GND} \pm 0.2\text{V}$                                                                                         |

| I <sub>CCD</sub>                         | F-V <sub>CC</sub> Reset Power-Down Current                                          |         |      | 2                   | 15   | μΑ       | $      F-\overline{RP} = GND \pm 0.2V        I_{OUT}(F-RY/\overline{BY}) = 0mA $                                                                             |

| Lean                                     | F-V <sub>CC</sub> Read Current                                                      | 1       |      | 15                  | 25   | mA       | CMOS Input<br>F- $\overline{CE}$ = GND, f = 5MHz, I <sub>OUT</sub> = 0mA                                                                                     |

| I <sub>CCR</sub>                         | r-v <sub>CC</sub> Keau Current                                                      | 4       |      |                     | 30   | mA       | $\frac{\text{TTL Input}}{\text{F-}\overline{\text{CE}}} = \text{V}_{\text{IL}}, \text{ f} = 5\text{MHz}, \text{ I}_{\text{OUT}} = 0\text{mA}$                |

| I <sub>CCW</sub>                         | F-V <sub>CC</sub> Word Write or Set Lock-Bit<br>Current                             | 7       |      | 5                   | 17   | mA       | $F-V_{CCW} = V_{CCWH}$                                                                                                                                       |

| I <sub>CCE</sub>                         | F-V <sub>CC</sub> Block Erase, Full Chip Erase or<br>Clear Block Lock-Bits Current  | 7       |      | 4                   | 17   | mA       | $F-V_{CCW} = V_{CCWH}$                                                                                                                                       |

| I <sub>CCWS</sub><br>I <sub>CCES</sub>   | F-V <sub>CC</sub> Word Write or Block Erase Suspend Current                         |         |      | 1                   | 6    | mA       | $F-\overline{CE} = V_{IH}$                                                                                                                                   |

| I <sub>CCWS</sub>                        | F-V <sub>CCW</sub> Standby or Read Current                                          |         |      | ±2                  | ±15  | μΑ       | $F-V_{CCW} \le F-V_{CC}$                                                                                                                                     |

| I <sub>CCWR</sub>                        | r-v <sub>CCW</sub> standby of Keau Current                                          | ĺ       |      | 10                  | 200  | μΑ       | $F-V_{CCW} > F-V_{CC}$                                                                                                                                       |

| I <sub>CCWAS</sub>                       | F-V <sub>CCW</sub> Auto Power-Save Current                                          | 3,4     |      | 0.1                 | 5    | μΑ       | $\frac{CMOS \text{ Input}}{F-\overline{CE}} = \text{GND} \pm 0.2\text{V}$                                                                                    |

| I <sub>CCWD</sub>                        | F-V <sub>CCW</sub> Reset Power-Down Current                                         |         | <br> | 0.1                 | 5    | μΑ       | $F-\overline{RP} = GND \pm 0.2V$                                                                                                                             |

| I <sub>CCWW</sub>                        | $F-V_{CCW}$ Word Write or Set Lock-Bit Current                                      | 7       |      | 12                  | 40   | mA       | $F-V_{CCW} = V_{CCWH}$                                                                                                                                       |

| I <sub>CCWE</sub>                        | F-V <sub>CCW</sub> Block Erase, Full Chip Erase<br>or Clear Block Lock-Bits Current | 7       |      | 8                   | 25   | mA       | $F-V_{CCW} = V_{CCWH}$                                                                                                                                       |

| I <sub>CCWWS</sub><br>I <sub>CCWES</sub> | F-V <sub>CCW</sub> Word Write or Block Erase<br>Suspend Current                     |         |      | 10                  | 200  | μΑ       | $F-V_{CCW} = V_{CCWH}$                                                                                                                                       |

| I <sub>SB</sub>                          | S-V <sub>CC</sub> Standby Current                                                   |         |      | 1                   | 15   | μΑ       | $\overline{\text{S-CE}}_1$ , $\overline{\text{S-CE}}_2 \ge \overline{\text{S-V}}_{\text{CC}} - 0.2\text{V}$ or<br>$\overline{\text{S-CE}}_2 \le 0.2\text{V}$ |

| I <sub>SB1</sub>                         | S-V <sub>CC</sub> Standby Current                                                   |         |      |                     | 3    | mA       | $S - \overline{CE}_1 = V_{IH} \text{ or } S - CE_2 = V_{IL}$                                                                                                 |

| DC Electrical Characteristics (Continue)<br>$(T_A = -25^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 2.7V \text{ to } 3.3V)$ |                                                                                                                |     |      |  |                         |    |                                                                                                                                                                                             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------|--|-------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                                                                                                      | Parameter Notes Min. Typ. <sup>(1)</sup> Max. Unit Conditions                                                  |     |      |  |                         |    |                                                                                                                                                                                             |  |  |  |

| I <sub>CC1</sub>                                                                                                            | S-V <sub>CC</sub> Operation Current                                                                            |     |      |  | 45                      |    | $ \begin{array}{l} S \overline{CE}_1 = V_{IL}, \\ S \overline{CE}_2 = V_{IH}, \\ V_{IN} = V_{IL} \text{ or } V_{IH} \end{array} t_{CYCLE} = Min. \\ I_{I/O} = 0mA \end{array} $             |  |  |  |

| I <sub>CC2</sub>                                                                                                            | S-V <sub>CC</sub> Operation Current                                                                            |     |      |  | 8                       | mA | $\begin{array}{l} S - \overline{CE}_1 = 0.2V, \\ S - CE_2 = S - V_{CC} - 0.2V, \\ V_{IN} = S - V_{CC} - 0.2V \\ or \ 0.2V \end{array} t_{CYCLE} = 1 \mu s \\ I_{I/O} = 0 mA \\ \end{array}$ |  |  |  |

| V <sub>IL</sub>                                                                                                             | Input Low Voltage                                                                                              | 7   | -0.2 |  | 0.4                     | V  |                                                                                                                                                                                             |  |  |  |

| V <sub>IH</sub>                                                                                                             | Input High Voltage                                                                                             | 7   | 2.2  |  | V <sub>CC</sub><br>+0.2 | V  |                                                                                                                                                                                             |  |  |  |

| V <sub>OL</sub>                                                                                                             | Output Low Voltage                                                                                             | 2,7 |      |  | 0.4                     | V  | $I_{OL} = 0.5 mA$                                                                                                                                                                           |  |  |  |

| V <sub>OH</sub>                                                                                                             | Output High Voltage                                                                                            | 7   | 2    |  |                         | V  | $I_{OH} = -0.5 \text{mA}$                                                                                                                                                                   |  |  |  |

| V <sub>CCWLK</sub>                                                                                                          | F-V <sub>CCW</sub> Lockout during Normal Operations                                                            | 5,7 |      |  | 1.5                     | V  |                                                                                                                                                                                             |  |  |  |

|                                                                                                                             | F-V <sub>CCW</sub> during Block Erase, Full Chip<br>Erase, Word Write, or Lock-Bit<br>configuration Operations |     | 2.7  |  | 3.3                     | V  |                                                                                                                                                                                             |  |  |  |

| V <sub>LKO</sub>                                                                                                            | F-V <sub>CC</sub> Lockout Voltage                                                                              |     | 2    |  |                         | V  |                                                                                                                                                                                             |  |  |  |

Notes:

1. All currents are in RMS unless otherwise noted. Reference values at  $V_{CC} = 3.0V$  and  $T_A = +25^{\circ}C$ .

2. Includes  $F-RY/\overline{BY}$ .

3. The Automatic Power Savings (APS) feature is placed automatically power save mode that addresses not switching more than 300ns while read mode.

CMOS inputs are either V<sub>CC</sub> ± 0.2V or GND ± 0.2V. TTL inputs are either V<sub>IL</sub> or V<sub>IH</sub>.

Block erases, full chip erase, word writes and lock-bits configurations are inhibited when F-V<sub>CCW</sub> ≤ V<sub>CCWLK</sub> and not guaranteed in the range between V<sub>CCWLK</sub> (Max.) and V<sub>CCWH</sub> (Min.), and above V<sub>CCWH</sub> (Max.).

6.  $V_{CC}$  includes both F-V<sub>CC</sub> and S-V<sub>CC</sub>.

7. Sampled, not 100% tested.

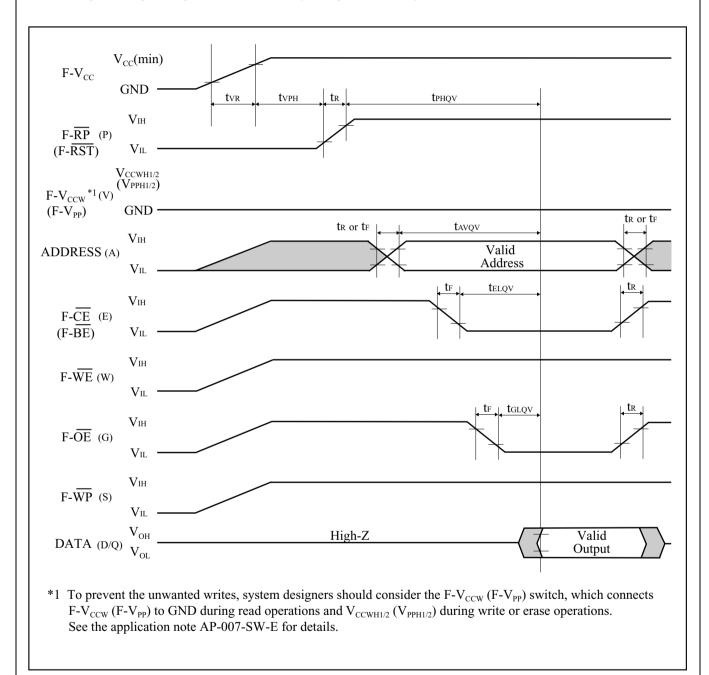

12. AC Electrical Characteristics for Flash Memory

| 12.1 | AC | Test | Conditions |

|------|----|------|------------|

|      |    |      |            |

| Input pulse level                  | 0V to 2.7V                                          |

|------------------------------------|-----------------------------------------------------|

| Input rise and fall time           | 10ns                                                |

| Input and Output timing Ref. level | 1.35V                                               |

| Output load                        | $1 \text{TTL} + \text{C}_{\text{L}} (50 \text{pF})$ |

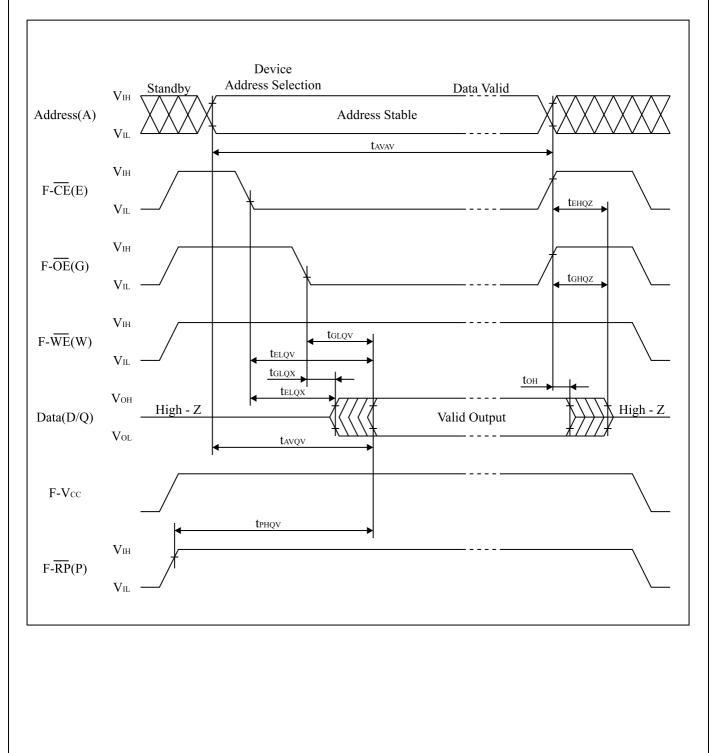

12.2 Read Cycle

|                   | (1                                                                                              | $f_A = -25^{\circ}C$ | to +85°C, | $V_{\rm CC} = 2.7$ | V to 3.3V) |

|-------------------|-------------------------------------------------------------------------------------------------|----------------------|-----------|--------------------|------------|

| Symbol            | Parameter                                                                                       | Notes                | Min.      | Max.               | Unit       |

| t <sub>AVAV</sub> | Read Cycle Time                                                                                 |                      | 90        |                    | ns         |

| t <sub>AVQV</sub> | Address to Output Delay                                                                         |                      |           | 90                 | ns         |

| t <sub>ELQV</sub> | F-CE to Output Delay                                                                            | 1                    |           | 90                 | ns         |

| t <sub>PHQV</sub> | F-RP High to Output Delay                                                                       |                      |           | 600                | ns         |

| t <sub>GLQV</sub> | F-OE to Output Delay                                                                            | 1                    |           | 40                 | ns         |

| t <sub>ELQX</sub> | F-CE to Output in Low-Z                                                                         |                      | 0         |                    | ns         |

| t <sub>EHQZ</sub> | F-CE High to Output in High-Z                                                                   |                      |           | 40                 | ns         |

| t <sub>GLQX</sub> | F-OE to Output in Low-Z                                                                         |                      | 0         |                    | ns         |

| t <sub>GHQZ</sub> | F-OE High to Output in High-Z                                                                   |                      |           | 15                 | ns         |

| t <sub>OH</sub>   | Output Hold form Address, $F-\overline{CE}$ or $F-\overline{OE}$ Change, Whichever Occurs First |                      | 0         |                    | ns         |

Note:

1. F- $\overline{OE}$  may be delayed up to  $t_{ELQV}$  -  $t_{GLQV}$  after the falling edge of F- $\overline{CE}$  without impact on  $t_{ELQV}$ .

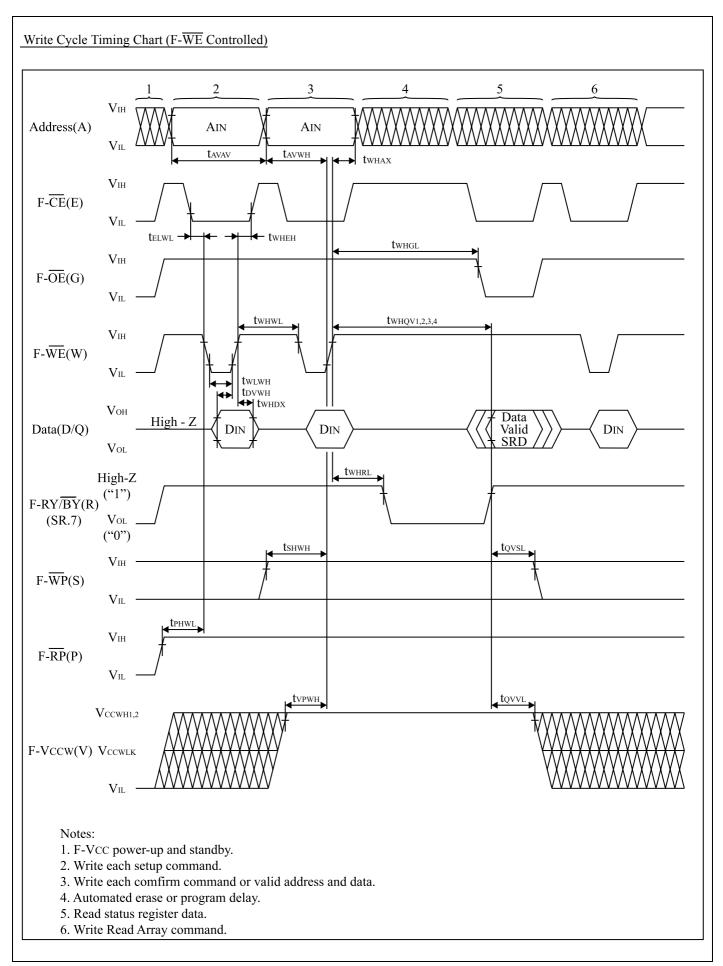

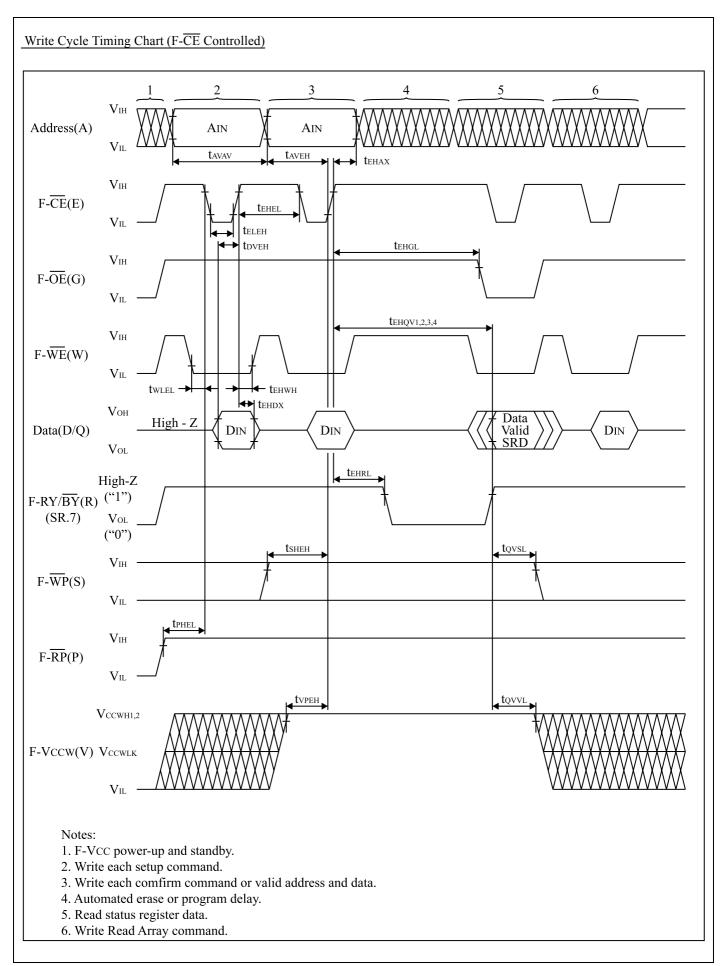

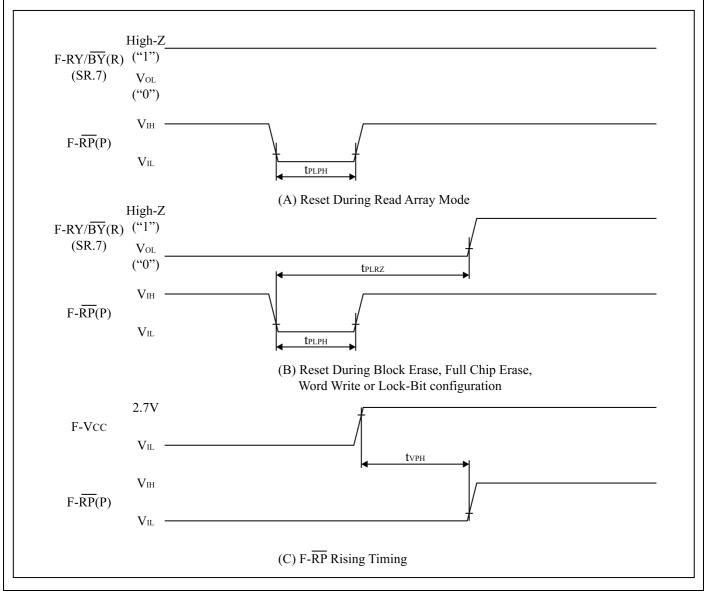

12.3 Write Cycle (F- $\overline{\text{WE}}$  Controlled)<sup>(1,5)</sup>

|                     |                                                                                      | $(T_A = -25^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 2.7 \text{V to } 3.3^{\circ})$ |      |      |      |  |  |

|---------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|--|--|

| Symbol              | Parameter                                                                            | Notes                                                                                  | Min. | Max. | Unit |  |  |

| t <sub>AVAV</sub>   | Write Cycle Time                                                                     |                                                                                        | 90   |      | ns   |  |  |

| t <sub>PHWL</sub>   | F-RP High Recovery to F-WE Going Low                                                 | 2                                                                                      | 1    |      | μs   |  |  |

| t <sub>ELWL</sub>   | F-CE Setup to F-WE Going Low                                                         |                                                                                        | 10   |      | ns   |  |  |

| t <sub>WLWH</sub>   | F-WE Pulse Width                                                                     |                                                                                        | 50   |      | ns   |  |  |

| t <sub>SHWH</sub>   | $F-\overline{WP} V_{IH}$ Setup to $F-\overline{WE}$ Going High                       | 2                                                                                      | 100  |      | ns   |  |  |

| t <sub>VPWH</sub>   | F-V <sub>CCW</sub> Setup to F-WE Going High                                          | 2                                                                                      | 100  |      | ns   |  |  |

| t <sub>AVWH</sub>   | Address Setup to F-WE Going High                                                     | 3                                                                                      | 50   |      | ns   |  |  |

| t <sub>DVWH</sub>   | Data Setup to $F-\overline{WE}$ Going High                                           | 3                                                                                      | 50   |      | ns   |  |  |

| t <sub>WHDX</sub>   | Data Hold from F-WE High                                                             |                                                                                        | 0    |      | ns   |  |  |

| t <sub>WHAX</sub>   | Address Hold from F-WE High                                                          |                                                                                        | 0    |      | ns   |  |  |

| t <sub>WHEH</sub>   | $F-\overline{CE}$ Hold from $F-\overline{WE}$ High                                   |                                                                                        | 10   |      | ns   |  |  |

| $t_{\mathrm{WHWL}}$ | F-WE Pulse Width High                                                                |                                                                                        | 30   |      | ns   |  |  |

| t <sub>WHRL</sub>   | F-WE going High to F-RY/BY Going Low                                                 |                                                                                        |      | 100  | ns   |  |  |

| t <sub>WHGL</sub>   | Write Recovery before Read                                                           |                                                                                        | 0    |      | ns   |  |  |

| t <sub>QVVL</sub>   | F-V <sub>CCW</sub> Hold from Valid SRD, F-RY/BY High-Z                               | 2,4                                                                                    | 0    |      | ns   |  |  |