QwikRadio<sup>®</sup> Sweep-Mode Receiver

### **General Description**

The MICRF008 QwikRadio<sup>®</sup> UHF receiver is a single-chip OOK (on-off keyed) receiver IC designed for remote wireless applications. This device is a true single-chip, "antenna-in, data-out" device, and it is easy to implement. MICRF008 receiver requires very few peripheral passive components. All tunings, RF and IF, are accomplished within the IC. Ease of use and minimal parts count translate to cost savings and shorter time to market. MICRF008 receiver offers a robust and low-cost solution for high volume wireless applications.

The MICRF008 sweeps the internal local oscillator at rates greater than the baseband data rate. This effectively broadens the RF bandwidth of the receiver to a value equivalent to conventional superregenerative receivers. This allows the MICRF008 to operate with less expensive LC transmitters without additional components or tuning, even though the receiver topology is still superheterodyne. In this mode the reference crystal can be replaced with a less expensive  $\pm 0.5\%$  ceramic resonator.

Since all post-detection (demodulator) data filtering is provided on the MICRF008, no external IF filters are required. One of the two internal filter bandwidths must be externally selected based on data rate and code modulation format.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

Complete UHF receiver on a monolithic chip 300MHz to 440MHz frequency range Up to 4.8kbps data rate. Automatic tuning, no manual adjustment Very low RF antenna reradiation CMOS logic interface for standard ICs Low external part count Replaces superregenerative receivers design Manufacturability and same performance over the years Very small PCB area required

### Applications

Garage door and gate openers Security systems Remote appliances control Toys Fan and light control

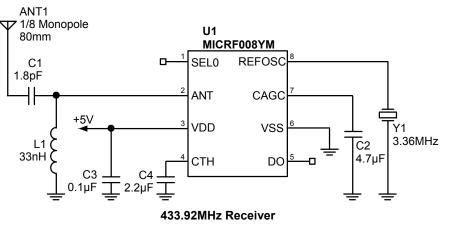

## **Typical Application**

QwikRadio is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

August 2008

## **Ordering Information**

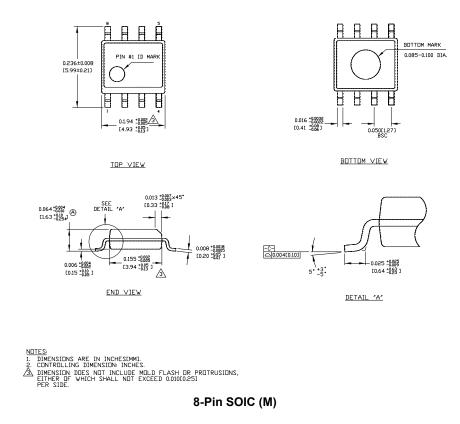

| Part Number | Junction Temperature Range | Package    | Lead Finish |

|-------------|----------------------------|------------|-------------|

| MICRF008YM  | –40°C to +85°C             | 8-Pin SOIC | Pb-Free     |

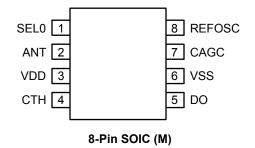

# **Pin Configuration**

## **Pin Description**

| Pin Number<br>SOIC-8 | Pin Name | Pin Name                                                                                                                                                                                                                                         |

|----------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | SEL0     | Bandwidth Selection Bit 0 (Digital Input): Sets the desired demodulator filter bandwidth. See Table 1. Internally pulled-up to VDD.                                                                                                              |

| 2                    | ANT      | Antenna (Input): High-impedance, internally AC-coupled receiver input. Connect this pin to the matching network. See "Applications Information" for optional band-pass filter information.                                                       |

| 3                    | VDD      | Positive Supply Input: Connect a low ESL, low ESR decoupling capacitor from this pin to VSS, as short as possible.                                                                                                                               |

| 4                    | СТН      | Data Slicing Threshold Capacitor (External Component): Capacitor extracts the DC average value from the demodulated waveform which becomes the reference for the internal data slicing comparator. See "Applications Information" for selection. |

| 5                    | DO       | Data Output (Output): CMOS-level compatible data output signal.                                                                                                                                                                                  |

| 6                    | VSS      | Negative Supply Input: Connect this pin to the RF ground.                                                                                                                                                                                        |

| 7                    | CAGC     | AGC Capacitor (External Component): Integrating capacitor for on-chip AGC (automatic gain control). The decay/attack time-constant (τ) ratio is nominally 10:1. See "Applications Information" for capacitor selection.                          |

| 8                    | REFOSC   | Reference Oscillator (External Component or Input): Timing reference for on-chip tuning and alignment. Connect either a ceramic resonator or a crystal between this pin and VSS, or drive the input with an AC-coupled 0.5VPP input clock.       |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>DDRF</sub> , V <sub>DDBB</sub> )     | +7V                       |

|-------------------------------------------------------------|---------------------------|

| Reference Oscillator Input Voltage (VREFOSC)                | V <sub>DDBB</sub>         |

| Input/Output Voltage (V <sub>I/O</sub> )V <sub>SS</sub> –0. | 3 to V <sub>DD</sub> +0.3 |

| Junction Temperature (T <sub>J</sub> )                      | +150°C                    |

| Storage Temperature (T <sub>s</sub> )65                     | 5°C to 150°C              |

| Lead Temperature (soldering, 10 sec.)                       | 260°C                     |

| ESD Rating <sup>(3)</sup>                                   |                           |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>DD</sub> )     | +4.75V to +5.5V                          |

|---------------------------------------|------------------------------------------|

| Ambient Temperature (T <sub>A</sub> ) | –40°C to +85°C                           |

| RF Frequency Range                    | 300MHz to 440Hz                          |

| Data Duty-Cycle                       | 20% to 80%                               |

| Reference Oscillator Input Range      | 0.2V <sub>PP</sub> to 1.5V <sub>PP</sub> |

| Demon Bandwidth                       | 0.1 to 4.8kHz                            |

# Electrical Characteristics<sup>(4)</sup>

+4.75V  $\leq$  V<sub>DD</sub>  $\leq$  5.5V, V<sub>SS</sub> = 0V; C<sub>AGC</sub> = 4.7µF, C<sub>TH</sub> = 2.2µF no preamble for data; f<sub>REFOSC</sub> = 3.36MHz. T<sub>A</sub> = 25°C, **bold** values indicate -40°C  $\leq$  T<sub>A</sub>  $\leq$  +85°C; current flow into device pins is positive; unless noted.

| Symbol                          | Parameter                                             | Condition                                                  | Min                | Тур | Max                | Units             |

|---------------------------------|-------------------------------------------------------|------------------------------------------------------------|--------------------|-----|--------------------|-------------------|

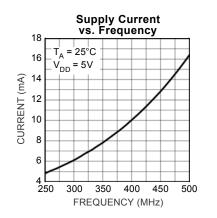

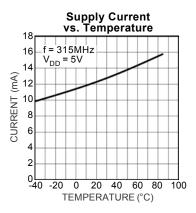

| I <sub>OP</sub>                 | Operating Current                                     | Continuous 315MHz operation                                |                    | 7   | 9                  | mA                |

|                                 |                                                       | continuous 433.92MHz operation                             |                    | 13  | 16                 | mA                |

|                                 |                                                       | reference oscillator powered down                          |                    | 2   | 2.5                | mA                |

| <b>RF Section</b>               | n, IF Section                                         |                                                            |                    |     |                    |                   |

|                                 | Receiver Sensitivity                                  | 315MHz, SEL0 = 0V; Notes 5, 6                              | -90                | -95 |                    | dBm               |

|                                 |                                                       | 433.92MHz, SEL0 = 0V; Notes 5, 6                           | -90                | -95 |                    | dBm               |

| f <sub>IF</sub>                 | IF Center Frequency                                   | Note 7                                                     |                    | 2.0 |                    | MHz               |

| f <sub>BW</sub>                 | IF Bandwidth                                          | 315MHz, <b>Notes 6, 7</b>                                  |                    | 0.8 |                    | MHz               |

|                                 |                                                       | 433.92MHz, Notes 6, 7                                      |                    | 1.1 |                    | MHz               |

|                                 | Maximum Receiver Input                                | $R_{SC} = 50\Omega$                                        |                    | -20 |                    | dBm               |

|                                 | Spurious Reverse Isolation                            | ANT pin, $R_{SC}$ = 50 $\Omega$ , <b>Note 8</b>            |                    | 30  |                    | μV <sub>RMS</sub> |

|                                 | AGC Attack to Decay Ratio                             | tattack ÷ tdecay                                           |                    | 0.1 |                    |                   |

| Reference                       | e Oscillator                                          | ·                                                          | •                  | •   |                    |                   |

|                                 | Reference Oscillator Source<br>Current                |                                                            |                    | 7   |                    | μA                |

| Z <sub>REFOSC</sub>             | Reference Oscillator Input<br>Impedance               | Note 9                                                     |                    | 200 |                    | kΩ                |

| Demodula                        | ator                                                  | - <b>·</b>                                                 |                    | •   | •                  |                   |

| Z <sub>CTH</sub>                | C <sub>TH</sub> Source Impedance                      | V <sub>SEL0</sub> = V <sub>DD</sub> , See Table 1, Note 10 |                    | 220 |                    | kΩ                |

| $\Delta Z_{CTH}$                | Maximum C <sub>TH</sub> Source<br>Impedance Variation |                                                            |                    | ±15 |                    | %                 |

| Digital/Co                      | ontrol Section                                        | ·                                                          |                    | •   |                    |                   |

| Z <sub>IN(pu)</sub>             | Input Pull-Up Impedance                               | SEL0                                                       |                    | 1.0 | 0.8                | MΩ                |

| I <sub>OUT</sub>                | Output Current                                        | DO pin, push-pull                                          |                    | 10  |                    | μA                |

| $V_{\text{OUT}(\text{high})}$   | Output High Voltage                                   | DO pin, I <sub>OUT</sub> = 1µA                             | 0.8V <sub>DD</sub> |     |                    | V                 |

| V <sub>OUT(low)</sub>           | Output Low Voltage                                    | DO pin, I <sub>OUT</sub> = 1µA                             |                    |     | 0.2V <sub>DD</sub> | V                 |

| t <sub>R</sub> , t <sub>F</sub> | Output Rise and Fall Times                            | DO pin, C <sub>LOAD</sub> = 15pF                           |                    | 10  | 1                  | μs                |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- Devices are ESD sensitive, use appropriate ESD precautions. Meets class 1 ESD test requirements, (human body model HBM), in accordance with MIL-STD-883C, method 3015. Do not operate or store near strong electrostatic fields.

- 4. Specification for packaged product only.

- Sensitivity is defined as the average signal level measured at the input necessary to achieve 10<sup>-2</sup> BER (bit error rate). The input signal is defined as a return-to-zero (RZ) waveform with 50% average duty cycle at a data rate of 1kbps (Manchester encoded). The RF input is assumed to be matched into 50Ω.

- 6. Sensitivity, a commonly specified receiver parameter, provides an indication of the receiver's input referred noise, generally input thermal noise. However, it is possible for a more sensitive receiver to exhibit range performance no better than that of a less sensitive receiver if the background noise is appreciably higher than the thermal noise. Background noise refers to other interfering signals, such as FM radio stations, pagers, etc.

A better indicator of achievable receiver range performance is usually given by its selectivity, often stated as intermediate frequency (IF) or radio frequency (RF) bandwidth, depending on receiver topology. Selectivity is a measure of the rejection by the receiver of ambient noise. More selective receivers will almost invariably provide better range. Only when the receiver selectivity is so high that most of the noise on the receiver input is actually thermal will the receiver demonstrate sensitivity-limited performance.

Parameter scales linearly proportional with reference oscillator frequency f<sub>T</sub>. For any reference oscillator frequency other than 3.36MHz, compute new parameter value as the ratio:

f<sub>REF</sub>OSC<sup>MHz</sup>

3 36MHz × (parameter value at 3.36MHz)

- Spurious reverse isolation represents the spurious components which appear on the RF input pin (ANT) measured into 50Ω with an input RF matching network

- Series resistance of the resonator (ceramic resonator or crystal) should be minimized to the extent possible. In cases where the resonator series

resistance is too great, the oscillator may oscillate at a diminished peak-to-peak level, or may fail to oscillate entirely. Micrel recommends that series

resistances for ceramic resonators and crystals not exceed 50Ω and 100Ω respectively.

- 10. Parameter scales linearly proportional with reference oscillator frequency f<sub>T</sub>. For any reference oscillator frequency other than 3.36MHz, compute new parameter value as the ratio:

3.36MHz

$\frac{1}{\text{f}}$  FREFOSC  $^{\text{MHz}}$  × (parameter value at 3.36MHz)

$C_{\text{TH}}$  source impedance in Table 1 is represented by (symbolic) resistor RSC in the MICRF008 Simplified Block Diagram. The Programmable LPF (Low Pass Filter) is also illustrated in the MICRF008 Simplified Block Diagram.

| SEL0 | Programmable LPF<br>Bandwidth (Hz) | C <sub>TH</sub> Source<br>Impedance (Ω) |

|------|------------------------------------|-----------------------------------------|

| 1    | 2400                               | 440k                                    |

| 0    | 4800                               | 220k                                    |

Table 1. Nominal Characteristics

Programmable LPF Bandwidth

and CTH Source Impedance

## **Typical Characteristics**

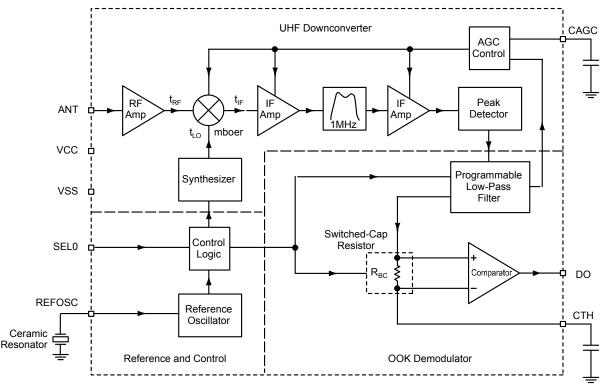

### **Functional Diagram**

Figure 1. MICRF008 Block Diagram

## **Functional Description**

The entire block diagram illustrates the basic structure of the MICRF008YM. It is made of three sub-blocks, which are the UHF Downconverter, the OOK Demodulator, and the Reference and Control. Also shown in the figure are two capacitors (CTH, and CAGC) and the reference frequency device, usually a ceramic resonator. With the exception of a supply decoupling capacitor and the matching network on the antenna pin, these are all the external components needed with the MICRF008YM to make a complete UHF receiver. There is one control input, the SEL0 pin. The purpose is to set the demodulator filter bandwidth of either 2.4kHz or 4.8kHz, and is set high or low according to the minimum pulse width in the demodulated signal. The input is CMOS compatible, and is pulled-up internally in the IC.

#### **Receiver Operation**

The MICRF008YM is a superheterodyne receiver working in sweep mode. It is capable of data rates up to 9.6kbaud NRZ or 4.8kbaud Manchester encoded. The MICRF008YM RF center frequency is controlled by a completely integrated PLL/VCO frequency synthesizer with frequency set by a ceramic resonator. The actual

swept bandwidth is approximately 3% of the RF carrier frequency. It makes an ideal part to work with LC-based transmitters or other types of transmitters that are not precise in nature and vary their frequency with time. In sweep mode the LO frequency (local oscillator) is varied in a rate much higher than the data signal, which results in down-conversion of approximately 3% of the carrier frequency present at the antenna pin. The low level RF signal is amplified by the RF amp section and downconverted by the mixer to the IF frequency which is amplified and filtered internally in the device and further amplified for the peak detector. The peak detector will detect the IF and further filtering is accomplished in the programmable low-pass filter. The detected/filtered signal is compared with the DC value of the demodulated signal in the data-slicer and a digital output is provided from the DO pin

#### Data Slicing Level

Extraction of the DC value of the demodulated signal for purposes of logic-level data slicing is accomplished by an external capacitor CTH and the on-chip switchedcapacitor resistor RSC, indicated in the block diagram. The effective resistance of RSC scales inversely proportional to REFOSC frequency. The nominal value of RSC given in the "Electrical Characteristics" Table is 220k $\Omega$  for a REFOSC frequency of 3.36MHz. Slicing level time constant value vary depending on data pattern, data rate and data duty cycle.

#### Automatic Gain Control (AGC)

The signal path has automatic gain control (AGC) to increase the overall receiver dynamic range. An external capacitor, CAGC, must be connected to the CAGC pin of the device. Normally the CAGC capacitor is connected to ground. If faster start-up times are required when the receiver is first poweredon, the CAGC capacitor may be connected to VDD. The ratio of decay-to-attack time constant is fixed at 10:1 (that is, the attack time constant is 1/10th of the decay time constant), and the user cannot change this ratio. Nevertheless, the attack time constant is set externally by choosing a value for CAGC.

Another function of the AGC control voltage is to raise the noise floor in order to guarantee a clean signal between the preamble and the data, sometimes called dead time. The AGC control voltage can be further manipulated and amplified to create an RSSI signal, which is useful for several different applications.

#### **Reference Oscillator**

All timing and tuning operations on the MICRF008YM are derived from the internal Colpitts reference oscillator. The reference frequency can be implemented in two ways, by using a resonator device (a ceramic resonator or crystal), or by driving an external signal, which should not exceed 0.5VRMS. The reference frequency is obtained by dividing the RF carrier frequency by 129.

#### I/O Pin Interface Circuitry

Interface circuitry for the various I/O pins of the MICRF008 is shown in Figures 2 through 6. Specific information regarding each of these circuits is discussed in the following subparagraphs. Not shown are ESD protection diodes which are applied to all input pins.

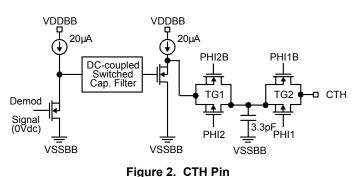

#### CTH Pin

Figure 2 illustrates the CTH pin interface circuit. CTH pin is driven from a P-Channel MOSFET source-follower biased with approximately 20µA of bias current. Transmission gates TG1 and TG2 isolate the 3.3pF capacitor. Internal control signals PHI1/PHI2 are related in a manner such that the impedance across the transmission gates looks like a "resistance." The DC potential on the CTH pin is approximately 2.2V, fundamentally determined by the VGS of the two PChannel MOSFET source-followers shown.

·

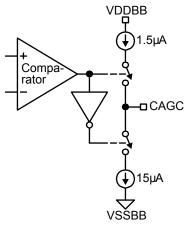

#### CAGC Pin

Figure 3 illustrates the CAGC pin interface circuit. The AGC control voltage is developed as an integrated current into a capacitor CAGC. The attack current is nominally 15 $\mu$ A, while the decay current is a 1/10th scaling of this, approximately 1.5 $\mu$ A. Signal gain of the RF/IF strip inside the IC diminishes as the voltage on CAGC decreases. By simply adding a capacitor to CAGC pin, the attack/decay time constant ratio is fixed at 1:10.

Figure 3. CAGC Pin

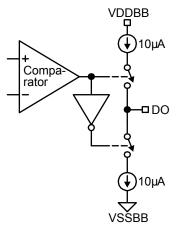

#### DO Pin

The output stage for the Data Comparator (DO pin) is shown in Figure 4. The output is a  $10\mu$ A push- $10\mu$ A pull, switched current stage. Such an output stage is capable of driving CMOS-type loads.

Figure 4. DO Pin

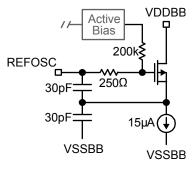

#### **REFOSC Pin**

The REFOSC input circuit is shown in Figure 5. Input impedance is quite high ( $200k\Omega$ ). This is a Colpitts oscillator, with internal 30pF capacitors. This input is intended to work with standard ceramic resonators, connected from this pin to VSSBB. The resonators should not contain integral capacitors, since these capacitors are contained inside the IC. Externally applied signals should be AC-coupled, amplitude limited to approximately 0.5V<sub>PP</sub>. The nominal DC bias voltage on this pin is 1.4V.

Figure 5. REFOSC Pin

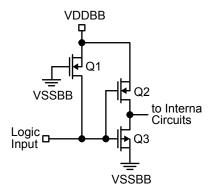

#### Control Input (SEL0)

Control input circuitry is shown in Figure 6. The standard input is a logic inverter constructed with minimum geometry MOSFETs (Q2, Q3). P-Channel MOSFET Q1 is a large channel length device which functions essentially as a "weak" pullup to VDDBB. Typical pullup current is  $5\mu$ A, leading to an impedance to the VDDBB supply of typically  $1M\Omega$ .

Figure 6. SEL0

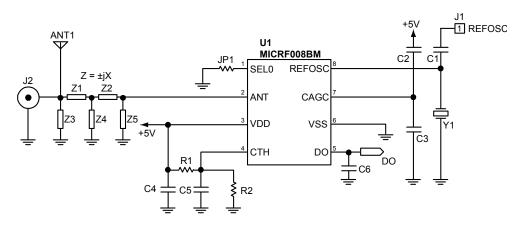

## **Test Circuit**

### **Test Circuit and Application Information**

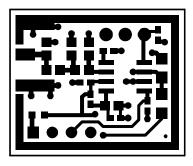

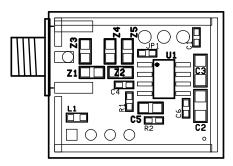

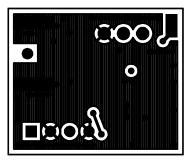

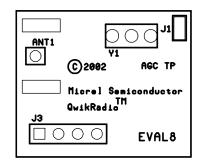

The test circuit is based on the EVAL8 PCB Design. Gerbers, the bill of material and complete schematic are available at Micrel website:

(http://www.micrel.com/product-info/qwikradio.shtml).

EVAL8 provides the means for a complete evaluation of the MICRF008YM. It is not intended as a final receiver design. For final receiver applications, look for the RX8-x series of reference designs. The board is a FR4 material, 0.062 inch thick, in two layers. It is strongly recommended that all RF designs are made in a minimum two-layer board, one side being as solid ground as possible. Blank EVAL8 boards are available for selected customers. To obtain a blank board contact your local Micrel representative/distributor. Four drawings are shown below, the top layer, bottom layer, the top silkscreen layer, and the bottom silkscreen layer. The size of the board is 0.910 x 0.760 inches. It provides the means to test the part thoroughly.

Figure 7a. Top Layer

Figure 7c. Top Silkscreen Layer

Figure 7b. Bottom Layer

Figure 7d. Bottom Silkscreen Layer

#### Input Connector/Antenna

Starting at J2, a SMA connector to connect to a RF signal generator. Levels above –20dBm should be avoided. An antenna pad is also provided. Solder a piece of solid wire for the frequency of interest. See Table 2 for 1/4 wavelength antennas. It should be noted that 1/4 wavelength antennas work best ONLY with ground planes of an equivalent size of the antenna. This is not the case here since the board size is very small.

| Freq. (MHz) | ANT1 (mm) | ANT1 (inches) |

|-------------|-----------|---------------|

| 315         | 231       | 9.1           |

| 390         | 185       | 7.3           |

| 418         | 173       | 6.8           |

| 433.92      | 168       | 6.6           |

Table 2. 1/4 Wave Antenna Lengths

The size of the antenna is calculated by the following equation:

$$\frac{1}{4}\lambda \text{Ant} = \frac{3 \times 10^8 \times 0.97 \times 1000}{\text{f} \times 4} \text{[mm]}$$

$$\frac{1}{4}\lambda \text{Ant} = \frac{3 \times 10^8 \times 0.97 \times 1000}{\text{f} \times 101.6} \text{[inches]}$$

where,

- 3 x 108 is the speed of light in vacuum in meter per seconds.

- 0.97 is a correction factor for the difference between electrical length and physical length and varies depending on ground plane, and objects next to the antenna.

- f is the frequency of interest in Hertz.

1/4 wavelength antennas are good for initial tests, but should never be used in a final product, unless the PCB area has a large ground plane. Small ground planes makes 1/4 wavelength monopole antennas unstable, and any object close to the antenna changes its impedance. It is completely useless if the antenna is not straight up or if any object touches it. Other antennas, such as half-wave dipole, or 1/8 wavelength monopole are better solutions for small ground planes. A 1/8 wavelength antenna has approximately half the size of a 1/4 wavelength antenna, which makes it very attractive for small designs. The 1/8 wavelength antenna is not as sensitive to proximity effects as the 1/4 wavelength antenna. However, the 1/8 wavelength antenna has a reactive element in its impedance that needs to be taken into account in the matching network. The halfwave dipole has a size approximately double the 1/4 wavelength and does not require a large ground plane. One side of the antenna is connected to the RF input and the other is connected to ground as seen in Figure 8.

Halfwave-Dipole Antenna

one side connected to the RF input

one side connected to ground

Figure 8. Halfwave-Dipole Antenna

#### **Matching Network**

Z1 to Z5 are used for the matching network. Not all parts are used at the same time. Several types of matching network can be implemented: T,  $\pi$ , or a L network. Here a matching network has two purposes. The main purpose is to match the antenna to the antenna pin. By matching it is meant to reduce the loss there is between two circuits; here the antenna being used or signal generator and the antenna pin. The secondary purpose is to filter undesired signals, which will reduce the receiver performance. Since it is a secondary function, more filtering may be required, depending on the amount of noise or adjacent signal interference present in the antenna. A T-Network was chosen assuming that an 1/4 wavelength antenna is being used, which has impedance close to  $50\Omega$  in free air or the receiver is being connected to a RF signal generator that has  $50\Omega$  output impedance. By using the proper matching elements, almost 9dB better sensitivity can be obtained. There are several techniques used for impedance matching. One frequently used is to plot impedance values in the Smith Chart. However, one needs to know the antenna impedance and the antenna pin impedance in the MICRF008YM to perform the matching. Table 3 below shows the antenna pin input impedance versus frequency and the matching elements needed to match  $50\Omega$  to the antenna pin.

| Freq. (MHz) | ANT1 (mm) | ANT1 (inches) |

|-------------|-----------|---------------|

| 315         | 231       | 9.1           |

| 390         | 185       | 7.3           |

| 418         | 173       | 6.8           |

| 433.92      | 168       | 6.6           |

**Note 1.** All inductors used are Coilcraft 0603 size, and the capacitors are Vishay COG 5%. Z3 and Z5 are not used.

Table 3. Antenna Input, Frequency and Matching Values

#### **C**<sub>TH</sub> Capacitor

In order to calculate the right value for the  $C_{TH}$  capacitor, the data format needs to have a preamble that resembles the data pattern, that is it has the same period and duty cycle. (See *"Application Hint 42"*) If the data pattern has no preamble, a large capacitor value should be used, such as 1µF to 2.2µF. However, if the data pattern has a preamble, the  $C_{TH}$  capacitor can be calculated and should be used instead of a large capacitor. This will guarantee a stable and reliable performance for the receiver. If the data pattern has variable data rates, the  $C_{TH}$  capacitor should be calculated for the lowest data rate and optimized in range tests. To find the  $C_{TH}$  capacitor value follow the procedure below:

- 1. Find the data period or bit period, and the reference oscillator frequency. The reference oscillator frequency is the RF carrier frequency divided by 129. The bit period is the elapsed time from one high and one low of the data pattern.

- 2. The  $C_{TH}$  capacitor is calculated by:

$$C_{TH} = \frac{5 \times \text{bit period} \times \text{REFOSC}}{144.55 \times 10^3} [\text{F}]$$

where:

REFOSC is the reference oscillator frequency in MHz.

Bit period is given in seconds and is the inverse of the baud rate for Manchester encoding.

The result obtained is in farads.

It follows the  $C_{TH}$  capacitor value for the common frequencies mentioned above in the Table 4. Again, as mentioned before, the data pattern needs preamble.

|                    | Baud Rate (Hz)          |                         |                         |

|--------------------|-------------------------|-------------------------|-------------------------|

| Frequency<br>(MHz) | 1000<br>С <sub>тн</sub> | 2400<br>С <sub>тн</sub> | 4800<br>С <sub>тн</sub> |

| 315                | 82nF                    | 39nF                    | 18nF                    |

| 390                | 100nF                   | 47nF                    | 22nF                    |

| 418                | 120nF                   | 47nF                    | 22nF                    |

| 433.93             | 120nF                   | 47nF                    | 22nF                    |

Table 4. Recommended C<sub>TH</sub> Capacitor Values

#### **C**<sub>AGC</sub> Capacitor

The function of the  $C_{AGC}$  capacitor is to minimize the ripple on the AGC control voltage by using a sufficiently large capacitor. It is suggested a value between 1µF to 10µF depending on data dead time, noise, and recovery time from strong to low RF signals. Large capacitor values can be connected to  $V_{DD}$  if fast charge time is required (C2). When connected to  $V_{DD}$ , it will charge 10

August 2008

times faster. The drawback is the ripple noise from AGC pin being thrown into the  $V_{DD}$  line. The signal on this pin is current-based, with an attack current of 15µA, and a decay current of 1.5µA. It is suggested the following values for the C<sub>AGC</sub> capacitors in the Table 5. Values can be further optimized during receiver range tests.

| Baud Rate (Hz) | C <sub>AGC</sub> (μF) |

|----------------|-----------------------|

| 1000           | 4.7 to 10             |

| 2400           | 2.2 to 4.7            |

| 4800           | 1 to 2.2              |

| Table 5. | Recommended | Values for C <sub>AGC</sub> |

|----------|-------------|-----------------------------|

|----------|-------------|-----------------------------|

#### **Reference Oscillator Frequency**

A Colpitts oscillator inside the chip generates the reference oscillator frequency. It requires a resonator of some kind connected to the REFOSC pin. Either a ceramic resonator or a crystal can be used. A resonator is chosen due to its lower cost and because the MICRF008YM is running in sweep mode, which does not require the precision of a crystal. Resonators found in the market normally have a precision of 0.5%. This precision is sufficient for the MICRF008YM. The reference oscillator frequency can also be generated by an external source through connector J1 and capacitor C1. The maximum level should not exceed  $0.5V_{RMS}$ . The reference oscillator frequency is calculated by the following equation and Table 6 shows the resonator frequency for the most common used frequencies:

$$\mathsf{REFOSC} = \frac{\mathsf{fc}}{\mathsf{129}}$$

where:

- REFOSC is the reference oscillator frequency in MHz.

- fc is the RF received carrier frequency of interest in MHz.

| Frequency (MHz) | REFOSC (MHz) |

|-----------------|--------------|

| 315             | 2.44         |

| 390             | 3.02         |

| 418             | 3.24         |

| 433.92          | 3.36         |

Table 6. Reference Oscillator Frequency

For a list of ceramic resonator manufactures, see *"Application Hint 35."*

#### SEL0 Pin – Setting the Demodulator Bandwidth

The SEL0 pin sets the demodulator bandwidth. When the pin is connected to ground the demodulator bandwidth is set to its minimum. When the pin is left floating (internal pull-up) or connected to VDD, the demodulator bandwidth is set to its maximum. The demodulator bandwidth is a function of the RF frequency used. See Table 7 for the most common frequency used versus the demodulator bandwidth.

|      | RF Carrier Frequency (MHz) |        |        |        |

|------|----------------------------|--------|--------|--------|

| SEL0 | 315                        | 390    | 418    | 433.92 |

| 0    | 1.6kHz                     | 2.0kHz | 2.2kHz | 2.4kHz |

| 1    | 3.6kHz                     | 4.0kHz | 4.4kHz | 4.8kHz |

Table 7. Demodulator Bandwidth

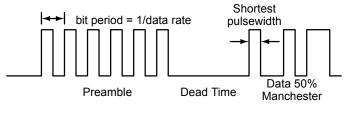

To determine what is the demodulator bandwidth required for the application, the absolute minimum pulse width used in the encoder transmitted signal needs to be found. The data pattern has several different types of pulse width depending what data format is being used (NRZ, Manchester, PWM, etc). The minimum pulsewidth is the shortest pulse in the output of the encoder being sent to the transmitter input measured during one bit time when the signal is high. See Figure 9 below for clarification.

Figure 9. Data Pattern

Then, the demodulator bandwidth required is calculated by:

$$\mathsf{Demod}\,\mathsf{BW} = \frac{0.65}{\mathsf{shortest}\,\mathsf{pulse}} \big[\mathsf{Hz}\big]$$

#### **Data Squelching**

Data squelching can be achieved by software or hardware. The software squelch is preferred over hardware squelch for it is more flexible, reliable, lower cost over manufacturing, etc. However, it takes time and resources to develop any software. If one needs a squelch function, a resistor can be used in the  $C_{TH}$  pin. R1 and R2 are in the test circuit for this purpose. Either one of them can be used or both. If only one resistor is used, the value of the resistor should be chosen according to the amount of squelch needed and if the DO pin needs to be sitting high or low without an RF income signal. Values from 10M $\Omega$  and below can be used. When both resistors are used, a more accurate control can be achieved for the squelch function.

The drawbacks using these resistors are: loss in receiver sensitivity, reduced demodulator bandwidth, and the  $C_{TH}$  capacitor equation will not work. As a result,  $C_{TH}$  capacitor will have to be determined empirically. Another way to implement a hardware squelch is to make R1 equal to 10M $\Omega$  to 6.8M $\Omega$ , and use a low-pass filter after the DO pin and a comparator circuit. The low-pass filter can be a capacitor, which is C6 in the Test Circuit. The reference voltage in the comparator can be set close to VDD/2 and the other input connected to the DO pin.

#### **Power Supply Filter**

A decoupling capacitor right at the VDD pin is strongly recommended as it is in the test circuit, which has  $0.1\mu$ F. Not shown in the Test Circuit Schematic is an EMI Inductor, L1 in the silkscreen layer. It has the purpose to further filter an income noise on the VDD line, generally present in switching power supplies. It is good practice to separate RF ground from digital ground and also VDD RF from other VDD lines

### **Package Information**

## MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.