# **TL3M Device Triple Level 3 Mapper** TXC-03453B

# DATA SHEET

# FEATURES

- Maps up to three independent DS3/E3 line formats into SDH/SONET formats as follows:

- DS3 to/from STM-1/TUG-3

- DS3 to/from STS-3/STS-1

- E3 to/from STM-1/TUG-3

- SDH/SONET bus access:

- Byte-wide drop and Add buses Drop bus timing mode (Add bus timing derived from Drop bus)

- Add bus timing mode (independent timing for drop/Add buses)

- Path overhead byte processing:

- Microprocessor access External interface

- B3 generation/detection with test mask

- B3 bit/block performance counters

- REI bit/block performance counters

- C2 mismatch detection

- C2 unequipped detection and generation

- Alarm indication port

- Path REI count and RDI status for APS applications

- O-bit channel access via external interface

- Digital desynchronizer with internal pointer leak algorithm

- Line interface:

- NRZ or P/N rail option for transmit and for receive Monitor NRZ transmit data

- Microprocessor access:

- Motorola or Intel compatible

- Hardware interrupt with mask bits

- Software polling bits

- Testing

- Facility or line loopback

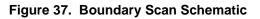

- PRBS generator/analyzer Boundary scan (IEEE 1149.1 standard)

- A fully tested device driver is available

- 3.3 volt power supply, 5 volt tolerant inputs

- 324-lead plastic ball grid array package (23 mm x 23 mm)

Each of the three channels of the TL3M can map a DS3 line signal into an STM-1 TUG-3 or STS-3 STS-1 SPE SDH/SONET signal. An E3 signal can be mapped only into an STM-1 TUG-3. The TL3M interfaces to an STM-1 or STS-3 SDH/SONET signal using a byte- wide parallel interface in the TranSwitch Telecom Bus format. The TL3M supports Drop bus and Add bus SDH/ SONET timing modes. Drop bus timing provides the timing sig-nals for the add side. Timing for both buses is independent for the Add bus timing mode. Individual POH bytes are mapped into a RAM interface for microprocessor access and to an external interface for external processing if required. In the add direction (except for the B3 byte) POH bytes may be inserted individually from RAM locations, from the external interface, or from the local side/alarm indication port. An option is provided to generate an unequipped channel or AIS. An external interface is provided for accessing the O-bits. An alarm indication port is provided for ring operation. The TL3M also uses internal digital desynchronizers that have a built-in pointer leak algorithm. The line side can be configured for a NRZ or positive/negative rail interface. For testing purposes, the TL3M provides boundary scan, PRBS generators and analyzers, a BIP error mask, and DS3/E3 line and facility loopbacks. The TL3M provides either Motorola or Intel micróprocessor access. The interrupt has programmable mask bits. A software polling register is also provided.

# APPLICATIONS

- Add/drop multiplexers

- Digital cross connect systems

- Broadband switching systems

- Transmission equipment

PRELIMINARY information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product

External O-Bit POH Alarm Control Interfaces Interfaces Signals Interfaces SDH/SONET SIDE LINE SIDE (TELECOM BUS) Receive Interfaces (3) Drop Bus (Rail, NRZ) TL3M Transmit Monitor **Triple Level 3 Mapper** Interfaces (3) TXC-03453B ransmit Interfaces (3) Add Bus (Rail, NRZ) 1 Alarm Boundary Microprocessor Interface Indication Scan Port U.S. Patents No.: 4,967,405; 5,040,170; 5,157,655; 5,265,096; 5,297,180; 5,289,507; 5,473,611; 5,535,218; 5,528,598; 6,463,111 B1 U.S. and/or foreign patents issued or pending Document Number: Copyright © 2003 TranSwitch Corporation PRELIMINARY TXC-03453B-MB, Ed. 3 PHAST, TranSwitch and TXC are registered trademarks of TranSwitch Corporation September 2003 TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 USA Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com

Downloaded from Elcodis.com electronic components distributor

## DATA SHEET

# TABLE OF CONTENTS

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| Features                                               | 4    |

| Application Examples                                   | 8    |

| Block Diagram                                          | 9    |

| Block Diagram Description                              | 10   |

| Lead Diagram                                           | 15   |

| Lead Descriptions                                      | 16   |

| Absolute Maximum Ratings and Environmental Limitations | 29   |

| Thermal Characteristics                                | 29   |

| Power Requirements                                     | 29   |

| Input, Output and Input/Output Parameters              | 30   |

| Timing Characteristics                                 |      |

| Operation                                              | 51   |

| Digital Desynchronizer PLL Connections                 | 51   |

| Transmit and Receive Synthesizer Connections           | 51   |

| Typical Test Results                                   | 52   |

| MTIE per GR-253-CORE Sec 5.7                           | 54   |

| Testing                                                | 58   |

| Boundary Scan                                          | 60   |

| Memory Map                                             | 62   |

| Package Information                                    | 90   |

| Ordering Information                                   | 91   |

| Related Products                                       | 91   |

| Standards Documentation Sources                        |      |

| List of Data Sheet Changes                             | 94   |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# LIST OF FIGURES

#### Figure

#### Page

| 1          | Typical Application using the TL3M and PHAST-3N Devices                | 0  |

|------------|------------------------------------------------------------------------|----|

| 1.<br>2.   | TL3M TXC-03453B Block Diagram                                          |    |

| 2.<br>3.   | TL3M Multiplexing Structure                                            |    |

| 3.<br>4.   | SONET AU-3/STS-1 SPE Build Format                                      |    |

| 4.<br>5.   | ITU-T TUG-3 Build Format                                               |    |

| 5.<br>6.   | TL3M TXC-03453B Lead Diagram                                           |    |

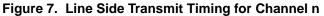

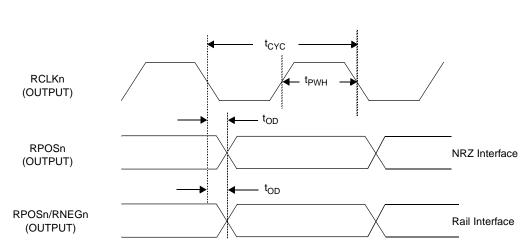

| 0.<br>7.   | Line Side Transmit Timing for Channel n                                |    |

| 7.<br>8.   | Line Side Receive Timing for Channel n                                 |    |

| o.<br>9.   | Line Side Receive Timing for Chamer A                                  |    |

| 9.<br>10.  | STM-1 Add Bus Derived Interface Timing                                 |    |

| 10.        | STN-1 Add Bus Derived Interface Timing                                 |    |

| 11.<br>12. | C C                                                                    |    |

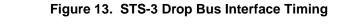

| 12.<br>13. | STM-1 Drop Bus Interface Timing                                        |    |

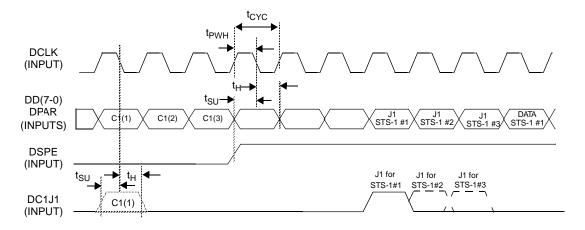

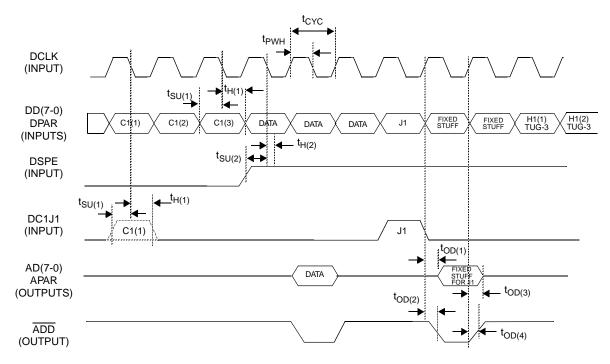

| 13.<br>14. | STS-3 Drop Bus Interface Timing<br>STM-1 Add/Drop Bus Interface Timing |    |

| 14.<br>15. |                                                                        |    |

| 15.<br>16. | STS-3 Add/Drop Bus Interface Timing<br>Transmit Path Overhead Timing   |    |

| -          |                                                                        |    |

| 17.        | Receive Path Overhead Timing                                           |    |

| 18.        | Transmit Alarm Indication Port Timing                                  |    |

| 19.<br>20  | Receive Alarm Indication Port Timing                                   |    |

| 20.        | Transmit Overhead Communications Channel Interface Timing              |    |

| 21.        | Receive Overhead Communications Channel Interface Timing               |    |

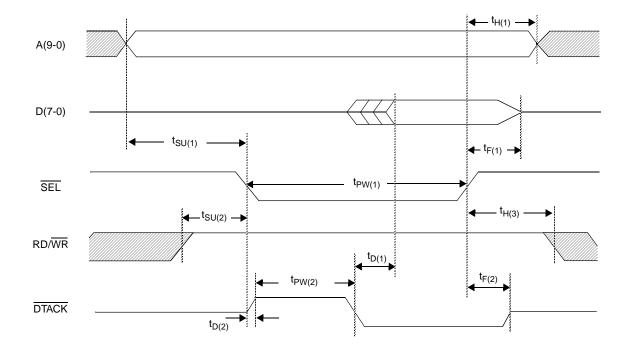

| 22.        | Intel Microprocessor Read Cycle Timing                                 |    |

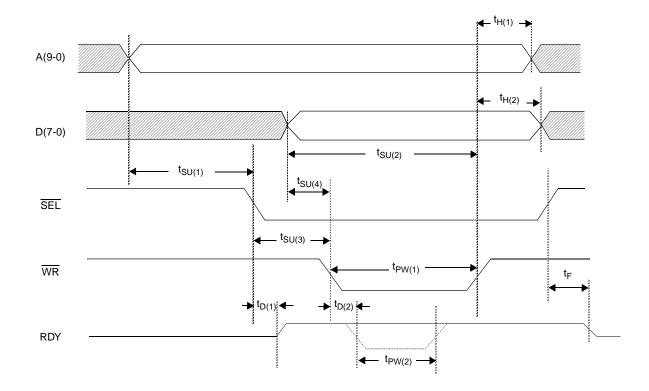

| 23.        | Intel Microprocessor Write Cycle Timing                                |    |

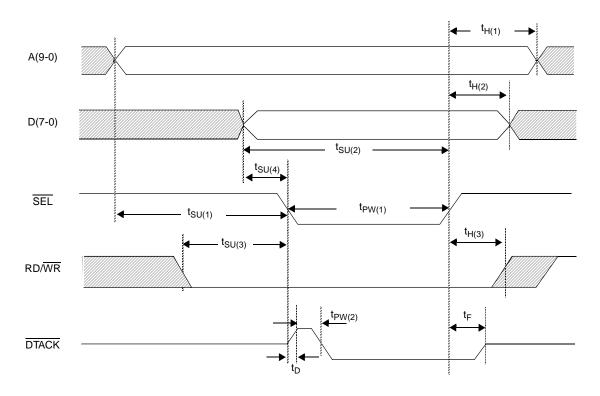

| 24.        | Motorola Microprocessor Read Cycle Timing                              |    |

| 25.        | Motorola Microprocessor Write Cycle Timing                             |    |

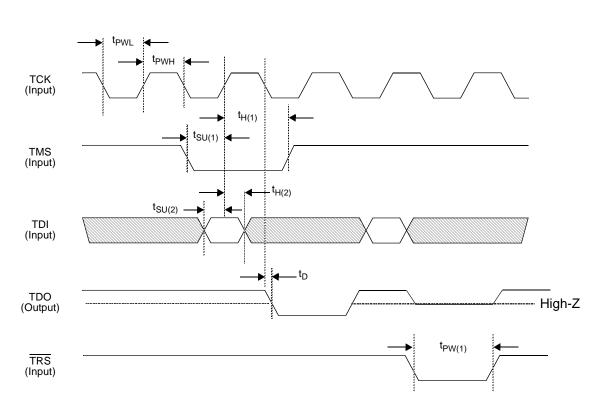

| 26.        | Boundary Scan Timing                                                   |    |

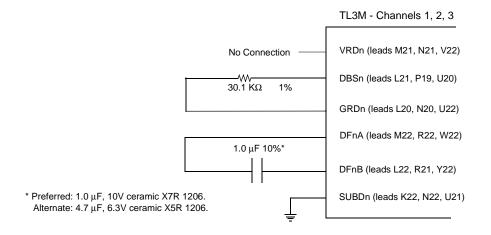

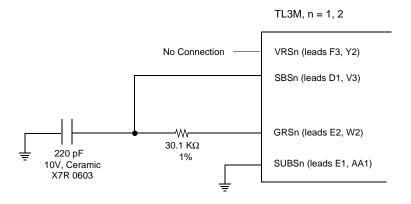

| 27.        | Digital Desynchronizer External Component Connections                  |    |

| 28.        | Transmit and Receive Synthesizer External Component Connections        |    |

| 29.        | STS3/DS3 Mapping, Measured Jitter                                      |    |

| 30.        | STM1/E3 Mapping, Measured Jitter                                       |    |

| 31.        | STS-1 Pointer Movements on DS3 Payload                                 |    |

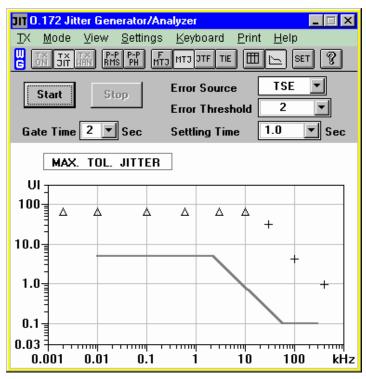

| 32.        | Jitter Tolerance for DS3 (from GR-499)                                 |    |

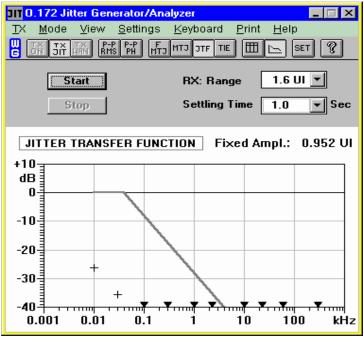

| 33.        | Jitter Transfer for DS3 (GR-253)                                       |    |

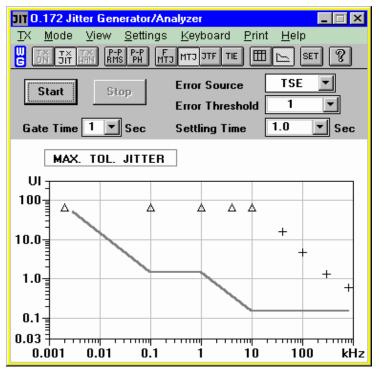

| 34.        | Jitter Tolerance for E3 (ITU G.751 Fig. 2)                             |    |

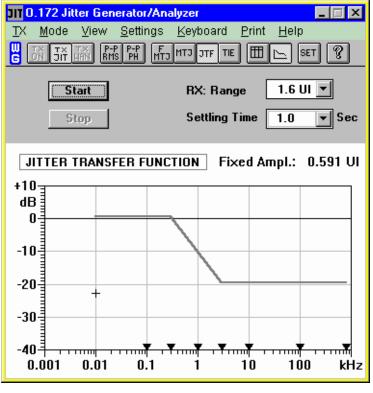

| 35.        | Jitter Transfer for E3 (from ITU G.823 Fig. 15)                        |    |

| 36.        | Per Channel Loopbacks and PRBS Test Generators/Analyzer                |    |

| 37.        | Boundary Scan Schematic                                                |    |

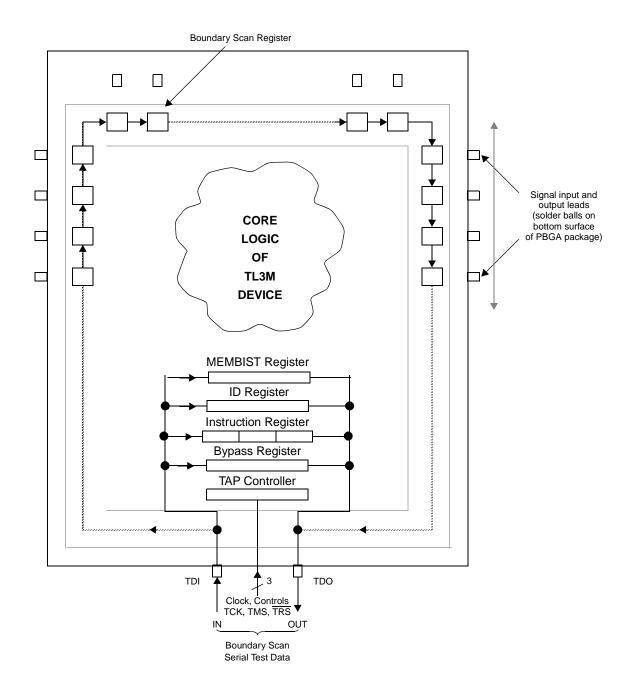

| 38.        | TL3M TXC-03453B Package Diagram                                        | 90 |

DATA SHEET

# FEATURES

The TL3M supports the following features. Please note that the convention used here is that the transmit (or add) direction is from the DS3/E3 line signal (rail or NRZ) to the SDH/SONET format (Telecom Bus), while the receive (or drop) direction is from the SDH/SONET format to the DS3/E3 line.

#### Bus Timing (Telecom Bus):

The TL3M provides the following bus timing modes for the Telecom Bus modes of operation:

- Drop bus timing

- Add bus timing is derived from the Drop bus timing input signals

- Drop bus: C1J1, SPE, optional C1, data, clock, and parity signals leads are inputs

- Add bus: data, parity, and add indication signal leads are outputs

- Add bus timing

- · Add bus timing is supplied and is independent of the Drop bus timing

- Drop bus: C1J1, SPE, optional C1, data, clock and parity signal leads are inputs

- Add bus: clock, C1J1, and SPE signal leads are inputs; data, parity, and add indication signal leads are outputs

#### Mappings:

The TL3M provides the following mapping features:

- Maximum of three channels for either E3 or DS3 line signals

- STM-1 AU-4 VC-4 format

- Each E3 or DS3 signal into TUG-3 format

- STS-3 format

- Each DS3 signal into STS-1 format

- Same drop and Add bus for all channels

- Add bus contention indication (same channel assignment)

- Add Bus: high impedance Add bus if there is contention

- Broadcast mode

- Drop Bus: multiple channel assignment to the same TUG-3

#### SDH/SONET Rates:

The TL3M provides the following Telecom Bus rates and format mappings:

- STS-3 STS-1s (19.44 Mbyte/s)

- STM-1 VC-4 (19.44 Mbyte/s)

## Other Telecom Bus Features:

The TL3M provides the following additional bus features:

- SDH/SONET interface Drop bus

- Input parity check with alarm monitoring

- Odd parity

- Bus signals

- Input loss of clock detection

- Stuck high or low

- Loss of J1 reference

Downloaded from Elcodis.com electronic components distributor

- Positive/negative justification count for J1 pulse

- External path AIS and other alarm (e.g., LOP) indication

- SDH/SONET interface Add bus

- Output parity generation

- Odd parity

- Bus indication (active low to indicate bus activity)

- Ability to High-Z the output bus signals

- Under processor control

- Input loss of clock detection

- Stuck high or low

## **SDH/SONET** Processing Features

- In-band upstream path AIS detection

- TOH E1 bytes

- Majority vote

- TUG-3 pointer tracking

- ETSI-based state machine

- 8-bit PJ and NJ counters

- NDF, LOP, and AIS alarm detection

- TUG-3 pointer generation

- Slaved to drop or Add bus J1 pulse

- Adjusts pointer accordingly

- POH byte processing (TUG-3, STS-1)

- All receive POH bytes accessible

- Microprocessor access

- POH interface

- J1 byte

- 64-byte host processor read

- B3 parity error check

- Bit or block count

- G1 byte

- Single-bit RDI alarm detection with a 5 or 10 event option

- REI (FEBE) counter (16 bits)

- C2 byte

- Signal label mismatch and unequipped detection

- POH byte Insertion (TUG-3, STS-1)

- All POH bytes

- Microprocessor access

- POH interface

- Control bits to determine source of input bytes

- J1 byte

- 64-byte message

# DATA SHEET

- G1 byte

- Receive side or alarm indication port

- REI (FEBE) insertion from B3 byte errors

- Single-bit RDI insertion

- C2 byte

- Path label insertion

- SDH/SONET AIS generation

- TUG-3s

- Unequipped channel generation

- TUG-3s

- Desynchronizer

- · Meets ITU, ETSI, and ANSI performance requirements

- Pointer test sequence

- Jitter

- Internal

- Digital

- Internal pointer leak algorithm or microprocessor control

#### **O-Bit (Overhead Communications) Channel Access:**

- Microprocessor access (two-bit field)

- Option for two reserved bits in the E3 format

- External serial bit interface (clock and data)

- Gapped clock

- Asynchronous

#### Line AIS Detection:

• Transmit E3 AIS detection per ITU G.775

#### Line AIS Generation:

- Transmit and receive sides

- · Generate as a result SDH/SONET alarms or line level alarms

- Mask enable bits

- Global enable bit

- Microprocessor control

#### Line Interface:

- Rail interface

- Clock, positive and negative rail signals

- DS3/E3 loss of signal detection in transmit direction

- BPV counter

- DS3 B3ZS or E3 HDB3 codec function

- Loss of clock detector

- Invert clock polarity (receive and transmit)

- NRZ interface

- Clock and data

- Loss of Clock Detector

- External interface for loss of signal (transmit direction)

- Invert clock polarity (receive and transmit)

- High-Z output leads

- Receive Line Outputs

- Transmit Monitor Outputs

- Per channel control via host

- Transmit Monitor Port

- Clock and data

# **Test Features:**

- Boundary Scan that meets IEEE 1149.1 standard

- High-Z all output leads option

- Loopbacks per channel

- DS3/E3 line with generate receive AIS output option

- DS3/E3 facility

- Pseudo-random test generator and analyzer per channel

- 2<sup>15</sup>-1, or 2<sup>23</sup>-1

- Uses CV counter to count errors

- B3 BIP-8 error mask

- RAM value substituted

- Column error control

## Microprocessor Interface:

- Microprocessor

- Split address/data buses

- Selectable Intel or Motorola

## Alarms And Interrupts:

- Hardware interrupt option

- Mask bits

- Positive level

- Software polling bit

- Latched and unlatched alarms

- Saturating or rollover counters option

## **Device Driver:**

- Device configuration

- Fault monitoring

- Performance monitoring

Proprietary TranSwitch Corporation Information for use Solely by its Customers

TL3M TXC-03453B

DATA SHEET

# **APPLICATION EXAMPLES**

The TL3M can be used in a wide range of telecommunications applications, such as:

- Add/drop multiplexers

- Digital cross connect systems

- Router systems

- Transmission systems

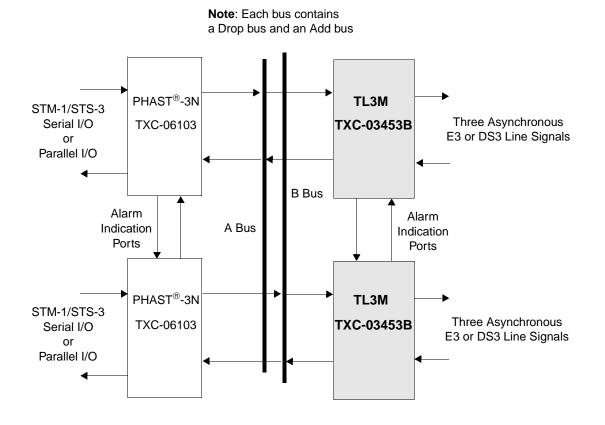

Figure 1. Typical Application using the TL3M and PHAST-3N Devices

Figure 1 shows a Telecom Bus bidirectional E3/DS3 add/drop STM-1/STS-3 multiplexer. The three E3's or DS3's may be dropped from either direction with full time slot reuse in both directions. If required, the asynchronous line interfaces for the two TL3M devices may be tied together. An option is provided in which the output line interface can be forced to the high impedance state.

# TXC-03453B

TL3M

# **BLOCK DIAGRAM**

WITCH

TRAF

#### SDH/SONET SIDE

DATA SHEET

# **BLOCK DIAGRAM DESCRIPTION**

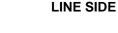

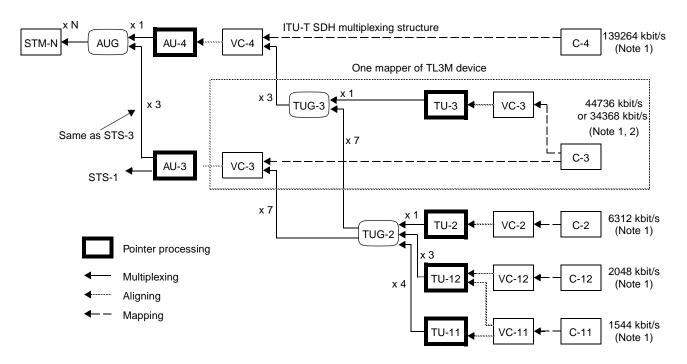

A functional block diagram of the TL3M is shown in Figure 2. The portion of the ITU-T SDH multiplexing structure implemented by each Level 3 Mapper within the TL3M device is shown in Figure 3. Each of the three Level 3 mappers is multiplexed/demultiplexed from a SDH/SONET Telecom Bus interface which is carrying the three STS-3 STS-1s or STM-1 VC-4 TUG-3s.

Note 1: G.702 tributaries associated with containers C-x are shown. Other signals (e.g., ATM) can also be accommodated. Note 2: AU-3/VC-3 is for DS3 only.

#### Figure 3. TL3M Multiplexing Structure

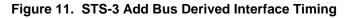

In the receive direction the drop side parallel Telecom Bus interface uses a bus signaling rate of 19.44 MHz. The parallel interface at the drop block consists of byte-wide input data (DD(7-0)), a C1J1 input indication (DC1J1), an SPE input indication (DSPE), input clock (DCLK), and input parity (DPAR). The C1 (J0) pulse, which is required, is used in conjunction with an active low SPE indication to determine the start of the SDH/ SONET frame. The J1 pulse (in the DC1J1 signal) and an active high SPE indication determine the starting location of the VC-4 within the STM-1 format and also the start of each of the STS-1s in the STS-3 format. There are three J1 pulses required for the STS-3 format, and a single J1 pulse required for the STM-1 VC-4 format. The Drop bus clock (DCLK) is also monitored for a stuck high or low state. The data leads and other bus leads are calculated for odd parity and compared against the incoming input parity lead (DPAR) to determine if there is a parity error. Other than a parity error indication, no action is taken by the TL3M. The C1J1 pulse is also monitored for a loss of J1 pulse. An option is provided in which the C1 pulse can be supplied on a separate lead from the DC1J1 lead (DC1 lead).

The Decode block contains the logic for performing the pointer interpretation and tracking for each of the three TUG-3s, when the STM-1 VC-4 format is selected. The H1/H2 pointer bytes in each of the TUG-3s are monitored for loss of pointer, AIS, and a New Data Flag (NDF) indication. The pointer state machines are implemented using the algorithms specified in ETSI and ANSI documents. Performance counters are provided for justification events. The TL3M does not perform pointer tracking for the STS-1 signals, or for the VC-4 formats. Instead, the J1 indication is used as the start of format indication.

This block also performs SDH/SONET E1 byte AIS detection, which may be carrying an upstream in-band AIS indication. The TranSwitch PHAST-3N and SOT-3 devices have an option to generate an in-band line/path AIS indication for the downstream mappers, such as the TL3M, which enables line AIS to be generated without having to perform an additional pointer AIS detection. In addition, two leads are provided for an out-of-band upstream AIS indication, using either the PAISn or ISTAn leads.

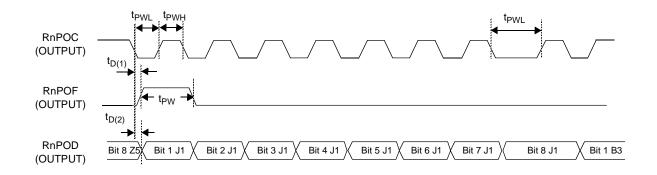

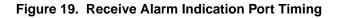

The POH bytes from the TUG-3 or the STS-1 format are provided at the POH Interface block for external processing, if required. Each of the three mappers' POH interfaces consists of an output data lead (RnPOD), framing pulse (RnPOF) and a clock signal (RnPOC), where n represents each of three level 3 mappers, starting with channel 1. All the POH bytes in each of the STS-1s and TUG-3s are supplied, including the B3 byte.

All POH bytes from each of the TUG-3s or STS-1s are also written into Internal RAM block segments for microprocessor access. In addition, the J1 byte is written into a 64-byte RAM segment on an arbitrary address rotating basis. Each mapper section also performs POH byte processing, which includes RDI detection, C2 mismatch detection and unequipped detection.

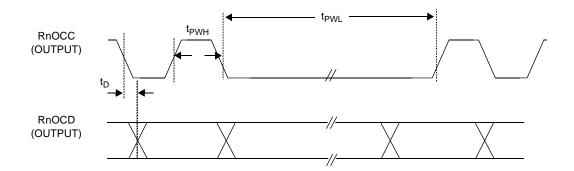

The received O-bits for the DS-3 format are provided at the O-Bit Interface block and are also written into a 2-bit RAM location for microprocessor access. Two reserved bits in the E3 format have been designated as an O-bit channel, if required. The bits in the RAM location are updated each frame by the TL3M. There is no synchronous relationship between the SDH/SONET frame and the bits written into these RAM locations. The external interface consists of a serial data lead (RnOCD) and a clock lead (RnOCC).

An Alarm Indication Port block is provided for ring configurations. The alarm indication port consists of a data lead (RnAID), which is used with the corresponding POH interface framing pulse (RnPOF) and clock signal (RnPOC). The information on the data lead consists of the REI count and the path RDI alarm summary status. In a ring configuration, this information is inserted from the mate TL3M mapper channel into the local TL3M mapper channel G1 byte for transmission.

The Destuff block works in conjunction with the Desync block to remove the stuff columns in the payloads, and also performs the majority logic voting for the DS3 and E3 formats. The majority voting logic uses the justification control bits to determine if the S-bit (or bits) is carrying a stuffing state or data.

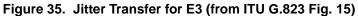

The Desync block, using a digital desynchronizer, is responsible for removing the effects on the output of the DS3 or E3 signals of systemic jitter due to signal mapping and pointer movements. Each of the three desyncronizers has a built-in TranSwitch proprietary pointer leak algorithm, which is transparent to the user. An option is provided in which the pointer leak rate can be programmed by the host processor. The output has an average frequency equal to the source frequency and has jitter characteristics that meet both ITU and ANSI standards.

A line DS3/E3 AIS generator is provided, which enables line AIS to be generated for the various upstream alarms, such as loss of pointer. A control bit is also provided which enables the microprocessor to send line AIS independent of the alarm states. An option is provided which enables line AIS to be generated when a channel is placed in line loopback.

The Output block provides either a positive (RPOSn) and negative (RNEGn) rail line signal, or an NRZ line signal (RPOSn), and a clock signal (RCLKn). The receive E3 HDB3 and DS3 B3ZS coder operates independent of the transmitter side. A control bit is provided for inverting the clock output, if required. Also provided is a control bit which enables the receive data and clock leads to be forced to a high impedance state, independent of interface type (rail or NRZ) selected. This permits two interfaces from two different devices to be tied together for ring configurations.

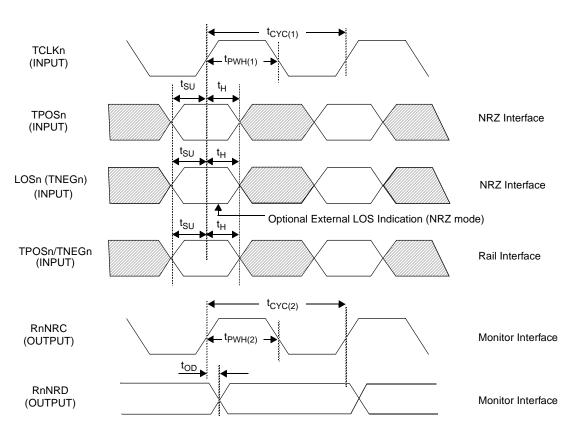

In the transmit direction (towards the Add bus), the Input block supports either a positive (TPOSn) and negative (TNEGn) rail line signal, or an NRZ line signal (TPOSn), and a clock signal (TCLKn). A control bit enables the transmit input clock to be inverted. The Input block performs either the E3 HDB3 or DS3 B3ZS decoder function. Bipolar violations are counted in a 16-bit counter. A choice of bipolar violation sequence detection is also provided. The rail interface also detects an E3 or DS3 loss of signal. The input clock is also monitored for a stuck high or low condition. When the NRZ interface is selected, the unused negative rail input lead can be used to clock in an external loss of signal (LOS) indication from a downstream codec.

DATA SHEET

Control bits are provided which enable line AIS to be sent when either a loss of signal or input clock failure is detected. A control bit also enables the microprocessor to send line AIS, independent of alarms. Separate NRZ data (RnNRD) and clock (RnNRC) output signals are also provided which may be used for monitoring.

The line signal is connected to the Stuff/Sync block. This block basically consists of a FIFO into which the data is written from the line and is read out by a SDH/SONET clock which is either derived from the Add bus (i.e., Add bus timing), or from the Drop bus (i.e., Drop bus timing). The stuffing algorithm for the DS3 signal uses one set of five control bits (C-bits) with one stuffing opportunity bit (S-bit) for frequency justification per subframe (nine subframes). The E3 format uses five pairs of control bits (C1 and C2 bits) to control two stuff opportunity bits (S1 and S2) per subframe (one subframe per three rows for a total of three subframes per frame). FIFO underflow and overflow alarm indications are provided. Should an underflow or overflow condition occur, the FIFO will immediately reset to a preset value. The FIFO also tracks an incoming line signal having an average frequency deviation as high as ± 20 ppm, and can simultaneously accept the signal with up to 5 UI peak-topeak jitter (where 1 UI = 1/f).

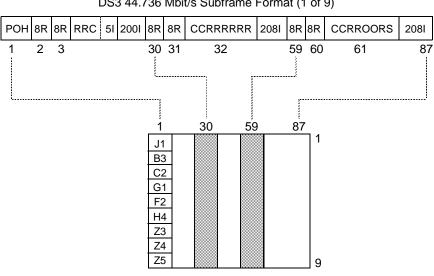

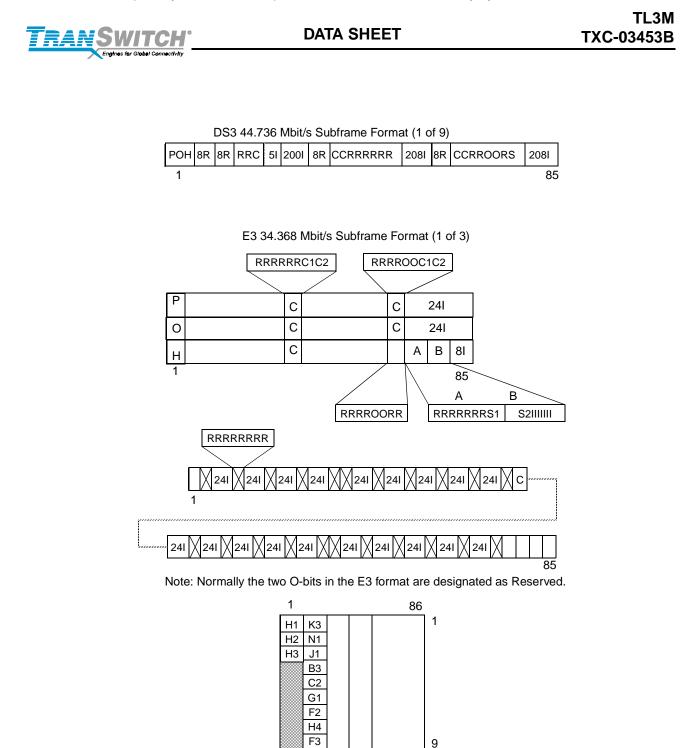

The Build block formats the data bits into either a SONET STS-3 STS-1 SPE format (see Figure 4) or an STM-1 VC-4 TUG-3 format (see Figure 5). The STS-1 format has two stuff columns and payload plus a column of POH bytes, while the TUG-3 format consists of the payload, plus a column of POH bytes and H1/H2 pointer bytes. The TUG-3 pointer bytes define the start of the J1 POH byte within the TUG-3. A fixed pointer value of 6800 hex is used as the initial value when building a TUG-3 format. There are two levels of pointer movements in the TUG-3 build process. In either drop or add timing, the transmit pointer value will increment or decrement when there is an STM-1 VC-4 increment or decrement based on the relative position of the J1 pulse in the C1J1. The pointer movement for the TUG-3s will be in the opposite direction. This feature can be disabled.

DS3 44.736 Mbit/s Subframe Format (1 of 9)

AU-3/STS-1 SPE Format (87 x 9)

#### Figure 4. SONET AU-3/STS-1 SPE Build Format

TUG-3 Format (86 x 9)

Figure 5. ITU-T TUG-3 Build Format

DATA SHEET

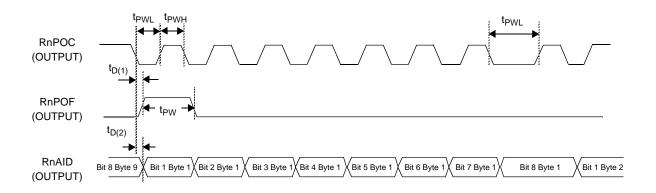

An O-bit interface value or a value written into RAM by the microprocessor is mapped into the two O-bit positions in the DS3 format. The O-bit interface consists of an output clock signal (TnOCC) and an input data lead (TnOCD). The relationship between the O-bit channel and the SDH/SONET frame in both directions is asynchronous.

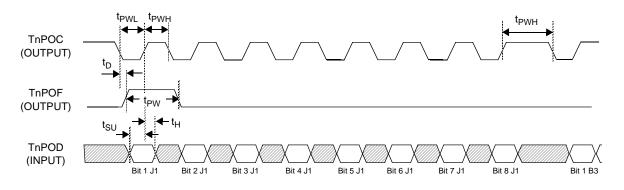

The nine individual POH bytes (except the B3 byte) can be inserted into the TUG-3 or STS-1 POH bytes from values written to RAM by the microprocessor or from the transmit POH interface. The POH interface consists of an input data lead (TnPOD), output framing pulse (TnPOF), and an output clock signal (TnPOC), where n represents each of three level 3 mappers. A control bit enables the POH interface bytes to be written into RAM for microprocessor access when transmitted. In the case of the G1 byte, the value can also be inserted from the local receive side or from the alarm indication port. A test mask is provided for the calculated B3 byte, which permits up to eight errors to be transmitted.

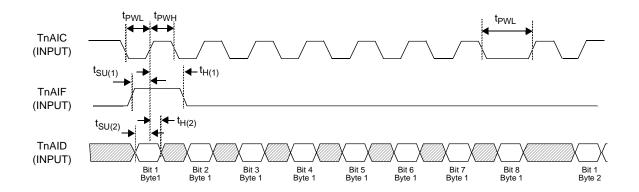

For ring operation, an alarm indication port is provided in the AIP block. The alarm indication port consists of an input data lead (TnAID), input framing pulse (TnAIF), and input clock signal (TnAIC). The information on the data lead consists of the REI count, and the path RDI alarm summary status. In ring operation, this information is inserted into the G1 byte for transmission.

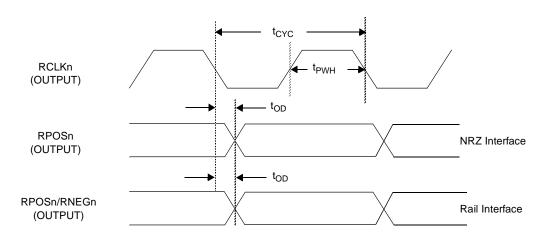

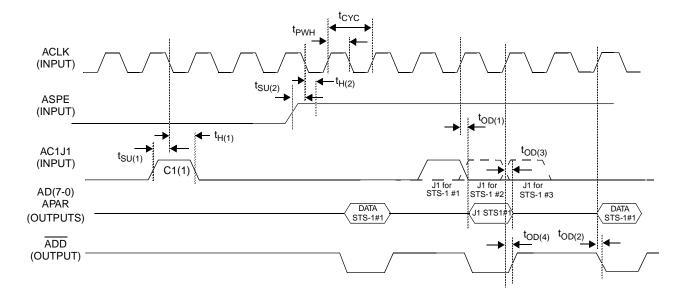

The Add block uses either the add or drop timing signals. Add bus timing is enabled by placing a high on control lead ABTIM. When Add bus timing is selected, the timing for the two buses, add and drop, is supplied by separate inputs for add and drop. When Add bus timing is selected, the output Add bus signals consist of bytewide data (AD(7-0)), add indication (ADD), and odd parity (APAR). The Add bus input timing signals consist of a 19.44 MHz clock (ACLK), C1J1 indication (AJ1C1) and a <u>SPE</u> active indication (ASPE). The output Add bus signals consist of byte-wide data (AD(7-0)), add indication (ADD), and odd parity (APAR). The active low add indication (ADD) indicates the location of all time slots being added to the Add bus. The Add bus clock is also monitored for a stuck high or low state when Add bus timing is selected. A bus contention alarm is provided if more than one channel is assigned to the same TUG-3 or STS-1.

Drop bus timing is enabled by placing a low on control lead ABTIM. When Drop bus timing is selected, the timing for the Add bus depends upon the Drop bus input signals for operation. When Drop bus timing is selected, the output Add bus signals consist of byte-wide data (AD(7-0)), add indication (ADD), and odd parity (APAR).

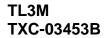

All of the control registers and performance counters, as well as the status and alarm indications, are accessible via a microprocessor interface. The TL3M supports either Intel or Motorola microprocessor bus interfaces, with hardware and software interrupts. Mask bits are provided for the latched status and alarm indications, to control whether each of them will generate an interrupt when active. The counters may be configured as either rollover or saturating. Saturating counters are cleared automatically when they are read.

For board testing, boundary scan and the ability to force all the output signals to a high impedance state are provided. For network and device debugging, facility and line loopbacks are provided at the line interfaces. Each channel also has a PRBS test analyzer and generator (not shown in Figure 2).

# LEAD DIAGRAM

|    |                       |              |            |            |            |            |            |            | B          | DT.         | то         | M١         | /IE        | W          |            |             |            |             |             |            |             |            |

|----|-----------------------|--------------|------------|------------|------------|------------|------------|------------|------------|-------------|------------|------------|------------|------------|------------|-------------|------------|-------------|-------------|------------|-------------|------------|

| AB | GND                   | SUB          |            |            | D4         | D7         |            |            | GND        | GND         | A3         | A4         | A8         |            |            | ISTA3       |            | TMS         | тсікз       |            | R3NRC       | GND        |

| AA | SUBS2                 | VDS2         | TSE1       | TSE2       |            | D5         | SEL        |            | EAISC      | DAISC       | A2         | A5         | A9         | PAIS1      | PAIS2      | PAIS3       | тск        | TDO         | DF3E        | R3NRD      |             | VDD3       |

| Y  | VSS2                  | VRS2         |            | ADD        | TSE3       |            | D6         | RDY        | мото       | GND         | A1         | A6         | таска      | NC         | NC         |             |            | TPOS3       |             | VDD3       | VSD3        | DF3B       |

| w  | VDS2                  | GRS2         | VSS2       | VDD        | NC         | ŴR         | VDDC       | VDD        |            |             | VDDC       | VDD        | Ă7         | NC         | VDDC       | VDD         | NC         | NC          | VDD         | RPOS3      | VDD3        | DF3A       |

| v  | VDS2                  | VSS2         | SBS2       | NC         | 0          |            | -          | -          | 0          | 0           | -          | •          | 0          | 0          | -          | -           | 0          | 0           | ŇC          | VSD3       | VSD3        | VRD3       |

| U  | TSCK                  | 2 NC         | VSS2       | ŇČ         |            |            |            |            |            |             |            |            |            |            |            |             |            |             | ŇĊ          | DBS3       | SUBD3       | $\bigcirc$ |

| т  |                       |              | $\bigcirc$ | VDD        |            |            |            |            |            |             |            |            |            |            |            |             |            |             | VDDC        | VSD3       |             | VSD2       |

| R  | TMOD                  | $\bigcirc$   | NC         | VDDC       | ;          |            |            |            |            |             |            |            |            |            |            |             |            |             | VDD         | VSD2       | DF2B        | DF2A       |

| Ρ  | ACLK                  | ADD<br>AC1J1 |            |            |            |            |            |            | GND<br>GND | GND<br>GND  | GND<br>GND | GND<br>GND | GND<br>GND | GND<br>GND |            |             |            |             |             | GRD2       | VSD2        | VDD2       |

| Ν  |                       | ACTJ1        |            |            |            |            |            |            |            |             |            |            |            |            |            |             |            |             | $\otimes$   |            | $\bigcirc$  | DF1A       |

| М  | AD4                   | AD5          | AD6        | VDDC       |            |            |            |            |            |             |            |            |            |            |            |             |            |             |             | GRD1       | DBS1        | O<br>DF1B  |

| L  | AD7                   |              |            | NC ND DD C |            |            |            |            |            |             |            |            |            |            |            |             |            |             | VDD<br>VSD1 |            | VSD1        | SUBD1      |

| к  |                       | $\bigcirc$   | DC1J1      | $\bigcirc$ |            |            |            |            |            |             |            | GND        | GND        |            |            |             |            |             | $\bigcirc$  | •          | VSD1        | $\bigcirc$ |

| J  |                       |              | O<br>DD1   |            |            |            |            |            | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | ٢          | $\bigcirc$ | $\bigcirc$ |            |             |            |             | $\otimes$   | $\bigcirc$ | TPOS2       |            |

| н  | O<br>DD3              | O<br>DD4     | O<br>DD5   | VDDC       | ;          |            |            |            |            |             |            |            |            |            |            |             |            |             | VDD         | C<br>RPOS2 | CLK2        | R2NRD      |

| G  | DD7                   | O<br>VSS1    | O<br>VRS1  | NC         |            |            |            |            |            |             |            |            |            |            |            |             |            |             | R2NRC       |            |             | O<br>RNEG2 |

| F  | SUBS                  | I GRS1       | O<br>VSS1  |            |            |            |            |            |            |             |            |            |            |            |            |             |            |             |             |            |             |            |

| Е  | SBS1                  | O<br>VDS1    | DD6        |            | NC         | NC         | VDD        | VDDC       | NC         | NC          | VDD        | VDDC       | NC         | NC         | VDD        | VDDC        | NC         | EXDCK       |             |            | ()<br>RPOS1 |            |

| D  | VDS1                  | VSS1         | UDS1       | NC         | R10CC      |            | DR2AID     | R2POD      | R3AID      | R3POO       | T1AIC      | TIOCD      |            |            | T2POD      | T3AID       |            | С ТЗРОС     | NC          |            |             |            |

| С  | VSS1                  | NC NC        | S2         |            | R1POC      |            | R2OCD      |            | R3OCC      | R3POE       |            |            | U<br>T1POC | C<br>T2AIC | C<br>T2OCC | ()<br>T2POC |            | ()<br>T30CC |             |            |             |            |

| В  | GND                   | R1AID        | S1         | R10CE      |            |            |            |            | R3OCD      | C)<br>R3POF |            |            | U<br>T1POD |            |            | U<br>T2OCD  | U<br>T2POF | T3AIC       | U<br>T3OCE  |            |             |            |

| A  | <ul> <li>.</li> </ul> | $\bigcirc$   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$  | $\bigcirc$ | $\bigcirc$  | $\bigcirc$  | $\bigcirc$ | $\bigcirc$  | <b>()</b>  |

|    | 1                     | 2            | 3          | 4          | 5          | 6          | 7          | 8          | 9          | 10          | 11         | 12         | 13         | 14         | 15         | 16          | 17         | 18          | 19          | 20         | 21          | 22         |

#### Notes:

- 1. This is the bottom view. The leads are solder balls. See Figure 38 for package information. This view is rotated relative to the bottom view in Figure 38.

- 2. Lead symbols are described in the "Lead Descriptions" section.

- 3. Power supply leads are shown as solid black circles, ground leads as cross-hatched circles.

#### Figure 6. TL3M TXC-03453B Lead Diagram

# DATA SHEET

# LEAD DESCRIPTIONS

#### POWER SUPPLY, GROUND AND NO CONNECTS

| Symbol | Lead No.                                                                                                                                                                                        | I/O/P* | Name/Function                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDC   | D8, D12, D16, G4, H19, L4,<br>M19, R4, T19, W7, W11,<br>W15                                                                                                                                     | Ρ      | Core VDD: +3.3 volts, $\pm$ 5% power supply                                                                                                                                                                   |

| VDD    | D4, D7, D11, D15, D19,<br>G19, H4, L19, M4, R19, T4,<br>W4, W8, W12, W16, W19                                                                                                                   |        | <b>VDD:</b> +3.3 volts, $\pm$ 5% power supply                                                                                                                                                                 |

| VDS1   | C1, C3, D2                                                                                                                                                                                      | Р      | <b>VDD Analog:</b> +3.3 volts, $\pm$ 5% power supply                                                                                                                                                          |

| VDS2   | V1, W1, AA2                                                                                                                                                                                     | Р      | <b>VDD Analog:</b> +3.3 volts, $\pm$ 5% power supply                                                                                                                                                          |

| VDD1   | J22, K20, M20                                                                                                                                                                                   | Р      | <b>VDD Analog:</b> +3.3 volts, $\pm$ 5% power supply                                                                                                                                                          |

| VDD2   | P20, P22, T21                                                                                                                                                                                   | Р      | VDD Analog: +3.3 volts, ± 5% power supply                                                                                                                                                                     |

| VDD3   | W21, Y20, AA22                                                                                                                                                                                  | Р      | VDD Analog: +3.3 volts, ± 5% power supply                                                                                                                                                                     |

| GND    | J9 - J14<br>K9 - K14<br>L9 - L14<br>M9-M14<br>N9 - N14<br>P9 - P14                                                                                                                              | Ρ      | Core Ground: 0 volts reference                                                                                                                                                                                |

| GND    | A1, Y10, A22, AB1, AB9,<br>AB10, AB22                                                                                                                                                           |        | Ground: 0 volts reference                                                                                                                                                                                     |

| VSS1   | B1, C2, E3, F2                                                                                                                                                                                  | Р      | VSS (Analog Ground): 0 volts reference                                                                                                                                                                        |

| VSS2   | U3, V2, W3, Y1                                                                                                                                                                                  | Р      | VSS (Analog Ground): 0 volts reference                                                                                                                                                                        |

| VSD1   | J19, J21 K19, K21                                                                                                                                                                               | Р      | VSS (Analog Ground): 0 volts reference                                                                                                                                                                        |

| VSD2   | N19, P21, R20, T22                                                                                                                                                                              | Р      | VSS (Analog Ground): 0 volts reference                                                                                                                                                                        |

| VSD3   | T20, V20, V21, Y21                                                                                                                                                                              | Р      | VSS (Analog Ground): 0 volts reference                                                                                                                                                                        |

| NC     | A8, A12, B2, B6, B17, B22,<br>C4, C19, C21, D5, D6, D9,<br>D10, D13, D14, D17, D20,<br>D22, E4, E19, F4, J4, K4,<br>N4, P3, R2, R3, T3, U2, U4,<br>U19, V4, V19, W5, W14,<br>W17, W18, Y14, Y15 |        | <b>No Connect:</b> NC leads are not to be connected, not even<br>to another NC lead, but must instead be left floating.<br>Connection of these leads may impair performance or<br>cause damage to the device. |

\* Note: I = Input; O = Output; P = Power; T = Tristate:

# DROP BUS INTERFACE

| Symbol  | Lead No.                          | I/O/P | Туре* | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DD(7-0) | F1, D3, G3, G2,<br>G1, H1, H3, H2 | I     | LVTTL | <b>Drop Bus Data Byte:</b> 19.44 Mbyte/s byte-wide data that corresponds to the STM-1 or STS-3 signal from the Drop bus. Lead F1 is DD7. Data that may be present on the bus, other than the TUG-3s, or the STS-3 STS-1 SPEs, is ignored.                                                                                                                                                                                                                                            |

| DCLK    | КЗ                                | Ι     | LVTTL | <b>Drop Bus Clock:</b> This clock operates at a 19.44 MHz rate. Drop bus byte-wide data (DD(7-0)), parity (DPAR), payload indicator (DSPE), and C1/J1 (DC1J1 and DC1) are clocked in on falling edges of this clock.                                                                                                                                                                                                                                                                 |

|         |                                   |       |       | This signal will provide timing for the add direction when<br>the Drop bus timing mode is selected (lead ABTIM is<br>low).                                                                                                                                                                                                                                                                                                                                                           |

| DC1     | К2                                | I     | LVTTL | <b>Drop C1 Pulse:</b> External positive C1 pulse that may be provided on this lead instead of in the DC1J1 signal. This signal is internally or-gated with the DC1J1 signal to form a composite C1J1 signal. If this lead is not used it must be grounded.                                                                                                                                                                                                                           |

|         |                                   |       |       | This signal will provide timing for the add direction when<br>the Drop bus timing mode is selected (lead ABTIM is<br>low).                                                                                                                                                                                                                                                                                                                                                           |

| DC1J1   | J3                                | Ι     | LVTTL | <b>Drop Bus C1 and J1 Indicator:</b> The C1 pulse is an active high, one clock cycle-wide (DCLK) timing pulse that indicates the location of the first C1 (J0) time slot in the STM-1 or STS-3 frame. If the C1 pulse is not present in this signal, it must be provided at the DC1 lead. One or three J1 pulses, also one clock cycle wide, identify the starting location of the J1 byte in the VC-4 format or the starting locations of the J1 bytes in each of the three STS-1s. |

|         |                                   |       |       | This signal will provide timing for the add direction when<br>the Drop bus timing mode is selected (lead ABTIM is<br>low).                                                                                                                                                                                                                                                                                                                                                           |

| DSPE    | J2                                | I     | LVTTL | <b>Drop Bus SPE Indicator:</b> A signal that is active high during the STM-1 VC-4 format, and for each of the STS-3 STS-1 SPE periods. It is active low during the STS-3 TOH and STM-1 RSOH/MSOH byte times.                                                                                                                                                                                                                                                                         |

|         |                                   |       |       | This signal will provide timing for the add direction when<br>the Drop bus timing mode is selected (lead ABTIM is<br>low).                                                                                                                                                                                                                                                                                                                                                           |

| DPAR    | J1                                | Ι     | LVTTL | <b>Drop Bus Parity Bit:</b> Odd parity input for the data byte, the DSPE signal, and the composite DC1J1 pulse.                                                                                                                                                                                                                                                                                                                                                                      |

\* Note: See the "Input, Output and Input/Output Parameters" section for Type definitions.

DATA SHEET

#### ADD BUS INTERFACE

| Symbol  | Lead No.                          | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-----------------------------------|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD(7-0) | K1, L3, L2, L1,<br>M1, M3, M2, N1 | O(T)  | LVCMOS<br>4mA | <ul> <li>Add Bus Data Byte: 19.44 Mbytes/s byte-wide data that corresponds to the time slots that are placed on the Add bus by the TL3M. Lead K1 is AD7. The first bit transmitted (MSB) corresponds to bit 7. These leads are forced to a high impedance state when: <ul> <li>Data is not present</li> <li>Hardware or software reset occurs</li> <li>Drop Bus Loss Of Clock (DLOC) occurs when the Drop bus timing mode is selected (ABTIM lead is low)</li> <li>When control bit ADDEN (bit 1 in 0C2H) is set to 0.</li> </ul> </li> </ul>                                                                                                                    |

| ACLK    | P1                                | Ι     | LVTTL         | Add Bus Clock: This input clock operates at 19.44 MHz.<br>The add clock is used when the Add bus timing mode is<br>selected (ABTIM lead is high). Add bus byte-wide data<br>(AD(7-0)), the ASPE signal, and the AC1J1 signal are<br>clocked in on its falling edges. The parity (APAR) signal,<br>and add indicator (ADD) are clocked out on its rising<br>edges. This lead is disabled, and should be grounded,<br>when the drop timing mode is selected (ABTIM lead is<br>low).                                                                                                                                                                                |

| ASPE    | N3                                | Ι     | LVTTL         | Add Bus SPE Indicator: An input signal that must be<br>high to indicate the STM-1 VC-4 period, and each of the<br>three STS-3/STS-1 SPE periods, when Add bus timing is<br>selected. This lead is disabled, and should be grounded,<br>when the drop timing mode is selected (ABTIM lead is<br>low).                                                                                                                                                                                                                                                                                                                                                             |

| AC1J1   | N2                                | Ι     | LVTTL         | Add Bus C1 and J1 Indicator: The C1 pulse is an active<br>high, one clock cycle-wide (ACLK) input timing pulse that<br>identifies the location of the first C1 (J0) time slot in the<br>STM-1 or STS-3 frame. A single J1 pulse, also one clock<br>cycle wide, identifies the starting location of the J1 byte in<br>the STM-1 VC-4 signal. Three J1 pulses are used to<br>identify the starting location of the J1 bytes in each of the<br>three STS-3 STS-1 SPEs. This lead will carry only J1<br>pulse information when the DC1 lead is used. This lead is<br>disabled, and should be grounded, when the drop timing<br>mode is selected (ABTIM lead is low). |

| ADD     | P2                                | 0     | LVCMOS<br>4mA | <ul> <li>Add Indicator: An active low signal that identifies the position of the TUG-3 and STS-1 bytes that are being mapped to the Add bus. This signal will be high when</li> <li>Data is not present</li> <li>Hardware or software reset occurs</li> <li>Drop Bus Loss Of Clock (DLOC) occurs when the Drop bus timing mode is selected (ABTIM lead is low)</li> <li>When control bit ADDEN (bit 1 in 0C2H) is set to 0.</li> </ul>                                                                                                                                                                                                                           |

| Symbol | Lead No. | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APAR   | P4       | O(T)  | LVCMOS<br>4mA | <ul> <li>Add Bus Parity Bit: This output bit represents an odd parity calculation for each data byte that is mapped to the Add bus in the add timing and Drop bus timing modes. This lead is forced to a high impedance state when</li> <li>Data is not present</li> <li>Hardware or software reset occurs</li> <li>Drop Bus Loss Of Clock (DLOC) occurs when the Drop bus timing mode is selected (ABTIM lead is low)</li> <li>When control bit ADDEN (bit 1 in 0C2H) is set to 0.</li> </ul> |

#### LINE INTERFACE

Where n represents the channel (mapper) number, for channels 1 through 3.

| Symbol                  | Lead No.           | I/O/P* | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|--------------------|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOS1<br>RPOS2<br>RPOS3 | D21<br>G20<br>W20  | O (T)  | LVCMOS<br>4mA | Receive Line Positive Rail/NRZ Data for Channel n:<br>When control bit CODE (bit 6 in XC1H) is a 0 for the cor-<br>responding channel, this lead provides the received NRZ<br>output for the 44.736 (DS3) or 34.368 Mbit/s (E3) asyn-<br>chronous line data. When control bit CODE is a 1, a pos-<br>itive rail output signal is provided. This lead is forced to a<br>high impedance state when<br>- Control bit L3EN (bit 0 in 0C2H) is set to 0<br>- Control bit L3OEN (bit 0 in XC2H) is set to 0 for the<br>corresponding channel<br>- Hardware reset (lead RESET) or software reset<br>(RESETS, bit 0 in 0C7H) occurs<br>- RESETn (bits 1-3 in 0C7H) is set to 1 for the corre-<br>sponding channel. |

| RNEG1<br>RNEG2<br>RNEG3 | E20<br>F22<br>AA21 | O (T)  | LVCMOS<br>4mA | <ul> <li>Receive Negative Rail Data for Channel n: When control bit CODE (bit 6 in XC1H) is a 0, the corresponding lead is set to low. When control bit CODE is a 1, a negative rail output is provided. This lead is forced to a high impedance state when</li> <li>Control bit L3EN (bit 0 in 0C2H) is set to 0</li> <li>Control bit L3OEN (bit 0 in XC2H) is set to 0 for the corresponding channel</li> <li>Hardware reset (lead RESET) or software reset (RESETS, bit 0 in 0C7H) occurs</li> <li>RESETn (bits 1-3 in 0C7H) is set to 1 for the corresponding channel.</li> </ul>                                                                                                                      |

DATA SHEET

| Symbol                                             | Lead No.           | I/O/P* | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------|--------------------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK1<br>RCLK2<br>RCLK3                            | C22<br>G21<br>Y19  | O (T)  | LVCMOS<br>4mA | <ul> <li>Receive Line Clock for Channel n: The 44.736 or<br/>34.368 Mbit/s line signals on the RPOSn/RNEGn signal<br/>leads are clocked out on falling edges of this clock when<br/>control bit INVCO (bit 4 in XC1H) is set to 0 for the corre-<br/>sponding channel. These signals are clocked out on ris-<br/>ing edges when control bit INVCO is set to 1.</li> <li>This lead is forced to a high impedance state when<br/>- Control bit L3EN (bit 0 in 0C2H) is set to 0</li> <li>Control bit L3OEN (bit 0 in XC2H) is set to 0 for the<br/>corresponding channel</li> <li>Hardware reset (lead RESET) or software reset<br/>(RESETS, bit 0 in 0C7H) occurs</li> <li>RESETn (bits 1-3 in 0C7H) is set to 1 for the corre-<br/>sponding channel.</li> </ul> |

| TPOS1<br>TPOS2<br>TPOS3                            | C20<br>H21<br>Y18  | I      | LVTTL         | <b>Transmit Line Positive Rail/NRZ Data: for Channel n.</b><br>When control bit DECODE (bit 7 in XC1H) is set to 0 for<br>the corresponding channel, this lead is used as the NRZ<br>input for the 44.736 (DS3) or 34.368 Mbit/s (E3) asyn-<br>chronous line signal. When control bit DECODE is a 1,<br>the corresponding lead provides the positive rail data<br>input for the internal decoder.                                                                                                                                                                                                                                                                                                                                                               |

| TNEG1/<br>LOS1<br>TNEG2/<br>LOS2<br>TNEG3/<br>LOS3 | E22<br>H22<br>AB20 | I      | LVTTL         | <b>Transmit Negative Rail Data or LOS Input:</b> When con-<br>trol bit DECODE (bit 7 in XC1H) is a 1, the corresponding<br>lead provides the negative rail data input for the internal<br>decoder. When control bit DECODE is set to 0 for the<br>corresponding channel, this lead can be used to input an<br>external loss of signal alarm. If a lead is not used, it must<br>be tied to ground.                                                                                                                                                                                                                                                                                                                                                               |

| TCLK1<br>TCLK2<br>TCLK3                            | F21<br>J20<br>AB19 | I      | LVTTL         | <b>Transmit Line Clock:</b> The NRZ or rail signal for a corresponding channel is clocked in on rising edges of this clock when control bit INVCI (bit 5 in XC1H) is set to 0. NRZ or rail data is clocked in on falling edges when control bit INVCI is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R1NRD<br>R2NRD<br>R3NRD                            | E21<br>G22<br>AA20 | O (T)  | LVCMOS<br>4mA | <ul> <li>Monitor Transmit Line Data: Output provided for an optional external performance monitoring circuit. This serial NRZ output is provided after the line decoder in the transmit direction, and is independent of whether the transmit line input is configured for a NRZ or rail interface. Data is clocked out on rising edges of clock (RnNRC). This lead is forced to a high impedance state when <ul> <li>Control bit L3EN (bit 0 in 0C2H) is set to 0</li> <li>Control bit L3OEN (bit 0 in XC2H) is set to 0 for the corresponding channel</li> <li>Hardware reset (lead RESET) or software reset (RESETS, bit 0 in 0C7H) occurs</li> <li>RESETn (bits 1-3 in 0C7H) is set to 1 for the corresponding channel.</li> </ul> </li> </ul>              |

| Symbol                  | Lead No.           | I/O/P* | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|--------------------|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1NRC<br>R2NRC<br>R3NRC | F20<br>F19<br>AB21 | O (T)  | LVCMOS<br>4mA | <ul> <li>Monitor Transmit Line Clock: Data (RnNRD) for the performance monitoring circuits is clocked out on rising edges of the corresponding clock. This lead is forced to a high impedance state when <ul> <li>Control bit L3EN (bit 0 in 0C2H) is set to 0</li> <li>Control bit L3OEN (bit 0 in XC2H) is set to 0 for the corresponding channel</li> <li>Hardware reset (lead RESET) or software reset (RESETS, bit 0 in 0C7H) occurs</li> <li>RESETn (bits 1-3 in 0C7H) is set to 1 for the corresponding channel.</li> </ul> </li> </ul> |

# OVERHEAD COMMUNICATIONS CHANNEL (O-BIT) INTERFACE

Where n represents the channel number, channels 1 through 3.

| Symbol                  | Lead No.          | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|-------------------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1OCD<br>R2OCD<br>R3OCD | A4<br>B7<br>A9    | 0     | LVCMOS<br>4mA | <b>Receive Overhead Communications Channel Data:</b><br>Unaligned data output for the overhead communications<br>channel (O-bits) defined in the DS3 format and two<br>reserved bits defined in the E3 format are provided. The<br>O-bits for channel n are clocked out on falling edges of<br>the RnOCC clock signal.                                                                                                                                                                     |

| R1OCC<br>R2OCC<br>R3OCC | C5<br>A6<br>B9    | 0     | LVCMOS<br>4mA | <b>Receive Overhead Communications Channel Clock:</b><br>A gapped 720 kHz output clock that has an average fre-<br>quency of 144 kHz, that is used for clocking out the<br>received overhead communications channel bits<br>(RnOCD) to external circuitry.                                                                                                                                                                                                                                 |

| T1OCD<br>T2OCD<br>T3OCD | C12<br>A16<br>A19 | Ι     | LVTTL         | <b>Transmit Overhead Communications Channel Data:</b><br>Data input for transmitting the overhead communications<br>channel in the DS3 format, and two defined reserved bits<br>in the E3 format. This input is enabled when a 1 is written<br>to control bit EXOO (bit 7 in XC4H) for the corresponding<br>channel. Data is clocked in on rising edges of the TnOCC<br>clock signal. The bits are transmitted unaligned regarding<br>bit position and subframe number within the payload. |

| T1OCC<br>T2OCC<br>T3OCC | B12<br>B15<br>B18 | 0     | LVCMOS<br>4mA | <b>Transmit Overhead Communications Channel Clock:</b><br>A gapped 720 kHz output clock that has an average fre-<br>quency of 144 kHz, which is used for clocking in the<br>transmit overhead communications channel bits<br>(TnOCD) from external circuitry when enabled.                                                                                                                                                                                                                 |

# DATA SHEET

## PATH OVERHEAD BYTE INTERFACE

Where n represents the channel number, channels 1 through 3.

| Symbol                  | Lead No.          | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                         |

|-------------------------|-------------------|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1POD<br>R2POD<br>R3POD | C6<br>C8<br>B10   | 0     | LVCMOS<br>4mA | <b>Receive Path Overhead Byte Data:</b> These leads provide a serial output for the nine path overhead bytes associated with each of the three TUG-3s or STS-1s. The nine POH bytes are clocked out on falling edges of the corresponding clock signal (RnPOC).                                                       |

| R1POF<br>R2POF<br>R3POF | A5<br>B8<br>A10   | 0     | LVCMOS<br>4mA | <b>Receive Path Overhead Byte Framing:</b> A positive one (RnPOC) clock cycle-wide output framing pulse that is synchronous to the J1 byte location in the receive path overhead data signal (RnPOD). This signal is also used as the framing pulse for the receive alarm indication port output data signal (RnAID). |

| R1POC<br>R2POC<br>R3POC | B5<br>A7<br>C10   | 0     | LVCMOS<br>4mA | <b>Receive Path Overhead Byte Clock:</b> A gapped clock<br>used for clocking out the receive path overhead bytes<br>(RnPOD), and receive alarm indication port data (RnAID)<br>for each channel.                                                                                                                      |

| T1POD<br>T2POD<br>T3POD | A13<br>C15<br>A20 | Ι     | LVTTL         | <b>Transmit Path Overhead Byte Data:</b> A serial input for the following path overhead bytes: J1, C2, G1, F2, H4, F3, K4, and N1 bytes. The POH bytes are clocked in on rising edges of the clock signal (TnPOC). The bit times corresponding to the B3 byte are ignored.                                            |

| T1POF<br>T2POF<br>T3POF | C13<br>A17<br>B20 | 0     | LVCMOS<br>4mA | <b>Transmit Path Overhead Byte Framing:</b> A positive one (TnPOC) clock cycle-wide output framing pulse that determines the start of the J1 byte in transmit path overhead byte data signal (TnPOD).                                                                                                                 |

| T1POC<br>T2POC<br>T3POC | B13<br>B16<br>C18 | 0     | LVCMOS<br>4mA | <b>Transmit Path Overhead Byte Clock:</b> A gapped output clock used for clocking in the transmit path overhead bytes from an external circuit.                                                                                                                                                                       |

# ALARM INDICATION PORT

Where n represents the channel number, channels 1 through 3

| Symbol                  | Lead No.          | I/O/P | Туре          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|-------------------|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|