# **ICs for Communications**

Sophisticated Answering Machine with Echo Cancellation SAM-EC

PSB 4860 Version 4.1

Data Sheet 2000-01-14

| PSB 4860                         |                                 |                                              |  |  |

|----------------------------------|---------------------------------|----------------------------------------------|--|--|

| Revision History:                |                                 | Current Version: 2000-01-14                  |  |  |

| Previous Version:                |                                 |                                              |  |  |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |  |

|                                  |                                 |                                              |  |  |

|                                  |                                 |                                              |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 2000-01-14 Published by Infineon Technologies AG, TR, Balanstraße 73, 81541 München © Infineon Technologies AG 2000.

## All Rights Reserved. **Attention please!**

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

**Components used in life-support devices or systems must be expressly authorized for such purpose!** Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| 1      | Overview                                                      | 11   |

|--------|---------------------------------------------------------------|------|

| 1.1    | Features                                                      |      |

| 1.2    | Pin Configuration                                             |      |

| 1.3    | Pin Definitions and Functions                                 |      |

| 1.4    | Logic Symbol                                                  |      |

| 1.5    | Functional Block Diagram                                      |      |

| 1.6    | System Integration                                            |      |

| 1.6.1  | Analog Featurephone with Digital Answering Machine            |      |

| 1.6.2  | Featurephone with Digital Answering Machine for ISDN Terminal |      |

| 1.6.3  | DECT Basestation with Integrated Digital Answering Machine    |      |

| 1.7    | Backward Compatibility                                        | 24   |

| 2      | Functional Description                                        | .25  |

| 2.1    | Functional Units                                              |      |

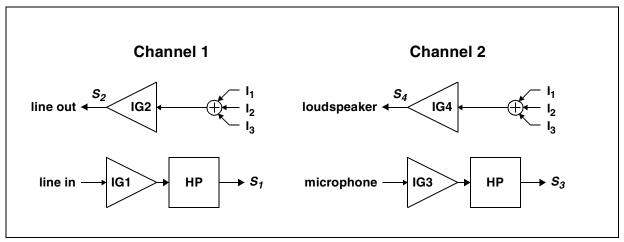

| 2.1.1  | Full Duplex Speakerphone                                      |      |

| 2.1.2  | Echo Cancellation                                             |      |

| 2.1.3  | Echo Suppression                                              |      |

| 2.1.4  | Line Echo Canceller                                           |      |

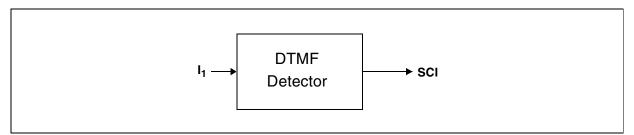

| 2.1.5  | DTMF Detector                                                 |      |

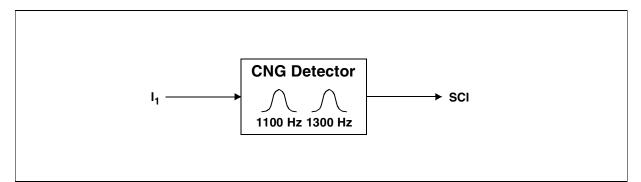

| 2.1.6  | CNG Detector                                                  |      |

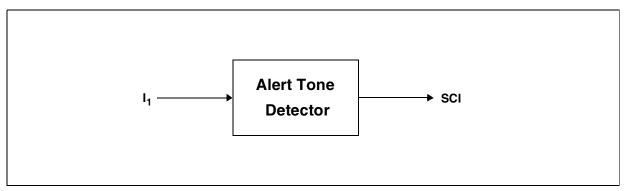

| 2.1.7  | Alert Tone Detector                                           |      |

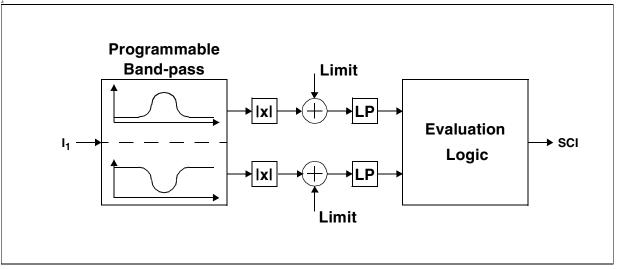

| 2.1.8  | Universal Tone Detector                                       |      |

| 2.1.9  | CPT Detector                                                  |      |

| 2.1.10 | Caller ID Decoder                                             |      |

| 2.1.11 | Caller ID Sender                                              |      |

| 2.1.12 | DTMF Generator                                                |      |

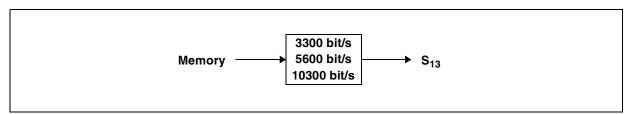

| 2.1.13 | Speech Coder                                                  | 60   |

| 2.1.14 | Speech Decoder                                                |      |

| 2.1.15 | Analog Front End Interface                                    | 69   |

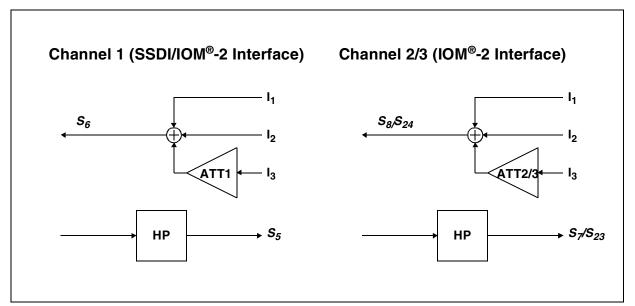

| 2.1.16 | Digital Interface                                             |      |

| 2.1.17 | Universal Attenuator                                          | 72   |

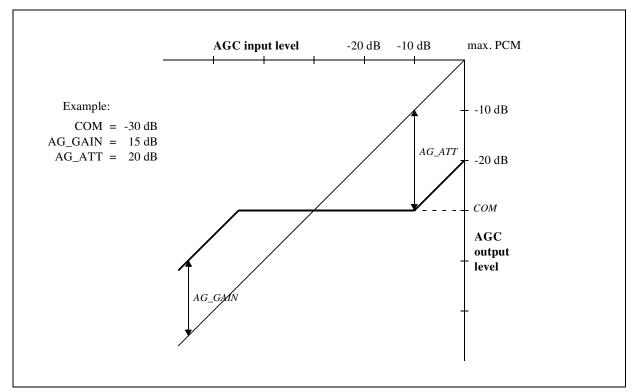

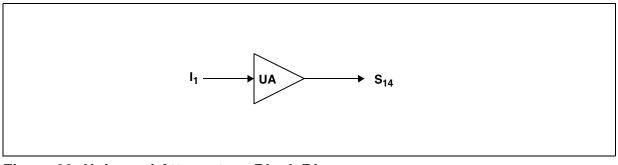

| 2.1.18 | Automatic Gain Control Unit                                   | 73   |

| 2.1.19 | Equalizer                                                     | 75   |

| 2.1.20 | Peak Detector                                                 | 77   |

| 2.2    | Memory Management                                             | 79   |

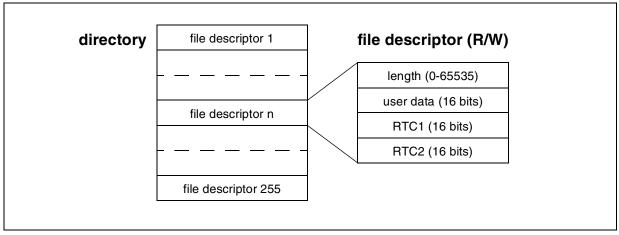

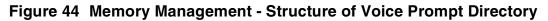

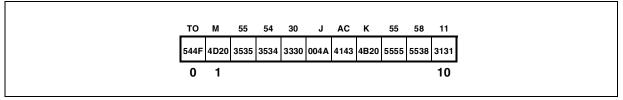

| 2.2.1  | File Definition and Access                                    | 80   |

| 2.2.2  | User Data Word                                                |      |

| 2.2.3  | High Level Memory Management Commands                         | 83   |

| 2.2.4  | Low Level Memory Management Commands                          |      |

| 2.2.5  | Execution Time                                                |      |

| 2.2.6  | Special Notes on File Commands                                |      |

| 2.3    | Miscellaneous                                                 |      |

| 2.3.1  | Real Time Clock                                               | .101 |

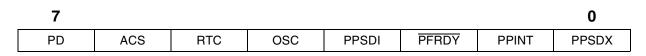

| 2.3.2  | SPS Control Register                               |

|--------|----------------------------------------------------|

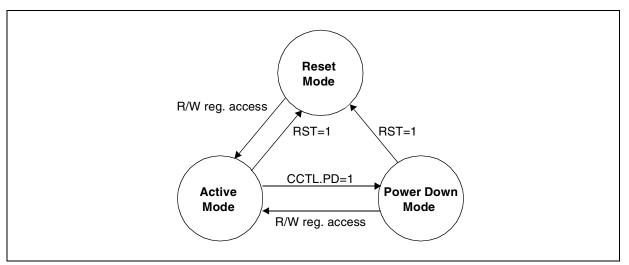

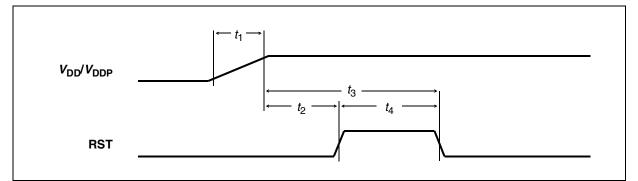

| 2.3.3  | Reset and Power Down Mode102                       |

| 2.3.4  | Interrupt                                          |

| 2.3.5  | Abort                                              |

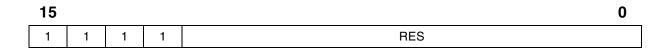

| 2.3.6  | Revision Register                                  |

| 2.3.7  | Hardware Configuration104                          |

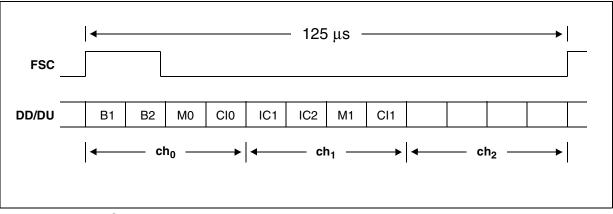

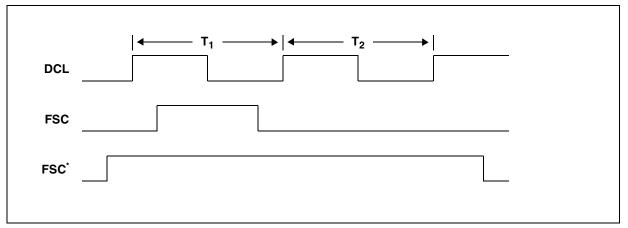

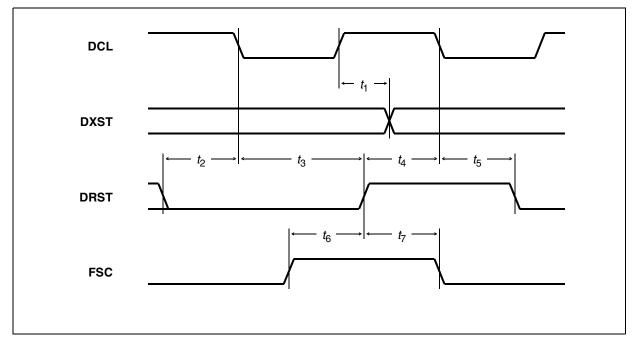

| 2.3.8  | Frame Synchronization104                           |

| 2.3.9  | Clock Tracking                                     |

| 2.3.10 | AFE Clock Source                                   |

| 2.3.11 | Restrictions and Mutual Dependencies of Modules106 |

| 2.3.12 | Emergency Mode                                     |

| 2.4    | Interfaces                                         |

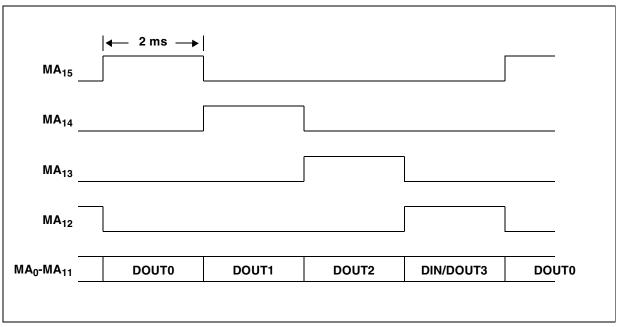

| 2.4.1  | IOM®-2 Interface                                   |

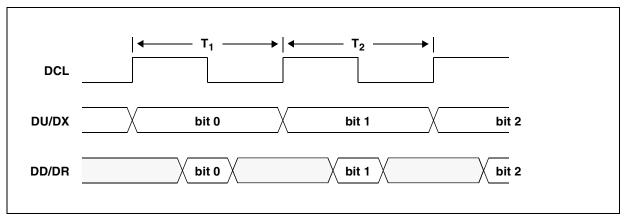

| 2.4.2  | SSDI Interface                                     |

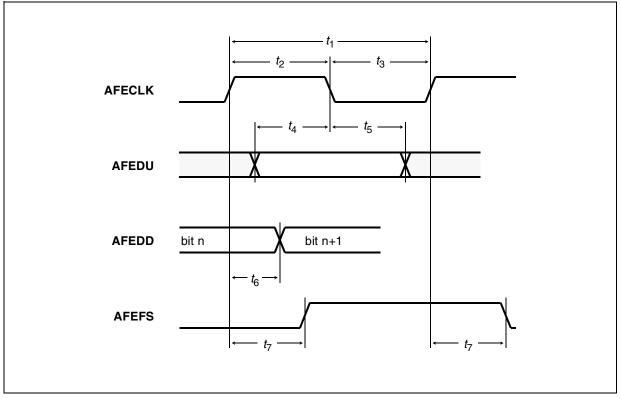

| 2.4.3  | Analog Front End Interface117                      |

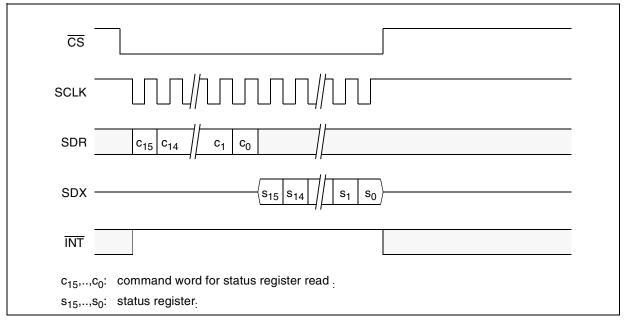

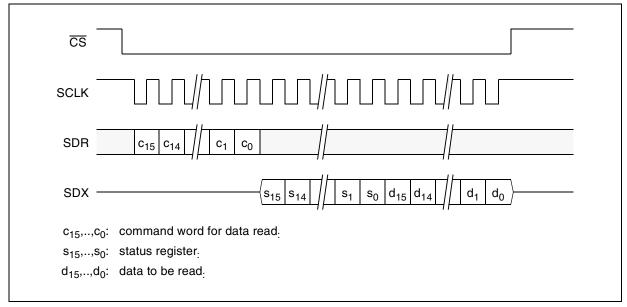

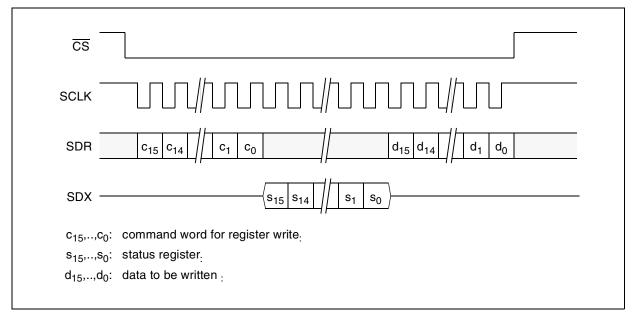

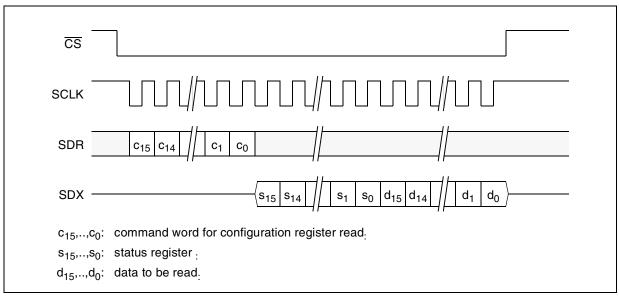

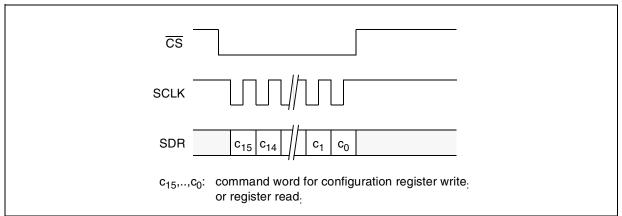

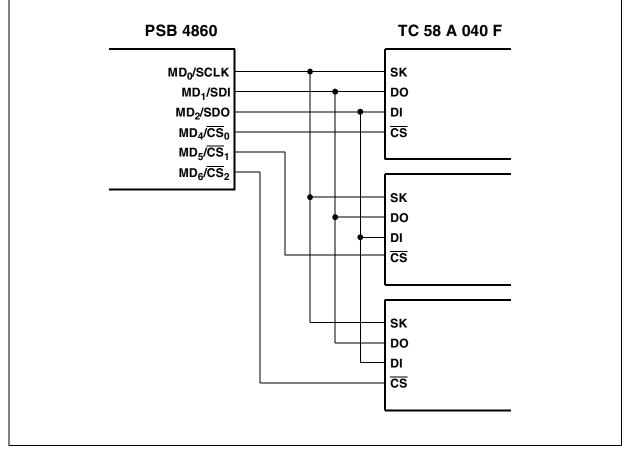

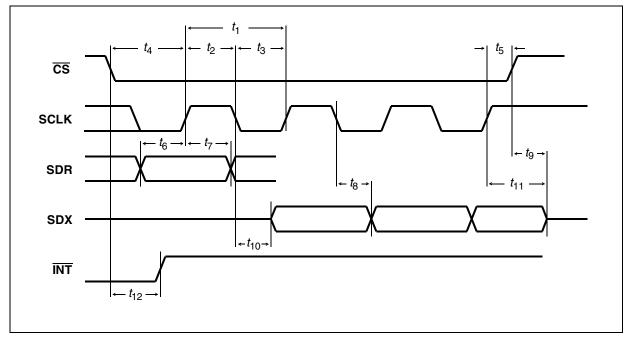

| 2.4.4  | Serial Control Interface119                        |

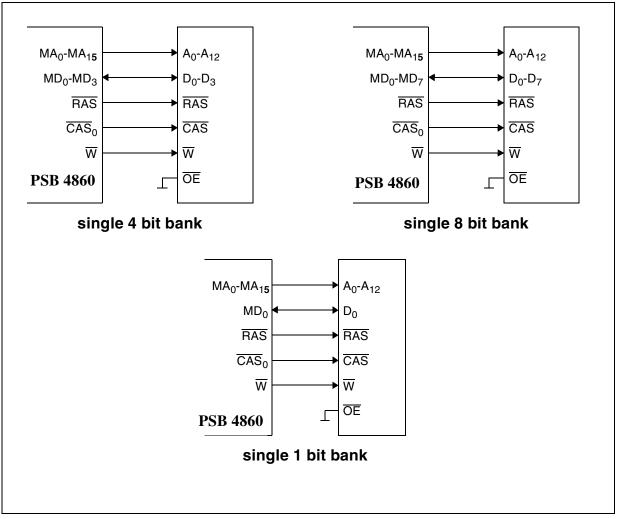

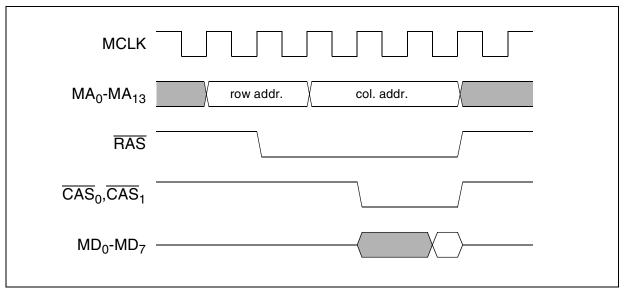

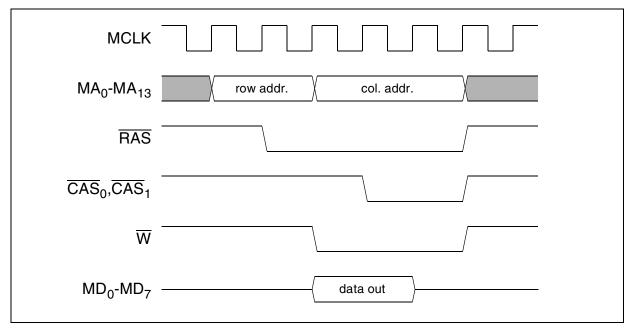

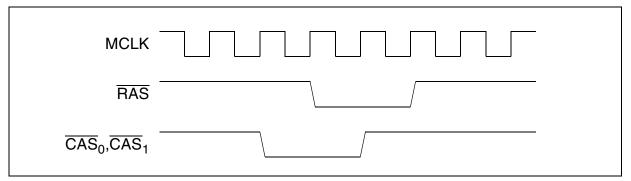

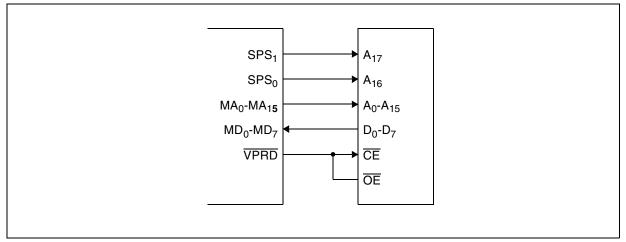

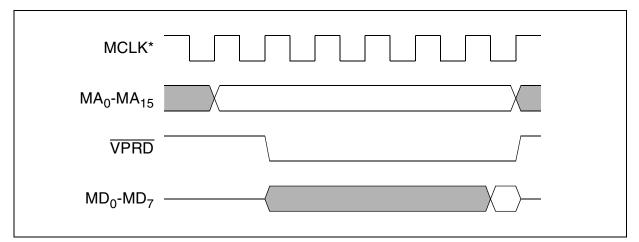

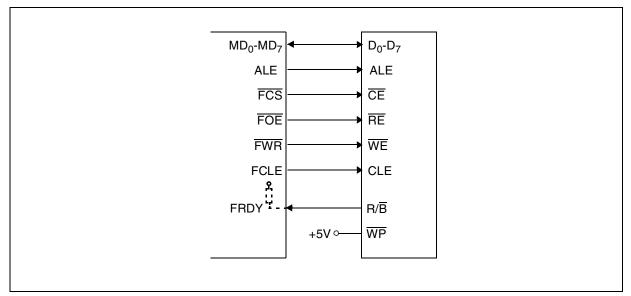

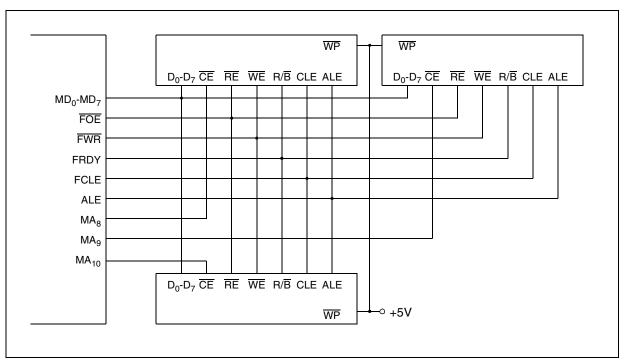

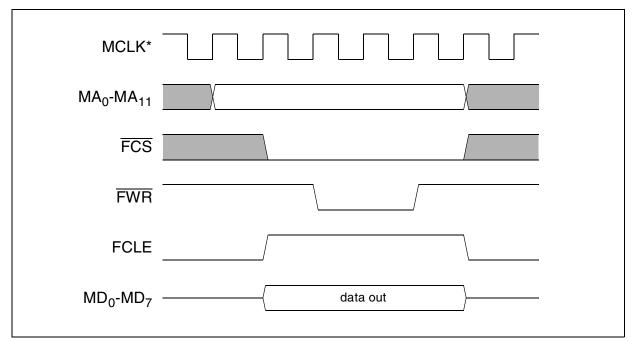

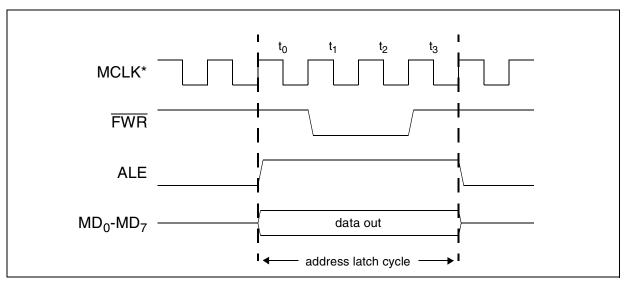

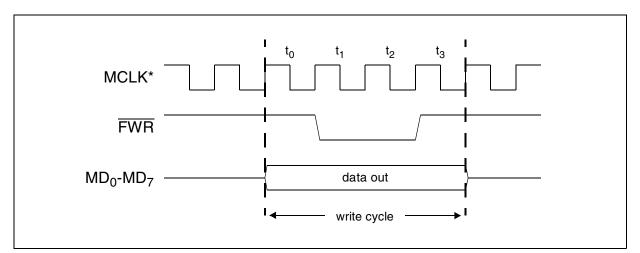

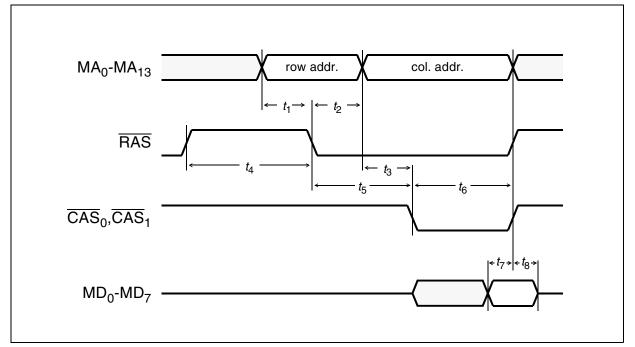

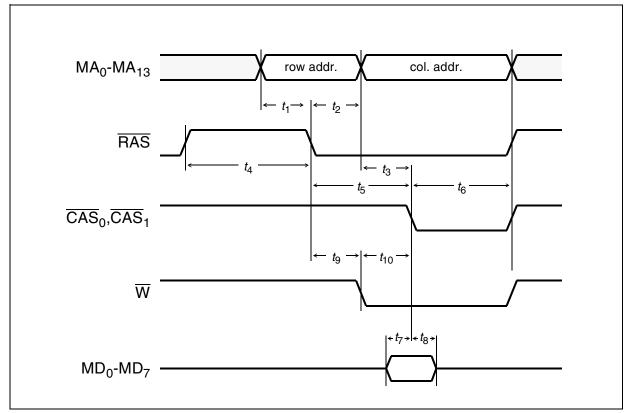

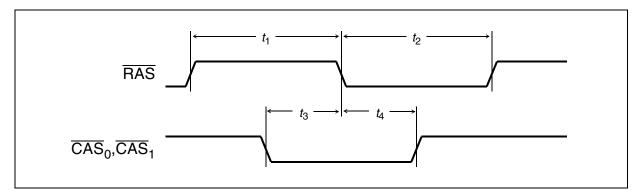

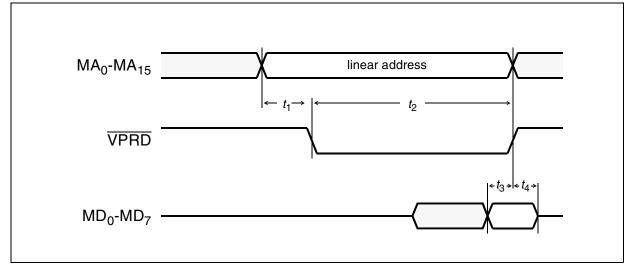

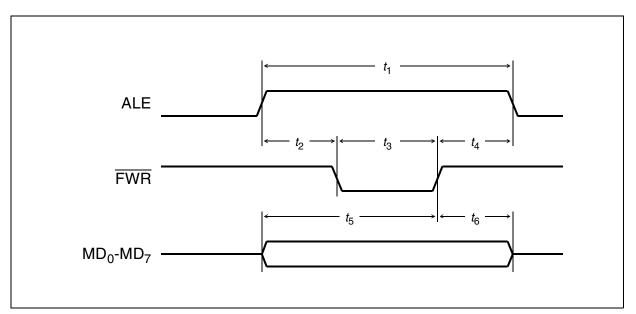

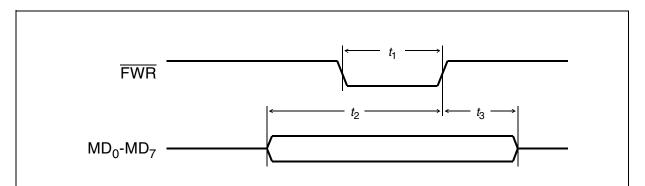

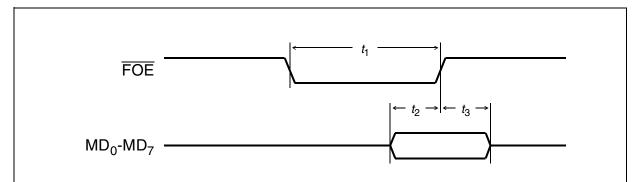

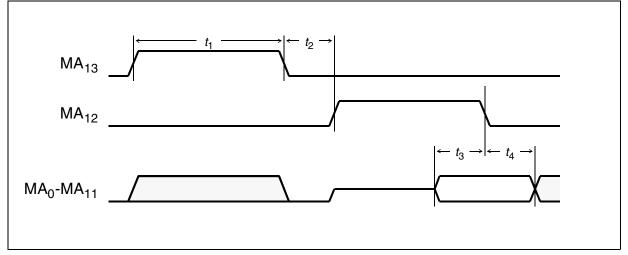

| 2.4.5  | Memory Interface                                   |

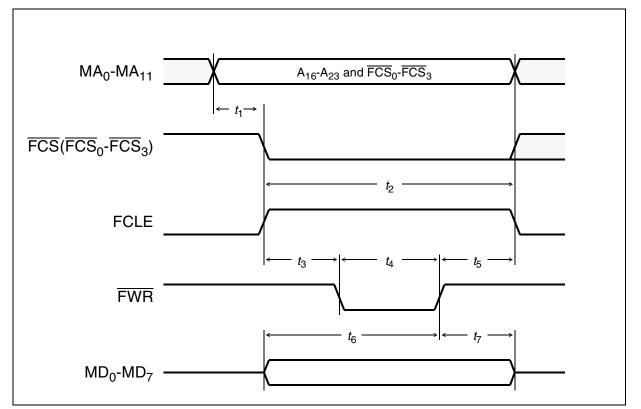

| 2.4.6  | Auxiliary Parallel Port                            |

| 3      | Detailed Register Description141                   |

| 3.1    | Status Register                                    |

| 3.2    | Hardware Configuration Registers144                |

| 3.3    | Read/Write Registers                               |

| 3.3.1  | Register Table                                     |

| 3.3.2  | Register Naming Conventions151                     |

| 4      | Electrical Characteristics                         |

| 4.1    | Absolute Maximum Ratings                           |

| 4.2    | DC Characteristics                                 |

| 4.3    | AC Characteristics                                 |

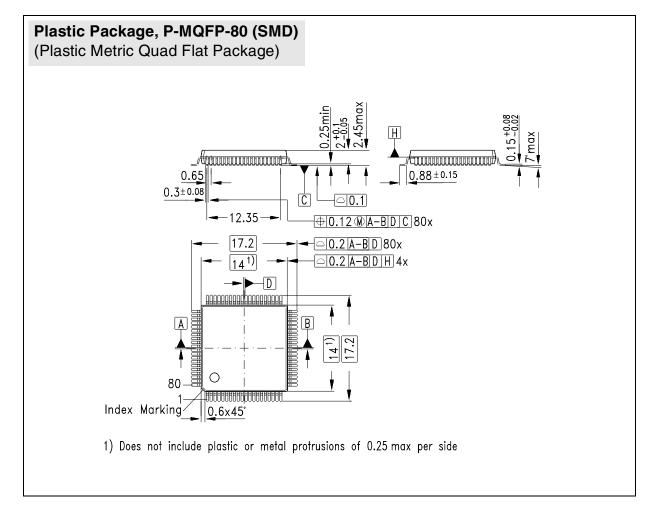

| 5      | Package Outlines                                   |

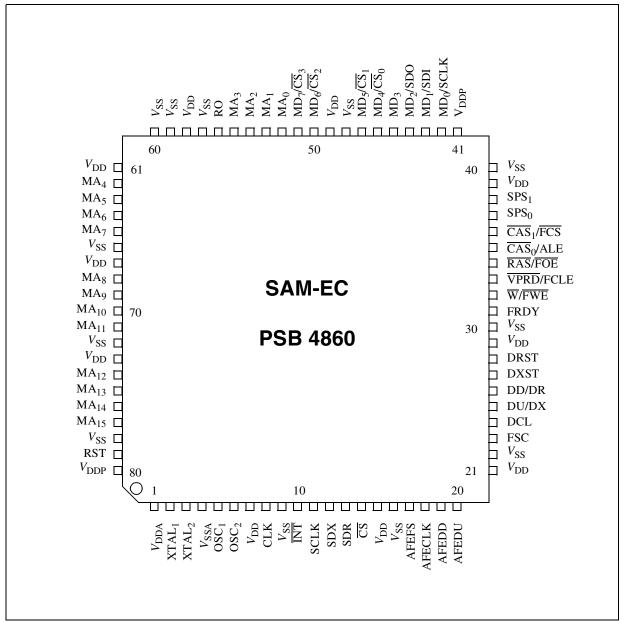

| Figure 1:                                                                                                                                                                                                                                  | Pin Configuration of PSB 4860                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

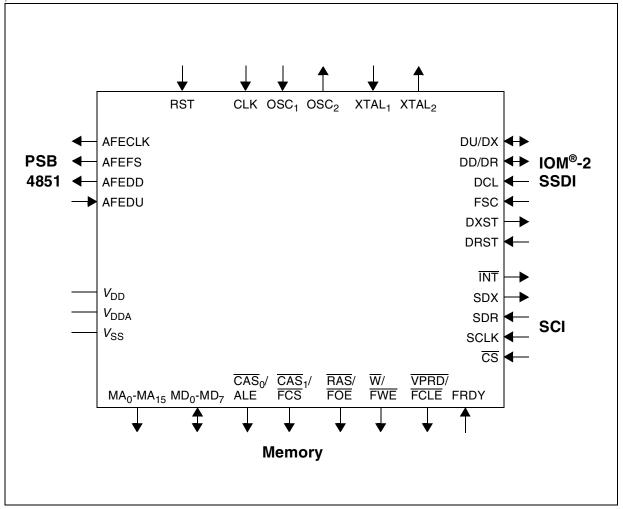

| Figure 2:                                                                                                                                                                                                                                  | Logic Symbol of PSB 4860                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                                                                                                                         |

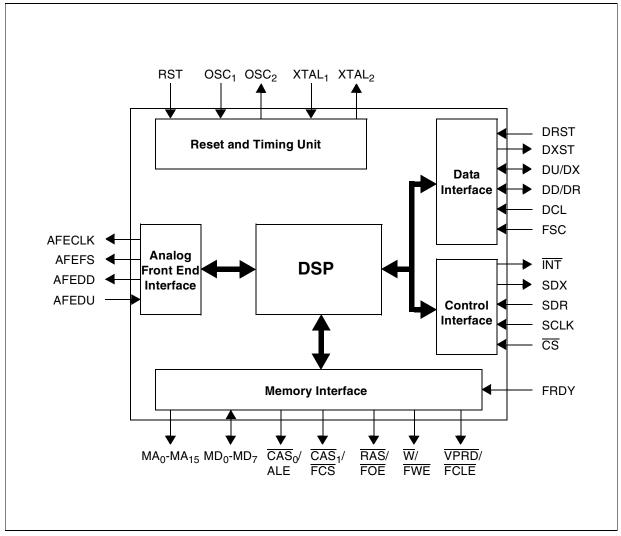

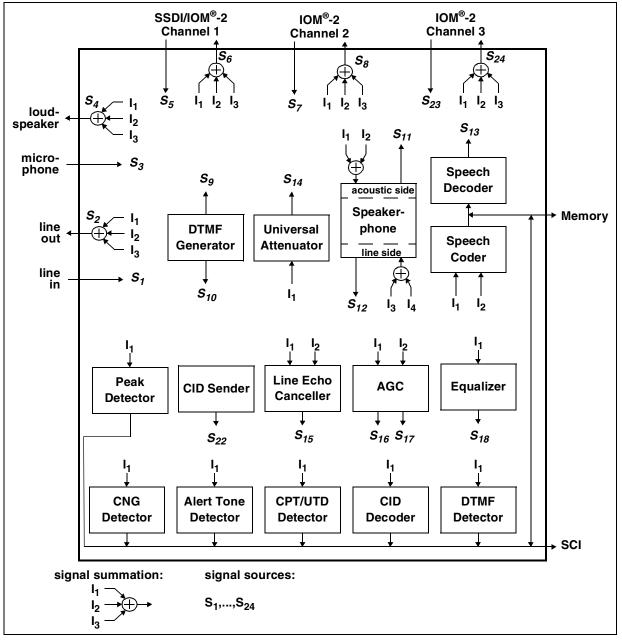

| Figure 3:                                                                                                                                                                                                                                  | Block Diagram of PSB 4860                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                                                                                                                                                         |

| Figure 4:                                                                                                                                                                                                                                  | Analog Full Duplex Speakerphone with Digital Answering Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                         |

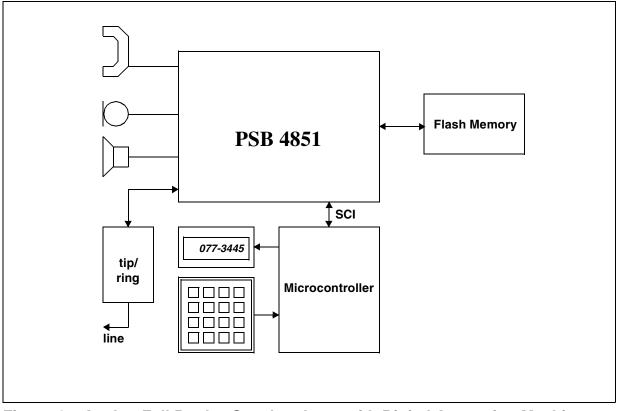

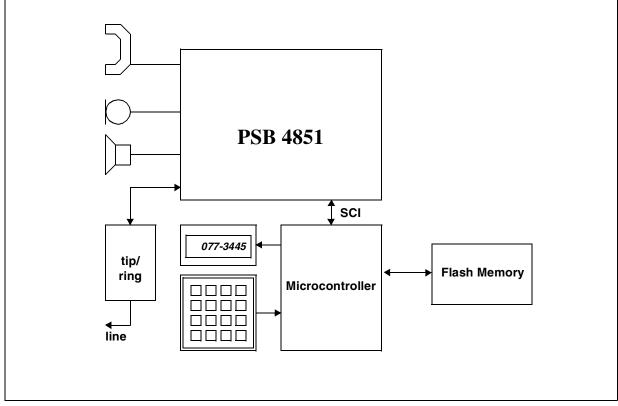

| Figure 5:                                                                                                                                                                                                                                  | Stand-Alone Answering Machine with Data Access via SCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21                                                                                                                                                                                                         |

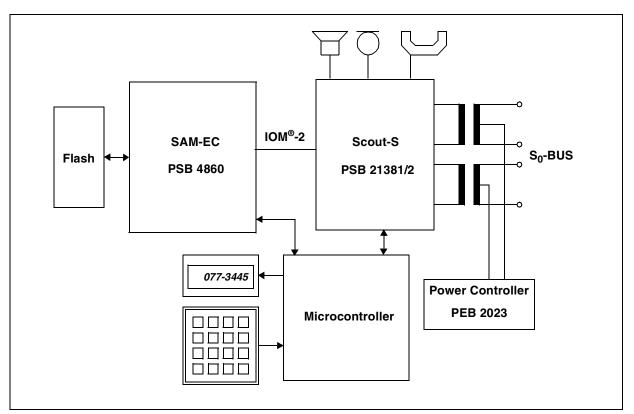

| Figure 6:                                                                                                                                                                                                                                  | Featurephone with Answering Machine for ISDN Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                                                                                                                         |

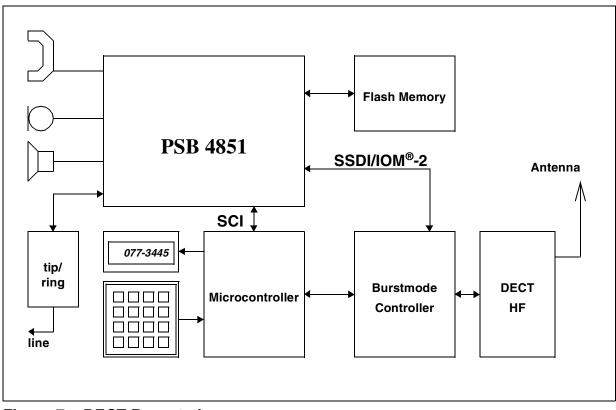

| Figure 7:                                                                                                                                                                                                                                  | DECT Basestation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                                                                                                                                                                                                         |

| Figure 8:                                                                                                                                                                                                                                  | Functional Units - Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25                                                                                                                                                                                                         |

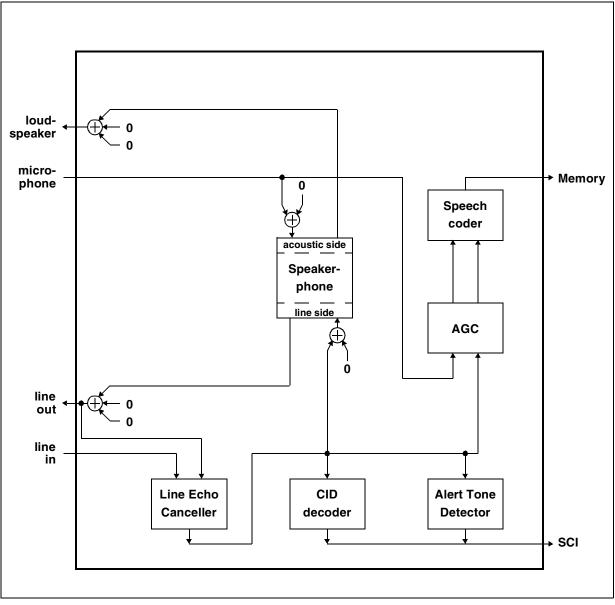

| Figure 9:                                                                                                                                                                                                                                  | Functional Units - Recording a Phone Conversation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                                                                                         |

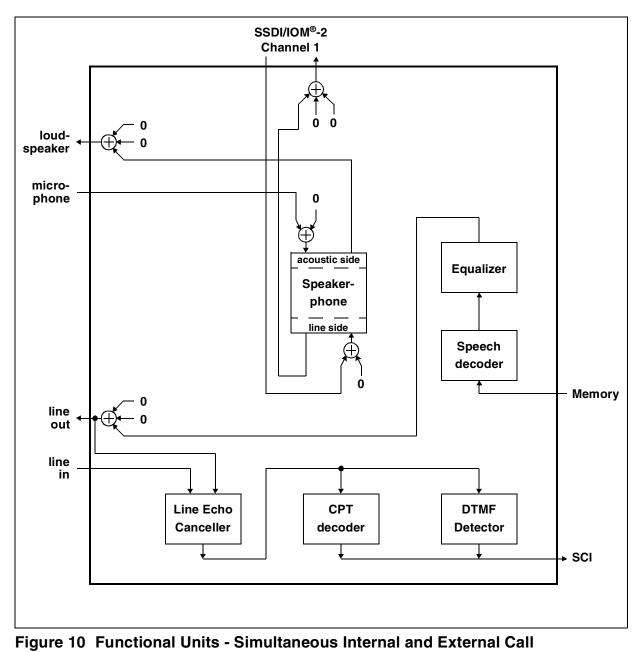

| Figure 10:                                                                                                                                                                                                                                 | Functional Units - Simultaneous Internal and External Call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                                                                                                                                                                                         |

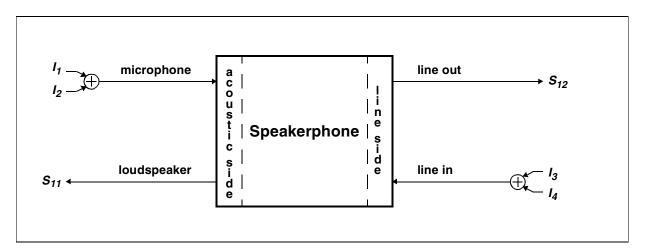

| -                                                                                                                                                                                                                                          | Speakerphone - Signal Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |

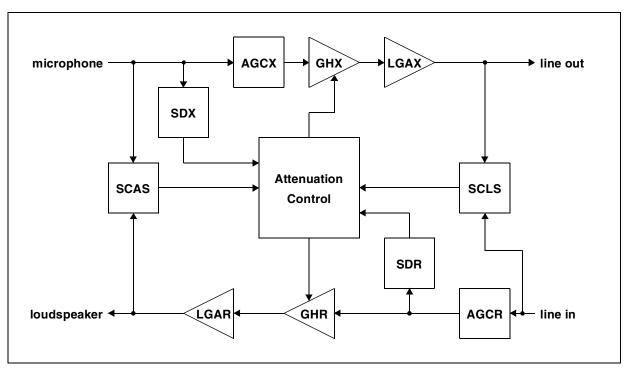

| -                                                                                                                                                                                                                                          | Speakerphone - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                            |

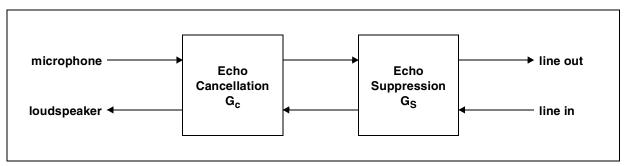

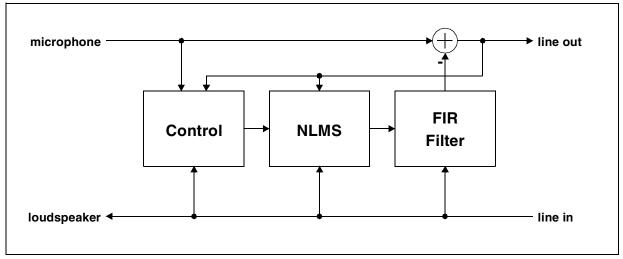

| Figure 13:                                                                                                                                                                                                                                 | Echo Cancellation Unit - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                                                                                                                                                                         |

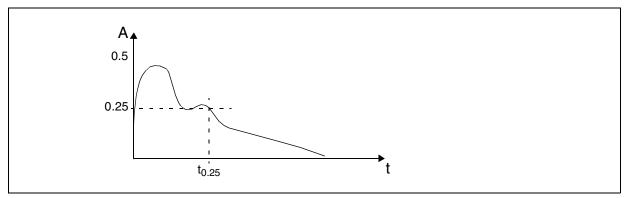

|                                                                                                                                                                                                                                            | Echo Cancellation Unit - Typical Room Impulse Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                            |

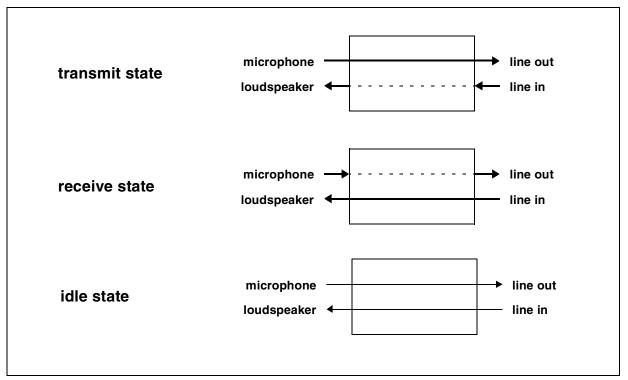

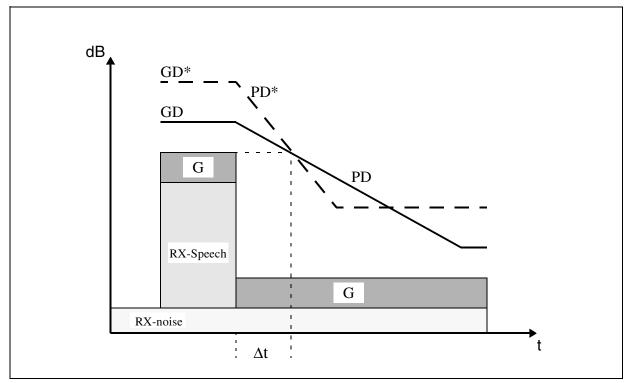

|                                                                                                                                                                                                                                            | Echo Suppression Unit - States of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                            |

| •                                                                                                                                                                                                                                          | Echo Suppression Unit - Signal Flow Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |

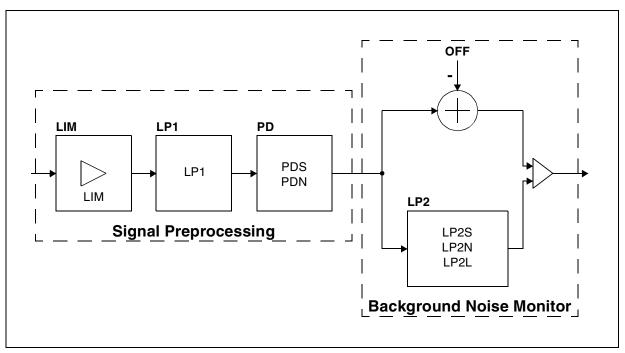

| •                                                                                                                                                                                                                                          | Speech Detector - Signal Flow Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            |

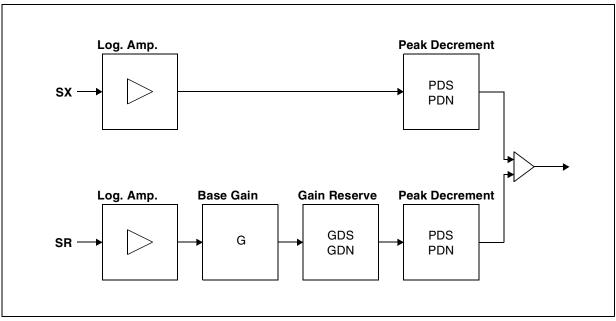

| 0                                                                                                                                                                                                                                          | Speech Comparator - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |

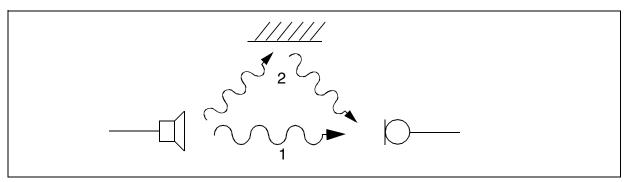

| •                                                                                                                                                                                                                                          | Speech Comparator - Acoustic Echoes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            |

| -                                                                                                                                                                                                                                          | Speech Comparator - Interdependence of Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |

| -                                                                                                                                                                                                                                          | Echo Suppression Unit - Automatic Gain Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |

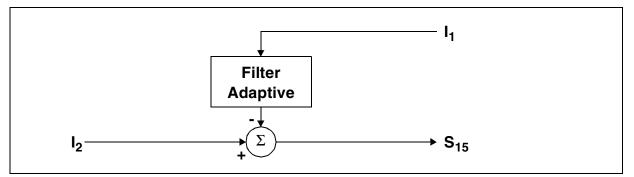

| •                                                                                                                                                                                                                                          | Line Echo Cancellation Unit - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                            |

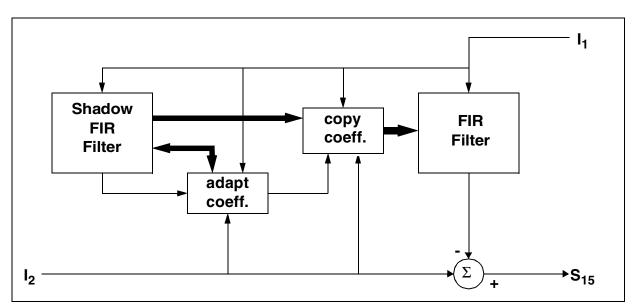

| -                                                                                                                                                                                                                                          | Line Echo Cancellation Unit - Superior Mode with Shadow FIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                            |

| •                                                                                                                                                                                                                                          | DTMF Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |

| Figure 25:                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |

| •                                                                                                                                                                                                                                          | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                                                                                                                                                         |

| Figure 26:                                                                                                                                                                                                                                 | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50                                                                                                                                                                                                   |

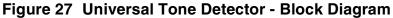

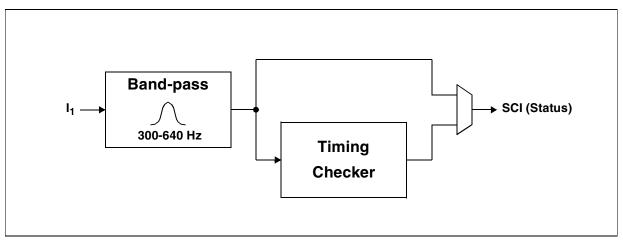

| Figure 26:<br>Figure 27:                                                                                                                                                                                                                   | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51                                                                                                                                                                                             |

| Figure 26:<br>Figure 27:<br>Figure 28:                                                                                                                                                                                                     | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53                                                                                                                                                                                       |

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:                                                                                                                                                                                       | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53                                                                                                                                                                                 |

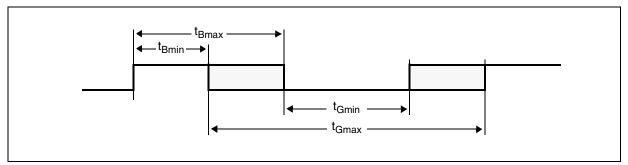

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:                                                                                                                                                                         | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53<br>55                                                                                                                                                                           |

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:                                                                                                                                                           | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53<br>55<br>57                                                                                                                                                                     |

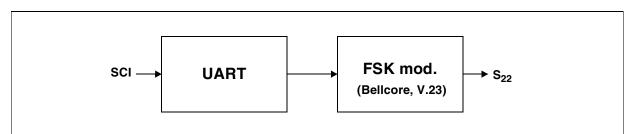

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:                                                                                                                                             | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53<br>55<br>57<br>59                                                                                                                                                               |

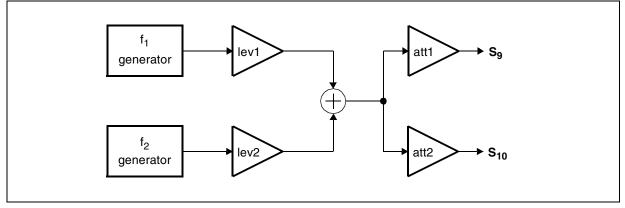

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:                                                                                                                               | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53<br>55<br>57<br>59<br>60                                                                                                                                                         |

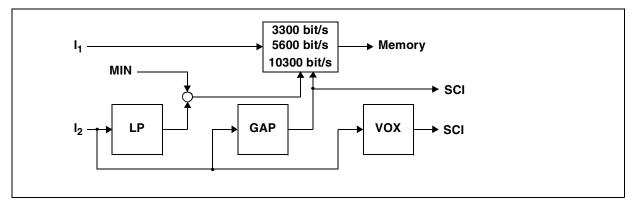

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:                                                                                                                 | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>53<br>55<br>57<br>59<br>60<br>63                                                                                                                                                   |

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:                                                                                                   | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>53<br>53<br>55<br>57<br>59<br>60<br>63<br>66                                                                                                                                                   |

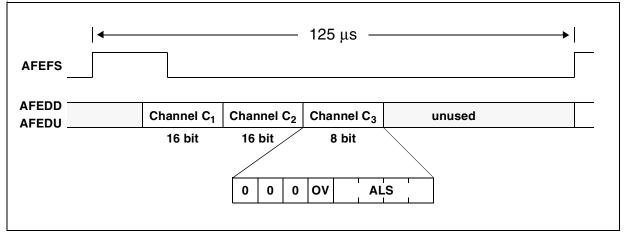

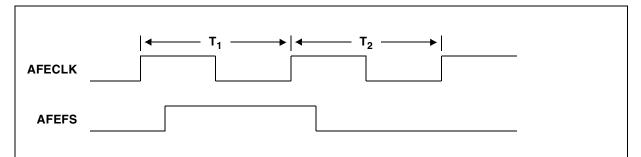

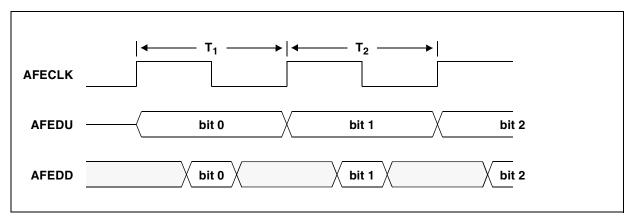

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:<br>Figure 36:                                                                                     | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>50<br>51<br>53<br>55<br>57<br>59<br>60<br>63<br>66<br>69                                                                                                                                             |

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:<br>Figure 36:<br>Figure 37:                                                                       | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>49</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>63</li> <li>66</li> <li>69</li> <li>70</li> </ul>                                     |

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:<br>Figure 36:<br>Figure 37:<br>Figure 38:                                                         | CNG Detector - Block Diagram<br>Alert Tone Detector - Block Diagram<br>Universal Tone Detector - Block Diagram<br>CPT Detector - Block Diagram<br>CPT Detector - Cooked Mode<br>Caller ID Decoder - Block Diagram<br>Caller ID Sender - Block Diagram<br>DTMF Generator - Block Diagram<br>Speech Coder - Block Diagram<br>VOX Detector<br>Speech Decoder - Block Diagram<br>Analog Front End Interface - Block Diagram<br>Digital Interface - Block Diagram                                                                                                                     | <ul> <li>49</li> <li>50</li> <li>51</li> <li>53</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>63</li> <li>66</li> <li>69</li> <li>70</li> <li>72</li> </ul>                                     |

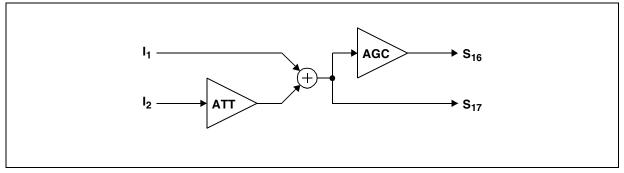

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:<br>Figure 36:<br>Figure 37:<br>Figure 38:<br>Figure 39:                                           | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>49</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>63</li> <li>66</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> </ul>             |

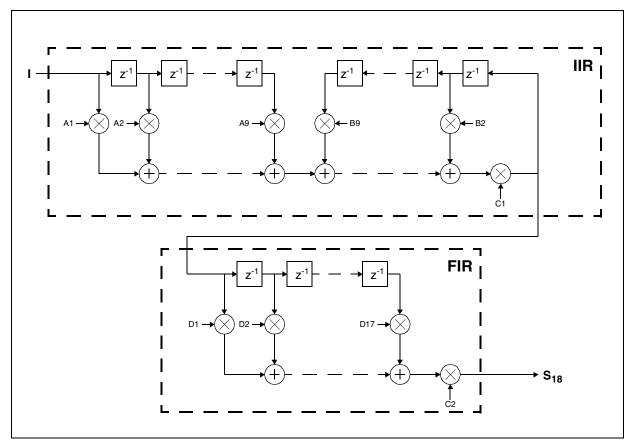

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 34:<br>Figure 35:<br>Figure 35:<br>Figure 37:<br>Figure 38:<br>Figure 39:<br>Figure 40:                             | CNG Detector - Block Diagram<br>Alert Tone Detector - Block Diagram<br>Universal Tone Detector - Block Diagram<br>CPT Detector - Block Diagram<br>CPT Detector - Cooked Mode<br>Caller ID Decoder - Block Diagram<br>Caller ID Sender - Block Diagram<br>DTMF Generator - Block Diagram<br>Speech Coder - Block Diagram<br>VOX Detector<br>Speech Decoder - Block Diagram<br>Analog Front End Interface - Block Diagram<br>Digital Interface - Block Diagram<br>Universal Attenuator - Block Diagram<br>Automatic Gain Control Unit - Block Diagram<br>Equalizer - Block Diagram | <ul> <li>49</li> <li>50</li> <li>51</li> <li>53</li> <li>53</li> <li>55</li> <li>57</li> <li>59</li> <li>60</li> <li>63</li> <li>66</li> <li>69</li> <li>70</li> <li>72</li> <li>73</li> <li>75</li> </ul> |

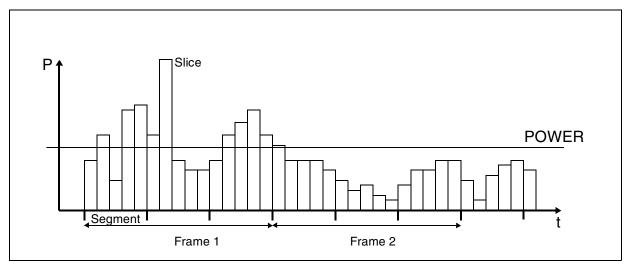

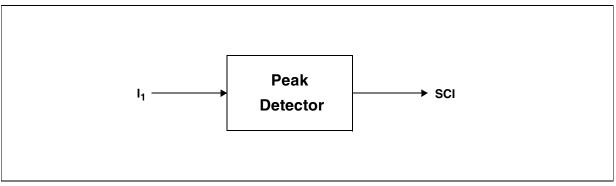

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 33:<br>Figure 35:<br>Figure 36:<br>Figure 37:<br>Figure 38:<br>Figure 39:<br>Figure 40:<br>Figure 41:               | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{c} 49\\ 50\\ 51\\ 53\\ 55\\ 57\\ 59\\ 60\\ 63\\ 66\\ 69\\ 70\\ 72\\ 73\\ 75\\ 77\end{array}$                                                                                                |

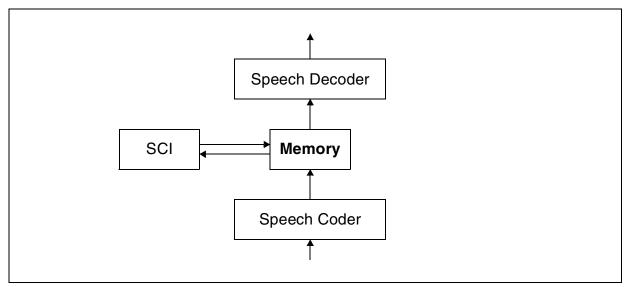

| Figure 26:<br>Figure 27:<br>Figure 28:<br>Figure 29:<br>Figure 30:<br>Figure 31:<br>Figure 32:<br>Figure 33:<br>Figure 33:<br>Figure 35:<br>Figure 36:<br>Figure 37:<br>Figure 38:<br>Figure 39:<br>Figure 40:<br>Figure 41:<br>Figure 42: | CNG Detector - Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{c} 49\\ 50\\ 51\\ 53\\ 55\\ 57\\ 59\\ 60\\ 63\\ 66\\ 69\\ 70\\ 72\\ 73\\ 75\\ 77\\ 79 \end{array}$                                                                                          |

| -          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

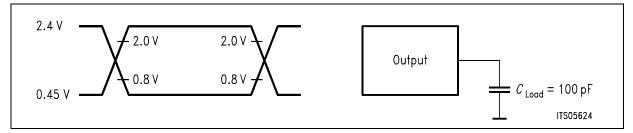

| •          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |