# Élan™SC400 and ÉlanSC410

#### Single-Chip, Low-Power, PC/AT-Compatible Microcontrollers

#### DISTINCTIVE CHARACTERISTICS Élan™SC400 and ÉlanSC410 Microcontrollers

- E86<sup>™</sup> family of x86 embedded processors

- Offers improved time-to-market, software migration, and field-proven development tools

- Highly integrated single-chip CPU with a complete set of common peripherals

- Accelerates time-to-market with simplified hardware

- Low-power 0.35-micron process technology

- Single chip delivers smallest system form factor

- 33-MHz, 66-MHz, and 100-MHz operating frequencies

#### ■ Am486<sup>®</sup> CPU core

- Robust Microsoft<sup>®</sup> Windows<sup>®</sup> compatible CPU

- 8-Kbyte write-back cache for enhanced performance

- Fully static design with System Management Mode (SMM) for power savings

- Comprehensive power management unit

- Seven modes of operation allow fine-tuning of power requirements for maximum battery life

- Provides a superset of APM 1.2 features

#### Glueless burst-mode ROM/Flash memory/SRAM interface

Reduces system cost by allowing mask ROM and Flash memory at the same time with three ROM/ Flash memory/SRAM chip selects

#### Glueless DRAM controller

- Allows mixed DRAM types on a per-bank basis to reduce system cost

- VESA Local (VL) bus and ISA bus interface

- Reduces time-to-market with a wide variety of offthe-shelf companion chips

- Standard PC/AT system logic (PICs, DMACs, timer, RTC)

- DOS, ROM-DOS, Windows, and industrystandard BIOS support

- Leverages the benefits of desktop computing environment at embedded price points

- Bidirectional parallel port with Enhanced Parallel Port (EPP) mode

- 16550-compatible UART

- Infrared port for wireless communication

- Standard and high-speed

- Keyboard interface

- Matrix keyboard support with up to 15 rows and 8 columns

- SCP-emulation mode for PC/AT and XT keyboard support

#### ÉlanSC400 Microcontroller Only

The ÉlanSC400 microcontroller includes the following additional features designed specifically for mobile computing applications. The ÉlanSC410 microcontroller does not include these features.

- Dual PC Card (PCMCIA Version 2.1) controller supports 8- or 16-bit data bus

- End-user (after-market) system expansion

- ExCA-compliant, 82365-register set compatible

- Leverages off-the-shelf card and socket services

- Supports DMA transfers between I/O PC cards and system DRAM

#### LCD graphics controller

- Supports monochrome and 4-bit color Super Twisted Nematic (STN) LCDs

- Unified Memory Architecture (UMA) eliminates separate video memory

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or surgical indication of the surgical indication in which the failure of AMD's product could create a situation where personal indications.

or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such product.

<sup>©</sup> Copyright 1998 Advanced Micro Devices, Inc. All Rights Reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to discontinue its products, or make changes in its products, at any time without notice.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

#### **GENERAL DESCRIPTION**

The Élan<sup>TM</sup>SC400 and ÉlanSC410 microcontrollers are the among the latest in a series of  $E86^{TM}$  family microcontrollers, which integrate proven x86 CPU cores with a comprehensive set of on-chip peripherals in a 0.35-micron process.

The ÉlanSC400 and ÉlanSC410 microcontrollers combine a 32-bit, low-voltage Am486 CPU with a complete set of PC/AT-compatible peripherals, along with the power management features required for battery operation.

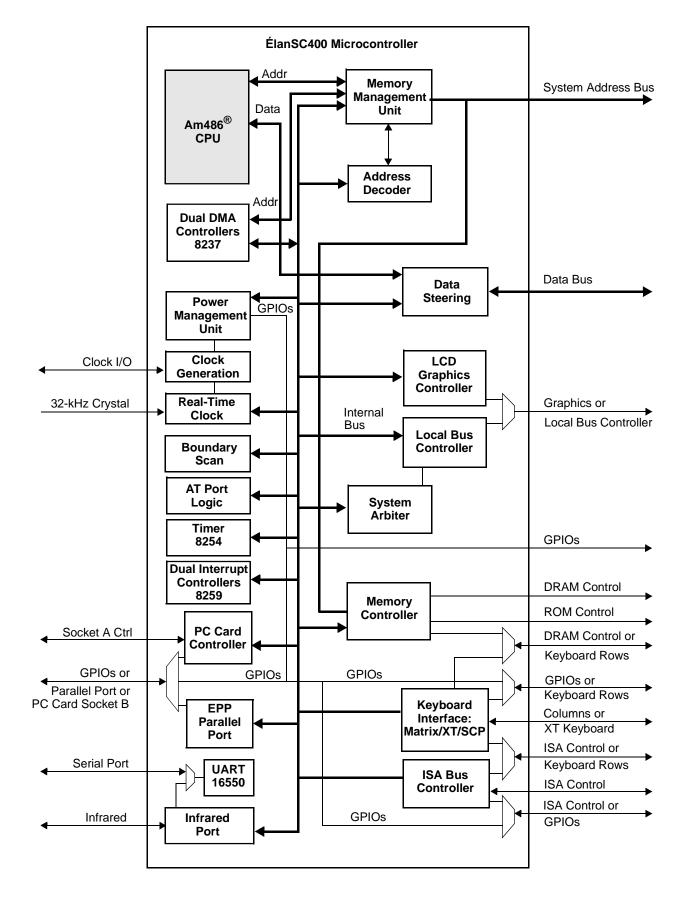

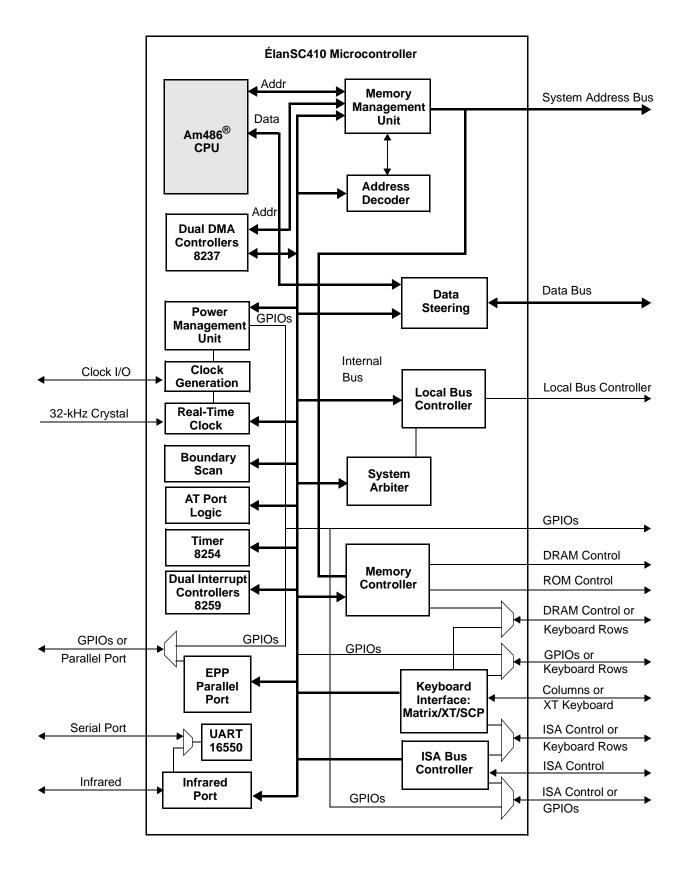

Leveraging the benefits of the x86 desktop computing environment, the ÉlanSC400 and ÉlanSC410 microcontrollers integrate all of the common logic and I/O functionality associated with a PC/AT computing system into a single device, eliminating the need for multiple peripheral chips. Fully integrated PC/AT-compatible peripherals include two 8259A-compatible programmable interrupt controllers (PICs), two 8237A-compatible DMA controllers, an 8254-compatible timer, a 16550 UART, an IrDA controller, VL-bus and ISA bus controllers, a real-time clock (RTC), and Enhanced Parallel Port (EPP) mode for the parallel port. With its low-voltage Am486<sup>®</sup> CPU core and ultra-small form factor, the ÉlanSC400 microcontroller is highly optimized for mobile computing applications. The ÉlanSC410 microcontroller is targeted specifically for embedded systems.

A feature comparison of the two microcontrollers is shown in Table 1 on page 3.

The ÉlanSC400 and ÉlanSC410 microcontrollers use the industry-standard 486 microprocessor instruction set. All software written for the x86 architecture family is compatible with the ÉlanSC400 and ÉlanSC410 microcontrollers.

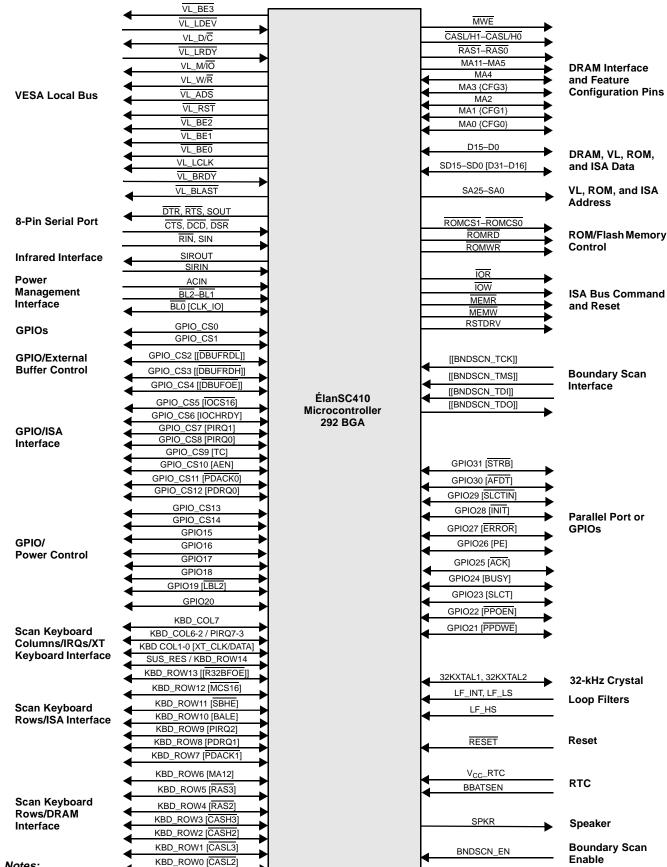

The ÉlanSC400 and ÉlanSC410 microcontrollers are based on a fully static design and include an advanced power management unit. Operating voltages are 2.7 V–3.3 V with 5-V-tolerant I/O pads. Orderable in both 33-MHz, 66-MHz, and 100-MHz peak processor speeds, the product is available in the ultra-small 292 ball grid array (BGA) package.

#### **ORDERING INFORMATION**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |        |  |

|--------------------|--------|--|

| ELANSC400-33       | AC, AI |  |

| ELANSC400-66       |        |  |

| ELANSC400-100      | AC     |  |

| ELANSC410-33       | AC, AI |  |

| ELANSC410-66       |        |  |

| ELANSC410-100      | AC     |  |

#### TEMPERATURE RANGE

C = Commercial For 33 and 66 MHz:  $T_{CASE} = 0^{\circ}C$  to +95°C For 100 MHz:  $T_{CASE} = 0^{\circ}C$  to +85°C

I = Industrial For 33 and 66 MHz,  $T_{CASE}$  = - 40°C to +95°C

#### PACKAGE TYPE

A = 292-pin BGA (Ball Grid Array)

#### SPEED OPTION

-33 = 33 MHz -66 = 66 MHz -100 = 100 MHz

#### **DEVICE NUMBER/DESCRIPTION**

ÉlanSC400 microcontroller ÉlanSC410 microcontroller

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Table 1. Product Comparison—Ela<br>Feature                    | INSC400 and ElanSC410 Microc<br>ÉlanSC410 | ÉlanSC400                     |

|---------------------------------------------------------------|-------------------------------------------|-------------------------------|

| Core CPU                                                      | Am486 CPU                                 | Am486 CPU                     |

| L1 Cache                                                      | 8-Kbyte Write-Back                        | 8-Kbyte Write-Back            |

| System management mode (SMM)                                  | Yes                                       | Yes                           |

| Floating-point unit                                           | No                                        | No                            |

| Data Bus                                                      | 16, 32 bit                                | 16, 32 bit                    |

| ISA Interface                                                 | 8, 16 bit                                 | 8, 16 bit                     |

| ISA interface<br>ISA bus mastering                            | No                                        | No                            |

| VESA Local Bus                                                | 32 bit                                    | 32 bit                        |

| VL bus mastering                                              | No                                        | No                            |

| Power Management                                              | Yes                                       | Yes                           |

| Mode timers                                                   | Yes                                       | Yes                           |

| Activity detection                                            | Yes                                       | Yes                           |

| SMI/NMI generation                                            | Yes                                       | Yes                           |

| Battery monitoring                                            | Yes                                       | Yes                           |

|                                                               | 163                                       | 163                           |

| On-Chip ROM Interface<br>Width                                | 8, 16, 32 bit                             | 9 16 22 hit                   |

| Size (total ROM space)                                        | 3 x 64 Mbyte                              | 8, 16, 32 bit<br>3 x 64 Mbyte |

|                                                               | -                                         | 3 X 04 Mibyte                 |

| ROM chip selects<br>Burst-mode support                        | 3<br>Yes                                  | Yes                           |

| Support for SRAM as ROM address space                         | Yes                                       | Yes                           |

|                                                               | 165                                       | 165                           |

| On-Chip DRAM Controller<br>Banks                              | 4                                         | 4                             |

| Width                                                         |                                           |                               |

|                                                               | 16, 32 bit                                | 16, 32 bit                    |

| Size (total of all banks)                                     | 64 Mbyte<br>Yes                           | 64 Mbyte<br>Yes               |

| EDO support                                                   |                                           |                               |

| Support for SRAM as main memory                               | ROM-mappable                              | ROM-mappable                  |

| Integrated PC/AT-Compatible Peripherals                       |                                           | N N                           |

| Programmable timer (8254-compatible)                          | Yes                                       | Yes                           |

| Real-time clock (146818A-compatible)                          | Yes                                       | Yes                           |

| Port B and Port 92h I/O registers                             | Yes                                       | Yes                           |

| Cascaded DMA Controllers (8237A)                              | 2                                         | 2                             |

| Width<br>Total number of channels                             | 8, 16 bit                                 | 8, 16 bit                     |

| External channels                                             | 7                                         | 7                             |

|                                                               | 2                                         | 2 2                           |

| Cascaded Interrupt Controllers (8259)<br>External IRQ signals | 2 8                                       | 8                             |

|                                                               | -                                         |                               |

| Bidirectional Parallel Port with EPP Mode                     | Yes                                       | Yes                           |

| Serial Port (UART)                                            | 16550-compatible                          | 16550-compatible              |

| Keyboard Interface                                            |                                           |                               |

| Support for external 8042 SCP                                 | Yes                                       | Yes                           |

| XT interface                                                  | Yes                                       | Yes                           |

| Matrix scanned with SCP emulation                             | Yes                                       | Yes                           |

| General-Purpose Input/Output Signals                          | 32                                        | 32                            |

| Infrared (IrDA) Port                                          | Yes                                       | Yes                           |

| PC Card Controller                                            | No                                        | Yes                           |

| Sockets                                                       |                                           | 2                             |

| PCMCIA 2.1-compliant                                          |                                           | Yes                           |

| 82365-compatible                                              |                                           | Yes                           |

| LCD Graphics Controller                                       | No                                        | Yes                           |

| Programmable clock frequency                                  |                                           | Yes                           |

| Unified memory architecture (UMA)                             |                                           | Yes                           |

| JTAG Support                                                  | Yes                                       | Yes                           |

| Pin Count and Package                                         | 292 BGA                                   | 292 BGA                       |

| V <sub>CC</sub> : CPU core                                    | 2.7–3.3 V                                 | 2.7–3.3 V                     |

| On-chip peripheral logic                                      | 3.3 V                                     | 3.3 V                         |

| I/O tolerance (designated pins)                               | 5 V                                       | 5 V                           |

| Processor Clock Rate                                          | 33, 66, 100 MHz                           | 33, 66, 100 MHz               |

| FIDLESSUL GIUCK RALE                                          | 33, 00, 100 IVIEZ                         | ວວ, ບບ, 100 IVI⊓∠             |

Table 1. Product Comparison—ÉlanSC400 and ÉlanSC410 Microcontrollers

#### BLOCK DIAGRAM—ÉlanSC400 MICROCONTROLLER

#### BLOCK DIAGRAM—ÉlanSC410 MICROCONTROLLER

### LOGIC SYMBOL—ÉlanSC400 MICROCONTROLLER

|                                  | LCDD7 [VL_BE3]                       |                 |                         |                                      |

|----------------------------------|--------------------------------------|-----------------|-------------------------|--------------------------------------|

| •                                |                                      |                 | MWE                     |                                      |

| •                                |                                      |                 | CASL/H1-CASL/H0         |                                      |

| •                                | LCDD5 [VL_D/C]                       |                 | RAS1-RAS0               |                                      |

| •                                | LCDD4 [VL_LRDY]                      |                 | MA11–MA5                |                                      |

| •                                | LCDD3 [VL_M/IO]                      |                 | MA1                     | DRAM Interface                       |

|                                  | LCDD2 [VL_W/R]                       |                 | MA3 {CFG3}              | and Feature                          |

| LCD Graphics                     | LCDD1 [VL_ADS]                       |                 | MA2 {CFG2}              | Configuration Pins                   |

| Controller or                    | LCDD0 [VL_RST]                       |                 | MA1 {CFG1}              |                                      |

| VESA Local Bus                   | M [VL_BE2]                           |                 | MA0 {CFG0}              |                                      |

|                                  | LC [VL_BE1]                          |                 |                         |                                      |

|                                  | SCK [VL_BE0]                         |                 | ■ D15-D0                | DRAM, VL, ROM, ISA                   |

|                                  | FRM [VL_LCLK]                        |                 | SD15-SD0 [D31-D16]      | and PC Card Data                     |

|                                  | LVEE [VL_BRDY]                       |                 |                         |                                      |

|                                  | LVDD [VL_BLAST]                      |                 | SA25–SA0                | VL, ROM, ISA, and                    |

|                                  | DTR, RTS, SOUT                       |                 |                         | PC Card Address                      |

| 8-Pin Serial Port                | CTS, DCD, DSR                        |                 | ROMCS1-ROMCS0           |                                      |

|                                  |                                      |                 | ROMRD                   | ROM/Flash Memory                     |

| -                                | RIN, SIN                             |                 | ROMWR                   | Control                              |

| Infrared Interface               | SIROUT                               |                 | IOR                     |                                      |

| -                                | SIRIN                                |                 | IOW                     | PC Card Command                      |

| Power                            | ACIN                                 |                 | MEMR                    | ISA Bus Command<br>and Reset         |

| Management<br>Interface          | BL2-BL1                              |                 | MEMW                    | and Reset                            |

| internace                        | BL0 [CLK_IO]                         |                 | RSTDRV                  |                                      |

| GPIOs                            | GPIO_CS0                             |                 | MCEL_A [[BNDSCN_TCK]]   |                                      |

|                                  | GPIO_CS1                             |                 | MCEH_A [[BNDSCN_TMS]]   |                                      |

| GPIO/External                    | GPIO_CS2 [[DBUFRDL]]                 |                 |                         |                                      |

| Buffer Control                   | GPIO_CS3 [[DBUFRDH]]                 |                 | RST_A [[BNDSCN_TDI]]    | De die ste d Cin ale                 |

|                                  | GPIO_CS4 [[DBUFOE]]                  |                 | REG_A [[BNDSCN_TDO]]    | Dedicated Single<br>Slot PC Card and |

| •                                |                                      | ÉlanSC400       |                         | Boundary Scan                        |

|                                  | GPIO_CS5 [IOCS16]                    | Microcontroller | RDY_A                   | Interface                            |

| •                                | GPIO_CS6 [IOCHRDY]                   | 292 BGA         | BVD1_A, BVD2_A          |                                      |

| GPIO/ISA                         | GPIO_CS7 [PIRQ1]<br>GPIO_CS8 [PIRQ0] |                 | WP_A                    |                                      |

| Interface                        | GPIO_CS9 [TC]                        |                 | WAIT_AB                 |                                      |

| •                                | GPIO_CS10 [AEN]                      |                 |                         |                                      |

| •                                | GPIO_CS11 [PDACK0]                   |                 | WE                      |                                      |

| •                                | GPIO_CS12 [PDRQ0]                    |                 | ICDIR                   |                                      |

| •                                | GPIO_CS13 [PCMA_VCC]                 |                 | GPIO31 [STRB] [MCEL_B]  |                                      |

| •                                | GPIO_CS14 [PCMA_VCC]                 |                 |                         |                                      |

| •                                | GPIO15 [PCMA_VPP2]                   |                 | GPIO30 [AFDT] [MCEH_B]  |                                      |

| GPIO/PC Card                     | GPIO16 [PCMB_VCC]                    |                 | GPIO29 [SLCTIN] [RST_B] |                                      |

| Power Control                    | GPIO17 [PCMB_VPP1]                   |                 | GPIO28 [INIT] [REG_B]   | Parallel Port or                     |

|                                  | GPIO18 [PCMB_VPP2]                   |                 | GPIO27 [ERROR] [CD_B]   | Second PC Card or                    |

| •                                | GPIO19 [LBL2]                        |                 | GPIO26 [PE] [RDY_B]     | GPIOs                                |

| •                                | GPIO20 [CD_A2]                       |                 |                         |                                      |

| •                                |                                      |                 | GPIO25 [ACK] [BVD1_B]   |                                      |

| Coor Koukoord                    | KBD_COL7                             |                 | GPIO24 [BUSY] [BVD2_B]  |                                      |

| Scan Keyboard<br>Columns/IRQs/XT | KBD_COL6-2 / PIRQ7-3                 |                 | GPIO23 [SLCT] [WP_B]    |                                      |

| Keyboard Interface               | KBD COL1-0 [XT_CLK/DATA]             |                 | GPIO22 [PPOEN]          |                                      |

| Reybourd Internate               | SUS_RES / KBD_ROW14                  |                 | GPIO21 [PPDWE]          |                                      |

| •                                | KBD_ROW13 [[R32BFOE]]                |                 |                         |                                      |

| 4                                | KBD_ROW12 [MCS16]                    |                 | 20KVTAL 1, 20KVTAL 2    |                                      |

| Scan Keyboard                    | KBD_ROW11 [SBHE]                     |                 | 32KXTAL1, 32KXTAL2      | 32-kHz Crystal                       |

| Rows/ISA Interface               | KBD_ROW10 [BALE]                     |                 | LF_INT, LF_LS           | Loop Filters                         |

|                                  | KBD_ROW9 [PIRQ2]                     |                 | LF_VID, LF_HS           |                                      |

| 4                                | KBD_ROW8 [PDRQ1]                     |                 | DEOET                   | Reset                                |

|                                  | KBD_ROW7 [PDACK1]                    |                 | RESET                   | 116361                               |

|                                  | KBD_ROW6 [MA12]                      |                 | V <sub>CC</sub> _RTC    |                                      |

| •                                | KBD_ROW5 [RAS3]                      |                 | BBATSEN                 | RTC                                  |

| Scan Keyboard                    | KBD_ROW4 [RAS2]                      |                 |                         |                                      |

| Rows/DRAM                        | KBD_ROW3 [RAS2]                      |                 | 051/5                   |                                      |

| Interface                        | KBD_ROW3 [CASH3]                     |                 | SPKR                    | Speaker                              |

| •                                |                                      |                 |                         | Boundary Seen                        |

| •                                | KBD_ROW1 [CASL3]                     |                 | BNDSCN_EN               | Boundary Scan<br>Enable              |

| Notes:                           | KBD_ROW0 [CASL2]                     |                 |                         |                                      |

|                                  |                                      |                 |                         |                                      |

/ =Two functions available on the pin at the same time. { } = Function during hardware reset. [ ] = Alternative function selected by firmware configuration. [[ ]] = Alternate function selected by a hardware configuration pin state at power-on reset. This does not apply to [[BNDSCN\_TCK]], [[BNDSCN\_TMS]], [[BNDSCN\_TDI]], and [[BNDSCN\_TDO]]. These alternate functions are enabled by the BNDSCN\_EN signal.

#### LOGIC SYMBOL—ÉLANSC410 MICROCONTROLLER

#### Notes:

/=Two functions available on the pin at the same time. { } = Function during hardware reset. [ ] = Alternative function selected by firmware configuration. [[]] = Alternate function selected by a hardware configuration pin state at power-on reset. This does not apply to [[BNDSCN\_TCK]], [[BNDSCN\_TMS]], [[BNDSCN\_TDI]], and [[BNDSCN\_TDO]]. These functions are enabled by the BNDSCN\_EN signal.

### TABLE OF CONTENTS

| Distinctive Characteristics                                                               |     |

|-------------------------------------------------------------------------------------------|-----|

| Élan™SC400 and ÉlanSC410 Microcontrollers                                                 | . 1 |

| ÉlanSC400 Microcontroller Only                                                            | 1   |

| General Description                                                                       | 2   |

| Block Diagram—ÉlanSC400 Microcontroller                                                   | 4   |

| Block Diagram—ÉlanSC410 Microcontroller                                                   |     |

| Logic Symbol—ÉlanSC400 Microcontroller                                                    | 6   |

| Logic Symbol—ÉlanSC410 Microcontroller                                                    | 7   |

| Related AMD Products                                                                      |     |

| E86™ Family Devices                                                                       |     |

| Related Documents                                                                         |     |

| Élan™SC400 Microcontroller Evaluation Board                                               |     |

| Third-Party Development Support Products                                                  |     |

| Customer Service                                                                          |     |

|                                                                                           |     |

| Architectural Overview                                                                    |     |

| Low-Voltage Am486 CPU Core                                                                |     |

| Power Management                                                                          |     |

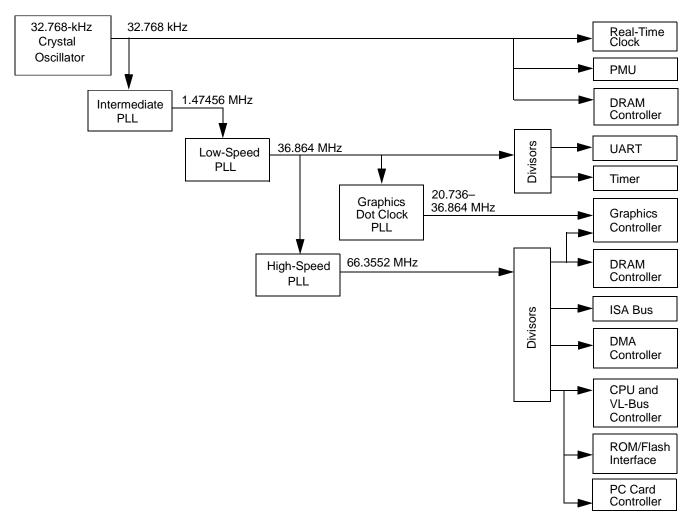

| Clock Generation                                                                          |     |

| ROM/Flash Memory Interface                                                                |     |

| DRAM Controller                                                                           |     |

| Integrated Standard PC/AT Peripherals                                                     |     |

| PC/AT Support Features                                                                    |     |

| Bidirectional Enhanced Parallel Port (EPP)                                                |     |

| Serial Port                                                                               |     |

| Keyboard Interfaces                                                                       | 17  |

| Programmable General-Purpose Inputs and Outputs                                           | 17  |

| Infrared Port for Wireless Communication                                                  | 17  |

| Dual PC Card Controller (ÉlanSC400 Microcontroller Only)                                  | 17  |

| Graphics Controller for CGA-Compatible Text and Graphics (ÉlanSC400 Microcontroller Only) |     |

| JTAG Test Features                                                                        |     |

| System Interfaces                                                                         | 18  |

| System Considerations                                                                     |     |

| Connection Diagram—ÉlanSC400 and ÉlanSC410 Microcontrollers                               |     |

| Pin Designations                                                                          |     |

| Pin Naming                                                                                |     |

| Pin Changes for the ÉlanSC410 Microcontroller                                             |     |

| Pin Designations (Pin Number)—ÉlanSC400 Microcontroller                                   |     |

| Pin Designations (Pin Name)—ÉlanSC400 Microcontroller                                     | 29  |

| Pin Designations (Pin Number)—ÉlanSC410 Microcontroller                                   | 23  |

| Pin Designations (Pin Name)—ÉlanSC410 Microcontroller                                     |     |

| Pin State Tables                                                                          |     |

| Pin State Tables                                                                          |     |

| Using the Pin State Tables                                                                |     |

| Signal Descriptions                                                                       |     |

| Multiplexed Pin Function Options                                                          |     |

| Using the Configuration Pins to Select Pin Functions                                      |     |

| Clocking                                                                                  |     |

| Clock Generation                                                                          |     |

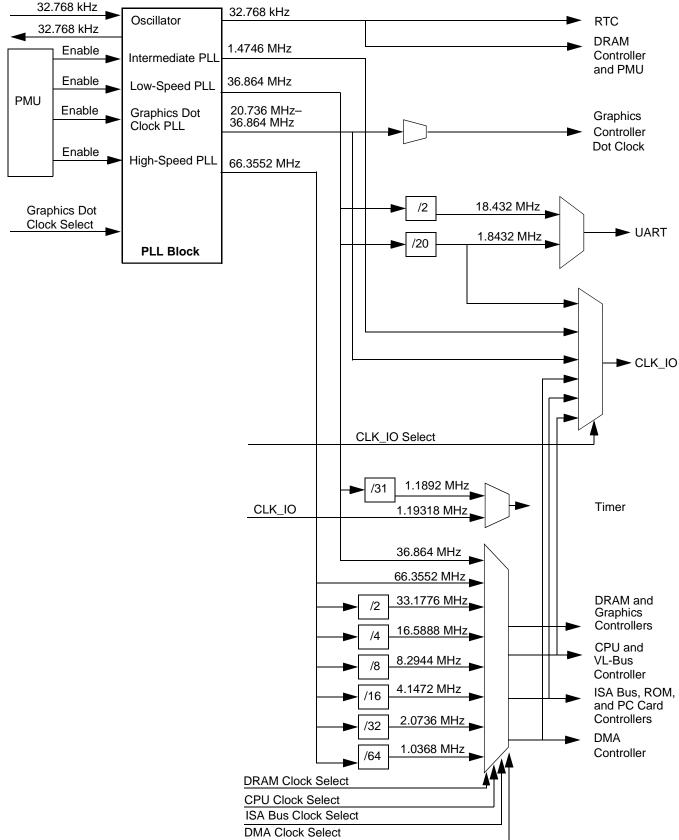

| Integrated Peripheral Clock Sources                                                       |     |

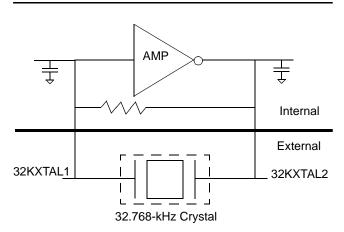

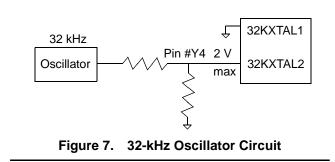

| 32-kHz Crystal Oscillator                                                                 |     |

| Loop Filters                                                                              |     |

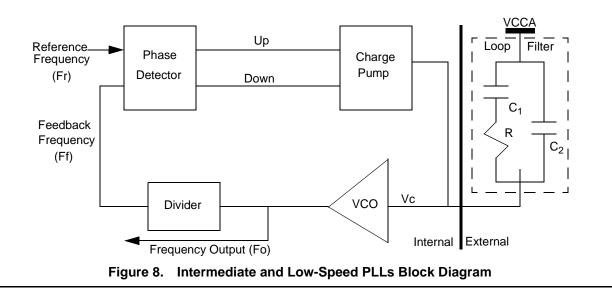

| Intermediate and Low-Speed PLLs                                                           | 79  |

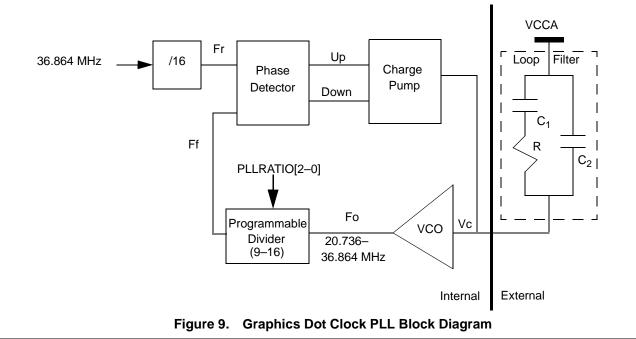

| Graphics Dot Clock PLL (ÉlanSC400 Microcontroller Only)                                   |     |

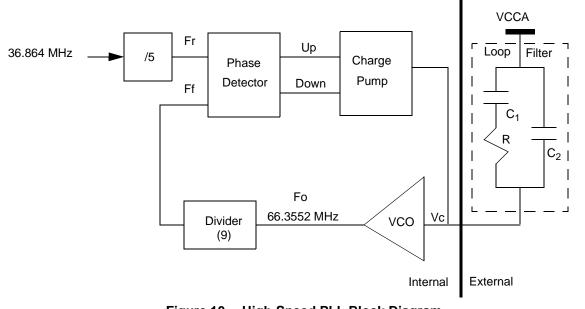

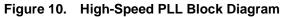

| High-Speed PLL                                                                 | 81  |

|--------------------------------------------------------------------------------|-----|

| Band Gap Block                                                                 | 81  |

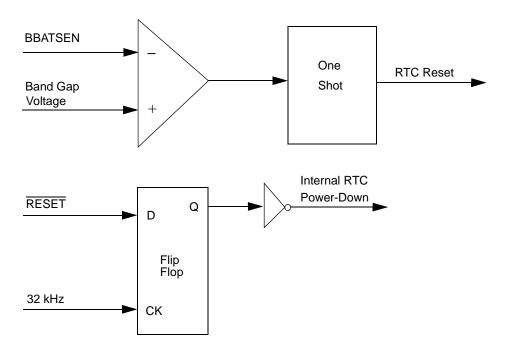

| RTC Voltage Monitor                                                            | 81  |

| Clock Specifications                                                           |     |

| Absolute Maximum Ratings                                                       | 86  |

| Operating Ranges                                                               | 86  |

| DC Characteristics Over Commercial and Industrial Operating Ranges             | 86  |

| Capacitance                                                                    | 87  |

| Typical Power Numbers                                                          | 88  |

| Power Requirements Under Different Power Management Modes                      | 88  |

| Derating Curves                                                                | 89  |

| AC Switching Characteristics and Waveforms                                     | 91  |

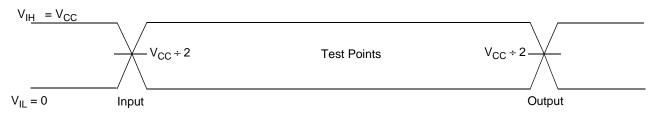

| Key to Switching Waveforms                                                     | 91  |

| AC Switching Test Waveforms                                                    | 91  |

| AC Switching Characteristics over Commercial and Industrial Operating Ranges . | 92  |

| Thermal Characteristics                                                        | 130 |

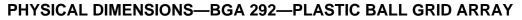

| Physical Dimensions—BGA 292—Plastic Ball Grid Array                            | 131 |

|                                                                                |     |

#### **LIST OF FIGURES**

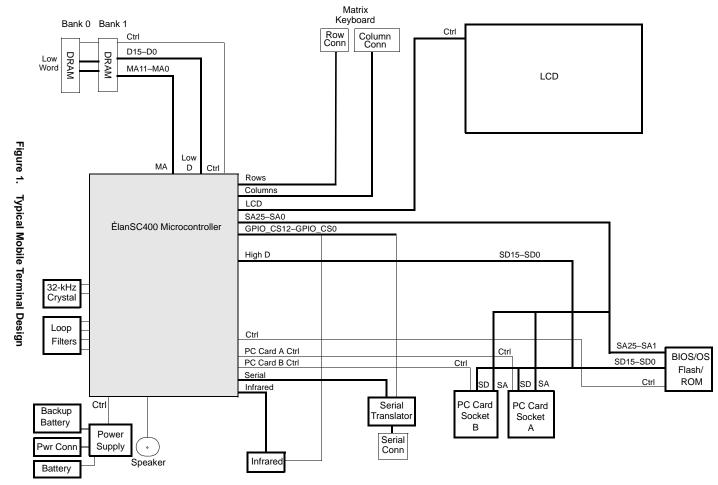

| Figure 1.  | Typical Mobile Terminal Design                                            |     |

|------------|---------------------------------------------------------------------------|-----|

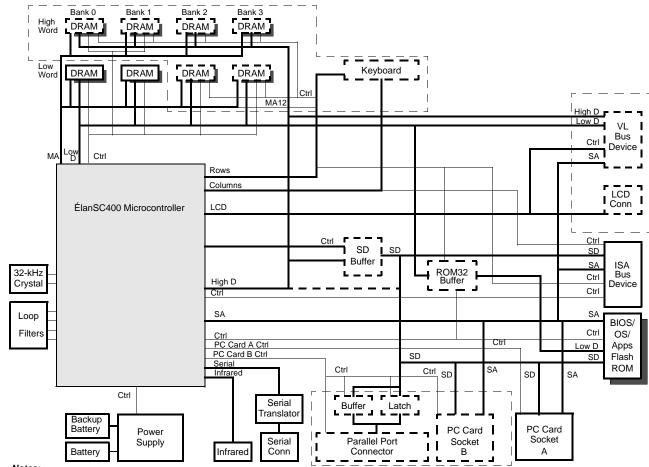

| Figure 2.  | System Diagram with Trade-offs—ÉlanSC400 Microcontroller                  | 22  |

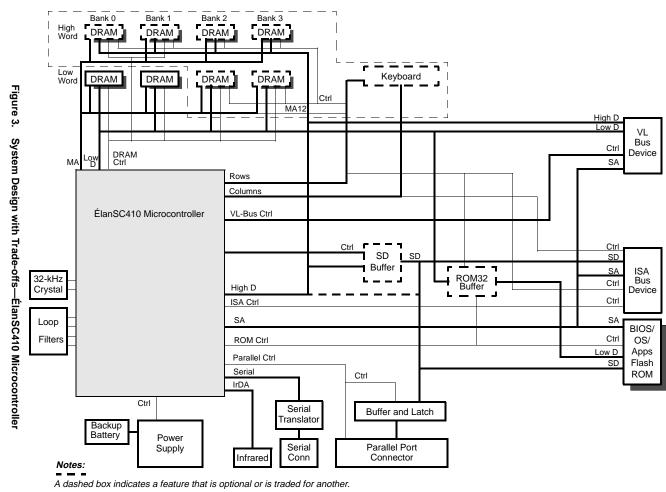

| Figure 3.  | System Design with Trade-offs—ÉlanSC410 Microcontroller                   |     |

| Figure 4.  | Clock Generation Block Diagram                                            | 76  |

| Figure 5.  | Clock Source Block Diagram                                                | 78  |

| Figure 6.  | 32-kHz Crystal Circuit                                                    | 79  |

| Figure 7.  | 32-kHz Oscillator Circuit                                                 |     |

| Figure 8.  | Intermediate and Low-Speed PLLs Block Diagram                             | 80  |

| Figure 9.  | Graphics Dot Clock PLL Block Diagram                                      | 81  |

| Figure 10. | High-Speed PLL Block Diagram                                              | 82  |

| Figure 11. | RTC Voltage Monitor Circuit                                               | 82  |

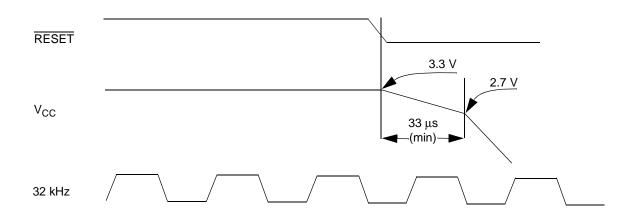

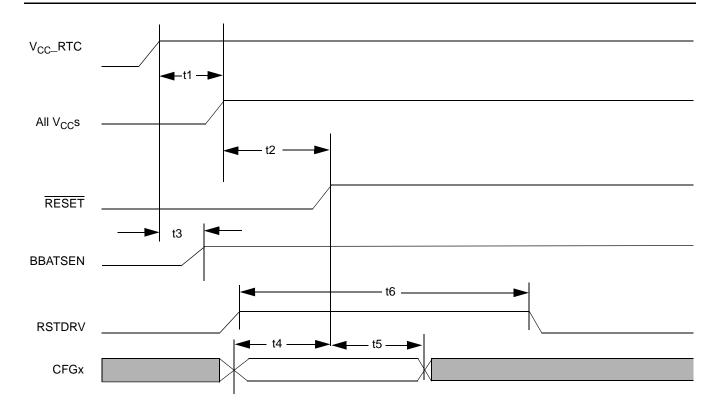

| Figure 12. | Timing Diagram for RTC-On Power-Down Sequence                             | 83  |

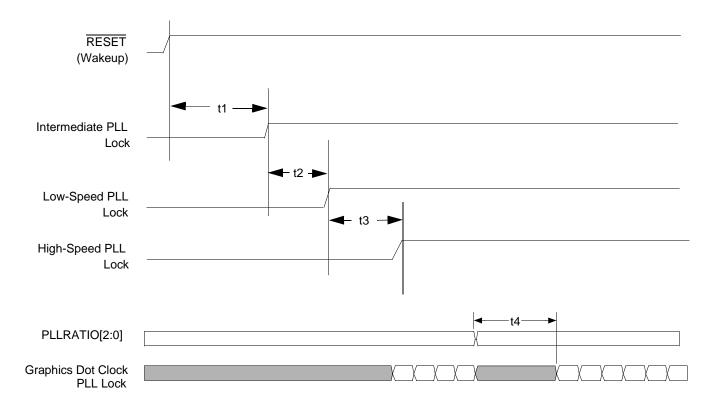

| Figure 13. | PLL Enabling Timing Sequence                                              |     |

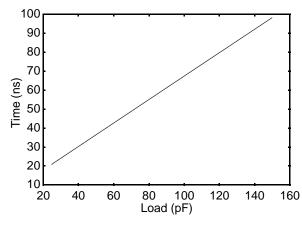

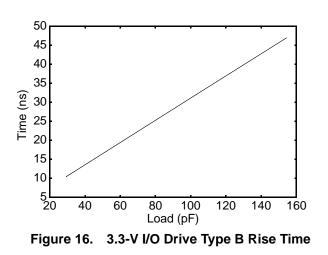

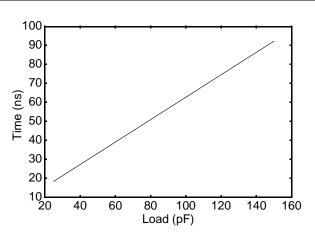

| Figure 14. | 3.3-V I/O Drive Type A Rise Time                                          | 89  |

| Figure 15. | 3.3-V I/O Drive Type A Fall Time                                          |     |

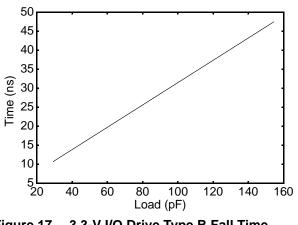

| Figure 16. | 3.3-V I/O Drive Type B Rise Time                                          | 89  |

| Figure 17. | 3.3-V I/O Drive Type B Fall Time                                          |     |

| Figure 18. | 3.3-V I/O Drive Type C Rise Time                                          | 90  |

| Figure 19. | 3.3-V I/O Drive Type C Fall Time                                          |     |

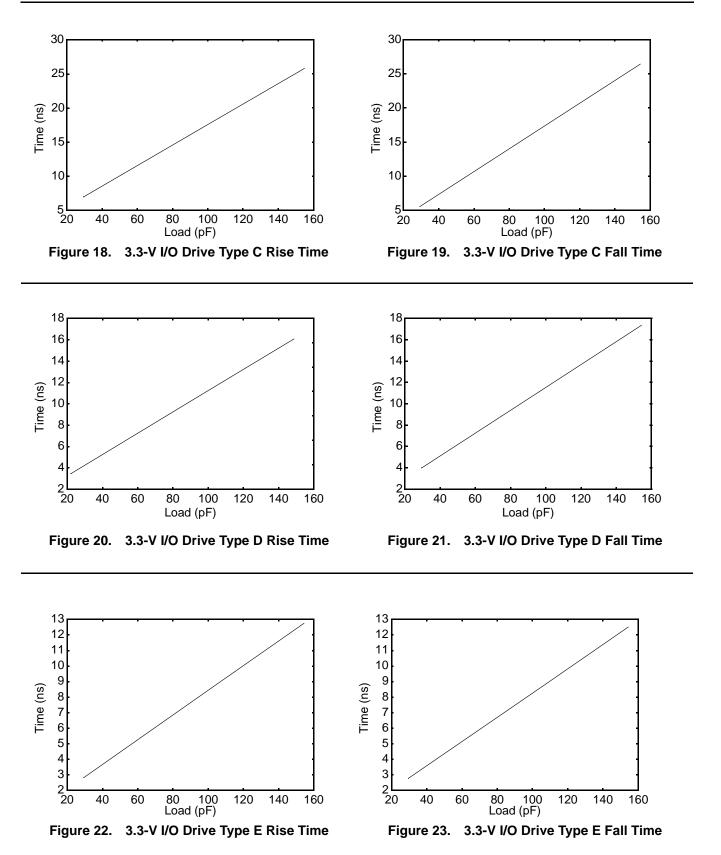

| Figure 20. | 3.3-V I/O Drive Type D Rise Time                                          | 90  |

| Figure 21. | 3.3-V I/O Drive Type D Fall Time                                          |     |

| Figure 22. | 3.3-V I/O Drive Type E Rise Time                                          |     |

| Figure 23. | 3.3-V I/O Drive Type E Fall Time                                          |     |

| Figure 24. | Power-Up Timing Sequence                                                  |     |

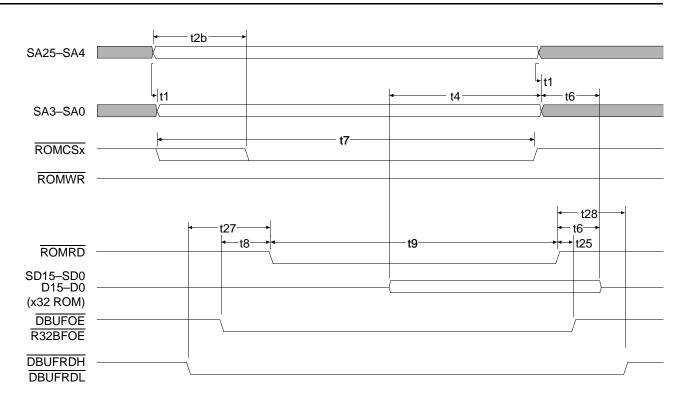

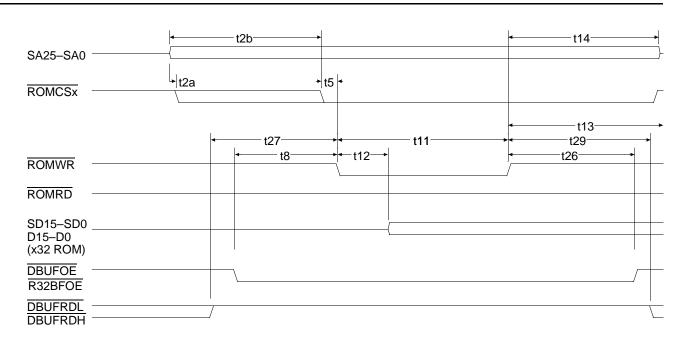

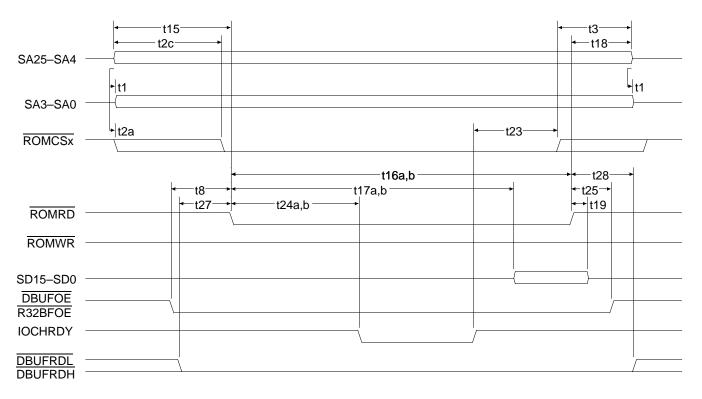

| Figure 25. | Fast Mode 8-/16-/32-Bit ROM/Flash Memory Read Cycle                       |     |

| Figure 26. | Fast Mode CPU Read of Three Consecutive Bytes from 8-Bit ROM/Flash Memory | 95  |

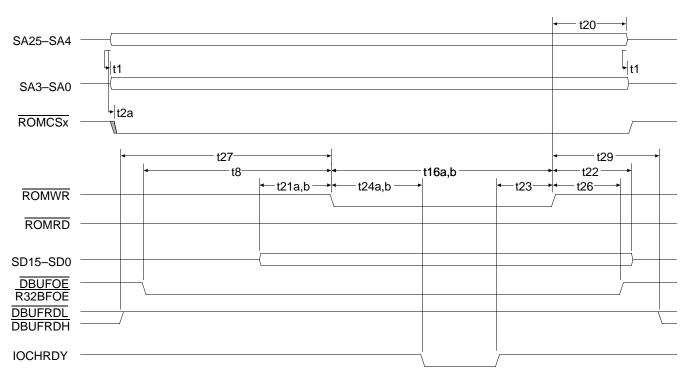

| Figure 27. | Fast Mode 8-/16-/32-Bit Flash Memory Write Cycles                         |     |

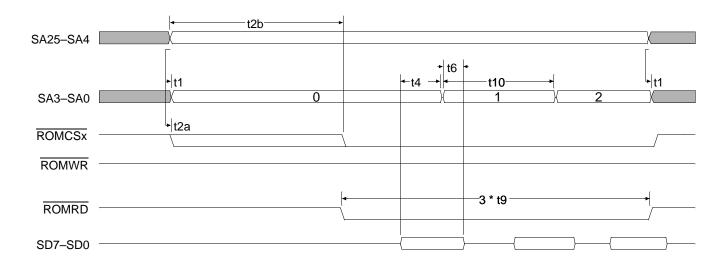

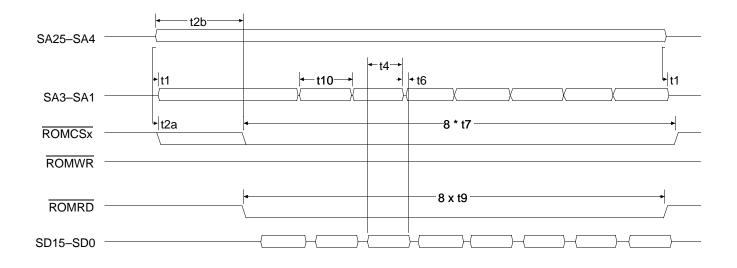

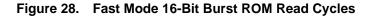

| Figure 28. | Fast Mode 16-Bit Burst ROM Read Cycles                                    |     |

| Figure 29. | Fast Mode CPU Burst Read from 32-Bit Burst Mode ROM/Flash Memory          |     |

| Figure 30. | Normal Mode 8-/16-Bit ROM/Flash Memory Read Cycles                        |     |

| Figure 31. | Normal Mode 8-/16-Bit Flash Memory Write Cycles                           | 97  |

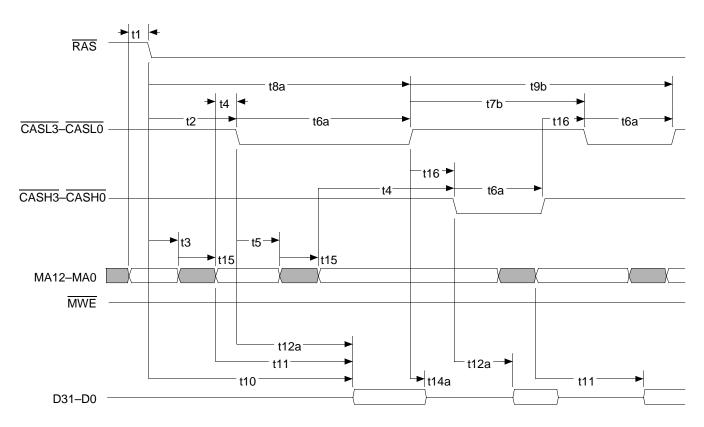

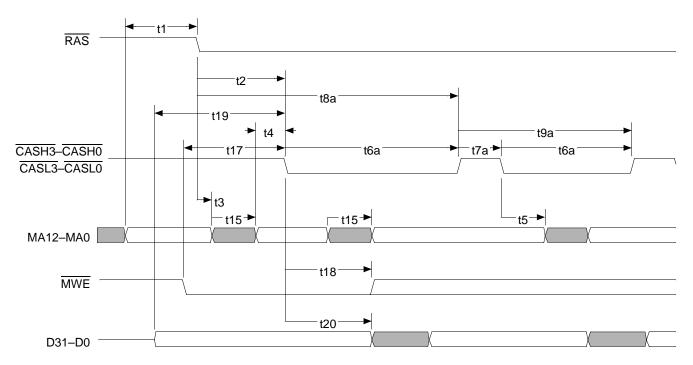

| Figure 32. | DRAM Page Hit Read, Interleaved                                           |     |

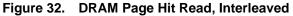

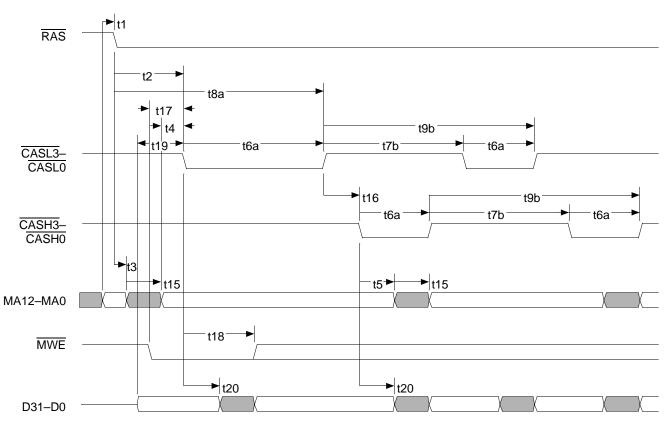

| Figure 33. | DRAM Page Hit Write, Interleaved                                          |     |

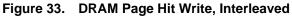

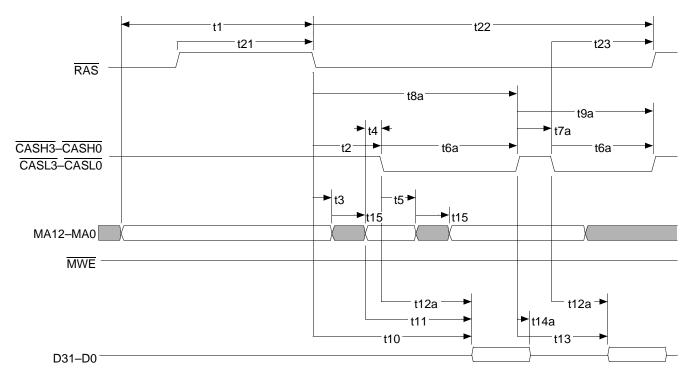

| Figure 34. | DRAM Page Miss Read, Interleaved                                          | 100 |

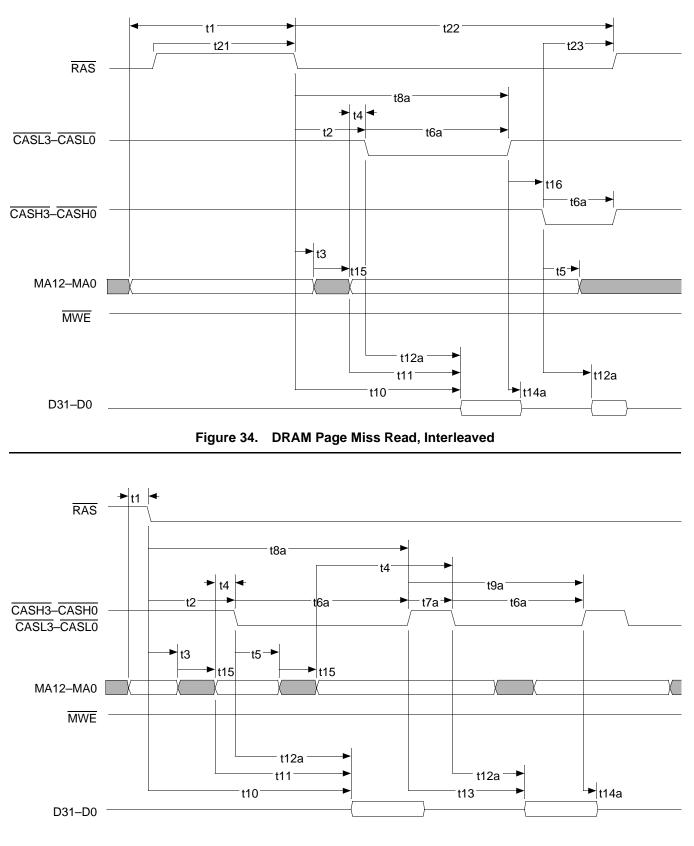

| Figure 35.<br>Figure 36. | DRAM Page Hit Read, Non-Interleaved<br>DRAM Page Hit Write, Non-Interleaved |     |

|--------------------------|-----------------------------------------------------------------------------|-----|

| Figure 37.               | DRAM Page Miss Read, Non-Interleaved                                        |     |

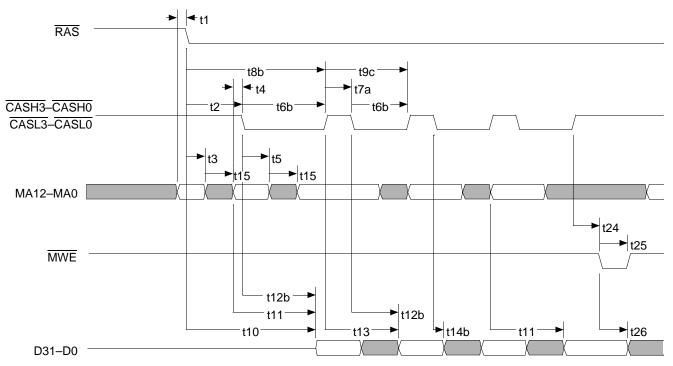

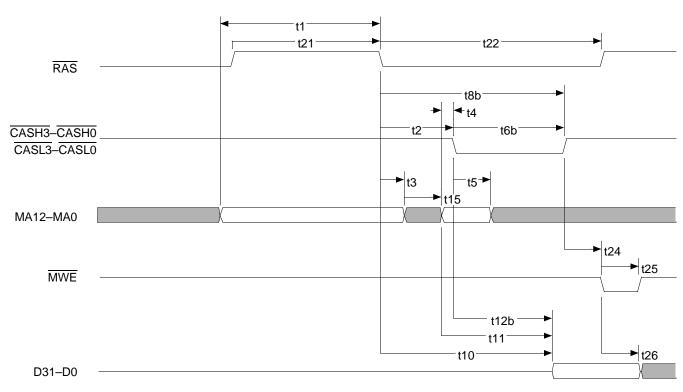

| Figure 38.               | EDO DRAM Page Hit Read, Non-Interleaved                                     |     |

| Figure 39.               | EDO DRAM Page Miss Read, Non-Interleaved                                    |     |

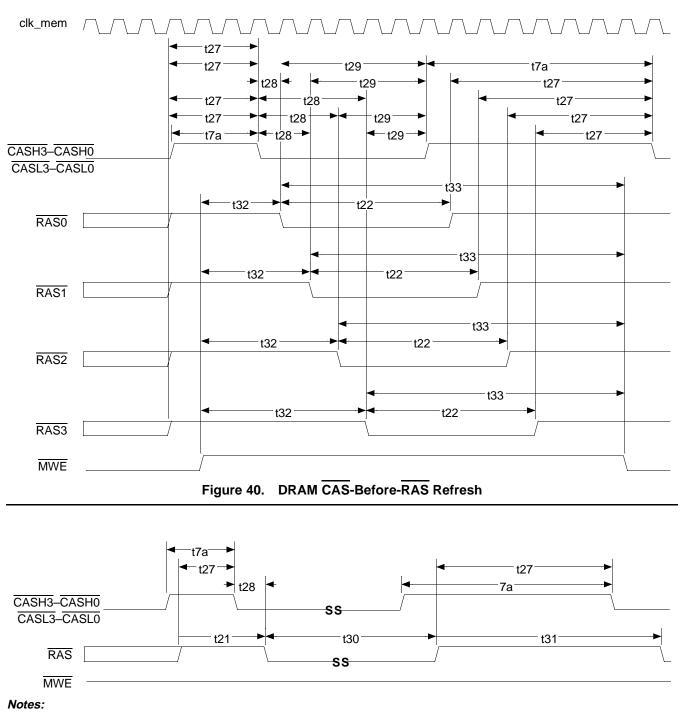

| Figure 40.               | DRAM CAS-Before-RAS Refresh                                                 | 103 |

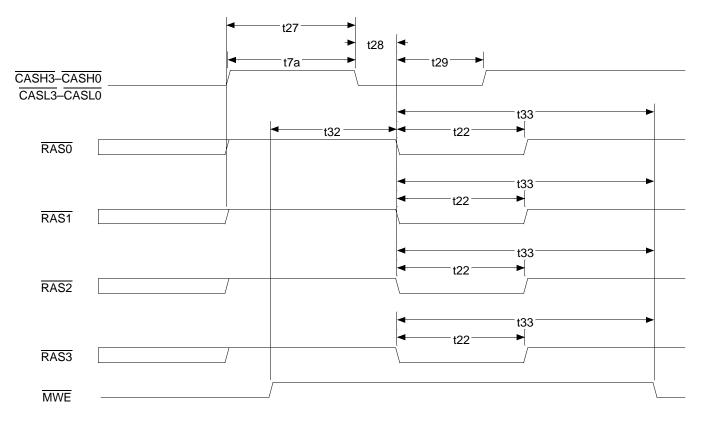

| Figure 41.               | DRAM Self-Refresh                                                           | 103 |

| Figure 42.               | DRAM Slow Refresh                                                           | 104 |

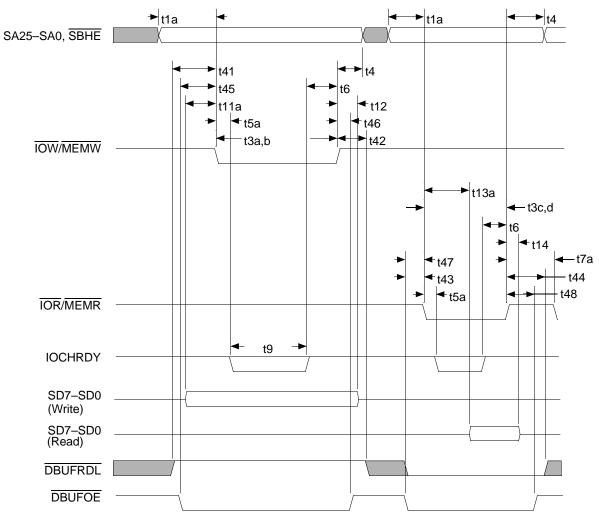

| Figure 43.               | 8-Bit ISA Bus Cycles                                                        |     |

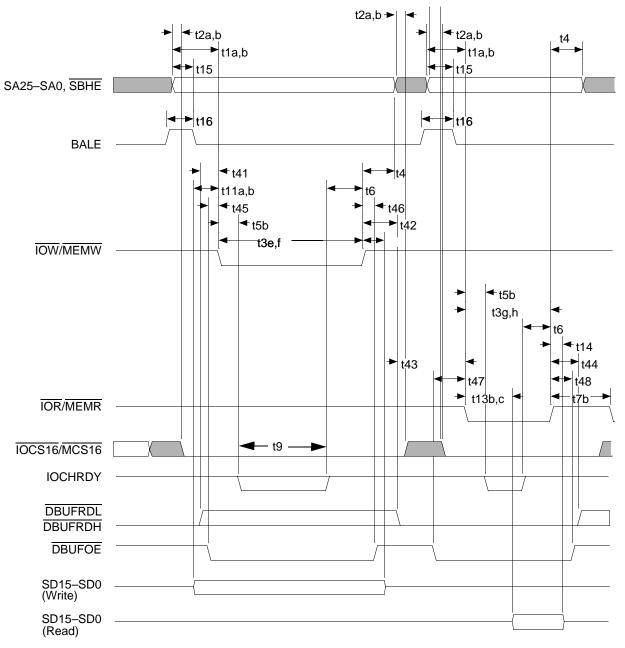

| Figure 44.               | 16-Bit ISA Bus Cycles                                                       | 108 |

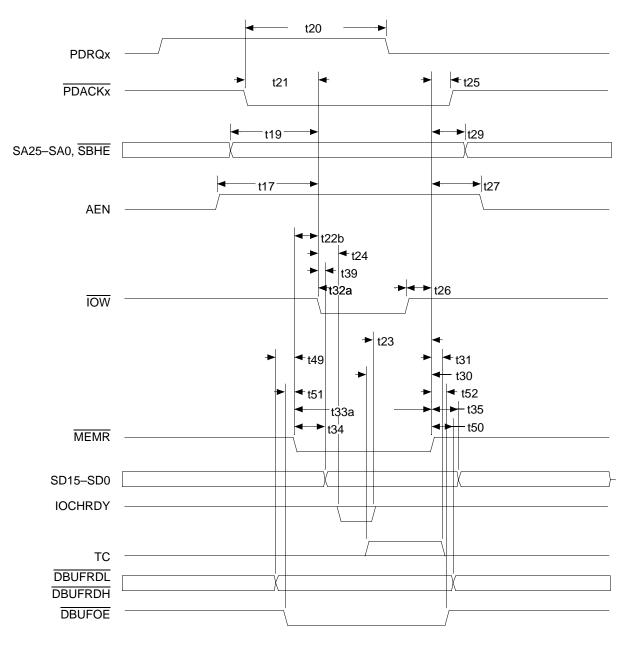

| Figure 45.               | ISA DMA Read Cycle                                                          |     |

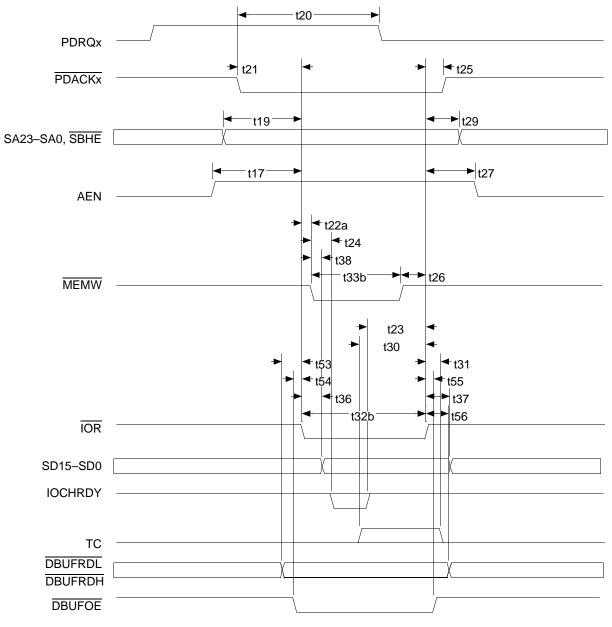

| Figure 46.               | ISA DMA Write Cycle                                                         |     |

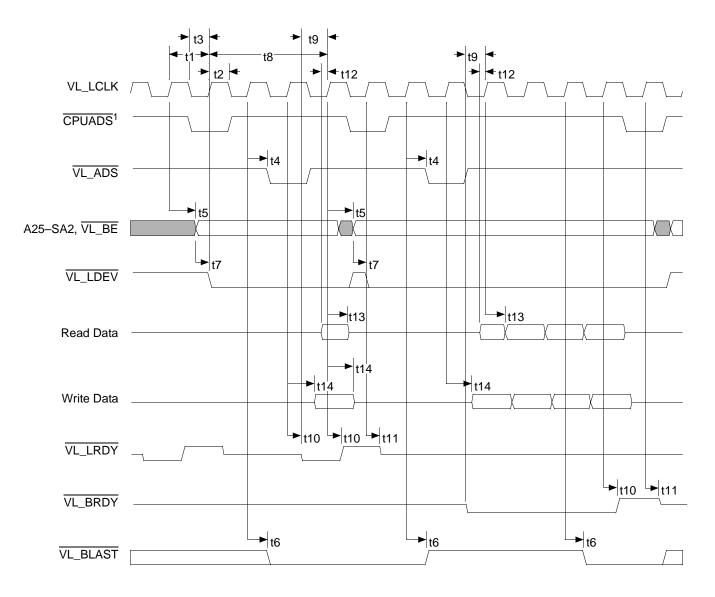

| Figure 47.               | VESA Local Bus Cycles                                                       |     |

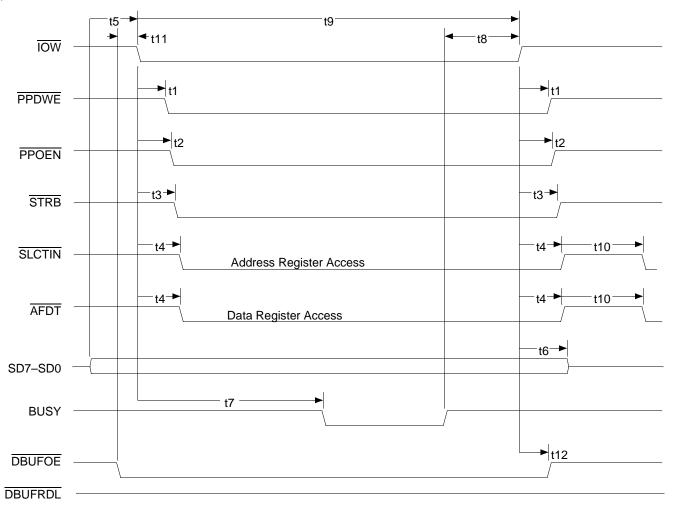

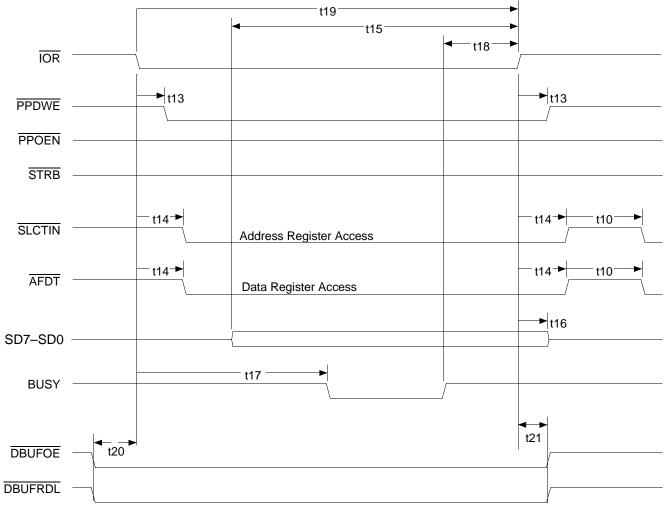

| Figure 48.               | EPP Parallel Port Write Cycle                                               |     |

| Figure 49.               | EPP Parallel Port Read Cycle                                                | 115 |

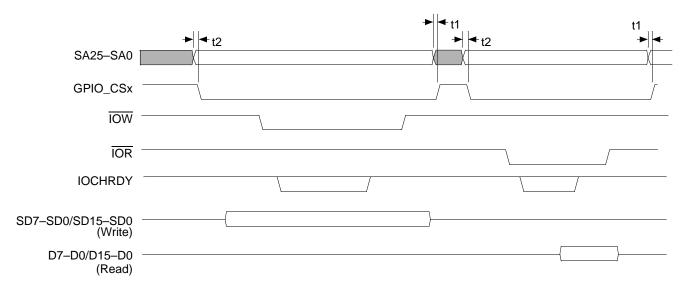

| Figure 50.               | I/O Decode (R/W), Address Decode Only                                       |     |

| Figure 51.               | I/O Decode (R/W), Command Qualified                                         |     |

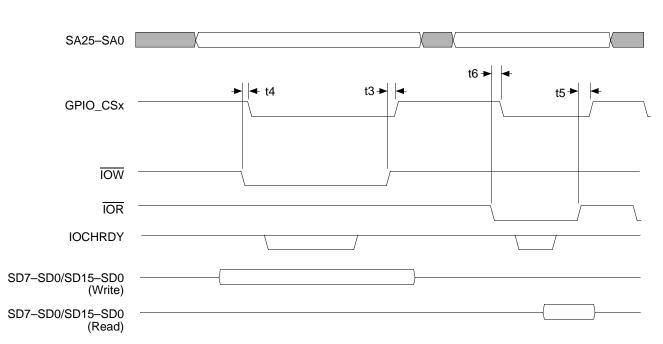

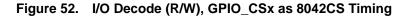

| Figure 52.               | I/O Decode (R/W), GPIO_CSx as 8042CS Timing                                 | 117 |

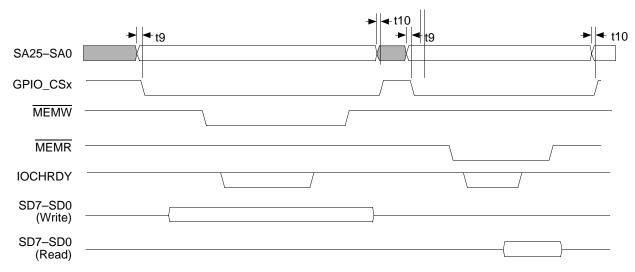

| Figure 53.               | Memory CS Decode (R/W), Address Decode Only                                 | 117 |

| Figure 54.               | Memory CS Decode (R/W), Command Qualified                                   |     |

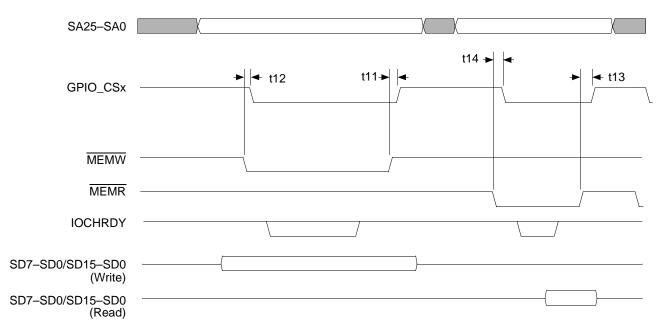

| Figure 55.               | PC Card Attribute Memory Read Cycle (ÉlanSC400 Microcontroller Only)        |     |

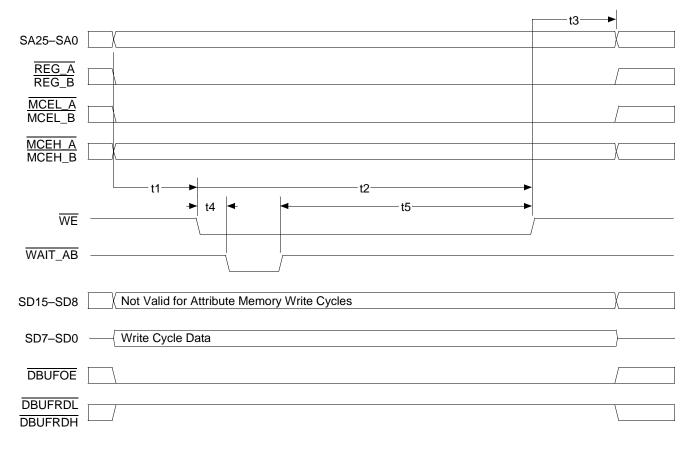

| Figure 56.               | PC Card Attribute Memory Write Cycle (ÉlanSC400 Microcontroller Only)       | 121 |

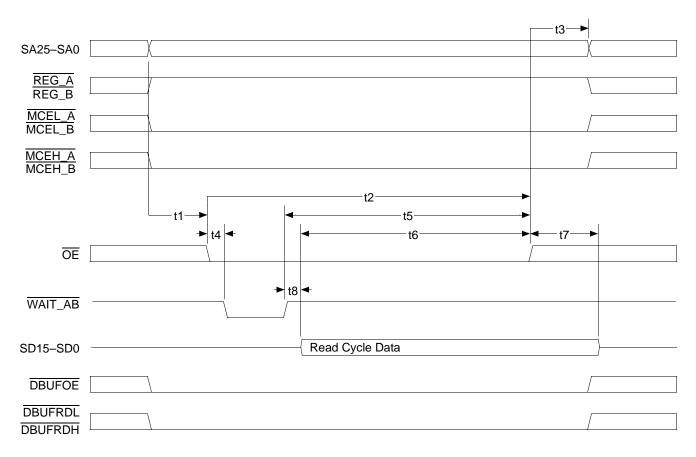

| Figure 57.               | PC Card Common Memory Read Cycle (ÉlanSC400 Microcontroller Only)           | 122 |

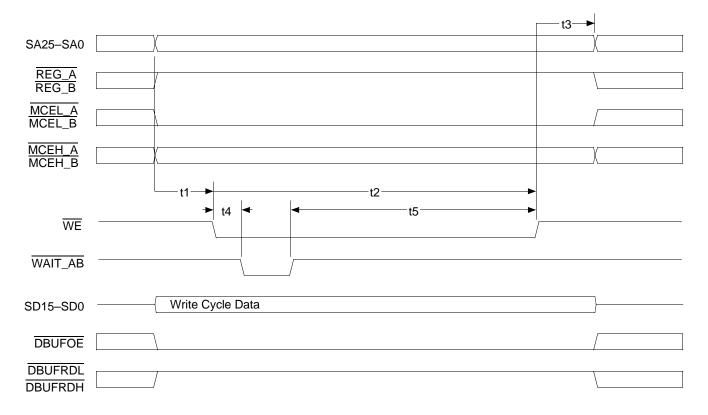

| Figure 58.               | PC Card Common Memory Write Cycle (ÉlanSC400 Microcontroller Only)          | 123 |

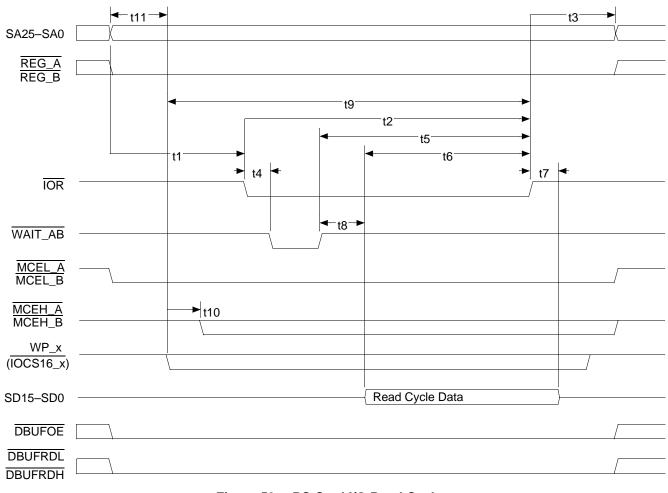

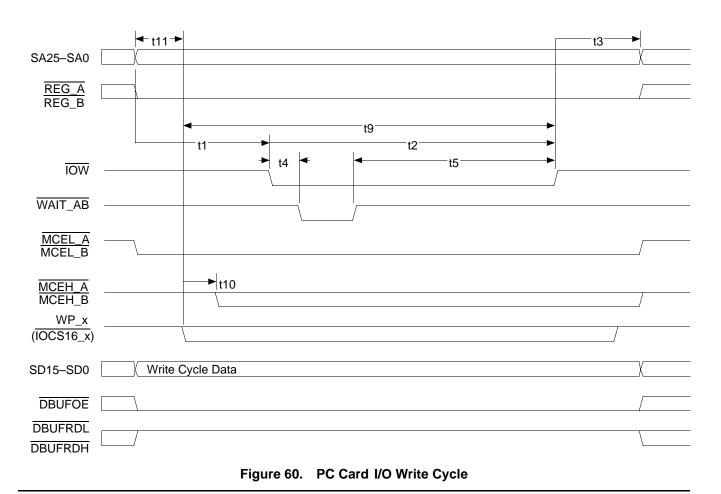

| Figure 59.               | PC Card I/O Read Cycle                                                      | 124 |

| Figure 60.               | PC Card I/O Write Cycle                                                     | 125 |

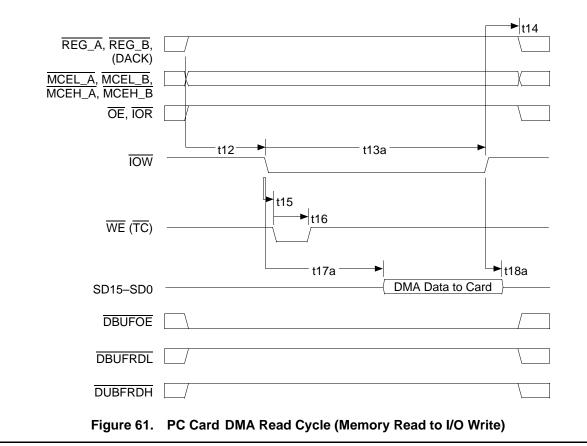

| Figure 61.               | PC Card DMA Read Cycle (Memory Read to I/O Write)                           | 126 |

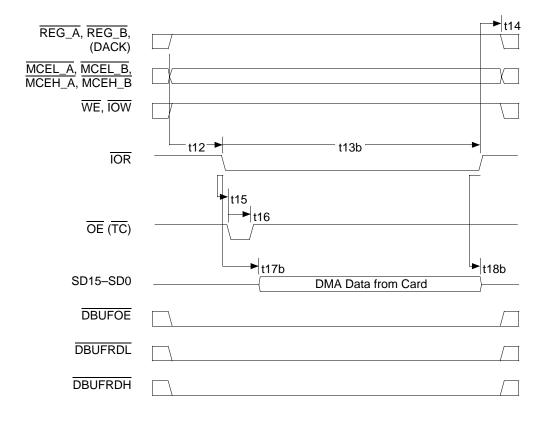

| Figure 62.               | PC Card DMA Write Cycle (I/O Read to Memory Write)                          | 127 |

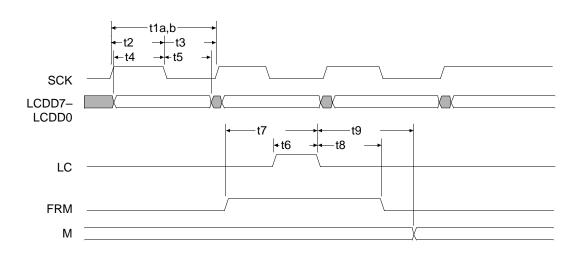

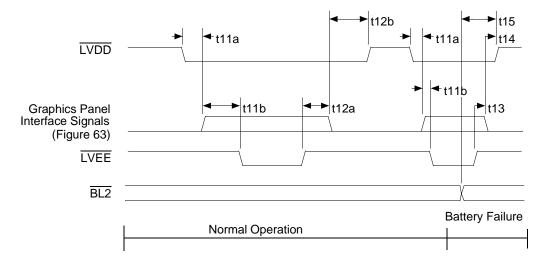

| Figure 63.               | Graphics Panel Interface Timing (ÉlanSC400 Microcontroller Only)            |     |

| Figure 64.               | Graphics Panel Power Sequencing (ÉlanSC400 Microcontroller Only)            |     |

|                          |                                                                             |     |

#### LIST OF TABLES

| Product Comparison—ÉlanSC400 and ÉlanSC410 Microcontrollers | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drive Output Description                                    | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin Type Abbreviations                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Power Pin Type Abbreviations                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Power-Down Groups                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—System Interface                            | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—Memory Interface                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—GPIOs/Parallel Port/PC Card Socket B        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—GPIOs/ISA Bus                               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—GPIOs/System Data (SD) Buffer Control       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—GPIOs                                       | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin State Table—Infrared Interface                          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—Keyboard Interface                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—PC Card Socket A                            | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—Graphics Controller/VESA Local Bus Control  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—Miscellaneous                               | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin State Table—Power and Ground                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Signal Description Table                                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multiplexed Pin Configuration Options                       | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pinstrap Bus Buffer Options                                 | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                             | Drive Output Description<br>Pin Type Abbreviations<br>Power Pin Type Abbreviations<br>Power-Down Groups<br>Pin State Table—System Interface<br>Pin State Table—Memory Interface<br>Pin State Table—GPIOs/Parallel Port/PC Card Socket B<br>Pin State Table—GPIOs/Parallel Port/PC Card Socket B<br>Pin State Table—GPIOs/System Data (SD) Buffer Control<br>Pin State Table—GPIOs<br>Pin State Table—GPIOs<br>Pin State Table—GPIOs<br>Pin State Table—GPIOs<br>Pin State Table—Infrared Interface<br>Pin State Table—Lefter Control Interface<br>Pin State Table—Veyboard Interface<br>Pin State Table—Card Socket A<br>Pin State Table—Graphics Controller/VESA Local Bus Control<br>Pin State Table—Miscellaneous<br>Pin State Table—Power and Ground<br>Signal Description Table<br>Multiplexed Pin Configuration Options |

| Table 22. | CFG0 and CFG1 Configuration                                                         | 74   |

|-----------|-------------------------------------------------------------------------------------|------|

| Table 23. | CFG2 Configuration (ÉlanSC400 microcontroller only)                                 | 74   |

| Table 24. | CFG3 Configuration                                                                  | 75   |

| Table 25. | BNDSCN_EN Configuration                                                             | 75   |

| Table 26. | Integrated Peripheral Clock Sources                                                 |      |

| Table 27. | Frequency Selection Control for Graphics Dot Clock PLL                              | 80   |

| Table 28. | Loop-Filter Component Specification for PLLs                                        | 84   |

| Table 29. | Analog V <sub>CC</sub> (VCCA) Specification                                         |      |

| Table 30. | 32.768-kHz Crystal Characteristics                                                  |      |

| Table 31. | Start-Up Time Specifications PLLs                                                   | 84   |

| Table 32. | PLL Jitter Specification                                                            | 85   |

| Table 33. | Operating Voltage (Commercial and Industrial)                                       | 87   |

| Table 34. | Power Estimates                                                                     | 88   |

| Table 35. | Power-On Reset Cycle                                                                | 92   |

| Table 36. | ROM/Flash Memory Cycles                                                             | 93   |

| Table 37. | DRAM Cycles                                                                         | . 98 |

| Table 38. | ISA Cycles 1                                                                        | 105  |

| Table 39. | VESA Local Bus Cycles                                                               | 111  |

| Table 40. | Parallel Port Cycles                                                                | 113  |

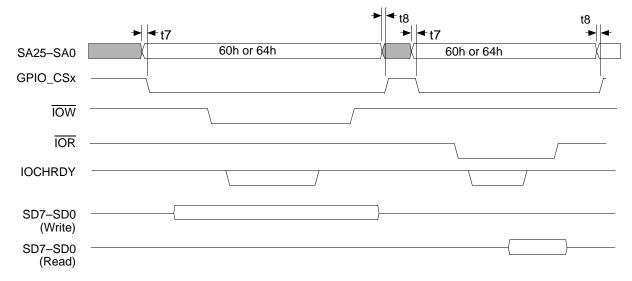

| Table 41. | General-Purpose Input/Output Cycles 1                                               |      |

| Table 42. | PC Card Cycles—ÉlanSC400 Microcontroller Only 1                                     | 119  |

| Table 43. | PC Card Attribute Memory Read Function (ÉlanSC400 Microcontroller Only) 1           | 120  |

| Table 44. | PC Card Attribute Memory Write Function (ÉlanSC400 Microcontroller Only) 1          | 121  |

| Table 45. | PC Card Common Memory Read Function (ÉlanSC400 Microcontroller Only) 1              |      |

| Table 46. | PC Card Common Memory Write Function (ÉlanSC400 Microcontroller Only) 1             |      |

| Table 47. | PC Card I/O Read Function (ÉlanSC400 Microcontroller Only)                          | 124  |

| Table 48. | PC Card I/O Write Function (ÉlanSC400 Microcontroller Only)                         |      |

| Table 49. | PC Card DMA Read Function (ÉlanSC400 Microcontroller Only) 1                        |      |

| Table 50. | PC Card DMA Write Function (ÉlanSC400 Microcontroller Only) 1                       | 127  |

| Table 51. | LCD Graphics Controller Cycles—ÉlanSC400 Microcontroller Only                       |      |

| Table 52. | Thermal Resistance $\Psi_{J-T}$ and $\theta_{JA}$ (°C/W) for the 292-BGA Package) 1 | 130  |

| Table 53. | Maximum T <sub>A</sub> at Various Airflows in °C                                    | 130  |

#### **RELATED AMD PRODUCTS**

| E86 <sup>™</sup> Fam | ily Devices                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Device               | Description                                                                                                                                 |

| 80C186               | 16-bit microcontroller                                                                                                                      |

| 80C188               | 16-bit microcontroller with 8-bit external data bus                                                                                         |

| 80L186               | Low-voltage, 16-bit microcontroller                                                                                                         |

| 80L188               | Low-voltage, 16-bit microcontroller with 8-bit external data bus                                                                            |

| Am186™EM             | High-performance, 80C186-compatible, 16-bit embedded microcontroller                                                                        |

| Am188™EM             | High-performance, 80C188-compatible, 16-bit embedded microcontroller with 8-bit external data bus                                           |

| Am186EMLV            | High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller                                                           |

| Am188EMLV            | High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit external data bus                              |

| Am186ES              | High-performance, 80C186-compatible, 16-bit embedded microcontroller                                                                        |

| Am188ES              | High-performance, 80C188-compatible, 16-bit embedded microcontroller with 8-bit external data bus                                           |

| Am186ESLV            | High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller                                                           |

| Am188ESLV            | High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit external data bus                              |

| Am186ED              | High-performance, 80C186- and 80C188-compatible, 16-bit embedded microcontroller with 8- or 16-bit external data bus                        |

| Am186EDLV            | High-performance, 80C186- and 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8- or 16-bit external data bus           |

| Am186ER              | High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller with 32 Kbyte of internal RAM                             |

| Am188ER              | High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit external data bus and 32 Kbyte of internal RAM |

| Am186CC              | High-performance, 80C186-compatible 16-bit embedded communications controller                                                               |

| Am186CH              | High-performance, 80C186-compatible 16-bit embedded HDLC microcontroller                                                                    |

| Am186CU              | High-performance, 80C186-compatible 16-bit embedded USB microcontroller                                                                     |

| Élan™SC300           | High-performance, highly integrated, low-voltage, 32-bit embedded microcontroller                                                           |

| ÉlanSC310            | High-performance, single-chip, 32-bit embedded PC/AT microcontroller                                                                        |

| ÉlanSC400            | Single-chip, low-power, PC/AT-compatible microcontroller                                                                                    |

| ÉlanSC410            | Single-chip, PC/AT-compatible microcontroller                                                                                               |

| Am386®DX             | High-performance, 32-bit embedded microprocessor with 32-bit external data bus                                                              |

| Am386®SX             | High-performance, 32-bit embedded microprocessor with 16-bit external data bus                                                              |

| Am486®DX             | High-performance, 32-bit embedded microprocessor with 32-bit external data bus                                                              |

#### **Related Documents**

The following documents provide additional information regarding the ÉlanSC400 and ÉlanSC410 microcontrollers.

- ÉlanSC400 and ÉlanSC410 User's Manual, order #21030

- ÉlanSC400 Register Set Reference Manual, order #21032

- ÉlanSC400 Register Set Reference Manual Amendment, order #21032A/1

- ÉlanSC400 Evaluation Board User's Manual, order #21906

- ÉlanSC400 Microcontroller and Windows CE μforCE Demonstration System User's Manual, order #21892

- ROMCSO Redirection to PC Card Socket A on the ÉlanSC400 Microcontroller Application Note, order #21643

#### Élan<sup>™</sup>SC400 Microcontroller Evaluation Board

The Élan<sup>™</sup>SC400 microcontroller evaluation board is a stand-alone evaluation platform for the ÉlanSC400 and ÉlanSC410 microcontrollers.

As a test and development platform for designs based on the ÉlanSC400 and ÉlanSC410 microcontrollers, this AMD product is used by system designers to experiment with design trade-offs, make power measurements, and develop software. Contact your local AMD sales office for more information on evaluation board availability and pricing.

#### **Third-Party Development Support Products**

The FusionE86<sup>SM</sup> Program of Partnerships for Application Solutions provides the customer with an array of products designed to meet critical time-tomarket needs. Products and solutions available from the AMD FusionE86 partners include protocol stacks, emulators, hardware and software debuggers, boardlevel products, and software development tools, among others.

In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

#### **Customer Service**

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86<sup>™</sup> and Comm86<sup>™</sup> family hardware and software development questions.

#### Hotline and World Wide Web Support

For answers to technical questions, AMD provides e-mail support as well as a toll-free number for direct access to our corporate applications hotline.

The AMD World Wide Web home page provides the latest product information, including technical information and data on upcoming product releases. In addition, EPD CodeKit software on the Web site provides tested source code example applications.

#### **Corporate Applications Hotline**

| (800) 222-9323      | Toll-free for U.S. and Canada |

|---------------------|-------------------------------|

| 44-(0) 1276-803-299 | U.K. and Europe hotline       |

Additional contact information is listed on the back of this datasheet. For technical support questions on all E86 and Comm86 products, send e-mail to **epd.support@amd.com**.

#### World Wide Web Home Page

To access the AMD home page, go to: **www.amd.com**. Then follow the **Embedded Processors** link for information about E86 and Comm86 products.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to **webmaster@amd.com**.

#### **Documentation and Literature**

Free information such as data books, user's manuals, data sheets, application notes, the  $E86^{TM}$  Family *Products and Development Tools CD*, order #21058, and other literature is available with a simple phone call. Internationally, contact your local AMD sales office for product literature. Additional contact information is listed on the back of this data sheet.

#### Literature Ordering

| (800) 222-9323 | Toll-free for U.S. and Canada |

|----------------|-------------------------------|

| (512) 602-5651 | Direct dial worldwide         |

| (512) 602-7639 | Fax                           |

#### **ARCHITECTURAL OVERVIEW**

The architectural goals of the ÉlanSC400 and ÉlanSC410 microcontrollers included a focus on CPU performance, CPU-to-memory performance, and internal graphics controller (ÉlanSC400 microcontroller only) performance. The resulting architecture includes several distinguishing features of interest to the system designer:

- The main system DRAM is shared between the CPU and graphics controller, so that the graphics controller can be serviced quickly to maintain video display performance at higher panel resolutions. The internal unified memory architecture (UMA) implemented on the ÉlanSC400 and ÉlanSC410 microcontrollers means lower cost and less complication for the system designer, with only one DRAM interface, fewer pins, and a much smaller board for many designs.

- CPU-to-memory performance is critical for both DRAM and ROM accesses. The CPU on the ÉlanSC400 microcontroller has a concurrent path to the ROM/Flash memory interface and can execute code out of ROM/Flash memory at the same time as the graphics controller is accessing DRAM for a screen refresh. Many system designs can take advantage of this concurrency without sacrificing performance.

- The ROM/Flash memory interface provides the flexibility to optimize the performance of ROM cycles, including the support of burst-mode ROMs. This is beneficial because products based on the ÉlanSC400 and ÉlanSC410 microcontrollers may be implemented such that the operating system or application programs are executed from ROM.

- Because the microcontrollers support a large number of external buses and interfaces, the address and data buses are shared between the various interfaces to reduce pin count on the chip.

These features result in a versatile architecture that can use various combinations of data bus sizes to achieve cost and performance goals. The architecture provides maximum performance and flexibility for highend vertical applications, but contains functionality for a wider horizontal market that may demand less performance.

- A typical lower performance/lower cost system might implement 16-bit DRAM banks, an 8-bit ISA bus, an 8/16-bit PC Card bus, and use the internal graphic controller.

- A higher performance, full-featured system might include 32-bit DRAM, VL-bus to an external graphics controller, and a 16-bit ISA/PC Card bus.

The following basic data bus configuration rules apply. (A complete list of feature trade-offs to be considered in system design can be found in "System Considerations" on page 20.)

When the internal graphics controller on the ÉlanSC400 microcontroller is enabled, DRAM is always 16 bits wide, and no 32-bit targets are supported. This is because the graphics controller needs a guaranteed short latency for adequate video performance. If either 32-bit DRAMs, 32-bit ROMs, or the VL-bus is enabled, the internal graphics controller is unavailable.

Note that, as a derivative of the original ÉlanSC400 microcontroller, the ÉlanSC410 microcontroller shares the primary architectural characteristics of the ÉlanSC400 microcontroller described above, minus the graphics controller and PCMCIA interfaces.

The following sections provide an overview of the features of the ÉlanSC400 and ÉlanSC410 microcontrollers, including on-chip peripherals and system interfaces.