# **DASL Digital Adapter for Subscriber Loops**

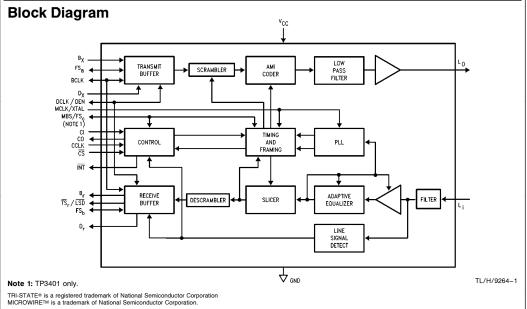

transceivers for data transmission on twisted pair subscriber loops. They are built on National's double poly microCMOS process, and require only a single +5 Volt supply. Alternate Mark Inversion (AMI) line coding, in which binary '1's are alternately transmitted as a positive pulse then a negative pulse, is used to ensure low error rates in the presence of noise with lower emi radiation than other codes such as Biphase (Manchester).

Full-duplex transmission at 144 kb/s is achieved on a single twisted wire pair using a burst-mode technique (Time Compression Multiplexed). Thus the device operates as an ISDN 'U' Interface for short loop applications, typically in a PBX environment, providing transmission for 2 B channels and 1 D channel. On #24 cable, the range is at least 1.8 km (6k ft).

System timing is based on a Master/Slave configuration, with the line card end being the Master which controls loop timing and synchronisation. All timing sequences necessary for loop activation and de-activation are generated on-chip. Selection of Master and Slave mode operation is programmed via the Microwire Control Interface.

A 2.048 MHz clock, which may be synchronized to the system clock, controls all transmission-related timing functions. For the TP3401, this clock must be provided from an exter-

nal source; the TP3402 includes an oscillator circuit requiring an external crystal. The TP3403 includes the functions of both the TP3401 and the TP3402.

#### **Features**

Complete ISDN PBX 2-Wire Data Transceiver including:

- 2 B plus D channel interface for PBX U' Interface

- 144 kb/s full-duplex on 1 twisted pair using Burst Mode

- Loop range up to 6 kft (#24AWG)

- Alternate Mark Inversion coding with transmit filter and scrambler for low emi radiation

- Adaptive line equalizer

- On-chip timing recovery, no external components

- Standard TDM interface for B channels

- Separate interface for D channel

- 2.048 MHz master clock

- Driver for line transformer

- 4 loop-back test modes

- Single +5V supply

- MICROWIRE™ compatible serial control interface

- Applications in:

PBX Line Cards

**Terminals**

Regenerators

■ Available in both 20-pin DIP and 28-pin PLCC

RRD-B30M115/Printed in U. S. A.

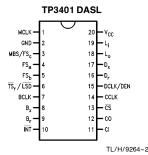

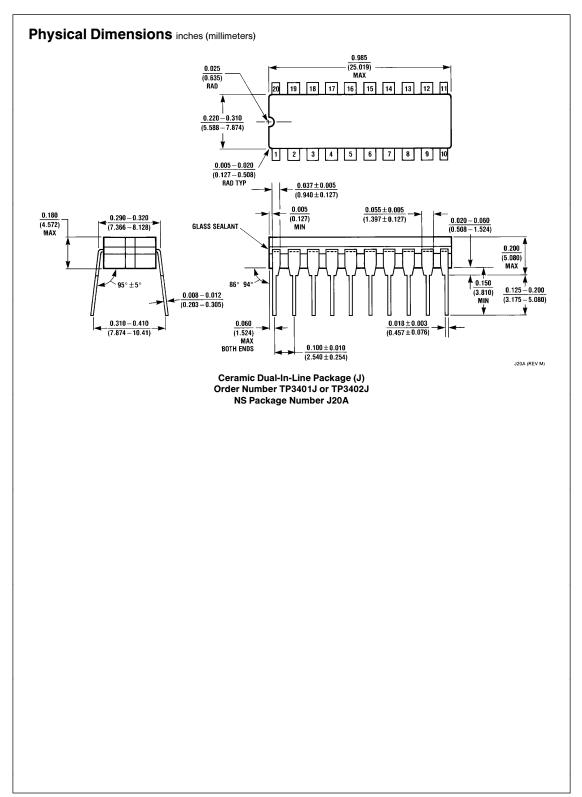

### **Connection Diagrams**

Order Number TP3401J See NS Package Number J20A

####

TL/H/9264-15

Order Number TP3402J

See NS Package Number J20A

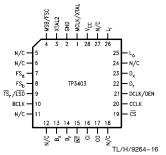

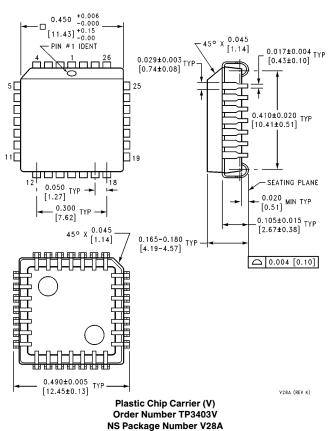

### **TP3403 Package Information**

Order Number TP3403V See NS Package Number V28A

### **Pin Descriptions**

| Name                                               | Description                                                                                                                                                                                                                                                                                                       | Name                 | Description                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                                | Negative power supply pin, normally 0V. All analog and digital signals are referred to this pin.                                                                                                                                                                                                                  |                      | tal output pulse which indicates the 8-bit periods of the B1 channel data transfer at both ${\sf B}_{\sf x}$ and ${\sf B}_{\sf r}$ .                                                                                                                                                                        |

| V <sub>CC</sub>                                    | Positive power supply input, which must be $+5\text{V}\pm5\%.$                                                                                                                                                                                                                                                    | FS <sub>b</sub>      | In Master mode only, this pin is the Receive Frame Sync pulse input, requiring a positive                                                                                                                                                                                                                   |

| MCLK<br>(TP3401 only)                              | The 2.048 MHz Master Clock input, which requires a CMOS logic level clock input from a stable source. Must be synchronous with BCLK.                                                                                                                                                                              |                      | edge to indicate the start of the active chan-<br>nel time of the device for receive B channel<br>data out from B <sub>f</sub> ; FS <sub>b</sub> must be synchronous<br>with BCLK and MCLK. In Slave mode only,<br>this pin is a digital output pulse which indi-                                           |

| MCLK/XTAL<br>(TP3402/3403<br>only)                 | This pin is the 2.048 MHz Master Clock in-<br>3 put, which requires either a crystal to be con-<br>nected between this pin and XTAL2 or a                                                                                                                                                                         |                      | cates the 8-bit periods of the B2 channel data transfer at both $B_x$ and $B_r$ .                                                                                                                                                                                                                           |

| .,                                                 | CMOS logic level clock from a stable source, which must be synchronous with BCLK.                                                                                                                                                                                                                                 | B <sub>x</sub>       | Digital input for B1 and B2 channel data to be transmitted to the line; must be synchronous with BCLK.                                                                                                                                                                                                      |

| XTAL2<br>(TP3402 and<br>TP3403 only)               | This pin is the output side of the oscillator amplifier.                                                                                                                                                                                                                                                          | B <sub>r</sub>       | Digital output for B1 and B2 channel data received from the line.                                                                                                                                                                                                                                           |

| MBS/FS <sub>C</sub><br>(TP3401 and<br>TP3403 only) | In Master Mode, this pin is the Master Burst Sync input, which may be clocked at 4 kHz to synchronize Transmit bursts from a number of devices at the Master end only. The 4 kHz should be nominally a square wave signal. If not used leave this pin open. In Slave mode, this pin is a short Frame Sync output, | TS <sub>r</sub> /LSD | In Master mode only, this pin is an open-<br>drain output which is normally high imped-<br>ance but pulls low during both B channel ac-<br>tive receive time slots. In Slave mode only,<br>this pin is an output which is normally high<br>impedance and pulls low when a valid line<br>signal is received. |

|                                                    | suitable for driving another DASL in Master<br>Mode to provide a regenerator (i.e. range-ex-<br>tender) capability.                                                                                                                                                                                               | D <sub>x</sub>       | Digital input for D channel data to be transmitted to the line; must be synchronous with DCLK.                                                                                                                                                                                                              |

| BCLK                                               | Bit Clock logic signal which determines the data shift rate for B channel data on the digi-                                                                                                                                                                                                                       | D <sub>r</sub>       | Digital output for D channel data received from the line.                                                                                                                                                                                                                                                   |

|                                                    | tal interface side of the device. In Master mode this pin is an input which may be any multiple of 8 kHz from 256 kHz to 2.048 MHz, but must be synchronous with MCLK. In Slave mode this pin is an output at 2.048 MHz.                                                                                          | DCLK/DEN             | In Master mode this pin is an input for the 16 kHz serial shift clock for D channel data on $D_x$ and $D_f$ , which should be synchronous with BCLK. It may also be re-configured via the Control Register to act as an enable input for clocking the D channel interface syn-                              |

| FS <sub>a</sub>                                    | In Master mode only, this pin is the Transmit Frame Sync pulse input, requiring a positive edge to indicate the start of the active channel time for transmit B channel data into B <sub>x</sub> ; FS <sub>a</sub> must be synchronous with BCLK and MCLK. In Slave mode only, this pin is a digi-                |                      | chronized to BCLK. In Slave mode this is a 16 kHz clock output for D channel data. stations: 2.048 MHz parallel resonant, R $_{\rm S} \le 100\Omega$ with a stati tolerance should be $\pm 75$ ppm for aging and tempera-                                                                                   |

|                                                    |                                                                                                                                                                                                                                                                                                                   |                      |                                                                                                                                                                                                                                                                                                             |

### Pin Descriptions (Continued)

| Name | Description                                                                                                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CI   | MICROWIRE control channel serial data input.                                                                                                                                                                                          |

| CO   | MICROWIRE control channel serial data output.                                                                                                                                                                                         |

| CCLK | Clock input for the MICROWIRE control channel.                                                                                                                                                                                        |

| CS   | Chip Select input which enables the MICRO-WIRE control channel data to be shifted in and out when pulled low. When high, this pin inhibits the MICROWIRE interface.                                                                   |

| ĪNT  | Interrupt output, a latched output signal which is normally high-impedance and goes low to indicate a change of status of the loop transmission system. This latch is cleared when the Status Register is read by the microprocessor. |

| Lo   | Transmit AMI signal output to the line transformer. This pin is capable of driving a load impedance $\geq 60\Omega.$                                                                                                                  |

| Li   | Receive AMI signal input from the line trans-                                                                                                                                                                                         |

### **Functional Description**

#### POWER-UP/POWER-DOWN CONTROL

Following the initial application of power, the DASL enters the power-down (de-activated) state, in which all the internal circuits are inactive and in a low power state except for the line-signal detect circuit and the necessary bias circuit; the line output  $L_0$  is in a low impedance state and all digital outputs are inactive. All bits in the Control Register power-up initially set to '0', so that the device always initializes as the Master end. Thus, at the Slave end, a control word must be written through the MICROWIRE port to select Slave mode. While powered-down, the Line-Signal Detect circuits in both Master and Slave devices continually monitor the line, to enable loop transmission to be initiated from either end

former. This is a high impedance input.

To power-up the device and initiate activation, bit C6 in the Control Register must be set high. Setting C6 low de-activates the loop and powers-down the device, see Table I.

TABLE I. Master Mode Burst Sync Control (TP3401 Only)

| MBS/FS <sub>c</sub><br>Pin I/P<br>at Master | C6<br>State | Action                                                     |

|---------------------------------------------|-------------|------------------------------------------------------------|

| Don't Care                                  | 0           | Powered-down, Line-Signal<br>Detect active                 |

| Open                                        | 1           | Powered-up, sending bursts synchronized to FS <sub>a</sub> |

| 4 kHz                                       | 1           | Powered-up, sending bursts synchronized to MBS             |

#### LINE TRANSMIT SECTION

Alternate Mark Inversion (AMI) line coding is used on the DASL because of its spectral efficiency and null dc energy content. All transmitted bits, excluding the start bit, are scrambled by a 9-bit scrambler to provide good spectral spreading with a strong timing content. The scrambler feedback polynomial is:

$$x^9 + x^5 + 1$$

.

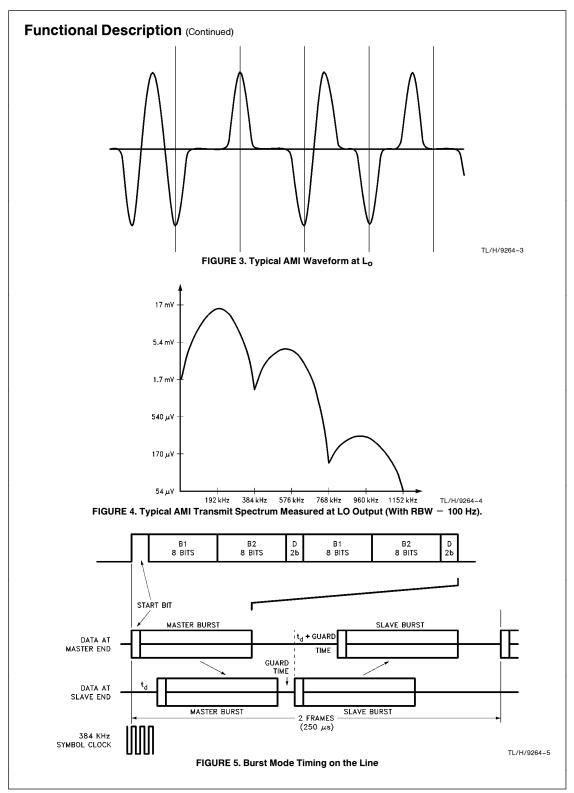

Pulse shaping is obtained by means of a raised cosine switched-capacitor filter, in order to limit rf energy and crosstalk while minimizing inter-symbol interference (isi).  $Figure\ 3$  shows the pulse shape at the L<sub>0</sub> output, while a template for the typical power spectrum transmitted to the line with random data is shown in  $Figure\ 4$ .

The line-driver output,  $L_0$ , is designed to drive a transformer through a capacitor and termination resistor. A 1:1 transformer, terminated in  $100\Omega$ , results in a signal amplitude of typically 1.3V pk-pk on the line. Over-voltage protection must be included in the interface circuit.

#### LINE RECEIVE SECTION

The front-end of the receive section consists of a continuous anti-alias filter followed by a switched-capacitor low-pass filter designed to limit the noise bandwidth with minimum intersymbol interference. To correct pulse attenuation and distortion caused by the transmission line an AGC circuit and first-order equalizer adapt to the received pulse shape, thus restoring a "flat" channel response with maximum received eye opening over a wide spread of cable attenuation characteristics.

From the equalized output a DPLL (Digital Phase-Locked Loop) recovers a low-jitter clock for optimum sampling of the received symbols. The MCLK input provides the reference clock for the DPLL at 2.048 MHz. At the Master end of the loop this reference is the network clock (BCLK), which controls all transmit functions; the DPLL clock is used only for received data sampling. At the Slave end, however, a 2.048 MHz crystal is required to generate a stable local oscillator which is used as a reference by the DPLL to run both the receive and transmit sides of the DASL device.

Following detection of the recovered symbols, the received data is de-scrambled by the same  $x^9 + x^5 + 1$  polynomial and presented to the digital system interface circuit.

When the device is de-activated, a Line-Signal Detect circuit remains powered-up to detect the presence of incoming bursts if the far-end starts to activate the loop. From a "cold" start, acquisition of bit timing and equalizer convergence with random scrambled data takes approximately 25 ms at each end of the loop. Full loop burst synchronization is achieved approximately 50 ms after the "activate" command at the originating end.

### Functional Description (Continued)

#### **BURST MODE OPERATION**

For full-duplex operation over a single twisted-pair, burst mode timing is used, with the line-card (exchange) end of the link acting as the timing Master.

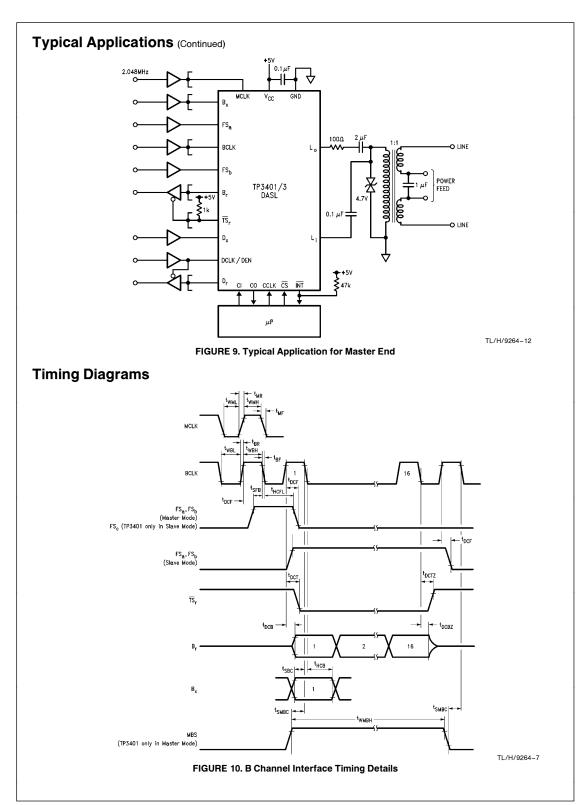

Each burst from the Master consists of the B1, B2 and D channel data from 2 consecutive frames combined in the format shown in Figure 5. During transmit bursts the Master's receiver input is inhibited to avoid disturbing the adaptive circuits. The Slave's receiver is enabled at this time and it synchronizes to the start bit of the burst, which is always an unscrambled '1' (of the opposite polarity to the last '1' sent in the previous burst). When the Slave detects that 36 bits following the start bit have been received, it disables the receiver input, waits 6 line symbol periods to match the other end settling guard time, and then begins to transmit its burst back towards the Master, which by this time has enabled its receiver input. The burst repetition rate is thus 4 kHz, which can either free-run or be locked to a synchronizing signal at the Master end by means of the MBS input (TP3401 only), (See Figure 10). In the latter case, with all Master-end transmitters in a system synchronized together, near-end crosstalk between pairs in the same cable binder may be eliminated, with a consequent increase in signal-tonoise ratio (SNR).

#### **ACTIVATION AND LOOP SYNCHRONIZATION**

Activation (i.e. power-up and loop synchronization) is typically completed in 50 ms and may be initiated from either end of the loop. If the Master is activating the loop, it sends normal bursts of scrambled '1's, which are detected by the Slave's line-signal detect circuit, causing it to set C0 = 1 in the Status Register, and pull the  $\overline{\text{INT}}$  pin low. Pin 6, the  $\overline{\text{LSD}}$  pin, also pulls low. To proceed with Activation, the device must be powered up by writing to the Control Register with C6 = 1. The Slave then replies with bursts of scrambled '1's synchronized to received bursts, and the flywheel circuit at each end searches for 4 consecutive correctly formatted receive bursts to acquire full loop synchronization. Each receiver indicates when it is correctly in sync with received bursts by setting the C1 bit in the Status Register high and pulling  $\overline{\text{INT}}$  low.

To activate the loop from the Slave end, bit C6 in the Control Register must be set high, which will power-up the device and begin transmission of alternate bursts i.e., the burst repetition rate is 2 kHz, not 4 kHz. At this point the Slave is running from its local oscillator and is not receiving any sync information from the Master. When the Master's line-signal detect circuit recognizes this "wake-up" signal, the Master is activated and begins to transmit bursts, synchronized, as normal, to the MBS or FS $_{\rm a}$  input with a 4 kHz repetition rate. This enables the Slave's receiver to correctly identify burst timing from the Master and to re-synchronize its own burst transmissions to those it receives. The flywheel circuits then acquire full loop sync as described earlier.

Loop synchronization is considered to be lost if the flywheel finds 4 consecutive receive burst "windows" (i.e. where a receive burst should have arrived based on timing from previous bursts) do not contain valid bursts. At this point bit C1 in the Status Register is set low, the  $\overline{\text{INT}}$  output is set low and the receiver searches to re-acquire loop sync.

### DIGITAL SYSTEM INTERFACE

The digital system interface on the DASL separates B and D channel information onto different pins to provide maximum  $\,$

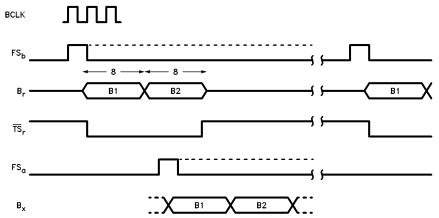

flexibility. On the B channel interface, phase skew between transmit and receive directions may be accommodated at the Master end since separate frame sync inputs,  $Fs_a$  and  $Fs_b$ , are provided. Each of these synchronizes a counter which gates the transfer of B1 and B2 channels in consecutive time-slots across the digital interface; since the counters are edge-synchronized the duration of the  $F_s$  input signals may vary from a single-bit pulse to a square-wave. The serial shift rate is determined by the BCLK input, and may be any frequency from 256 kHz to 2.048 MHz, as shown in Figure 6.

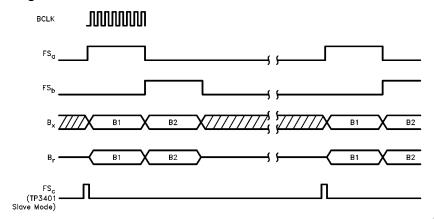

At the Slave end, both Fs<sub>a</sub> and Fs<sub>b</sub> are outputs. Fs<sub>a</sub> goes high for 8 cycles of BCLK coincident with the 8 bits of the B1 channel in both Transmit and Receive directions. Fs<sub>b</sub> goes high for the next 8 cycles of BCLK, which are coincident with the 8 bits of the B2 channel in both Transmit and Receive directions. BCLK is also an output at 2.048 MHz, the serial data shift rate, as shown in Figure 7. Data may be exchanged between the B1 and B2 channels as it passes through the device, by setting Control bit C0 = 1. An additional Frame Sync output, FS<sub>c</sub>, is provided to enable a regenerator to be built by connecting a DASL in Slave Mode to a DASL in Master Mode. The FS<sub>c</sub> output from the Slave directly drives the FS<sub>a</sub> and FS<sub>b</sub> inputs on the Master.

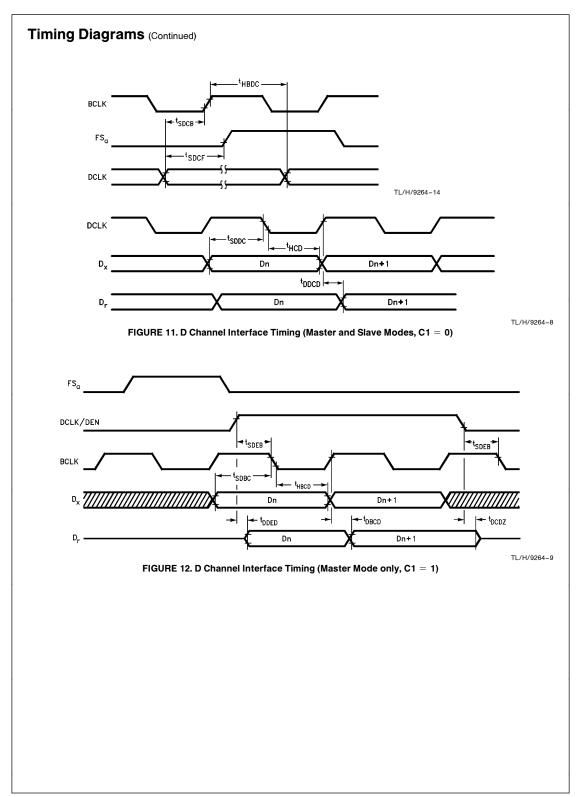

D channel information, being packet-mode, requires no synchronizing input. This interface consists of the transmit data input,  $D_x$ , receive data output,  $D_r$ , and 16 kHz serial shift clock DCLK, which is an input at the Master end and an output at the Slave end. Data shifts into  $D_x$  on falling edges of DCLK and out from  $D_r$  on rising edges, as shown in Figure 11. DCLK should be Synchronous with BCLK.

An alternative function of the DCLK/DEN pin allows  $D_{\rm X}$  and  $D_{\rm f}$  to be clocked at the same rate as BCLK at the Master end only. By setting bit C1 in the Control Register to a 1, DCLK/DEN becomes an input for an enabling pulse to gate 2 cycles of BCLK for shifting the 2 D bits per frame. Thus, at the Master end, the D channel bits can be interfaced to a TDM bus and assigned to a time-slot (the same time-slot for both transmit and receive), as shown in Figure 12.

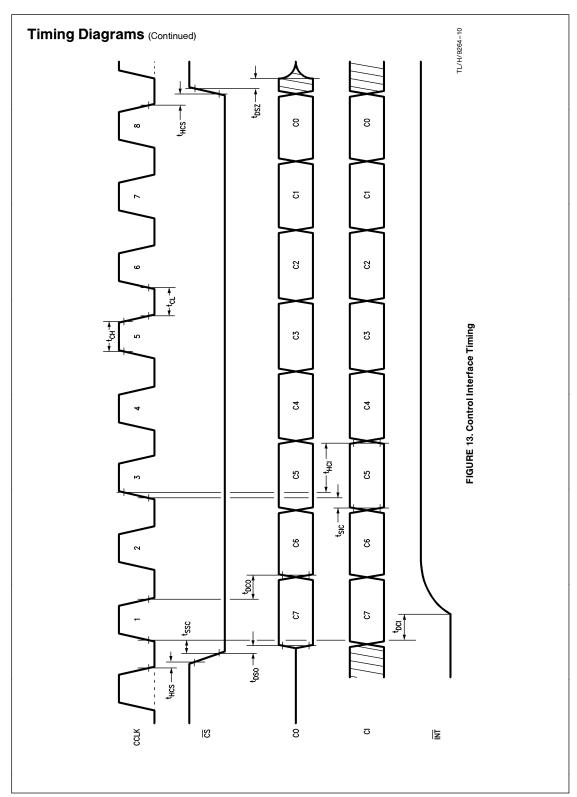

#### CONTROL INTERFACE

A serial interface, which can be clocked independently from the B and D channel system interfaces, is provided for microprocessor control of various functions on the DASL device. All data transfers consist of a single byte shifted into the Control Register via CI simultaneous with a single byte shifted out from the Status Register via CO, see Figure 13. Data shifts in to CI on rising edges of CCLK and out from CO on falling edges when CS is pulled low for 8 cycles of CCLK. An Interrupt output, INT goes low to alert the microprocessor whenever a change in one of the status bits, C1 and/or C0 has occurred. This latched output is cleared high following the first CCLK pulse when  $\overline{\text{CS}}$  is low. No interrupt is generated when status bit C2 (bipolar violation) goes high, however. This bit is set whenever 1 or more violations of the AMI coding rule is received, and cleared everytime the  $\overline{CS}$  is pulsed. Statistics on the line bit error rate can be accumulated by regularly polling this bit.

When reading the CO pin, data is always clocked into the Control Register; therefore the Cl data word should repeat the previous instruction if no change to the device mode is intended.

Figure 13 shows the timing for this interface, and Table II lists the control functions and status indicators.

TABLE II. Control and Status Register Functions

| Bit | State | Control Register Function                | Status Register Function                   |

|-----|-------|------------------------------------------|--------------------------------------------|

| C7  | 0     | Master Mode                              | Read Back C7 from Control Register         |

|     | 1     | Slave Mode                               | Read Back C7 from Control Register         |

| C6  | 0     | Deactivate and Power Down                | Read Back C6 from Control Register         |

|     | 1     | Power Up and Activate                    | Read Back C6 from Control Register         |

| C5  | 0     | Normal Through Connection                | Read Back C5 from Control Register         |

|     | 1     | Loopback to Digital Interface            | Read Back C5 from Control Register         |

| C4  | 0     | Normal Through Connection                | Read Back C4 from Control Register         |

| 04  | 1     | Loopback B1 + B2 + D to Line (Note 1)    | Read Back C4 from Control Register         |

| СЗ  | 0     | Normal Through Connection                | Read Back C3 from Control Register         |

|     | 1     | Loopback B1 Only to Line (Note 1)        | Read Back C3 from Control Register         |

| C2  | 0     | Normal Through Connection                | No Error                                   |

| 02  | 1     | Loopback B2 Only to Line (Note 1)        | Bipolar Violation Since Last READ (Note 2) |

| C1  | 0     | DCLK/DEN pin = 16 kHz Clock              | Out-Of-Sync                                |

| 01  | 1     | DCLK/DEN pin = D Channel Enable (Note 3) | Loop In-Sync and Activation Complete       |

| CO  | 0     | B1/B2 Channels Direct                    | No Line Signal at Receiver Input           |

|     | 1     | B1/B2 Channels Exchanged                 | Line Signal Present at Receiver Input      |

Note 1: Receive data active.

Note 2: After the device is in sync.

Note 3: In Master mode only.

Note 4: C7 is the first bit clocked in and out of the device.

### **Timing Diagrams**

FIGURE 6. B Channel Interface Timing: Master Mode

TL/H/9264-6

### Timing Diagrams (Continued)

FIGURE 7. B Channel Interface Timing: Slave Mode

TL/H/9264-13

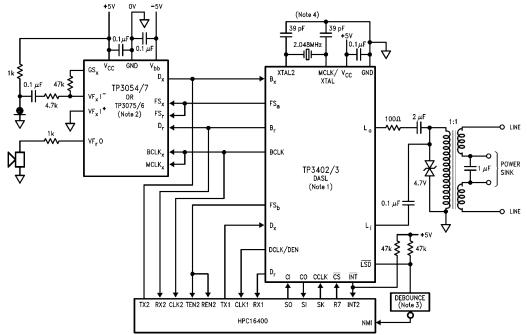

### **Typical Applications**

FIGURE 8. Typical Application for Slave End

TL/H/9264-11

Note 1: The TP3401 may also be used in this configuration with an external MCLK source.

Note 2: The TP3075/6 Programmable Combos also must be connected to the MICROWIRE interface.

$\textbf{Note 3:} \ \, \textbf{Only necessary if a mechanical Hookswitch is connected to the NMI input of the HPC.}$

Note 4: Crystal load capacitors include board and trace capacitance. Oscillator frequency can be checked by measuring the BCLK output frequency when slave mode part is in digital loopback.

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{ll} \text{V}_{CC} \text{ to GND} & \text{7V} \\ \text{Voltage at L}_{i,} \text{ L}_{o} & \text{V}_{CC} + 1\text{V to V}_{SS} - 1\text{V} \\ \text{Voltage at any Digital Input} & \text{V}_{CC} + 1\text{V to V}_{SS} - 1\text{V} \end{array}$

**Electrical Characteristics** Unless otherwise noted, limits printed in **bold** characters are guaranteed for  $V_{CC} = 5.0V \pm 5\%$  and  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $V_{CC} = 5.0V$  and  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. Typical characteristics are specified at  $V_{CC} = 5.0V$  and  $T_A = 25^{\circ}C$ . All digital signals are referenced to GND.

| Symbol            | Parameter                                           | Conditions                                                                             | Min        | Тур   | Max | Units    |

|-------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------|------------|-------|-----|----------|

| DIGITAL IN        | ITERFACES                                           |                                                                                        |            |       | •   |          |

| V <sub>IL</sub>   | Input Low Voltage                                   | All Digital Inputs (not MCLK)                                                          |            |       | 0.7 | V        |

| V <sub>IH</sub>   | Input High Voltage                                  | All Digital Inputs (not MCLK)                                                          | 2.2        |       |     | ٧        |

| V <sub>OL</sub>   | Output Low Voltage                                  | I <sub>L</sub> = 1 mA                                                                  |            |       | 0.4 | V        |

| V <sub>OH</sub>   | Output High Voltage                                 | $I_L = -1 \text{ mA}$                                                                  | 2.4        |       |     | V        |

| I <sub>IM</sub>   | Input Current at MBS/FSc                            | GND < V <sub>IN</sub> < V <sub>CC</sub>                                                | -600       |       | 10  | μΑ       |

| II                | Input Current                                       | Any Other Digital Input, GND $<$ V $_{IN}$ $<$ V $_{CC}$                               | -10        |       | 10  | μΑ       |

| l <sub>OZ</sub>   | Output Current in High Impedance State (TRI-STATE®) | B <sub>r</sub> , INT, TS <sub>r</sub> , CO<br>GND < V <sub>OUT</sub> < V <sub>CC</sub> | <b>-10</b> |       | 10  | μΑ       |

| LINE INTE         | RFACES                                              |                                                                                        |            |       |     |          |

| $R_{Li}$          | Input Resistance                                    | 0V < L <sub>i</sub> < 5.0V                                                             | 50         |       |     | kΩ       |

| CL <sub>Lo</sub>  | Load Capacitance                                    | CL <sub>Lo</sub> from L <sub>o</sub> to GND.                                           |            |       | 100 | pF       |

| RO                | Output Resistance at L <sub>o</sub>                 | Load = $60\Omega$ in Series with 2 $\mu$ F to GND                                      |            |       | 3.0 | Ω        |

| V <sub>DC</sub>   | Mean d.c. Voltage<br>at L <sub>o</sub>              | Load $= 60\Omega$ in Series with 2 $\mu$ F to GND                                      | 1.5        |       | 2.5 | ٧        |

| POWER DI          | SSIPATION                                           |                                                                                        |            |       |     |          |

| I <sub>CC</sub> 0 | Power Down Current                                  |                                                                                        |            | 1.3   | 2.2 | mA       |

| I <sub>CC</sub> 1 | Power Up Current (Activated)                        | Load at $L_0=200\Omega$ in Series with 2 $\mu F$ to GND (in Master Mode)               |            |       | 18  | mA       |

| TRANSMIS          | SION PERFORMANCE                                    |                                                                                        |            |       |     |          |

| <u> </u>          | Transmit Pulse Amplitude at Lo                      | $R_L=200\Omega$ in Series with 2 $\mu F$ to GND                                        | ± 0.9      | ± 1.1 |     | Vpk      |

|                   | Input Pulse Amplitude at Li                         |                                                                                        | ± 60       |       |     | mVpk     |

|                   | Timing Recovery Jitter                              | BCLK at Slave Relative to MCLK at Master                                               |            | 100   |     | ns pk-pk |

### **Timing Characteristics**

Unless otherwise noted:  $V_{CC} = +5V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to 70°C. Typical characteristics are specified at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ . All signals are referenced to GND.

| Symbol                                 | Parameter                                                       | Conditions                                                                | Min  | Тур   | Max  | Units    |

|----------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|------|-------|------|----------|

| MASTER                                 | CLOCK INPUT SPECIFICATION                                       | s                                                                         |      |       |      |          |

| F <sub>MCK</sub>                       | Master Clock Frequency                                          |                                                                           |      | 2.048 |      | MHz      |

|                                        | Master Clock Tolerance                                          | Measured Relative to the Slave MCLK                                       | -100 |       | +100 | ppm      |

|                                        | Master Clock Input Jitter                                       | 2.048 MHz Input, 18 kHz < f < 200 kHz                                     |      |       | 200  | ns pk-pk |

| t <sub>WMH</sub> ,<br>t <sub>WML</sub> | Clock Pulse Width<br>Hi & Low for MCLK                          | $\begin{aligned} V_{IH} &= V_{CC} - 0.5V \\ V_{IL} &= 0.5V \end{aligned}$ | 190  |       |      | ns       |

| t <sub>MR</sub> ,<br>t <sub>MF</sub>   | Rise and Fall Time of MCLK                                      | Used as a Logic Input                                                     |      |       | 15   | ns       |

| B CHANNE                               | L INTERFACE (Figure 10)                                         |                                                                           |      |       |      |          |

| F <sub>BCK</sub>                       | Bit Clock Frequency                                             | Master Mode Only                                                          |      | 2.048 |      | MHz      |

| t <sub>WBH</sub> ,<br>t <sub>WBL</sub> | Clock Pulse Width<br>Hi & Low for BCLK                          | $V_{IH} = 2.2V$<br>$V_{IL} = 0.7V$                                        | 190  |       |      | ns       |

| t <sub>BR</sub> ,<br>t <sub>BF</sub>   | Rise and Fall Time of BCLK                                      | Master Mode requirement for BCLK Source                                   |      |       | 15   | ns       |

| t <sub>SFB</sub>                       | Set-Up Time, FS <sub>a</sub> and<br>FS <sub>b</sub> to BCLK Low | Master Mode Only                                                          | 70   |       |      | ns       |

| t <sub>HCFL</sub>                      | Hold Time, BCLK Low to FS <sub>a</sub> and FS <sub>b</sub> Low  | Master Mode Only                                                          | 100  |       |      | ns       |

| t <sub>WBH</sub><br>t <sub>WBL</sub>   | Output Pulse Width<br>High and Low for BCLK                     | Slave Mode Only<br>Load = 2 LSTTL Inputs Plus 50 pF                       | 195  |       |      | ns       |

| t <sub>DCF</sub>                       | Delay Time, BCLK High to $FS_a$ , $FS_b$ and $FS_c$ Transitions | Slave Mode Only<br>Load = 2 LSTTL Inputs Plus 50 pF                       |      |       | 115  | ns       |

| t <sub>SBC</sub>                       | Set Up Time, B <sub>X</sub> Valid to BCLK Low                   |                                                                           | 30   |       |      | ns       |

| t <sub>HCB</sub>                       | Hold Time, BCLK Low to B <sub>X</sub> Invalid                   |                                                                           | 50   |       |      | ns       |

| t <sub>DCB</sub>                       | Delay Time, BCLK High<br>to B <sub>r</sub> Valid                | Load = 2 LSTTL Inputs Plus 100 pF                                         |      |       | 160  | ns       |

| t <sub>DCBZ</sub>                      | Delay Time, BCLK Low to<br>B <sub>r</sub> High-Impedance        | Slave Mode Only                                                           | 60   |       | 220  | ns       |

| t <sub>DCT</sub>                       | Delay Time, BCLK High<br>to TS <sub>r</sub> Low                 | Load = 2 LSTTL Inputs Plus 100 pF                                         |      |       | 180  | ns       |

| t <sub>DCTZ</sub>                      | Delay Time, BCLK Low to TS <sub>r</sub> High-Impedance          |                                                                           | 60   |       | 185  | ns       |

| t <sub>SMBC</sub>                      | Set-Up Time, MBS<br>to BCLK Low (Note 1)                        | Master Mode Only<br>(TP3401 and TP3403 only)                              | 60   |       |      | ns       |

| t <sub>WMBH</sub>                      | Width of MBS Input<br>High                                      | Master Mode Only<br>(TP3401 and TP3403 only)                              |      | 125   |      | μs       |

Note 1: MBS transitions may occur anywhere in the Frame, and require no specific relationship to FSa or FSb.

**Timing Characteristics** (Continued) Unless otherwise noted:  $V_{CC}=+5V\pm5\%$ ,  $T_A=0^{\circ}C$  to 70°C. Typical characteristics are specified at  $V_{CC}=5V$ ,  $T_A=25^{\circ}C$ . All signals are referenced to GND.

| Symbol            | Parameter                                                | Conditions                        | Min | Max | Units |

|-------------------|----------------------------------------------------------|-----------------------------------|-----|-----|-------|

| HANNEL INT        | ERFACE (Figure 11 & 12)                                  |                                   |     |     |       |

| tsddc             | Set Up Time, D <sub>X</sub><br>Valid to DCLK Low         |                                   | 100 |     | ns    |

| t <sub>HCD</sub>  | Hold Time, DCLK Low to D <sub>X</sub> Invalid            |                                   | 100 |     | ns    |

| t <sub>DDCD</sub> | Delay Time, DCLK High to<br>D <sub>r</sub> Data Valid    | Load = 100 pF<br>+ 2 LSTTL Inputs |     | 220 | ns    |

| t <sub>SDCB</sub> | Set-Up Time, DCLK<br>Transitions to BCLK High            | Master Mode<br>Only               | 50  |     | ns    |

| t <sub>HBDC</sub> | Hold Time, BCLK High to DCLK Transitions                 | Master Mode<br>Only               | 50  |     | ns    |

| t <sub>SDCF</sub> | Set-Up Time, DCLK<br>Transitions to FS <sub>a</sub> HIgh | Master Mode<br>Only               | 70  |     | ns    |

| t <sub>DDED</sub> | Delay Time, DEN High<br>to D <sub>r</sub> Valid          | Load = 100 pF + 2 LSTTL Inputs    |     | 200 | ns    |

| t <sub>SDEB</sub> | Set-Up Time, DEN to<br>BCLK Low                          |                                   | 100 |     | ns    |

| t <sub>SDBC</sub> | Set-Up Time, D <sub>X</sub><br>to BCLK Low               |                                   | 50  |     | ns    |

| t <sub>HBCD</sub> | Hold Time, BCLK<br>Low to D <sub>x</sub> Invalid         |                                   | 50  |     | ns    |

| t <sub>DBCD</sub> | Delay Time, BCLK<br>High to D <sub>r</sub> Valid         | Load = 100 pF<br>+2 LSSTL Inputs  |     | 190 | ns    |

| t <sub>DCDZ</sub> | Delay Time, DEN<br>Low to D <sub>r</sub> High Impedance  |                                   |     | 140 | ns    |

| NTROL INTER       | RFACE (Figure 13)                                        |                                   | •   |     |       |

| t <sub>CH</sub>   | CCLK High Duration                                       |                                   | 250 |     | ns    |

| t <sub>CL</sub>   | CCLK Low Duration                                        |                                   | 250 |     | ns    |

| t <sub>SIC</sub>  | Setup Time, Cl<br>Valid to CCLK High                     |                                   | 100 |     | ns    |

| t <sub>HCI</sub>  | Hold Time, CCLK High<br>to CI Invalid                    |                                   | 0   |     | ns    |

| t <sub>SSC</sub>  | Setup Time from CS Low to CCLK High                      |                                   | 200 |     | ns    |

| t <sub>HCS</sub>  | Hold Time from CCLK<br>Low to CS                         |                                   | 10  |     | ns    |

| t <sub>DCO</sub>  | Delay Time from CCLK Low<br>to C0 Data Valid             | Load = 100 pF<br>+2 LSTTL Inputs  |     | 150 | ns    |

| t <sub>DSO</sub>  | Delay Time from CS Low to CO Valid                       | 1st Bit Only                      |     | 100 | ns    |

| t <sub>DSZ</sub>  | Delay Time from CS High<br>to CO High Impedance          |                                   |     | 100 | ns    |

| t <sub>DCI</sub>  | Delay Time from CCLK1 High to INT High Impedance         |                                   |     | 120 | ns    |

## **Definitions and Timing Conventions DEFINITIONS**

$V_{IH}$   $V_{IH}$  is the d.c. input level above which an input level is guaranteed to appear

as a logical one. This parameter is to be measured by performing a functional test at reduced clock speeds and nominal timing, (i.e. not minimum setup and hold times or output strobes), with the high level of all driving signals set to  $V_{IH}$  and maximum supply voltages

applied to the device.

$V_{IL}$   $V_{IL}$  is the d.c. input level below which

an input level is guaranteed to appear as a logical zero to the device. This parameter is measured in the same manner as  $V_{IH}$  but with all driving signal low levels set to  $V_{IL}$  and minimum supply voltages applied to the device.

V<sub>OH</sub> is the minimum d.c. output level to

which an output placed in a logical one state will converge when loaded at the maximum specified load current.

V<sub>OL</sub> V<sub>OL</sub> is the maximum d.c. output level to which an output placed in a logical zero

state will converge when loaded at the maximum specified load current.

Threshold Region The threshold region is the range of in-

put voltages between  $V_{IL}$  and  $V_{IH}$ .

Valid Signal A signal is Valid if it is in one of the valid logic states, (i.e. above V<sub>IH</sub> or be-

low  $V_{\text{IL}}$ ). In timing specifications, a signal is deemed valid at the instant it en-

ters a valid state.

Invalid Signal A signal is Invalid if it is not in a valid

logic state, i.e. when it is in the threshold region between  $V_{IL}$  and  $V_{IH}$ . In timing specifications, a signal is deemed invalid at the instant it enters the

threshold region.

TIMING CONVENTIONS

For the purpose of this timing specification the following conventions apply:

Innut Cianala

Input Signals All input signals may be characterized

as:  $V_L = 0.4V$ ,  $V_{IH} = 2.4V$ ,  $t_R < 10$  ns,

$t_{\mathsf{F}} < 10 \; \mathsf{ns}.$

Period The period of clock signal is designated at  $t_{Pxx}$  where xx represents the

mnemonic of the clock signal being

specified.

Rise Time Rise times are designated at  $t_{\mbox{\scriptsize Ryy}},$  where yy represents a mnemonic of

where yy represents a mnemonic of the signal whose rise time is being specified.  $t_{Ryy}$  is measured from  $V_{IL}$  to

$V_{IH}$ .

Fall Time Fall times are designated as  $t_{\mbox{Fyy}}$ , where yy represents a mnemonic of

the signal whose fall time is being specified. t<sub>Fyy</sub> is measured from V<sub>IH</sub> to

V<sub>IL</sub>.

Pulse Width High  $\;\;\;$  The high width is designated as  $t_{\mbox{WzzH}},$

where zz represents the mnemonic of the input or output signal whose pulse width is being specified. High pulse widths are measured from  $V_{IH}$  to  $V_{IH}$ .

Pulse Width Low

The low pulse width is designed as

$t_{WzzL}$ , where zz represents the mnemonic of the input or output signal whose pulse width is being specified. Low pulse widths are measured from

V<sub>IL</sub> to V<sub>IL</sub>.

Setup Time Setup times are designated as t<sub>Swwxx</sub>,

where ww represents the mnemonic of the input signal whose setup time is being specified relative to a clock or strobe input represented by mnemonic xx. Setup times are measured from the

ww Valid to xx Invalid.

Hold Time Hold times are designated as t<sub>Hxxww</sub>, where ww represents the mnemonic of the input signal whose hold time is be-

the input signal whose hold time is being specified relative to a clock or strobe input represented by mnemonic xx. Hold times are measured from xx

Valid to ww invalid.

IHILI, where xx represents the mnemonic of the input reference signal and yy represents the mnemonic of the output signal whose timing is being specified relative to xx. The mnemonic may optionally be terminated by an H or L to specifiy the high going or low going transition of the output signal. Maximum delay times are measured from xx Valid to yy Valid. Minimum delay times are measured from xx Valid to yy invalid. This parameter is tested under the load conditions specified in the Conditions column of the Timing Specifica

tion section of this data sheet.

### Physical Dimensions inches (millimeters) (Continued)

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications