# **Axcelerator Family FPGAs**

#### **Leading-Edge Performance**

- 350+ MHz System Performance

- 500+ MHz Internal Performance

- High-Performance Embedded FIFOs

- 700 Mb/s LVDS Capable I/Os

#### **Specifications**

- Up to 2 Million Equivalent System Gates

- Up to 684 I/Os

- Up to 10,752 Dedicated Flip-Flops

- Up to 295 kbits Embedded SRAM/FIFO

- Manufactured on Advanced 0.15 μm CMOS Antifuse Process Technology, 7 Layers of Metal

#### **Features**

- Single-Chip, Nonvolatile Solution

- Up to 100% Resource Utilization with 100% Pin Locking

- 1.5V Core Voltage for Low Power

- Footprint Compatible Packaging

- Flexible, Multi-Standard I/Os:

- 1.5V, 1.8V, 2.5V, 3.3V Mixed Voltage Operation

- Bank-Selectable I/Os 8 Banks per Chip

- Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3V PCI, and 3.3V PCI-X

- Differential I/O Standards: LVPECL and LVDS

- Voltage-Referenced I/O Standards: GTL+, HSTL Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

- Registered I/Os

- Hot-Swap Compliant I/Os (except PCI)

- Programmable Slew Rate and Drive Strength on Outputs

- Programmable Delay and Weak Pull-Up/Pull-Down Circuits on Inputs

- Embedded Memory:

- Variable-Aspect 4,608-bit RAM Blocks (x1, x2, x4, x9, x18, x36 Organizations Available)

- Independent, Width-Configurable Read and Write Ports

- Programmable Embedded FIFO Control Logic

- Segmentable Clock Resources

- Embedded Phase-Locked Loop:

- 14-200 MHz Input Range

- Frequency Synthesis Capabilities up to 1 GHz

- Deterministic, User-Controllable Timing

- Unique In-System Diagnostic and Debug Capability with Actel Silicon Explorer II

- Boundary-Scan Testing Compliant with IEEE Standard 1149.1 (JTAG)

- FuseLock<sup>TM</sup> Secure Programming Technology Prevents Reverse Engineering and Design Theft

Table 1-1 • Axcelerator Family Product Profile

| Device                                | AX125    | AX250    | AX500    | AX1000        | AX2000    |

|---------------------------------------|----------|----------|----------|---------------|-----------|

| Capacity (in Equivalent System Gates) | 125,000  | 250,000  | 500,000  | 1,000,000     | 2,000,000 |

| Typical Gates                         | 82,000   | 154,000  | 286,000  | 612,000       | 1,060,000 |

| Modules                               |          |          |          |               |           |

| Register (R-cells)                    | 672      | 1,408    | 2,688    | 6,048         | 10,752    |

| Combinatorial (C-cells)               | 1,344    | 2,816    | 5,376    | 12,096        | 21,504    |

| Maximum Flip-Flops                    | 1,344    | 2,816    | 5,376    | 12,096        | 21,504    |

| Embedded RAM/FIFO                     |          |          |          |               |           |

| Number of Core RAM Blocks             | 4        | 12       | 16       | 36            | 64        |

| Total Bits of Core RAM                | 18,432   | 55,296   | 73,728   | 165,888       | 294,912   |

| Clocks (Segmentable)                  |          |          |          |               |           |

| Hardwired                             | 4        | 4        | 4        | 4             | 4         |

| Routed                                | 4        | 4        | 4        | 4             | 4         |

| PLLs                                  | 8        | 8        | 8        | 8             | 8         |

| I/Os                                  |          |          |          |               |           |

| I/O Banks                             | 8        | 8        | 8        | 8             | 8         |

| Maximum User I/Os                     | 168      | 248      | 336      | 516           | 684       |

| Maximum LVDS Channels                 | 84       | 124      | 168      | 258           | 342       |

| Total I/O Registers                   | 504      | 744      | 1,008    | 1,548         | 2,052     |

| Package                               |          |          |          |               |           |

| CSP                                   | 180      |          |          |               |           |

| PQFP                                  |          | 208      | 208      |               |           |

| BGA                                   |          |          |          | 729           |           |

| FBGA                                  | 256, 324 | 256, 484 | 484, 676 | 484, 676, 896 | 896, 1152 |

| CQFP                                  | ,        | 208, 352 | 208, 352 | 352           | 256, 352  |

|                                       |          |          |          |               |           |

© 2009 Actel Corporation

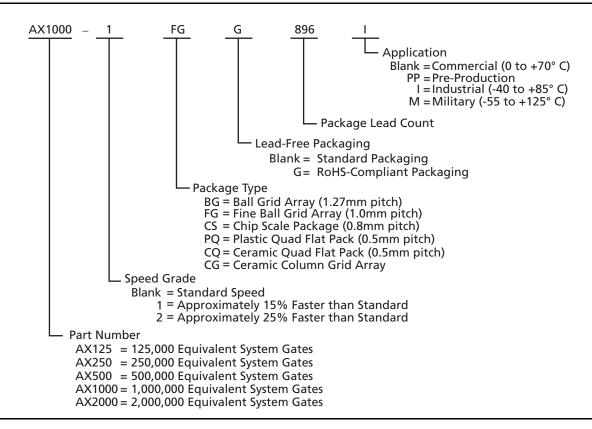

#### **Ordering Information**

#### **Device Resources**

|         | User I/Os (Including Clock Buffers) |       |       |        |        |

|---------|-------------------------------------|-------|-------|--------|--------|

| Package | AX125                               | AX250 | AX500 | AX1000 | AX2000 |

| CS180   | 98                                  | _     | _     | -      | _      |

| PQ208   | -                                   | 115   | 115   | -      | _      |

| CQ208   | -                                   | 115   | 115   | -      | _      |

| CQ256   | -                                   | _     | _     | -      | 136    |

| FG256   | 138                                 | 138   | _     | -      | _      |

| FG324   | 168                                 | _     | _     | -      | _      |

| CQ352   | -                                   | 198   | 198   | 198    | 198    |

| FG484   | -                                   | 248   | 317   | 317    | _      |

| CG624   | -                                   | _     | _     | 418    | 418    |

| FG676   | -                                   | _     | 336   | 418    | _      |

| BG729   | -                                   | -     | _     | 516    | _      |

| FG896   | -                                   | _     | _     | 516    | 586    |

| FG1152  | -                                   | _     | _     | -      | 684    |

**Note:** The FG256, FG324, and FG484 are footprint compatible with one another. The FG676, FG896, and FG1152 are also footprint compatible with one another.

#### **Temperature Grade Offerings**

| Package | AX125 | AX250   | AX500   | AX1000  | AX2000  |

|---------|-------|---------|---------|---------|---------|

| CS180   | С, І  | -       | _       | _       | -       |

| PQ208   | -     | C, I, M | C, I, M | _       | _       |

| CQ208   | -     | М       | М       | _       | -       |

| CQ256   | -     | _       | _       | _       | М       |

| FG256   | С, І  | C, I, M | _       | _       | -       |

| FG324   | С, І  | _       | _       | _       | -       |

| CQ352   | -     | М       | M       | М       | М       |

| FG484   | -     | C, I, M | C, I, M | C, I, M | -       |

| CG624   | -     | _       | _       | М       | М       |

| FG676   | -     | _       | C, I, M | C, I, M | -       |

| BG729   | -     | _       | _       | C, I, M | -       |

| FG896   | -     | _       | _       | C, I, M | C, I, M |

| FG1152  | -     | _       | _       | _       | C, I, M |

#### Notes:

- 1. C = Commercial

- 2. I = Industrial

- 3. M = Military

#### **Speed Grade and Temperature Grade Matrix**

|   | Std | -1 | -2 |

|---|-----|----|----|

| С | ✓   | ✓  | ✓  |

| I | ✓   | ✓  | ✓  |

| M | ✓   | ✓  | -  |

#### Notes:

- 1. C = Commercial

- 2. I = Industrial

- 3. M = Military

### **Packaging Data**

Refer to the following documents located on the Actel website for additional packaging information.

Package Mechanical Drawings

Package Thermal Characteristics and Weights

Hermatic Package Mechanical Information

Contact your local Actel representative for device availability.

# **Table of Contents**

| deneral Description                             |

|-------------------------------------------------|

| Device Architecture                             |

| Programmable Interconnect Element               |

| Logic Modules                                   |

| Embedded Memory 1-4                             |

| I/O Logic 1-4                                   |

| Routing 1-5                                     |

| Global Resources                                |

| Low Power (LP) Mode 1-6                         |

| Design Environment                              |

| Programming 1-7                                 |

| In-System Diagnostic and Debug Capabilities 1-7 |

| Summary                                         |

| Related Documents 1-8                           |

| Detailed Specifications                         |

| Operating Conditions                            |

| Thermal Characteristics                         |

| I/O Specifications                              |

| Voltage-Referenced I/O Standards 2-32           |

| Differential Standards                          |

| Module Specifications 2-43                      |

| Routing Specifications                          |

| Global Resources                                |

| Axcelerator Clock Management System 2-63        |

| Embedded Memory         2-72                    |

| Other Architectural Features                    |

| Programming 2-9                                 |

| Package Pin Assignments                         |

| 180-Pin CSP 3-                                  |

| 729-Pin PBGA 3-4                                |

| 256-Pin FBGA 3-12                               |

| 324-Pin FBGA 3-18                               |

| 484-Pin FBGA 3-22                               |

| 676-Pin FBGA 3-36                               |

| 896-Pin FRGΔ 3-49                               |

iv v2.8

# **Table of Contents**

| 1152-Pin FBGA 3-67                      |

|-----------------------------------------|

| 208-Pin PQFP                            |

| 208-Pin CQFP                            |

| 256-Pin CQFP                            |

| 352-Pin CQFP 3-92                       |

| 624-Pin CCGA 3-106                      |

| Datasheet Information                   |

| List of Changes 4-1                     |

| Datasheet Categories                    |

| Export Administration Regulations (EAR) |

# **General Description**

Axcelerator offers high performance at densities of up to two million equivalent system gates. Based upon the Actel AX architecture, Axcelerator has several system-level features such as embedded SRAM (with complete FIFO control logic), PLLs, segmentable clocks, chip-wide highway routing, and carry logic.

#### **Device Architecture**

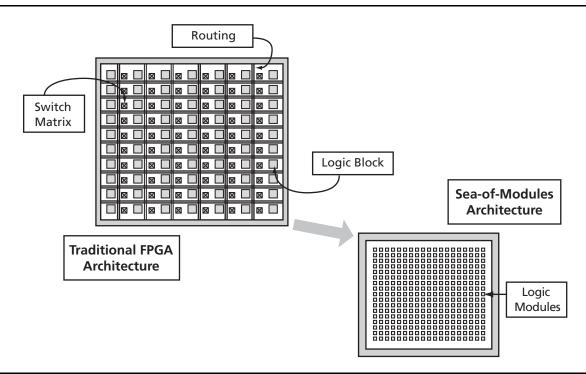

Actel's AX architecture, derived from the highly-successful SX-A sea-of-modules architecture, has been designed for high performance and total logic module utilization (Figure 1-1). Unlike in traditional FPGAs, the entire floor of the Axcelerator device is covered with a grid of logic modules, with virtually no chip area lost to interconnect elements or routing.

# **Programmable Interconnect Element**

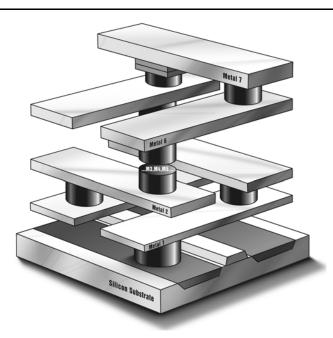

The Axcelerator family uses a patented metal-to-metal antifuse programmable interconnect element that resides between the upper two layers of metal (Figure 1-2 on

page 1-2). This completely eliminates the channels of routing and interconnect resources between logic modules (as implemented on traditional FPGAs) and enables the efficient sea-of-modules architecture. The antifuses are normally open circuit and, when programmed, form a permanent, passive, low-impedance connection, leading to the fastest signal propagation in the industry. In addition, the extremely small size of these interconnect elements gives the Axcelerator family abundant routing resources.

The very nature of Actel's nonvolatile antifuse technology provides excellent protection against design pirating and cloning (FuseLock technology). Cloning is impossible (even if the security fuse is left unprogrammed) as no bitstream or programming file is ever downloaded or stored in the device. Reverse engineering is virtually impossible due to the difficulty of trying to distinguish between programmed and unprogrammed antifuses and also due to the programming methodology of antifuse devices (see "Security" on page 2-90).

Figure 1-1 • Sea-of-Modules Comparison

v2.8 1-1

Figure 1-2 • Axcelerator Family Interconnect Elements

### **Logic Modules**

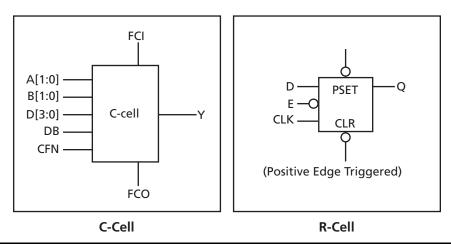

Actel's Axcelerator family provides two types of logic modules: the register cell (R-cell) and the combinatorial cell (C-cell). The

can implement more than 4,000 combinatorial functions of up to five inputs (Figure 1-3 on page 1-3).

The R-cell contains a flip-flop featuring asynchronous clear, asynchronous preset, and active-low enable control signals (Figure 1-3 on page 1-3). The R-cell registers feature programmable clock polarity selectable on a register-by-register basis. This provides additional flexibility (e.g., easy mapping of dual-data-rate functions into the FPGA) while conserving valuable clock resources. The clock source for the R-cell can be chosen from the hardwired clocks, routed clocks, or internal logic.

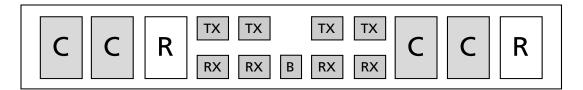

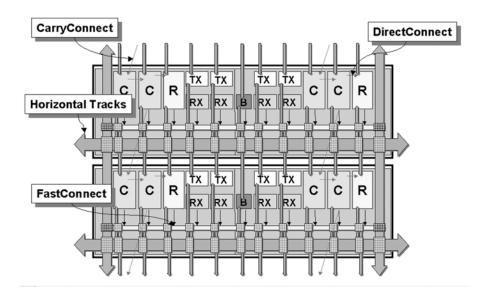

Two C-cells, a single R-cell, and two Transmit (TX) and two Receive (RX) routing buffers form a Cluster, while two Clusters comprise a SuperCluster (Figure 1-4 on page 1-3). Each SuperCluster also contains an independent Buffer (B) module, which supports buffer insertion on high-fanout nets by the place-and-route tool, minimizing system delays while improving logic utilization.

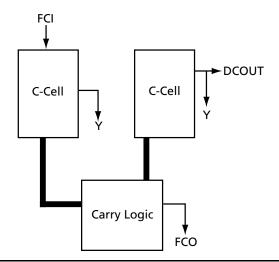

The logic modules within the SuperCluster are arranged so that two combinatorial modules are side-by-side, giving a C-C-R - C-C-R pattern to the SuperCluster. This C-C-R pattern enables efficient implementation (minimum delay) of two-bit carry logic for improved arithmetic performance (Figure 1-5 on page 1-3).

The AX architecture is fully fracturable, meaning that if one or more of the logic modules in a SuperCluster are used by a particular signal path, the other logic modules are still available for use by other paths.

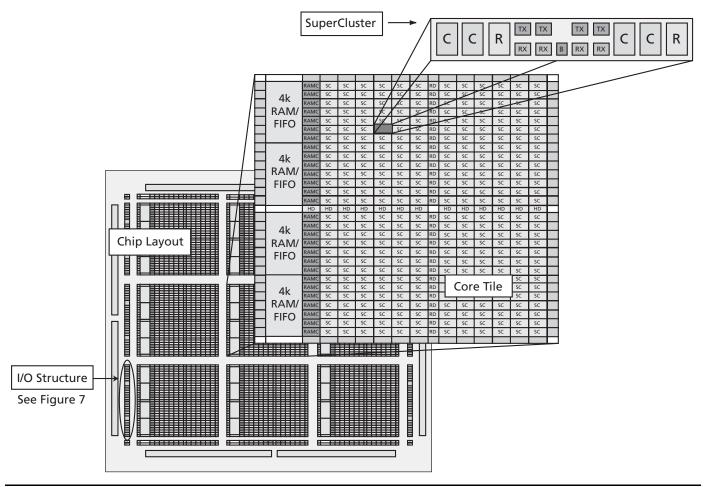

At the chip level, SuperClusters are organized into core tiles, which are arrayed to build up the full chip. For example, the AX1000 is composed of a 3x3 array of nine core tiles. Surrounding the array of core tiles are blocks of I/O Clusters and the I/O bank ring (Table 1-1 on page 1-3). Each core tile consists of an array of 336 SuperClusters and four SRAM blocks (176 SuperClusters and three SRAM blocks for the AX250). The SRAM blocks are arranged in a column on the west side of the tile (Figure 1-6 on page 1-4).

1-2 v2.8

Figure 1-3 • AX C-Cell and R-Cell

Figure 1-4 • AX SuperCluster

Figure 1-5 • AX 2-bit Carry Logic

Table 1-1 • Number of Core Tiles per Device

| Device | Number of Core Tiles |

|--------|----------------------|

| AX125  | 1 regular tile       |

| AX250  | 4 smaller tiles      |

| AX500  | 4 regular tiles      |

| AX1000 | 9 regular tiles      |

| AX2000 | 16 regular tiles     |

v2.8 1-3

Figure 1-6 • AX Device Architecture (AX1000 shown)

### **Embedded Memory**

As mentioned earlier, each core tile has either three (in a smaller tile) or four (in the regular tile) embedded SRAM blocks along the west side, and each variable-aspectratio SRAM block is 4,608 bits in size. Available memory configurations are: 128x36, 256x18, 512x9, 1kx4, 2kx2 or 4kx1 bits. The individual blocks have separate read and write ports that can be configured with different bit widths on each port. For example, data can be written in by eight and read out by one.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using core logic modules. The FIFO width and depth are programmable. The FIFO also features programmable ALMOST-EMPTY (AEMPTY) and ALMOST-FULL (AFULL) flags in addition to the normal EMPTY and FULL flags. In addition to the flag logic, the embedded FIFO control unit also contains the counters necessary for the generation of the read and write address pointers as well

as control circuitry to prevent metastability and erroneous operation. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

### I/O Logic

The Axcelerator family of FPGAs features a flexible I/O structure, supporting a range of mixed voltages with its bank-selectable I/Os: 1.5V, 1.8V, 2.5V, and 3.3V. In all, Axcelerator FPGAs support at least 14 different I/O standards (single-ended, differential, voltage-referenced). The I/Os are organized into banks, with eight banks per device (two per side). The configuration of these banks determines the I/O standards supported (see "User I/Os" on page 2-10 for more information). All I/O standards are available in each bank.

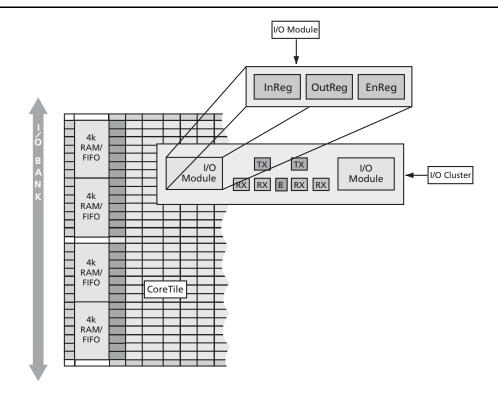

Each I/O module has an input register (InReg), an output register (OutReg), and an enable register (EnReg) (Figure 1-7 on page 1-5). An I/O Cluster includes two I/O modules, four RX modules, two TX modules, and a buffer (B) module.

1-4 v2.8

Figure 1-7 • I/O Cluster Arrangement

# Routing

The AX hierarchical routing structure ties the logic modules, the embedded memory blocks, and the I/O modules together (Figure 1-8 on page 1-6). At the lowest level, in and between SuperClusters, there are three local routing structures: FastConnect, DirectConnect, and CarryConnect routing. DirectConnects provide the highest performance routing inside the SuperClusters by connecting a C-cell to the adjacent R-cell. DirectConnects do not require an antifuse to make the connection and achieve a signal propagation time of less than 0.1 ns.

FastConnects provide high-performance, horizontal routing inside the SuperCluster and vertical routing to the SuperCluster immediately below it. Only one programmable connection is used in a FastConnect path, delivering a maximum routing delay of 0.4 ns.

CarryConnects are used for routing carry logic between adjacent SuperClusters. They connect the FCO output of one two-bit, C-cell carry logic to the FCI input of the two-bit, C-cell carry logic of the SuperCluster below it. CarryConnects do not require an antifuse to make the connection and achieve a signal propagation time of less than 0.1 ns.

The next level contains the core tile routing. Over the SuperClusters within a core tile, both vertical and horizontal tracks run across rows or columns, respectively. At the chip level, vertical and horizontal tracks extend across the full length of the device, both north-to-south and east-to-west. These tracks are composed of highway routing that extend the entire length of the device (segmented at core tile boundaries) as well as segmented routing of varying lengths.

#### **Global Resources**

Each family member has three types of global signals available to the designer: HCLK, CLK, and GCLR/GPSET. There are four hardwired clocks (HCLK) per device that can directly drive the clock input of each R-cell. Each of the four routed clocks (CLK) can drive the clock, clear, preset, or enable pin of an R-cell or any input of a C-cell (Figure 1-3 on page 1-3).

Global clear (GCLR) and global preset (GPSET) drive the clear and preset inputs of each R-cell as well as each I/O Register on a chip-wide basis at power-up.

Each HCLK and CLK has an associated analog PLL (a total of eight per chip). Each embedded PLL can be used for clock delay minimization, clock delay adjustment, or clock frequency synthesis. The PLL is capable of

Figure 1-8 • AX Routing Structures

operating with input frequencies ranging from 14 MHz to 200 MHz and can generate output frequencies between 20 MHz and 1 GHz. The clock can be either divided or multiplied by factors ranging from 1 to 64. Additionally, multiply and divide settings can be used in any combination as long as the resulting clock frequency is between 20 MHz and 1 GHz. Adjacent PLLs can be cascaded to create complex frequency combinations.

The PLL can be used to introduce either a positive or a negative clock delay of up to 3.75 ns in 250 ps increments. The reference clock required to drive the PLL can be derived from three sources: external input pad (either single-ended or differential), internal logic, or the output of an adjacent PLL.

## Low Power (LP) Mode

The AX architecture was created for high-performance designs but also includes a low power mode (activated via the LP pin). When the low power mode is activated, I/O banks can be disabled (inputs disabled, outputs tristated), and PLLs can be placed in a power-down mode. All internal register states are maintained in this mode. Furthermore, individual I/O banks can be configured to opt out of the LP mode, thereby giving the designer access to critical signals while the rest of the chip is in low power mode.

The power can be further reduced by providing an external voltage source (V<sub>PUMP</sub>) to the device to bypass the internal charge pump (See "Low Power Mode" on page 2-89 for more information).

# **Design Environment**

The Axcelerator family of FPGAs is fully supported by both Actel's Libero™ Integrated Design Environment and Designer FPGA Development software. Actel Libero IDE is an integrated design manager that seamlessly integrates design tools while guiding the user through the design flow, managing all design and log files, and passing necessary design data among tools. Additionally, Libero IDE allows users to integrate both schematic and HDL synthesis into a single flow and verify the entire design in a single environment (see the Libero IDE Flow diagram located on Actel's website). Libero IDE includes Synplify® Actel Edition (AE) from Synplicity<sup>®</sup>, ViewDraw<sup>®</sup> AE from Mentor Graphics®, ModelSim® HDL Simulator from Mentor Graphics, WaveFormer Lite™ AE SynaptiCAD<sup>®</sup>, and Designer software from Actel.

Actel's Designer software is a place-and-route tool and provides a comprehensive suite of backend support tools for FPGA development. The Designer software includes the following:

- Timer a world-class integrated static timing analyzer and constraints editor which support timing-driven place-and-route

- NetlistViewer a design netlist schematic viewer

- ChipPlanner a graphical floorplanner viewer and editor

- SmartPower allows the designer to quickly estimate the power consumption of a design

- PinEditor a graphical application for editing pin assignments and I/O attributes

- I/O Attribute Editor displays all assigned and unassigned I/O macros and their attributes in a spreadsheet format

1-6 v2.8

With the Designer software, a user can lock the design pins before layout while minimally impacting the results of place-and-route. Additionally, Actel's back-annotation flow is compatible with all the major simulators and the simulation results can be cross-probed with Silicon Explorer II, Actel's integrated verification and logic analysis tool. Another tool included in the Designer software is the SmartGen core generator, which easily creates popular and commonly used logic functions for implementation into your schematic or HDL design.

Actel's Designer software is compatible with the most popular FPGA design entry and verification tools from EDA vendors, such as Mentor Graphics, Synplicity, Synopsys, and Cadence Design Systems. The Designer software is available for both the Windows and UNIX operating systems.

# **Programming**

Programming support is provided through Actel's Silicon Sculptor II, a single-site programmer driven via a PC-based GUI. In addition, BP Microsystems offers multi-site programmers that provide qualified support for Actel devices. Factory programming is available for high-volume production needs.

# In-System Diagnostic and Debug Capabilities

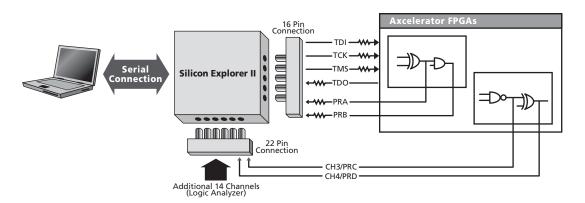

The Axcelerator family of FPGAs includes internal probe circuitry, allowing the designer to dynamically observe and analyze any signal inside the FPGA without disturbing normal device operation. Up to four individual signals can be brought out to dedicated probe pins (PRA/B/C/D) on the device. The probe circuitry is accessed and controlled via Silicon Explorer II (Figure 1-9), Actel's integrated verification and logic analysis tool that attaches to the serial port of a PC and communicates with the FPGA via the JTAG port (See "Silicon Explorer II Probe Interface" on page 2-91).

# **Summary**

Actel's Axcelerator family of FPGAs extends the successful SX-A architecture, adding embedded RAM/FIFOs, PLLs, and high-speed I/Os. With the support of a suite of robust software tools, design engineers can incorporate high gate counts and fixed pins into an Axcelerator design yet still achieve high performance and efficient device utilization.

Figure 1-9 • Probe Setup

#### **Related Documents**

#### **Application Notes**

Simultaneous Switching Noise and Signal Integrity

http://www.actel.com/documents/SSN\_AN.pdf

Axcelerator Family PLL and Clock Management

http://www.actel.com/documents/AX\_PLL\_AN.pdf

Implementation of Security in Actel Antifuse FPGAs

http://www.actel.com/documents/Antifuse\_Security\_AN.pdf

#### **User's Guides and Manuals**

Antifuse Macro Library Guide

http://www.actel.com/documents/libguide\_UG.pdf

SmartGen, FlashROM, Analog System Builder, and Flash Memory System Builder

http://www.actel.com/documents/genguide\_ug.pdf

Silicon Sculptor II User's Guide

http://www.actel.com/documents/silisculptII\_sculpt3\_ug.pdf

#### **White Paper**

Design Security in Nonvolatile Flash and Antifuse FPGAs http://www.actel.com/documents/DesignSecurity\_WP.pdf Understanding Actel Antifuse Device Security http://www.actel.com/documents/DesignSecurity\_WP.pdf

#### Miscellaneous

Libero IDE flow diagram http://www.actel.com/products/tools/libero/flow.html