## PHAST-1 Device SONET STS-1 Overhead Terminator TXC-06101

**DATA SHEET**

#### **FEATURES I**

- Provides SONET interface to any type of payload

- Programmable STS-1 or STS-N modes

- Receive bit-serial STS-1 signal input to the Line Side using external reference frame pulse for STS-N applications

- Transmit bit-serial STS-1 signal output from the Line Side using external reference frame pulse for outgoing phase synchronization

- Programmable: full STS-1 or SPE-only I/O on the Terminal Side

- 51.84 Mbit/s bit-serial, or 6.48/19.44 Mbyte/s byte-parallel I/O on the Terminal Side

- Optional AIS communication with peer PHAST-1, SOT-1, SOT-1E, or SOT-3 devices

- Interfaces to microprocessors with hierarchical scan and optional hardware interrupt on alarms

- SONET alarm processing and performance monitoring

- · Meets ANSI and Bellcore standards:

- T1.105-1995

- GR-1400-CORE

- GR-253-CORE

- GR-499

- TR-NWT-000496

- GR-1230

- Ring port for USHR/P support

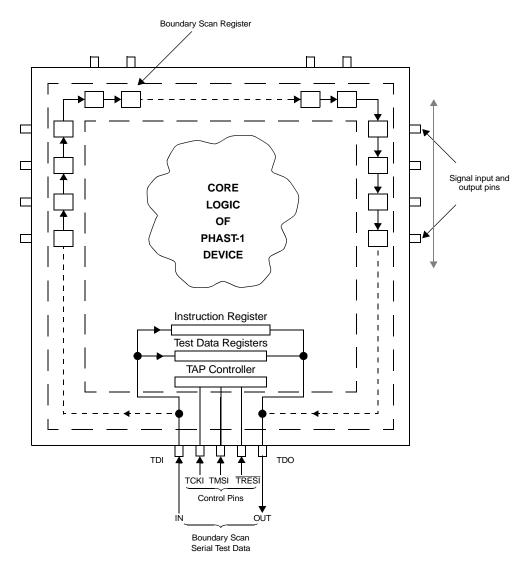

- Boundary Scan Capability (IEEE 1149.1)

- Single + 3.3 volt ± 5% power supply

- 5 volt tolerant inputs

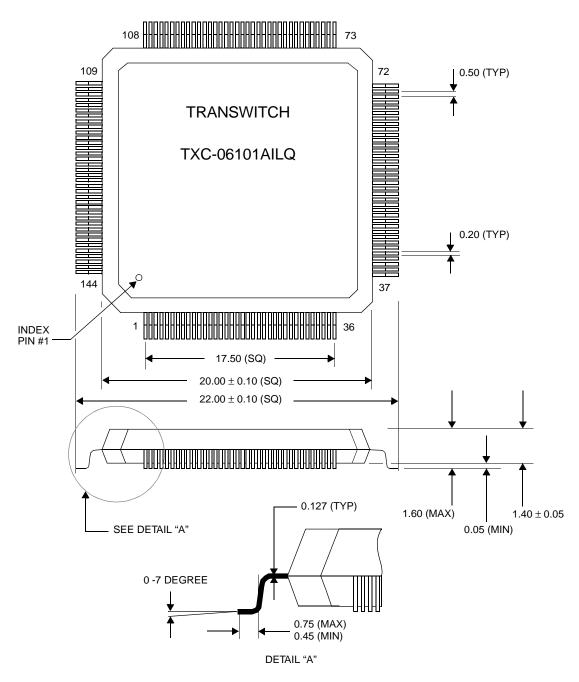

- 144-pin low profile plastic quad flat package

#### **DESCRIPTION**

The PHAST-1 SONET STS-1 Overhead Terminator performs Section, Line and Path Overhead processing for STS-1 SONET signals. This versatile device can be used anywhere in a SONET network where STS-1 signals are in use, e.g., repeaters, and Line or Path termination points. Interfaces are provided for both Section and Line Orderwire and Datacom channels. Further, control bits in the Memory Map enable the PHAST-1 to perform loopback and serial or parallel input/output. Line Side and Terminal Side clock rates can differ. The Receive and Transmit Pointers are recalculated as necessary to compensate for clock differences. All overhead bytes are stored in on-chip RAM. New overhead bytes can be substituted from RAM to either the Terminal or Line Side, depending on the application. The PHAST-1 also provides alarm detection and AIS generation, as well as software and hardware interrupt in the event of errors.

#### **APPLICATIONS I**

- SONET W-DCS/B-DCS

- SONET terminal or add/drop multiplexers

- High-speed data communication

- Payload extraction, introduction into STS-1

- STS-N multiplexer

- SONET test sets

U.S. Patents No. 4,967,405; 5,040,170; 5,141,529; 5,265,096; 5,724,362 U.S. and/or foreign patents issued or pending

Copyright © 2001 TranSwitch Corporation

TranSwitch and TXC are registered trademarks of TranSwitch Corporation

Document Number: TXC-06101-MB Ed. 3, April 2001

TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 • USA

Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com

## **TABLE OF CONTENTS**

| SECTION                                                | PAGE |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| List of Tables                                         | 5    |

| List of Equations                                      | 5    |

| SONET Tutorial                                         | 6    |

| Formats                                                | 6    |

| Overhead                                               | 10   |

| Pointers                                               | 17   |

| Block Diagram                                          | 20   |

| Receive Side                                           | 20   |

| Transmit Side                                          | 21   |

| Pin Diagrams                                           | 22   |

| Pin Descriptions                                       | 23   |

| Absolute Maximum Ratings and Environmental Limitations |      |

| Thermal Characteristics                                |      |

| Power Requirements                                     |      |

| Input, Output and I/O Parameters                       |      |

| Timing Characteristics                                 |      |

| Timing Generators                                      |      |

| Terminal Timing In Parallel Modes                      |      |

| Line Side Timing                                       |      |

| Order Wire-APS / TOH Port Timing                       |      |

| Section and Line DCC Port Timing                       |      |

| POH Port Timing                                        |      |

| Ring Port Timing                                       |      |

| Terminal Side Timing                                   |      |

| ISC Port Timing                                        |      |

| Microprocessor Interface Timing                        |      |

| Boundry Scan Timing                                    |      |

| Memory Map                                             |      |

| Status Register Descriptions                           |      |

| Control Register Descriptions                          |      |

| Control Register 0                                     |      |

| Control Register 1                                     |      |

| Control Register 8                                     |      |

| Operation                                              |      |

| Primary Operating Modes                                |      |

| Timing Generators                                      |      |

| Re-timing                                              |      |

| Line Formats                                           |      |

| Terminal Formats                                       |      |

| Ex-Kx / TOH Ports                                      |      |

| DCC Ports                                              |      |

| POH Ports                                              |      |

| Ring Ports                                             |      |

| ISC Port                                               |      |

| Rx TOH Processing                                      |      |

| Rx POH Processing                                      |      |

| Rx Side Alarm Hierarchy                                |      |

| Rx Terminal Output Generation                          |      |

| Rx Terminal Output Generation                          |      |

| 11/4 TOTHING OUDUG                                     | 104  |

## <u>TranSwitch'</u>

#### **DATA SHEET**

| Tx Terminal Inputs                      | 164 |

|-----------------------------------------|-----|

| Tx Terminal Overhead Processing         | 164 |

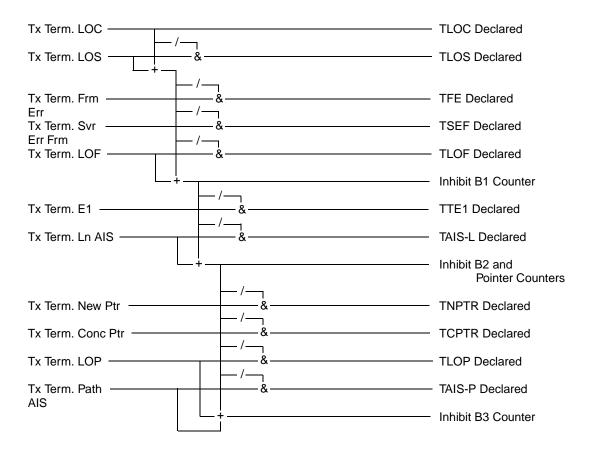

| Tx Side Alarm Hierarchy                 | 168 |

| Transmit POH Assembly                   | 169 |

| Transmit TOH Assembly                   | 171 |

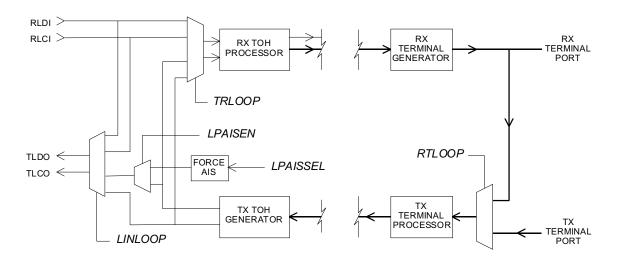

| Loopbacks                               | 178 |

| Resets                                  | 179 |

| Microprocessor Interface                | 180 |

| Test and Diagnostics                    | 184 |

| Package Information                     | 186 |

| Application Diagram                     |     |

| Ordering Information                    | 188 |

| Related Products                        | 188 |

| List of Data Sheet Changes              | 191 |

| Documentation Update Registration Form* | 195 |

## **LIST OF FIGURES**

| FIGUI | RE PAG                                     | ЭE  |

|-------|--------------------------------------------|-----|

| 1     | STS-1 Format                               | . 7 |

| 2     | STS-N Format                               | . 7 |

| 3     | STS-Nc Format                              | . 8 |

| 4     | VTn Format                                 | . 8 |

| 5     | VT Sizes                                   | . 9 |

| 6     | VT Superframe                              | 10  |

| 7     | Overhead Utilization                       | 11  |

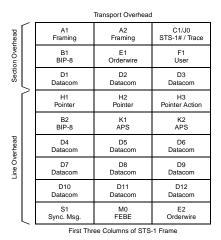

| 8     | STS-1 Overhead                             | 12  |

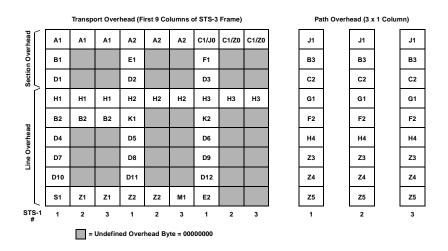

| 9     | STS-3 Overhead                             | 12  |

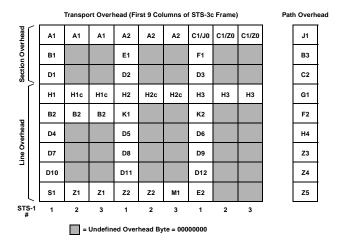

| 10    | STS-3c Overhead                            | 13  |

| 11    | STS-1 Frame                                |     |

| 12    | Positive Pointer Justifications            | 18  |

| 13    | Negative Pointer Justifications            |     |

| 14    | PHAST-1 TXC-06101 Block Diagram            |     |

| 15    | PHAST-1 TXC-06101 Functional Pin Diagram   |     |

| 16    | PHAST-1 TXC-06101 Actual Pin Diagram       |     |

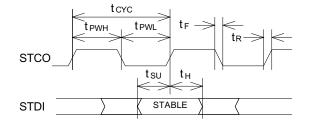

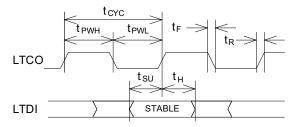

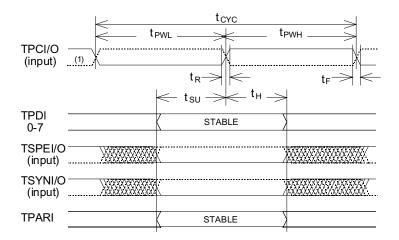

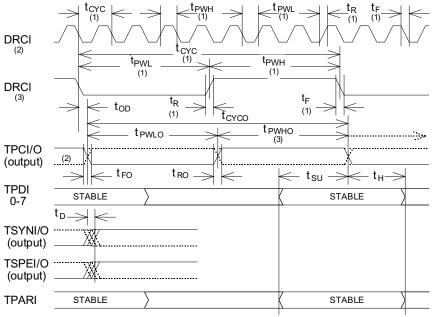

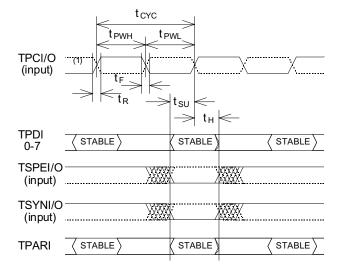

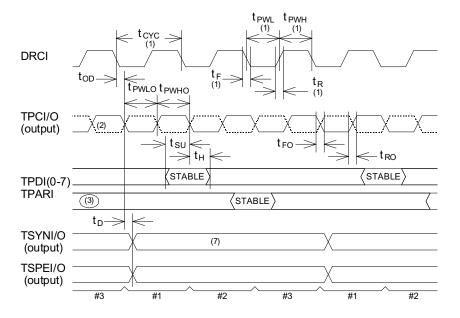

| 17    | TTG and LTG 51.84 Mbit/s Input Timing      |     |

| 18    | TTG and LTG 6.48 Mbyte/s Input Timing      |     |

| 19    | TTG and LTG 19.44 Mbyte/s Input Timing     |     |

| 20    | Frame Phase Margin - Tx Re-Timing Disabled |     |

| 21    | Receive Line Input Timing                  |     |

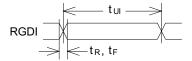

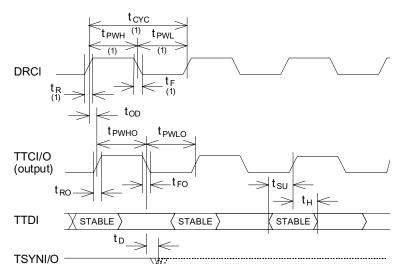

| 22    | Transmit Line Output Timing                |     |

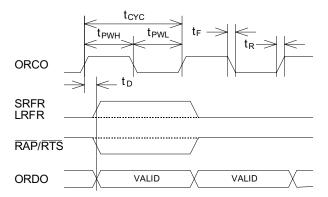

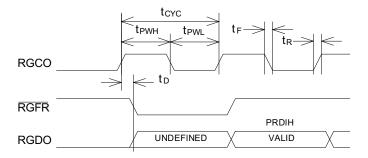

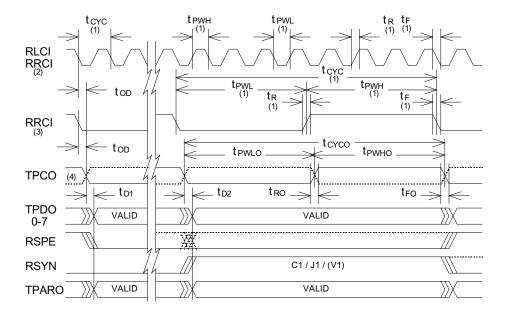

| 23    | Rx OW-APS / TOH Port Output Timing         |     |

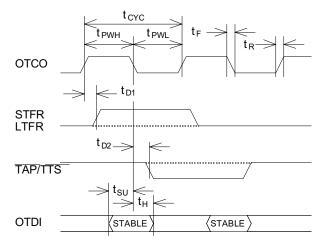

| 24    | Tx OW-APS / TOH Port Input Timing          |     |

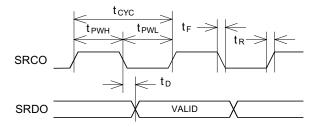

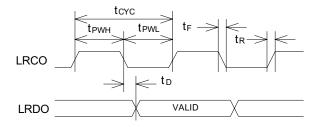

| 25    | Rx Section DCC Port Output Timing          |     |

| 26    | Rx Line DCC Port Output Timing             |     |

| 27    | Tx Section DCC Port Input Timing           |     |

| 28    | Tx Line DCC Port Input Timing              |     |

| 29    | Rx POH Port Output Timing                  | 49  |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

## **DATA SHEET**

| 30       | Tx POH Port Input Timing                                        | 50  |

|----------|-----------------------------------------------------------------|-----|

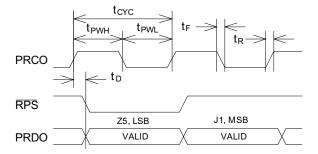

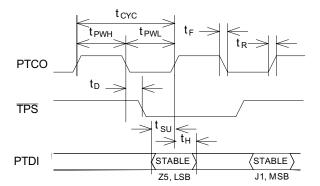

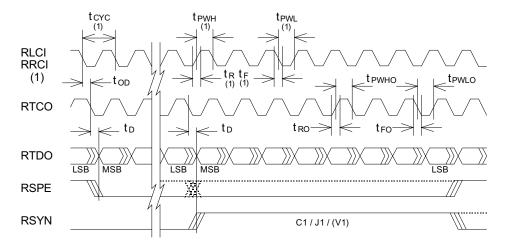

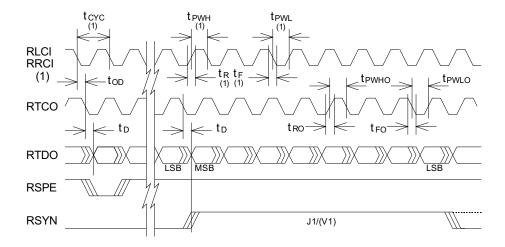

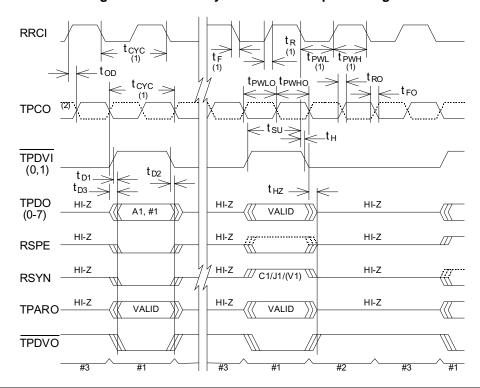

| 31       | Rx Ring Port Output Timing                                      | 51  |

| 32       | Tx Ring Port Input Timing                                       | 51  |

| 33       | SONET and Datacom Serial Output Timing                          | 52  |

| 34       | SPE-Only Output Timing                                          | 53  |

| 35       | 6.48 Mbyte/s Parallel Output Timing                             |     |

| 36       | 19.44 Mbyte/s Parallel Output Timing                            |     |

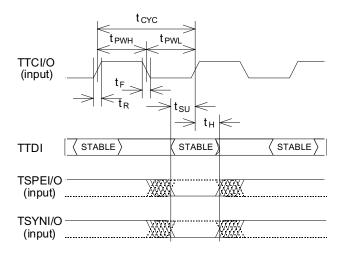

| 37       | Serial SONET and SPE-Only Input Timing                          |     |

| 38       | Serial Datacom Input Timing                                     |     |

| 39       | 6.48 Mbyte/s Parallel SONET Input Timing                        |     |

| 40       | 6.48 Mbyte/s Parallel Datacom Input Timing                      |     |

| 41       | 19.44 Mbyte/s Parallel SONET Input Timing                       |     |

| 42       | 19.44 Mbyte/s Parallel Datacom Input Timing                     |     |

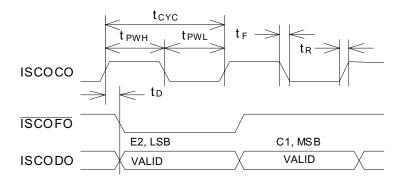

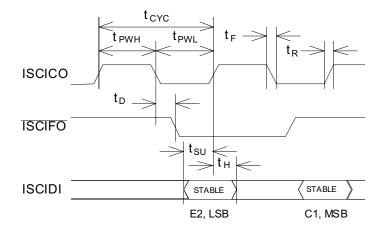

| 43       | ISC Port Output Timing                                          |     |

| 44       | ISC Port Input Timing                                           |     |

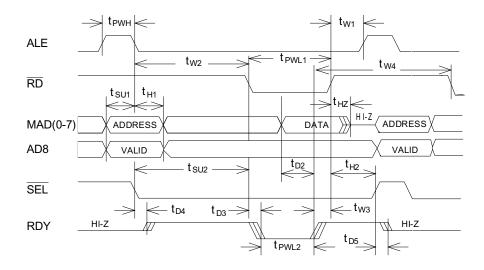

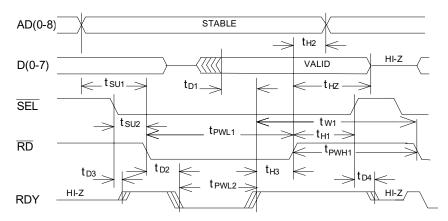

| 45       | Intel Multiplexed Read Timing                                   |     |

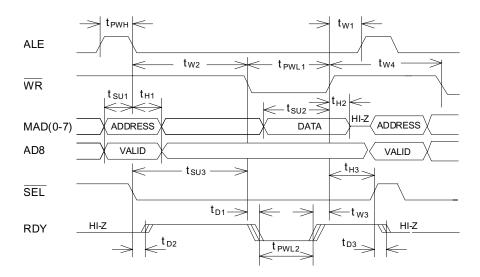

| 46       | Intel Multiplexed Write Timing                                  |     |

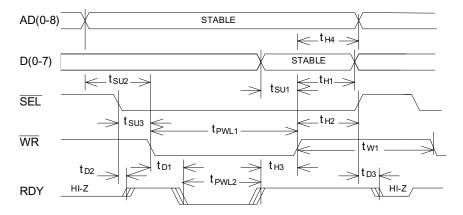

| 40<br>47 | Intel Read Timing                                               |     |

|          | •                                                               |     |

| 48       | Intel Write Timing                                              |     |

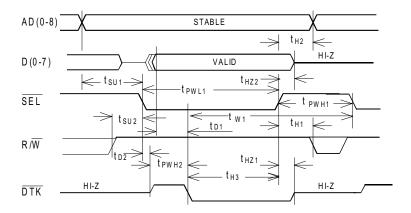

| 49       | Motorola Read Timing                                            |     |

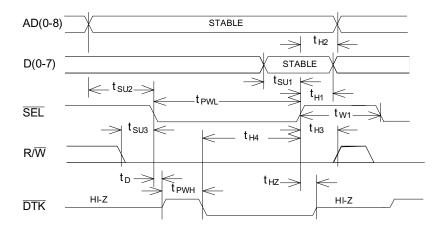

| 50       | Motorola Write Timing                                           |     |

| 51       | Boundary Scan Timing                                            |     |

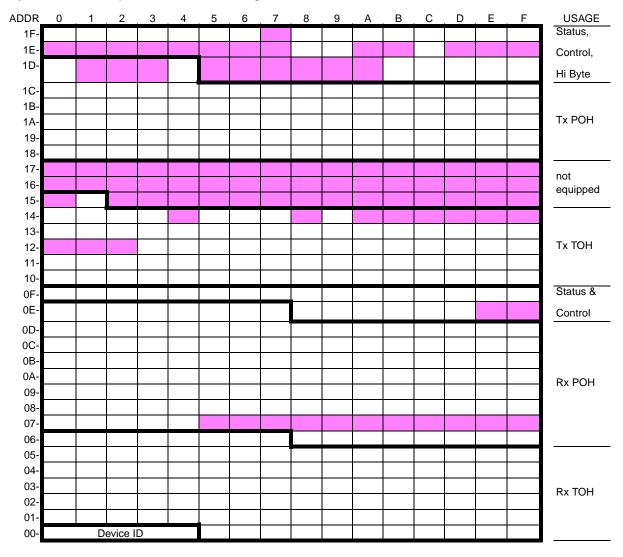

| 52       | Overall Memory Map                                              |     |

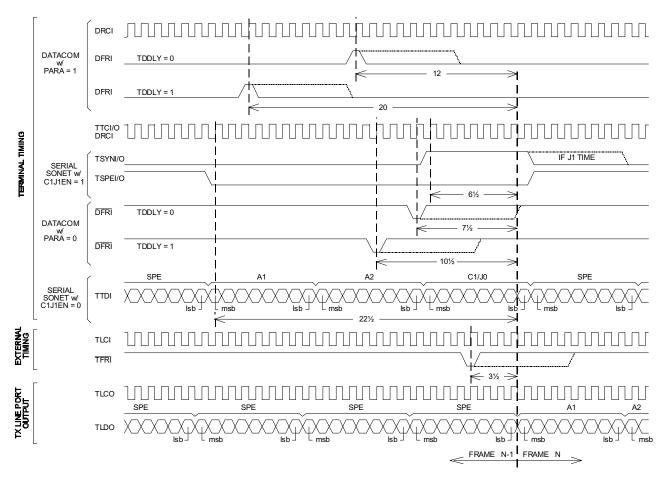

| 53       | Tx Line Format                                                  |     |

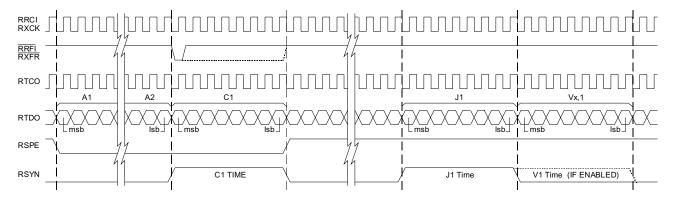

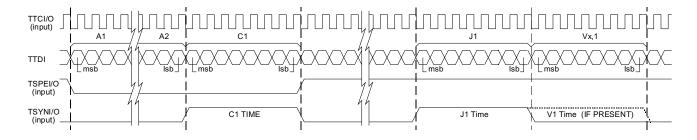

| 54       | Rx Terminal Port Serial SONET Format                            |     |

| 55       | Tx Terminal Port Serial SONET Format                            |     |

| 56       | Rx Terminal Port Parallel 6.48 Mbyte/s SONET Format             |     |

| 57       | Tx Terminal Port Parallel 6.48 Mbyte/s SONET Format             |     |

| 58       | Rx Terminal Port Parallel 19.44 Mbyte/s SONET Format            |     |

| 59       | Rx Terminal Port Parallel 19.44 Mbyte/s SONET FORMAT Example    |     |

| 60       | Tx Terminal Port Parallel 19.44 Mbyte/s SONET Format            |     |

| 61       | Rx Terminal Port Serial Datacom Format                          |     |

| 62       | Tx Terminal Port Serial Datacom Format                          |     |

| 63       | Rx Terminal Port Parallel 6.48 Mbyte/s Datacom Format           |     |

| 64       | Tx Terminal Port Parallel 6.48 Mbyte/s Datacom Format           |     |

| 65       | Rx Terminal Port Parallel 19.44 Mbyte/s Datacom Format          |     |

| 66       | Tx Terminal Port Parallel 19.44 Mbyte/s Datacom Format          |     |

| 67       | Rx Terminal Port SPE-only Format                                |     |

| 68       | Tx Terminal Port SPE-only Format                                | 145 |

| 69       | Rx OW/APS Port                                                  | 146 |

| 70       | Tx OW/APS Port                                                  | 146 |

| 71       | Rx All TOH Port                                                 | 147 |

| 72       | Tx All TOH Port                                                 | 147 |

| 73       | Rx POH Port                                                     | 149 |

| 74       | Tx POH Port                                                     | 149 |

| 75       | Rx and Tx Ring Ports                                            | 149 |

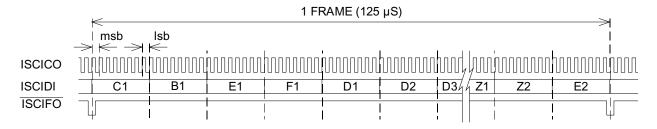

| 76       | ISC Port Input                                                  | 150 |

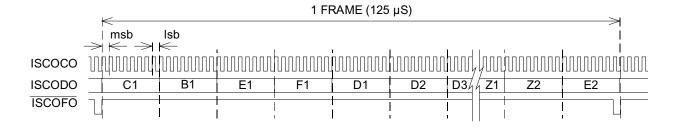

| 77       | ISC Port Output                                                 | 151 |

| 78       | Loopbacks                                                       |     |

| 79       | Boundary Scan Schematic                                         |     |

| 80       | PHAST-1 TXC-06101 144-Pin Low Profile Plastic Quad Flat Package |     |

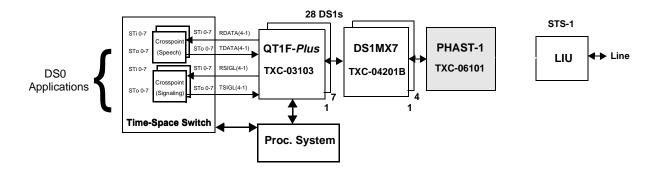

| 81       | Asynchronous DS0 to/from Synchronous STS-1 Application          |     |

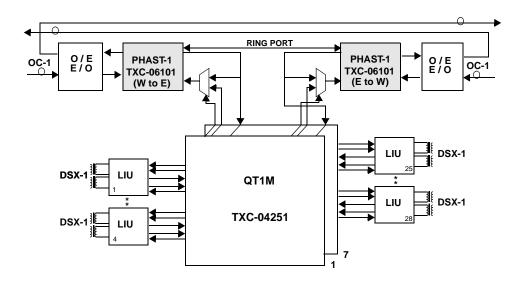

| 82       | Asynchronous DSX-1 Mapped to OC-1 Ring-Protected Application    |     |

|          | •••                                                             |     |

## **LIST OF TABLES**

| TABL | _E P/                                                | AGE |

|------|------------------------------------------------------|-----|

| 1    | Primary Operating Modes                              | 128 |

| 2    | Rx Timing Selection                                  |     |

| 3    | Datacom Mode Timing Selection                        | 129 |

| 4    | Tx Timing Selection                                  | 130 |

| 5    | Rx Re-Timing Control                                 | 131 |

| 6    | Tx Re-Timing Control                                 | 132 |

| 7    | Received TOH Locations                               | 152 |

| 8    | Debounced TOH Locations                              | 152 |

| 9    | B2EBER Parameters For Signal Degradation or Failure  | 154 |

| 10   | B2 Error Alarm Performance For BER Threshold of 10-3 |     |

| 11   | B2 Error Alarm Performance For BER Threshold of 10-4 | 155 |

| 12   | Received POH Locations                               |     |

| 13   | Debounced POH Locations                              | 157 |

| 14   | RDI-P Format                                         | -   |

| 15   | B3EBER Parameters For Signal Degradation or Failure  |     |

| 16   | B3 ERROR Alarm Performance For BER Threshold of 10-5 |     |

| 17   | Terminal Insert TOH Locations                        |     |

| 18   | Terminal TOH Options                                 |     |

| 19   | Terminal Insert POH Locations                        |     |

| 20   | Terminal TOH Locations                               |     |

| 21   | Terminal POH Locations                               |     |

| 22   | Tx Insert POH Locations                              |     |

| 23   | Tx Line POH Options                                  |     |

| 24   | Tx Insert TOH Locations                              |     |

| 25   | Tx C1/J0 Options                                     |     |

| 26   | Transport Layer Events                               |     |

| 27   | Path Layer Events                                    |     |

| 28   | Device Layer Events                                  | 183 |

|      |                                                      |     |

## **LIST OF EQUATIONS**

| EQUA | ATION PA                                | \GE |

|------|-----------------------------------------|-----|

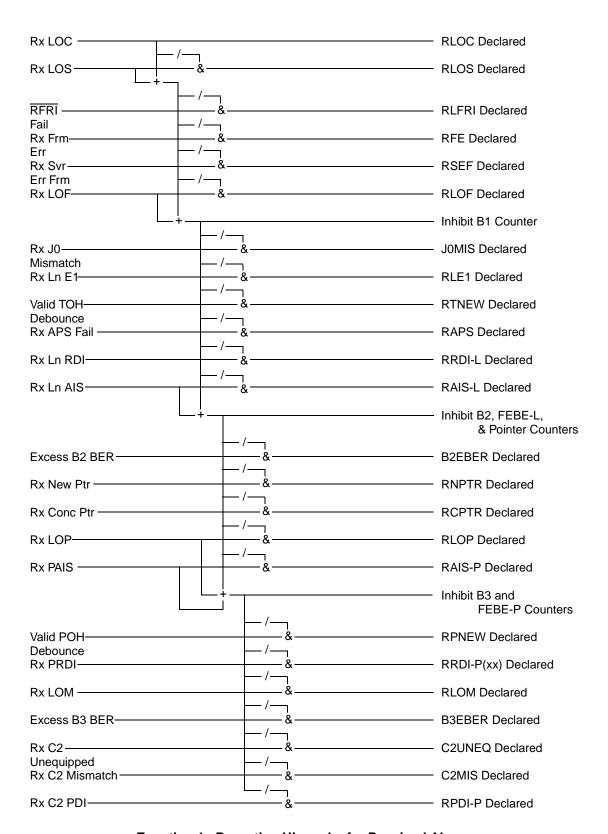

| 1    | Reporting Hierarchy for Received Alarms | 160 |

| 2    | Reporting Hierarchy for Transmit Alarms | 168 |

#### SONET TUTORIAL

A primary goal in developing the SONET (Synchronous Optical NETwork) format was to define a synchronous, optical hierarchy with sufficient flexibility to carry many different payloads. This has been accomplished by defining a basic signal of 51.84 Mbit/s and a byte-interleaved multiplex scheme that results in a family of standard rates and formats defined at a rate of N times 51.84 Mbit/s, where N is an integer. Since some signals that must be transported have speeds greater than the basic rate, a technique of linking several basic rate signals together to form a transport signal of varying capacity has also been defined. There are three major differences between the SONET Hierarchy and the North American Digital Hierarchy (NADH)<sup>1</sup>:

| <ol> <li>SONET</li> </ol> | is synchronous. All SONET tributaries in a SONET network must be traceable to one |

|---------------------------|-----------------------------------------------------------------------------------|

|                           | or more Stratum 1 synchronization sources.                                        |

NADH is asynchronous. The tributaries need not be synchronized.

2. SONET is a harmonic multiplexing structure. All higher rate SONET signals are integer

multiples of a base rate. Lower order SONET tributaries are byte-interleaved to

form the higher order SONET signal.

NADH is hierarchical. Higher order multiplexing is accomplished with bit stuffing to

accommodate speed differences in lower order tributaries.

3. <u>SONET</u> overhead (Framing, Performance Monitoring, Alarms, etc.) and payload are distinct

entities. In a SONET signal the payload bits do not occupy a fixed position in relation to the transport overhead bits. A pointer mechanism is used to identify the start of

the payload.

NADH overhead bits and payload bits have a fixed, unvarying relationship to each other.

The Basic modular signal (at 51.84 Mbit/s) is called the Synchronous Transport Signal level One (STS-1). The optical counterpart is the Optical Carrier level One (OC-1), which is the result of direct optical conversion of the STS-1 signal. Higher level signals are denoted by STS-N and OC-N, where N is an Integer. At present the standardized values of N are: 1, 3, 12, 24, 48 and 192. These values provide standardized multiplexing rates for SONET systems at 51.84 Mbit/s, 155.52 Mbit/s, 622.08 Mbit/s, 1.24416 Gbit/s, 2.48832 Gbit/s and 9.95328 Gbit/s, respectively.

#### **FORMATS**

There are four basic formats upon which the SONET Hierarchy is built.

#### **STS-1 Structure**

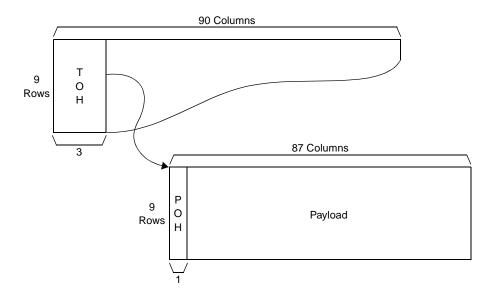

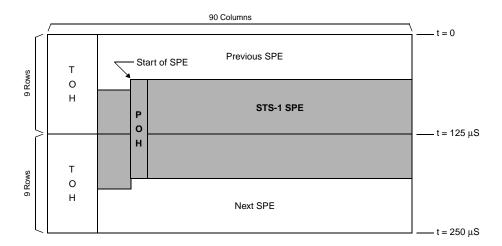

The basic SONET format is the 51.84 Mbit/s signal designated STS-1. It consists of 810 eight-bit bytes arranged in a matrix of nine rows each of which has 90 columns as shown in Figure 1. This nine by 90 arrangement is referred to as a SONET Frame. It repeats every 125 microseconds. The first three columns consist of the Transport Overhead (TOH). The remaining 87 columns are referred to as the Synchronous Payload Envelope (SPE). It is this portion of a SONET signal that is allowed to "float." Within the TOH is a pointer that identifies the starting position of the SPE with respect to the TOH Bytes in the Frame. The first column of the SPE is the Path Overhead (POH). The other 86 columns contain the actual payload information whose capacity is approximately 50 Mbit/s.

<sup>1.</sup> The North American Digital Hierarchy is described in ANSI standard T1.107. The ITU-T term "PDH" (Plesiochronous Digital Hierarchy) is used to refer generically to an asynchronous multiplexing structure.

Figure 1. STS-1 Format

#### **STS-N Structure**

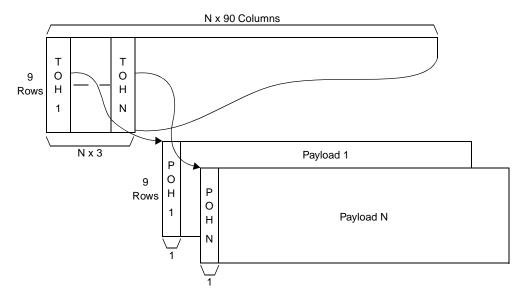

STS-N formats are higher order multiplex structures which allow the transportation of N number of 50 Mbit/s payloads (e.g., STS-3 transports three 50 Mbit/s payloads). As shown in Figure 2, the Frame consists of nine rows and N  $\times$  90 columns. The TOH is N  $\times$  3 columns wide. There are N number of nine by 87 SPEs, each of which contains one column of POH. The TOH contains N number of pointers: one for each of the SPEs.

Figure 2. STS-N Format

#### STS-Nc Structure

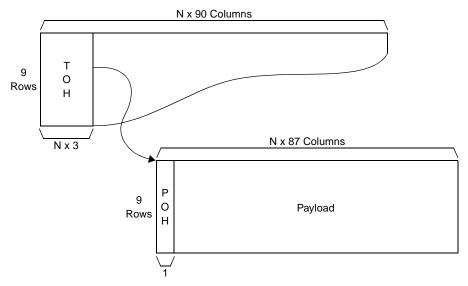

As mentioned earlier, SONET contains a mechanism by which payloads that are larger than  $\approx 50$  Mbit/s can be carried. This mechanism is called Concatenation and is indicated by the designation Nc. STS-Nc formats are higher order structures which allow the transportation of a single payload whose bandwidth is approximately N × 50 Mbit/s (e.g., STS-3c transports a single 149.76 Mbit/s payload). The STS-Nc format is shown in Figure 3. As with the STS-N format, the Frame consists of nine rows and N × 90 columns. The TOH is N × 3 columns wide. There is a single SPE which is nine rows by N × 87 columns. The first SPE column is used for POH. The TOH contains one pointer which identifies the start of the SPE in the Frame.

Figure 3. STS-Nc Format

#### **Virtual Tributary Structures**

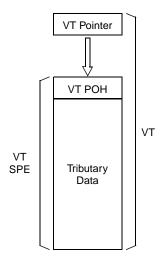

The Virtual Tributary (VT) is a structure designed for transport and switching of sub-STS-1 payloads (payloads less than DS3). As shown in Figure 4, it contains a VT Pointer, which indicates the start of the VT SPE. The VT SPE is composed of VT POH and Tributary Data (Payload). The VT Pointer provides for flexible and dynamic alignment of the VT SPE within the VT, independent of other VTs in the STS-1 SPE.

Figure 4. VTn Format

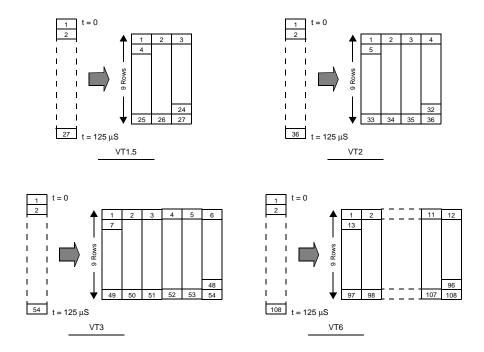

There are four sizes of VT: the VT1.5 ( $\approx$  1.7 Mbit/s), the VT2 ( $\approx$  2.3 Mbit/s), the VT3 ( $\approx$  3.5 Mbit/s) and the VT6 ( $\approx$  6.9 Mbit/s). These are shown in Figure 5. In the nine-row format of the STS-1 SPE they occupy three columns, four columns, six columns and twelve columns, respectively. VTs may only be carried in an STS-1 SPE. STS-Nc SPEs cannot be subrated into VTs. For example, to carry 84 DS1s in SONET an STS-3 format must be used with each STS-1 SPE organized as 28 VT1.5s.

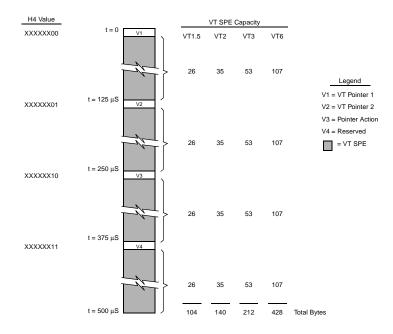

Four consecutive 125-microseconds frames of the STS-1 SPE are organized into a 500-microseconds Superframe, the phase of which is indicated by a Multiframe Indicator Byte (H4) in the STS-1 POH. This defines a 500-microseconds structure for each of the VTs, called the VT Superframe, which is shown in Figure 6. The VT Superframe contains the VT Pointer and the VT SPE. The VT Pointer occupies four bytes designated V1, V2, V3 and V4 and the remaining bytes define the VT SPE, the capacity of which is different for each VT type. The placement of the V1 through V4 Bytes is such that they will appear in Byte 1 (shown in Figure 5) of the VT regardless of the VT size. Since the PHAST-1 does not process VTs there will be no further discussion of VT characteristics.

Figure 5. VT Sizes

#### **OVERHEAD**

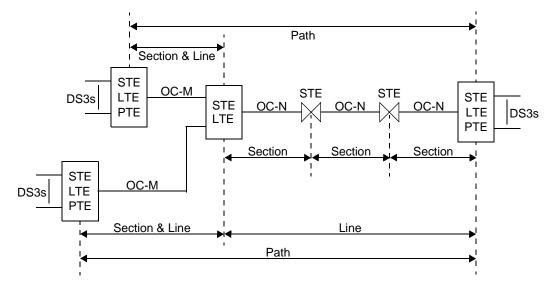

The overhead and transport functions in SONET have been broken into layers to promote understanding and structure. In order of increasing complexity the layers are: Physical Medium, Section, Line and Path. When viewed with a bottom-up approach, each layer builds upon the services provided by the lower layer. The Physical Medium Layer provides transmission at a standard bit rate. The Section layer provides framing, scrambling, and Section maintenance for the bits being transmitted. The Line layer provides Line maintenance and protection as well as multiplexing of the STS SPEs. The Path layer provides the payload mapping function and Path maintenance. Note than all layers can be implemented in a single piece of equipment or they can be broken into multiple pieces of equipment.

Figure 6. VT Superframe

#### **Physical Medium Layer**

The Physical Medium Layer deals with transport of the bits across the transmission medium. No overhead is associated with this layer. Its main function is the conversion between signals internal to a Network Element (NE) and signals suitable for transmission. Issues dealt with at this layer include pulse shape, power levels, and (for optical equipment) wavelength. Electro-optical units communicate at this level.

### **Section Layer**

The Section Layer deals with the reliable transport of an STS-N frame across the physical medium. Functions within this layer include framing, scrambling, error monitoring, data communications, and a local orderwire. Section and Physical Medium Layers can be utilized in some equipment without any higher order layers. A regenerator would operate in this manner.

#### **Line Layer**

The Line Layer deals with the reliable transport of Path Layer payload and its overhead across the Section and Physical Medium Layers. Overhead added here is accessed at points where SPEs are multiplexed together. The functions of this layer are to provide synchronization and multiplexing for the Path Layer, as well as error monitoring, data communications, orderwire, and protection signaling for Line protection switching. An example of equipment that communicates at this level is an OC-M to OC-N multiplexer *where*: M < N.

#### Path Layer

The Path Layer deals with the reliable transport of services over the Line, Section and Physical Medium Layers. Examples of such services are DS1s, DS3s and ATM signals. The main function of this layer is to map the services into the format required by the Line Layer. In addition, this layer provides error monitoring and connectivity checks. The overhead defined for this layer is read, interpreted, and modified by equipment that creates or disassembles the SONET payload for a given service. POH may be monitored but not modified by Line processing equipment. There is an exception to this last statement. Line processing elements that have implemented Tandem Connection Maintenance (see ANSI T1.105.05) may modify certain Path Layer bytes. However, the original Path Layer information must be restored at the termination point of the Tandem Connection function. An example of equipment that communicates at the Path level is a DS3 to STS-1 mapping circuit.

#### Overhead Termination

Any NE that originates or terminates an overhead layer is considered to be a terminating entity for that layer. This defines three types of NEs:

- Section Terminating Equipment (STE)

- Line Terminating Equipment (LTE)

- 3. Path Terminating Equipment (PTE)

Peer communications occur between pieces of equipment that terminate a particular layer. Examples of STE, LTE, and PTE Equipment and the layers processed by each entity are shown in Figure 7. There are four multiplexers and two regenerators (repeaters) in this example. The two multiplexers on the left and the one on the right are multiplexing and de-multiplexing DS3s into and out of a SONET signal. The multiplexer in the middle represents a higher order unit which is multiplexing and de-multiplexing lower order SONET signals to and from a higher order signal. Since the Physical Medium Layer does not have any overhead associated with it, it will not be discussed. By definition, all SONET NEs are Section Terminating and a regenerator is only STE. There are five Section Layer peer communication links. There are three Line Layer peer communication links: one from each of the leftmost multiplexers to the middle multiplexer, and one between the middle multiplexer and the multiplexer on the right. Finally, there are two Path Layer peer communication links. These exist between the multiplexers on the left and the multiplexer on the right.

Figure 7. Overhead Utilization

#### **Overhead Locations**

The functions of the Section and Line Layers have been combined into a structure of 27 bytes called Transport Overhead (TOH) which occupies the first three columns of an STS-1 Frame. The first three rows are Section Overhead (SOH). The last six rows are Line Overhead (LOH). This is shown in Figure 8. In STS-N and Nc frames there are  $3 \times N$  TOH columns. Figures 9 and 10 represent STS-N and Nc formats using STS-3 and 3c as an example. The byte-interleaved characteristic of SONET can be seen in these figures. Some of the transport overhead fields in STS-1 numbers two through N are the same as for STS-1 number one and some are not. In the STS-3 Format there are three H1 and H2 Bytes. Each H1, H2 combination is a pointer for one of the three payloads that is being transported. The STS-3c format is carrying one  $\approx$  150 Mbit/s payload. There is only one pointer. The H1 and H2 bytes in the STS-1 number one position are the pointer. The two remaining H1 and H2 byte pairs in STS-1 positions two and three are the Concatenation Indicators.

| Path Overhead       |

|---------------------|

| J1<br>Trace         |

| B3<br>BIP-8         |

| C2<br>Signal Label  |

| G1<br>Path Status   |

| F2<br>User          |

| H4<br>Multiframe    |

| Z3<br>Growth        |

| Z4<br>Growth        |

| Z5<br>Tandem Conn.  |

| First Column of SPE |

First Column of SP

Figure 8. STS-1 Overhead

The Path Layer functions are assigned to the nine bytes occupying the first column of the STS SPE. The distinction between TOH and POH is made so that transmission equipment can be specified without regard to the information structure that is being transported. The STS-1 and STS-3c formats have only one POH field. In the STS-3 format there are three POH fields, one for each payload. The shaded diagonals represent Pointer and POH bytes associated with STS-1 numbers two and three.

Figure 9. STS-3 Overhead

Figure 10. STS-3c Overhead

#### **Section Overhead Definitions - SOH**

The definitions for the Section Overhead Bytes are given below.

- A1, A2: Framing Two bytes are allocated in each STS-1 for Framing. The Pattern is A1 = F6[H] and A2 = 28[H]. These bytes are provided in all STS-1 portions of an STS-N/Nc signal.

- C1: <u>STS-1 I.D.</u> In earlier editions of the SONET standard, one byte labeled C1 in each STS-1 was allocated for an STS-1 identification function. These bytes are no longer used for this purpose. Instead, this overhead is currently allocated for Section Trace and Section Growth (defined below). However, to ensure interworking with older equipment, these bytes must be capable of transmitting and receiving the STS-1 Identification Codes. When used in this manner the following definition will apply. The C1 byte in Each STS-1 shall be set to a binary number corresponding to its order of appearance in the byte-interleaved STS-N frame where 01[H] is the number for the first STS-1 appearing in the frame. The C1 Byte is defined for all STS-1s in an STS-N/Nc signal.

- J0: Section Trace One byte is allocated to be used for a Section Trace function. This byte is defined only for STS-1 number one in an STS-N/Nc signal. J0 (formerly C1 of STS-1 number one) is used to repetitively transmit a one-byte fixed length string so that a receiving terminal can verify its continued connection to the intended transmitter. Any value in the range of 00[H] through FF[H] may be placed in this byte. When the Section Trace function is not supported or if no value has been assigned then 01[H] shall be transmitted.

- Z0: <u>Section Growth</u> One byte is defined in each STS-1 for future growth, except for STS-1 number one (defined as J0). For interworking with older equipment, the Z0 bytes shall be capable of being set consistent with the C1 definition described above.

- B1: Section BIP-8 One byte is allocated for a Section Error Monitoring function. This function is a bit-interleaved parity 8 code using even parity. The Section BIP-8 is calculated over all bits of the previous STS-N/Nc frame after scrambling. The computed BIP-8 is placed in the B1 Byte before scrambling. This byte is defined only for STS-1 number one of an STS-N/Nc signal.

- E1: Orderwire One byte is allocated to be used as a Section Orderwire. This is a local orderwire channel reserved for voice communications between STEs, hubs, and remote NEs. It is only defined for STS-1 number one.

PHAST-1 TXC-06101

- F1: Section User Channel One byte is set aside for the user's purposes. This byte is passed from Section to Section within a transmission system and is readable, writable, or both at each STE in that system. The use of this function is optional. The F1 Byte is defined only for STS 1 number one in an STS N/Nc signal.

- D1-D3: Section Datacom Channel Three bytes are allocated for a Section Data Communications Channel and are considered as a single 192 kbit/s message-based channel between STEs. The messaging protocols used are defined in ANSI T1.105.04. These bytes are defined only for STS-1 number one in an STS-N/Nc signal.

#### **Line Overhead Definitions - LOH**

The definitions for the Line Overhead Bytes are given below.

- H1, H2: Pointer Two bytes are allocated to a pointer that indicates the offset in bytes between the pointer and the first byte of the STS SPE. It allows alignment of the STS-1 TOHs in an STS-N/Nc signal and performance of frequency justification. In an STS-Nc signal the actual pointer is in the first set of H1 and H2 bytes. H1 and H2 bytes occupying STS-1 positions two through N carry a Concatenation Indicator, where: H1c = 93[H] and H2c = FF[H]. These bytes are required in all STS-1 portions of an STS-N/Nc signal.

- H3: <u>Pointer Action</u> The Pointer Action Byte is allocated for frequency justification purposes. Depending on the pointer value, this byte is used to adjust the fill of input buffers. In the event of a negative justification, it carries valid information. This byte is required in each STS-1 portion of an STS-N/Nc signal.

- B2: <u>Line BIP-8</u> One byte is allocated in each STS-1 for a Line Error Monitoring function. This function is a bit-interleaved parity 8 code using even parity. The Line BIP-8 is calculated over all bits of the Line Overhead and STS SPE of the previous frame before scrambling. The computed BIP-8 is placed in the B2 Byte before scrambling. This byte is defined for all STS-1s of an STS-N/Nc signal. The N B2 Bytes in an STS-N/Nc are intended to form a single error monitoring function capable of measuring error rate up to 10<sup>-3</sup> independent of the value of N. It can be thought of as either: (1) N BIP-8 functions each processing <sup>1</sup>/<sub>N</sub> of the signal or (2) a single BIP-(N×8) processing all of the information. The errors accumulated are to be accumulated into a single error count.

- K1, K2: <u>APS Channel</u> Two bytes are allocated for Automatic Protection Switching (APS) signaling between LTEs. The signaling protocols used are defined in ANSI T1.105.01. These bytes are defined only for STS-1 number one in an STS-N/Nc signal.

- D4-D12: <u>Line Datacom Channel</u> Nine bytes are allocated for a Line Data Communications Channel and are considered as a single 576 kbit/s message-based channel between LTEs. The messaging protocols used are defined in ANSI T1.105.04. These bytes are defined only for STS-1 number one in an STS-N/Nc signal.

- S1: <u>Synchronization Messaging</u> One byte is allocated for transporting synchronization status messages. Currently, only Bits 5 through 8 are defined. Bits 1 through 4 are reserved for future use. This byte is defined only in STS-1 number one in an STS-N/Nc signal.

- M0: <u>STS-1 Line FEBE</u> In a STS-1 signal one byte is allocated for a Line Far End Block Error (FEBE) function. Currently only Bits 5 through 8 are used. These bits are used to convey the count of errors detected by the B2 Byte. This count has nine legal values, i.e., zero through eight. The remaining seven values are interpreted as zero errors. Bits 1 through 4 are reserved for future use.

- M1: <u>STS-N/Nc Line FEBE</u> In a signal at or above the STS-3/3c level, one byte is allocated for a Line Far End Block Error (FEBE) function. The M1 Byte is located in the third STS-1 in an

STS-N/Nc signal. The entire byte is used to convey a count of errors detected by B2 Bytes. This count has  $(8 \times N) + 1$  legal values i.e., zero through  $(8 \times N)$  errors. For rates below STS-48/48c, the remaining possible 255- $(8 \times N)$  values are interpreted as zero errors. At rates at and above STS-48/48c, if greater than 255 errors are detected the Line FEBE shall relay a value of 255 errors.

- Z1: Growth In a signal at or above the STS-3/3c level and less than the STS-192/192c rate, one byte is reserved in STS-1 numbers two through N of the STS-N/Nc signal for future growth. At rates greater than or equal to STS-192/192c, Z1 is only defined for STS-1 numbers two through 48.

- Z2: <u>Growth</u> In a SONET signal at or above the STS-3/3c level and at or less than STS-192/192c, one byte is reserved in all STS-1s except for STS-1 number three of the STS-N/Nc signal for future growth. At rates greater than or equal to STS-192/192c, Z2 is only defined for STS-1 numbers one, two, and four through 48.

- E2: Orderwire One byte is allocated to be used as a Line Orderwire. This is an express orderwire channel reserved for voice communications between LTEs. It is only defined for STS-1 number one.

#### Path Overhead Definitions - POH

Path Overhead is assigned to a payload by a source device (DS3 mapping circuit, DS1 to STS-1 mux, etc.) and remains with the payload until demultiplexed by the sink device. Intermediate LTEs may be required to monitor these bytes. POH functions are divided into four classifications:

- Class A <u>Payload Independent Functions</u> These functions have a standard format and coding and are required for all PTEs.

- Class B <u>Mapping Dependent Functions</u> These functions have a standard format and coding that are specific to the type of payload. They are needed for more than one type of payload but not necessarily all payloads. These functions are processed by the appropriate PTEs.

- Class C <u>Application Specific Functions</u> The format and coding for these functions may not be defined in the SONET Standards. These functions are processed by the appropriate PTEs.

- Class D <u>Undefined Overhead functions</u> These overhead bytes are reserved for future use.

The definitions for the Path Overhead Bytes are given below.

- J1: Path Trace; Class A One byte is used to repetitively transmit a 64-byte fixed length string so that a sink device can verify its continued connection to the intended source device. The content of the message is not constrained by the SONET Standards. However, it is suggested that a message consisting of eight-bit ASCII characters, padded with NULL Characters, and terminated with CR and LF (total length 64 bytes) would be appropriate. If no message is designated then 00[H] is to be transmitted.

- B3: Path BIP-8; Class A One byte is allocated for a Path Error Monitoring function. This function is a bit interleaved parity 8 code using even parity. The Path BIP-8 is calculated over all bits of the previous STS SPE before scrambling. The computed BIP-8 is placed in the B3 Byte before scrambling.

- C2: <u>Path Signal Label; Class A/B</u> One byte is allocated to identify the construction and content of the SPE and for a Path Payload Defect Indicator (PDI-P). The Signal Label portion is a class A function. PDI-P is class B.

- G1: Path Status; Class A One byte is allocated to convey back to the Source PTE the Sink PTE status and performance. Bits 1 through 4 are a Path FEBE. These bits are used to convey the

count of errors detected by the B3 Byte. This count has nine legal values i.e., zero through eight. The remaining seven values are interpreted as zero errors. Bits 5, 6 and 7 are used for a Path Remote Defect Indication (RDI-P). Bit 8 is reserved for future use.

- F2: <u>Path User Channel; Class C</u> One byte is allocated for user communications purposes between PTEs.

- H4: <u>Multiframe Indicator; Class B</u> This byte provides a generalized multiframe indicator for payloads. Currently, it is only used with VT structured payloads.

- Z3, Z4: Growth; Class D Two bytes are reserved for future use.

- Z5: Tandem Connection Maintenance / Path Data Channel; Class C One byte is allocated to support Tandem Connection Maintenance (TCM) and a Path Data Channel. Bits 1 through four are reserved for TCM functions. Bits 5 through 8 form a 32 kbit/s data channel that uses the LAPD protocol. The Path Data channel is used in TCM applications and is also available for communications between PTEs. However, TCM messages have priority. Since TCM terminating entities are not required to perform store and forward or Layer 2 termination for non-TCM messages, some or all of the preempted PTE to PTE messages may be lost and require retransmission.

#### **POINTERS**

Pointers are defined in SONET at the STS-N and VT Levels. The STS-1 Payload Pointer provides a mechanism to allow the flexible and dynamic alignment of the STS-1 SPE within the SONET Transport Frame. Dynamic alignment means that the STS-1 SPE is allowed to float within the Transport frame. Thus the pointer is able to accommodate differences not only in the phases of the STS-1 SPE and the TOH, but in the frame rates as well. As is shown in Figure 11, the STS-1 SPE will usually start in one frame and end in the following frame.

Figure 11. STS-1 Frame

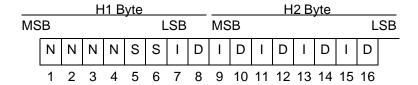

The Pointer Bytes (H1 and H2) can be viewed as one 16-bit word as shown below. The last ten bits (7-16) of the Pointer Word carry the pointer value. This value is a binary number with a range of 0 to 782 that indicates the offset between the Pointer Bytes and the first byte of the SPE (J1). The TOH Bytes are not counted in the offset. For example, a value of "0" indicates that the SPE starts in the byte position immediately following the H3 Byte. The last column of this row is indicated by a pointer value of "86". A value of "87" specifies that the SPE starts at the byte position immediately following the K2 Byte. A value of "522" would position the start of the SPE in the byte position immediately following the C1/J0 Byte. The two S bits are not used in STS-1 Pointers and are set to "00".

#### **Frequency Justification**

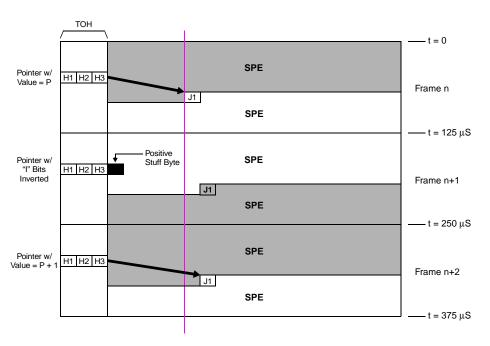

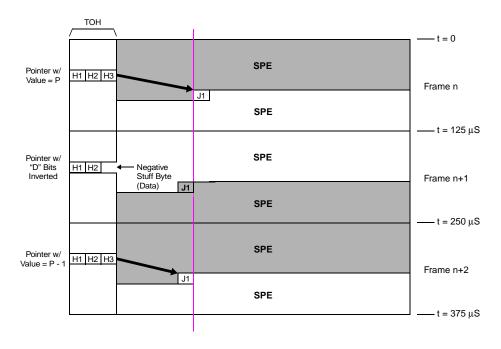

If there is a frequency offset between the frame rate of the TOH and that of the STS-1 SPE, then the pointer value will be incremented or decremented, as needed, accompanied by a corresponding positive or negative stuff byte. Consecutive pointer operations must be separated by at least three frames in which the pointer value remains constant.

If the frame rate of the SPE is too slow with respect to the TOH, then the alignment of the envelope is periodically slipped back in time and the pointer is incremented by one. This is shown in Figure 12. The operation is indicated by inverting Bits 7, 9, 11, 13 and 15 (I Bits) of the Pointer Word. A positive stuff byte appears immediately after the H3 Byte in the frame containing the inverted I Bits. Subsequent pointers contain the new offset.

Figure 12. Positive Pointer Justifications

If the frame rate of the SPE is too fast with respect to the TOH, then the alignment of the envelope is periodically advanced in time and the pointer is decremented by one. This operation is indicated by inverting Bits 8, 10, 12, 14 and 16 (D Bits) of the Pointer Word. A negative stuff byte appears in the H3 Byte Position in the frame containing the inverted D Bits. Subsequent pointers contain the new offset. This is shown in Figure 13.

Figure 13. Negative Pointer Justifications

PHAST-1 TXC-06101

#### **New Data Flag**

Bits 1 through 4 (N Bits) of the Pointer Word carry a New Data Flag (NDF). This is a mechanism that allows an arbitrary change of the value of the pointer if that change is due to a change in payload. Normal operation is indicated by a "0110" code in the N Bits. NDF is indicated by inversion of the N Bits to "1001". The new alignment is indicated by the pointer value accompanying the NDF and takes effect at the offset indicated.

#### Concatenation

A concatenation indication contained in the Pointer Word is used to show that the STS-1 is part of an STS-Nc. The operations indicated in the pointer word of the first STS-1 within the STS-Nc apply to all STS-1s within the group. The pointer value must be multiplied by N to obtain the byte offset into the STS-Nc envelope capacity. Positive and negative justifications are performed as N byte multiples. In the remaining pointer words in the group the I and D Bits are set to all "1"s. The N Bits are set to "1001" and the S Bits are set to "00". The PHAST-1 does not support concatenation but does provide a status bit indicating that a concatenation indication has been received in the H1 and H2 Bytes.

#### **BLOCK DIAGRAM**

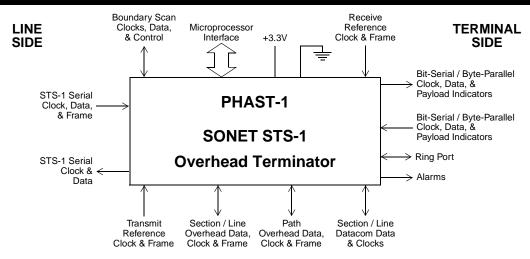

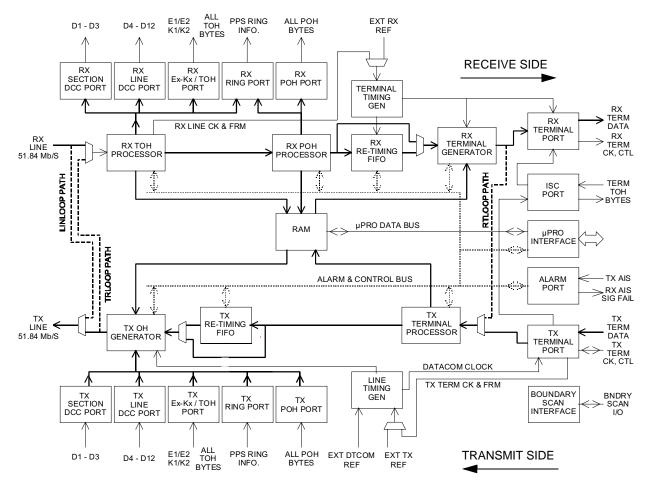

The Block Diagram for the PHAST-1 is shown in Figure 14.

Figure 14. PHAST-1 TXC-06101 Block Diagram

#### **RECEIVE SIDE**

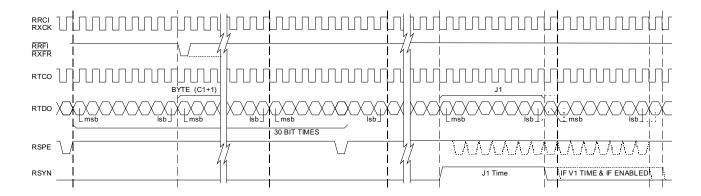

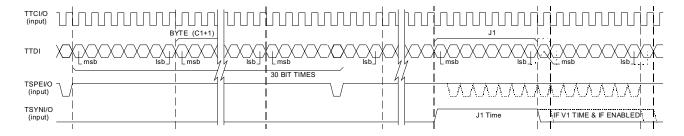

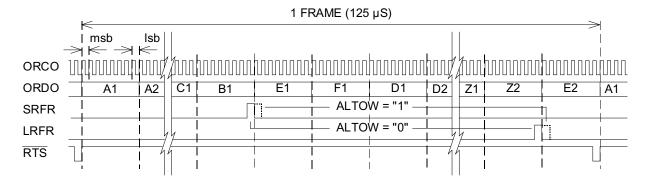

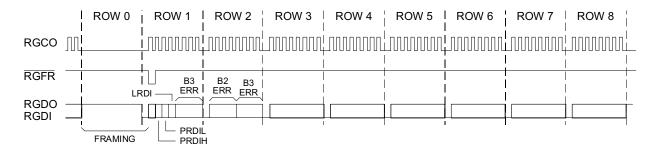

The Multiplexer at the Receive Line Input selects either the Line Side Input or the looped signal from the Transmit Line Output. The selected signal is applied to the Rx TOH Processor. The Rx TOH Processor Block is responsible for Framing, De-scrambling, Overhead Distribution and Overhead Processing. All Section and Line Overhead Bytes are stored in RAM and may be read through the  $\mu Pro^1$  Interface. The Section and Line DCC Bytes are output at the Rx Section and Line DCC Ports as serial Bit streams suitable for interfacing to HDLC Controllers. The  $E_X$ -K $_X$ /TOH Port has two modes of operation. In the First Mode it outputs the E1, E2, K1 and K2 Bytes in a manner that allows the E1 and E2 Bytes to be directly interfaced to CODECS. The other mode of operation allows external access to all of the Received TOH Bytes. Overhead Processing consists of J0 Processing, Error Accumulation (B1, B2, FEBE-L), Debouncing of selected TOH Bytes, Pointer Tracking and Alarm Detection. Section and Line Level Alarms are reported to the  $\mu Pro$  Interface. AIS-L and Signal Fail conditions are output at the Alarm Port.

<sup>1.</sup> Throughout this document "µPro" is used as a space-saving alias for "microprocessor".

### DATA SHEET

PHAST-1 TXC-06101

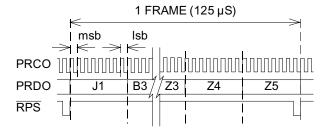

The Rx POH Processor Distributes and Processes the POH Bytes. All bytes are stored in RAM and available at the Rx POH Port. Selected POH Bytes are debounced. B3 and FEBE-P error counts are accumulated. Path Level Alarms are reported to the  $\mu$ Pro Interface. AIS-P conditions are output at the Alarm Port.

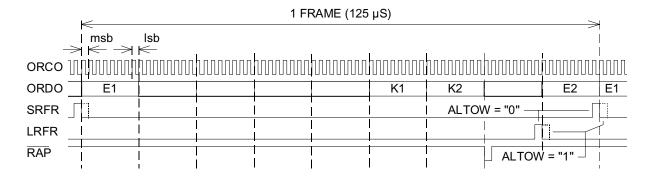

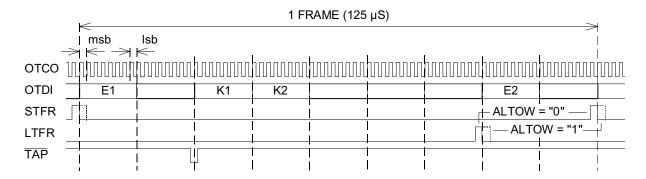

The Rx Ring Port is for use with a mated PHAST-1 in PPS Ring Operations. The information output consists of FEBE (Line and Path) values and Send RDI (Line and Path) indications.

The Terminal Timing Generator and Rx Re-timing FIFO are used to justify the STS-1 SPE to a Rx Reference Frequency. In certain modes of operation the Re-timing Function can be bypassed. The Reference Frequency may be derived from the Rx Line or from an External Reference Source. The Rx Re-timing FIFO Block performs Frequency Justification and Pointer Re-calculation.

The Rx Terminal Generator and Rx Terminal Port create and format the received Signal appearing at the Rx Terminal Port outputs. The Section and Line Overhead Bytes (not applicable in SPE-only Mode) appearing at the output may be taken from RAM, generated internally, or input at the ISC Port. The POH bytes are taken from RAM or internally generated. The Rx Terminal Generator generates the required bytes and performs Alarm Insertion.

#### TRANSMIT SIDE

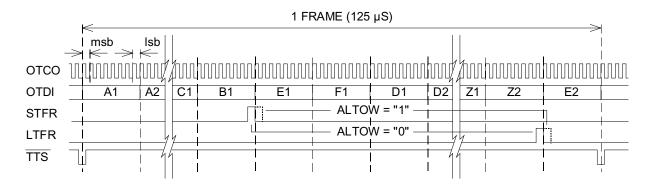

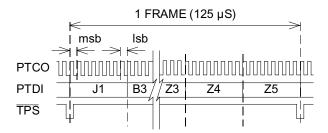

The data to be transmitted enters the PHAST-1 at the Tx Terminal Port. The Tx Terminal Clock and Control Signals are generated and output by the PHAST-1 in Datacom Mode and are inputs for all other modes. The TOH bytes (not applicable in SPE-only Mode) are extracted and output at the ISC Port.

The Multiplexer at the input to the Tx Terminal Processor selects either the Tx Terminal Port Data or the looped signal from the Rx Terminal Generator. The Tx Terminal Processor performs Frame Delineation, Pointer Tracking, stores all TOH (if present) and POH Bytes in RAM, accumulates B1, B2 and B3 errors, and detects Terminal Side Alarms. The payload portion of the STS-1 SPE is forwarded to the Tx Re-Timing FIFO.

The Line Timing Generator and Tx Re-timing FIFO are used to justify the STS-1 SPE to a Tx Reference Frequency. In certain modes of operation the Re-timing Function can be bypassed. The Reference Frequency may be derived from the Tx Terminal or from an External Reference Source. The Tx Re-timing FIFO performs Frequency Justification and Pointer Recalculation.

The Tx OH Generator is responsible for Section, Line and Path Overhead Byte Assembly, TOH and POH Level Alarm Insertion, and scrambling. The POH bytes may be selected from RAM or input at the Tx POH Port. Alarms are generated as a result of Rx Side anomalies, Terminal Side conditions, Alarm Port Input, Tx Ring Port Input or upon command from the  $\mu$ Pro Interface. The TOH Bytes are either internally generated, taken from RAM, or input externally. The external sources for the TOH Bytes are the Tx E<sub>X</sub>-K<sub>x</sub>/TOH Port, the Tx Line DCC Port, or the Tx Section DCC Port. Alarms are generated as a result of Rx Side anomalies, Terminal Side conditions, Alarm Port Input, Tx Ring Port Input or upon command from the  $\mu$ Pro Interface. The Tx Line Output consists of either the Tx OH Generator Output or the looped Received Line Signal.

#### **PIN DIAGRAMS**

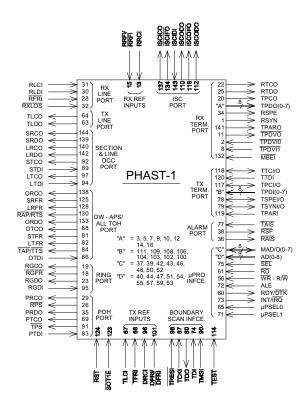

Figure 15. PHAST-1 TXC-06101 Functional Pin Diagram

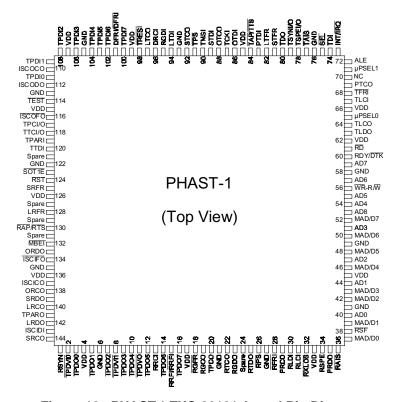

Figure 16. PHAST-1 TXC-06101 Actual Pin Diagram

## **PIN DESCRIPTIONS**

### Power Supply, Ground and Spare Pins

| Pin Name | Pin No.*                                                | I/O/P(T) | Туре | Name/Function                                                                                                                                               |

|----------|---------------------------------------------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD      | 4, 17, 33, 45, 62,<br>66, 85, 99, 107,<br>115, 126, 136 | Р        |      | +3.3 V ± 5% Supply Voltage, V <sub>DD</sub>                                                                                                                 |

| GND      | 6, 21, 27, 41, 49,<br>58, 76, 93, 105,<br>113, 122, 135 | Р        |      | V <sub>SS</sub> or Ground - 0 V reference                                                                                                                   |

| SPARE    | 24, 121, 127,<br>129, 131                               | _        |      | <b>Spare Pins</b> : Do not connect to Power, Ground, any circuit conductor or any other pin. Connection of this pin may impair performance or cause damage. |

<sup>\*</sup>Note: I =Input; O = Output; P = Power; (T) = Tri-state

### **Reference Inputs**

| Pin Name  | Pin No. | I/O/P(T) | Type** | Name/Function                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

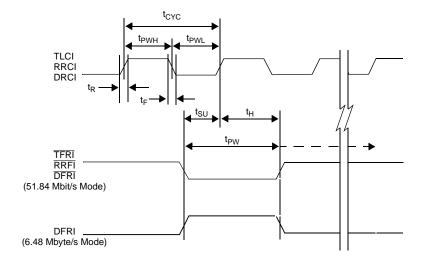

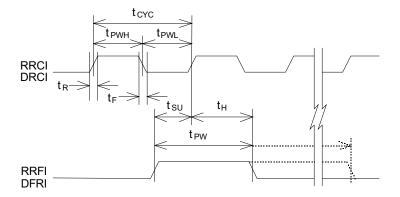

| RRCI      | 13      | I        | CMOSp  | Receive Reference Clock Input: 51.84/19.44/6.48 MHz clock optionally used for Receive Side re-timing. This input is enabled if control bit RCLK = "1" in CR10 (see Memory Map section).                                                                                                                                                               |

| RRFI/RRFI | 15      | I        | CMOSp  | Receive Reference Frame Input: Optional pulse in 51.84 Mbyte/s and 6.48 Mbyte/s modes, but required in 19.44 Mbyte/s mode; used to define the Receive Terminal start of frame. When RRCI is 51.84 MHz, it is active Low. Otherwise it is active High. If the pulse is not provided, the start of the frame at the Rx terminal port will be arbitrary. |

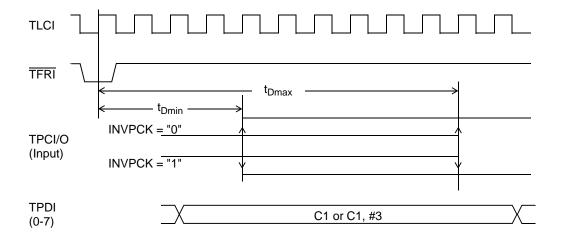

| TLCI      | 67      | I        | CMOS   | <b>Transmit Line Clock Input:</b> 51.84 MHz clock. Depending on the operating mode it may be used for Transmit Side re-timing.                                                                                                                                                                                                                        |

| TFRI      | 68      | I        | CMOSp  | Transmit Frame Reference Input: Optional active Low frame pulse. Depending on the operating modes it may be used to define the Transmit Line start of frame.                                                                                                                                                                                          |

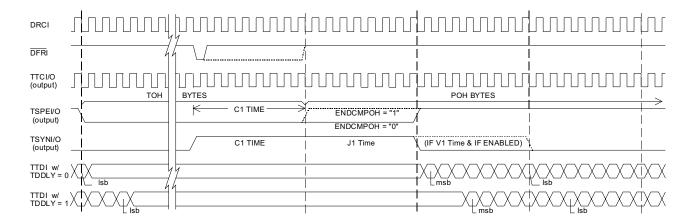

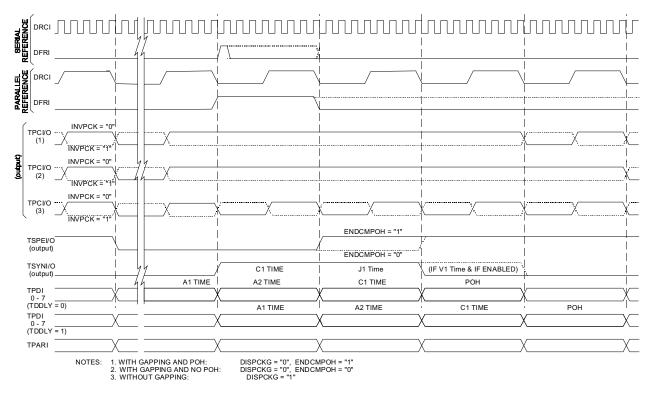

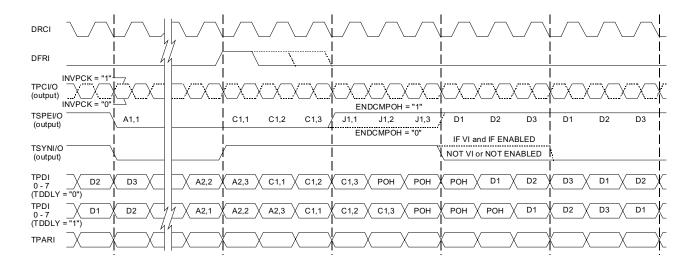

| DRCI      | 96      | I        | CMOSp  | Datacom Reference Clock Input: 51.84/19.44/6.48 MHz clock used in Datacom Mode to generate TTCI/O or TPCI/O. This is a required input for Datacom Mode.                                                                                                                                                                                               |

<sup>\*\*</sup>Note: See the Input, Output and I/O Parameters section for Type descriptions.

| Pin Name  | Pin No. | I/O/P(T) | Type** | Name/Function                                                                                                                                                                                                                                                                                                 |

|-----------|---------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFRI/DFRI | 101     | I        | CMOSp  | Datacom Reference Frame Input: Optional 8 kbit/s pulse used in Datacom Mode to define the Transmit Terminal start of frame. When in serial Datacom mode this pin is active Low, otherwise it is active High. When H4INT = "1", then either the pulse repetition rate must be 2 kbit/s or the pin is not used. |

#### **Receive Line Side Interface**

| Pin Name | Pin No. | I/O/P(T) | Туре  | Name/Function                                                                                                                                                                                                                                                        |

|----------|---------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

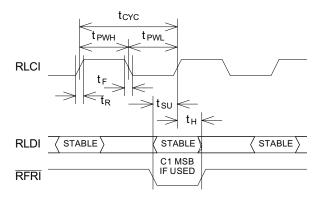

| RFRI     | 28      | I        | CMOSp | Receive Line Frame In: Optional, active Low frame pulse that occurs during the C1 Byte, Bit 7 time. When used, it reduces the SEF/OOF exit time from two frames to one frame. This input is only enabled if STS1 = "0". It is clocked in on the Rising Edge of RLCI. |

| RLDI     | 30      | I        | CMOS  | Receive Line Data Input: Incoming, serial STS-1 data which is clocked in on the Rising Edge of RLCI.                                                                                                                                                                 |

| RLCI     | 31      | I        | CMOS  | Receive Line Clock Input: Incoming 51.84 MHz Clock.                                                                                                                                                                                                                  |

| RXLOS    | 32      | I        | TTLp  | Receive Loss Of Signal: Active Low, external, LOS indicator. This input is combined with the internal LOS detectors to produce the RLOS status indicator. The minimum Low time is 20 ns.                                                                             |

#### **Transmit Line Side Interface**

| Pin Name | Pin No. | I/O/P(T) | Туре | Name/Function                                                                                                                                                                 |

|----------|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

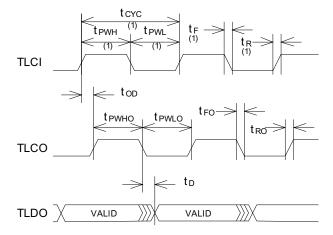

| TLDO     | 63      | 0        | CT8  | Transmit Line Data Output: Outgoing, serial STS-1 Data which is clocked out on the Falling Edge of TLCO.                                                                      |

| TLCO     | 64      | 0        | CT8  | Transmit Line Clock Output: Outgoing 51.84 MHz Clock. When TCLK = "0", it is derived from TTCI/O, DRCI, or TLCI, depending on mode. When TCLK = "1", it is derived from TLCI. |

### **Terminal Side Interface**

| Pin Name | Pin No. | I/O/P(T) | Туре | Name/Function                                                                                                                                    |

|----------|---------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

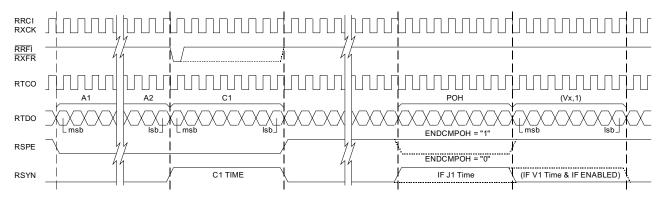

| RTCO     | 22      | 0        | CT8  | Receive Terminal Clock Output: Serial, 51.84 MHz terminal clock. Depending on the operating modes, RTCO may be derived from either RLCI or RRCI. |

| RTDO     | 25      | 0        | СТ8  | Receive Terminal Data Output: Serial, 51.84 MHz data. Data is clocked out on the Falling Edges of RTCO.                                          |

| TRA | NSW | ITCH° |

|-----|-----|-------|

|     |     |       |

| Pin Name  | Pin No.                                  | I/O/P(T) | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|------------------------------------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

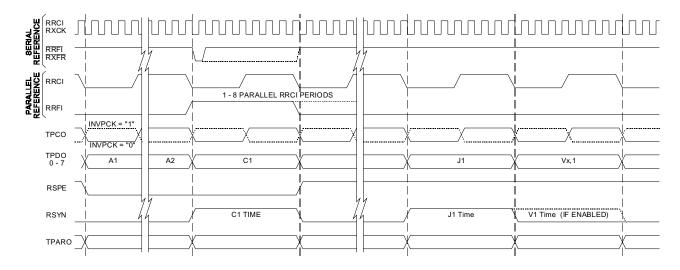

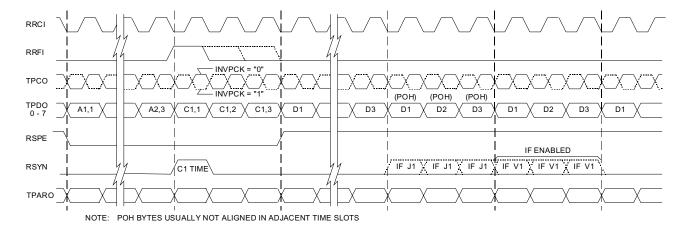

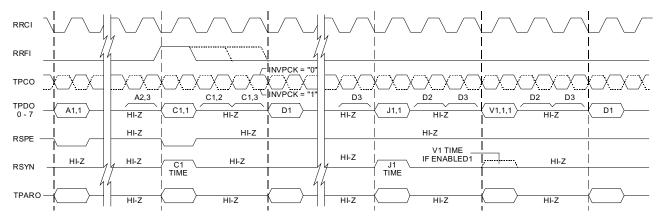

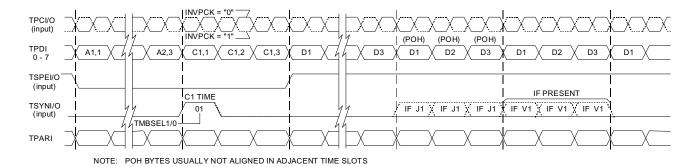

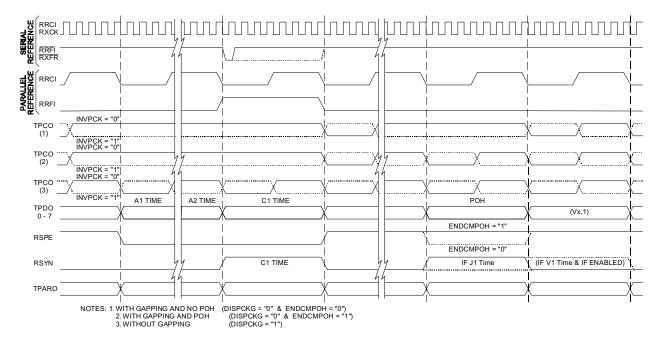

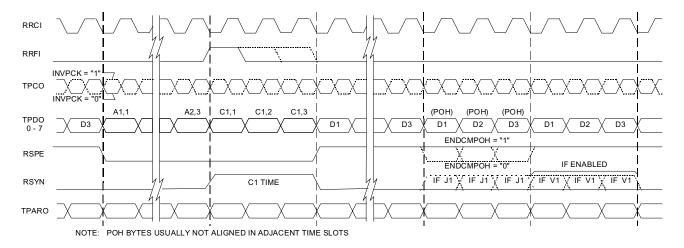

| TPCO      | 20                                       | 0        | CT4  | Terminal Parallel Clock Output: Parallel, 6.48 MHz or 19.44 MHz, Rx Terminal clock. Depending on the operating modes, TPCO at 6.48 MHz may be derived from either RLCI or RRCI. TPCO at 19.44 MHz must be derived from RRCI. When INVPCK = "1", TPCO is inverted. In SONET Modes and 19.44 Mbyte/s Datacom Mode, it is continuous. In 6.48 Mbyte/s Datacom Mode TPCO is:  1. continuous if DISPCKG = "1"  2. gapped during the TOH Byte times when DISPCKG = "0" and ENDCMPOH = "1"  3. gapped during TOH and POH Byte times if DISPCKG = "0" and ENDCMPOH = "0".                    |

| TPDO(0-7) | 3<br>5<br>7<br>9<br>10<br>12<br>14<br>16 | O(T)     | CT4  | <b>Terminal Parallel Data Output:</b> Parallel, 6.48 Mbyte/s or 19.44 Mbyte/s, Rx Terminal data. TPDO0 is the least significant bit of the SONET Byte. When INVPCK = "0", information is clocked out on the Falling Edges of TPCO. When INVPCK = "1" information is clocked out on the Rising Edges.                                                                                                                                                                                                                                                                                 |

| RSPE      | 34                                       | O(T)     | CT8  | Receive Terminal SPE Indication: In SPE-only Mode this is the active Low gapping signal. In Both SONET and Datacom Modes it is Low during the TOH Byte times. In SONET Mode it is High during the SPE Byte times. In Datacom Modes this is:  1. High during the SPE Byte times if ENDCMPOH = "1"  2. Low during the POH Byte times and High during the Payload Byte times if ENDCMPOH = "0"  RSPE is clocked out on the Falling Edges of RTCO. When INVPCK = "0", it is clocked out on the Falling Edges of TPCO. When INVPCK = "1" RSPE is clocked out on the Rising Edges of TPCO. |

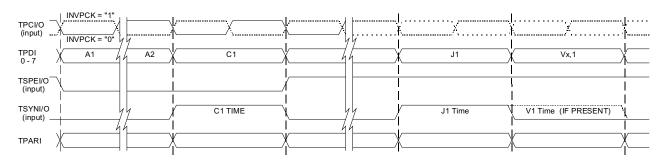

| RSYN      | 1                                        | O(T)     | CT8  | Receive Terminal Sync Pulse: In SONET and Datacom Modes this is High during the C1, J1, and, optionally, V1 Byte times. In SPE-only Mode this is High during the J1 Byte time and, optionally, during the V1 Byte time. RSYN is clocked out on the Falling Edges of RTCO. When INVPCK = "0", RSYN is clocked out on the Falling Edges of TPCO. When INVPCK = "1" it is clocked out on the Rising Edges of TPCO.                                                                                                                                                                      |

| TPARO     | 141                                      | O(T)     | CT4  | <b>Terminal Parity Output:</b> Odd parity over TPDO(0-7), RSPE and RSYN when C1J1EN = "1" or in Datacom mode. When C1J1EN = "0", it is generated over TPDO(0-7).                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **DATA SHEET**

| Pin Name | Pin No. | I/O/P(T) | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPDVO    | 11      | O        | CT4          | Terminal Parallel Data Valid Output: Active Low Signal that indicates that TPDO(0-7), RSPE, RSYN and TPARO are driving the parallel bus. In 6.48 Mbyte/s applications it will always be Low. When the bus is operating at 19.44 Mbyte/s the settings of ENFSTUA, ENLSTUA, MBSEL0 and MBSEL1 will determine when this pin is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TPDVI0   | 2       | I        | TTLp         | Terminal Parallel Data Valid Input x: Active Low sig-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TPDVI1   | 8       |          | TTLp         | nals that are used for bus collision protection when the 19.44 Mbyte/s operating mode is selected. They are connected to the TPDVO outputs of other devices.  A priority scheme can be implemented by:  1. Providing no inputs to the highest priority device 2. Providing one input to the middle priority device 3. Providing two inputs to the lowest priority device.  Another collision protection scheme can be implemented by connecting the TPDVO output of each device to either the TPDVIO or TPDVI1 inputs of the other device(s).  The advantage of implementing either type of collision protection scheme is to avoid signal contention when two or three devices are incorrectly programmed for the same time slot. (Also see RBUSCOL, Status Register 1, bit 1).  While TPDVIO and TPDVI1 are high the TPDO(0-7), RSPE, RSYN, and TPARO parallel bus is driven when operating in the 6.48 Mbyte/s mode, or in the 19.44 Mbyte/s mode if programmed by MBSEL0, MBSEL1, ENFSTUA, and ENLSTUA. The parallel bus is tri-stated when either or both TPDVIO or TDPVI1 are low in either the 6.48 Mbyte/s or 19.44 Mbyte/s mode. |

| MBEI     | 132     | I        | TTLp         | Multiplex Bus Enable Input: Active Low signal that enables 19.44 Mbtye/s bus operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TTCI/O   | 118     | I/O      | CMOS/<br>CT8 | Transmit Terminal Clock Input/Output: Serial, 51.84 MHz terminal clock. In SONET and SPE-only Modes it is an Input. In Datacom Mode it is an Output derived from DRCI. Since it is possible for the device to power up with this pin as an output, a reset should be performed via pin RST to ensure correct operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TTDI     | 120     | I        | CMOS         | <b>Transmit Terminal Data Input:</b> Serial, 51.84 Mbit/s data. Data is clocked in on the Rising Edges of TTCI/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## •

| Pin Name  | Pin No.                                              | I/O/P(T) | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------------------------------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPCI/O    | 117                                                  | I/O      | TTL/<br>CT4  | Terminal Parallel Clock Input/Output: Parallel, 6.48 or 19.44 MHz, Tx Terminal clock. In SONET Modes it is an Input. In Datacom Modes it is an Output derived from DRCI and will be inverted if INVPCK = "1". In 19.44 Mbyte/s Datacom Mode it is continuous. In 6.48 Mbyte/s Datacom Mode it is:  1. continuous if DISPCKG = "1"  2. gapped during the TOH Byte times when DISPCKG = "0" and ENDCMPOH = "1"  3. gapped during the TOH and POH Byte times if DISPCKG = "0" and ENDCMPOH = "0".  Since it is possible for the device to power up with this pin as an output, a reset should be performed via pin RST to ensure correct operation.                                                                                                                                                                                                                                                                                                                                                                       |

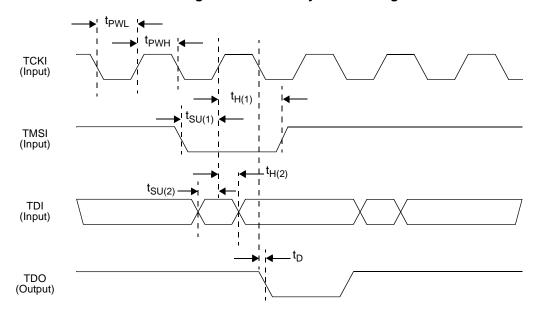

| TPDI(0-7) | 111<br>109<br>108<br>106<br>104<br>103<br>102<br>100 | I        | TTL          | Terminal Parallel Data Input: Parallel 6.48 Mbyte/s or 19.44 Mbyte/s data. In SONET Modes, data is clocked in on the Rising Edges of TPCI/O when INVPCK = "0", and on the Falling Edges when INVPCK = "1". In Datacom Modes data is sampled on:  1. the Falling Edge of TPCI/O when INVPCK = "0"  2. the Rising Edge of TPCI/O when INVPCK = "1"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |