# intel®

Intel<sup>®</sup> IXF6048

#### Datasheet

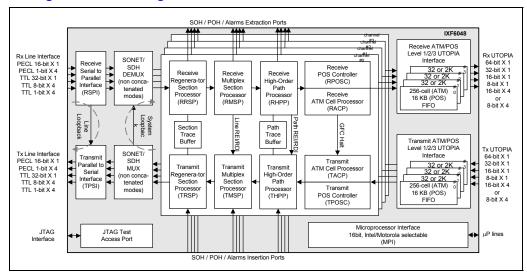

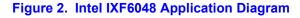

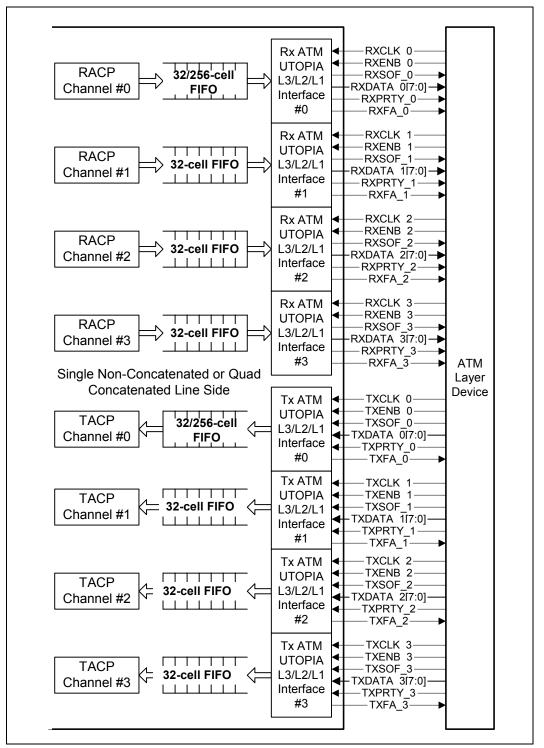

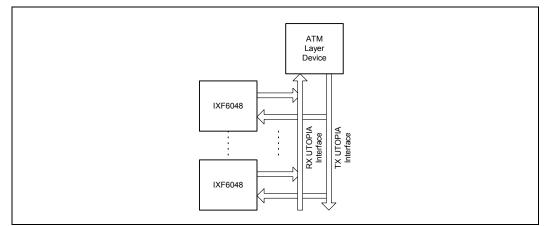

Intel IXF6048 is a single-chip interface solution for the transport of ATM cells or HDLC frames over SONET/SDH. Intel IXF6048 can operate as a quad 51/155/622 Mbit/s or as a single 2488 Mbit/s SONET/SDH processor. When configured in ATM UNI mode, it interfaces with an ATM layer device using the industry standard UTOPIA interface (Levels 3/2/1). When configured in Packet Over SONET mode, it transfers the PPP frames using a UTOPIA-enhanced interface, based on the ATM industry standard UTOPIA, which supports the transfer of variable length frames.

### **Product Features**

#### **Applications**

- WAN and edge ATM switches

- Layer 3 switches

- Video and File Servers

- Broadband Switching Systems

#### Features

- Maps ATM cells or HDLC frames into one STS-48c/STM-16c/STS-48/STM-16/STM-4 or four STS-12c/STM-4c/STS-3c/STM-1/STS-1 SONET/SDH signals.

- In POS mode, each channel performs SPE scrambling (1 + X<sup>43</sup>), HDLC processing, and offers a UTOPIA-type FIFO-based POS interface.

- Supports the UTOPIA Level 3 (single 64bit, 32-bit, or quad 8-bit), Level 2 (single 8/ 16-bit), and Level 1 (quad 8/16-bit) interface modes.

- Implements a GFC halt function (ITU I.150 and I.361).

- Handles full J0/J1 trace identifier processing.

- SOH, POH and Alarm insertion/extraction ports.

- Hardware assistance for APS implementation, via K1 and K2 bytes.

- Provides a 16-bit microprocessor port. One-second counters for B1/B2/B3, M1/G1 REI, etc.

- 600 TBGA package; -40 °C to +85 °C operating conditions; low power, 3.3 V operation, 5 V tolerant I/O

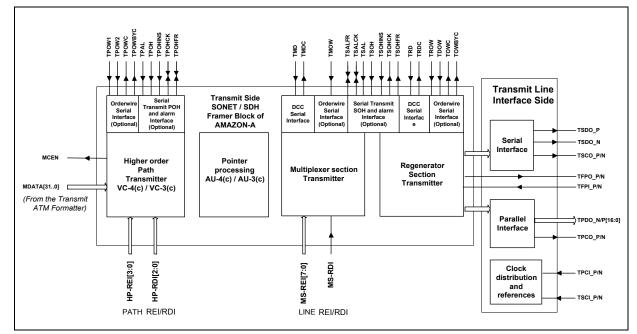

#### Figure 1. Block Diagram

Order Number: 273644-004 September 2003

### intel®

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> IXF6048 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Pentide, TokenExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2003

# int<sub>el®</sub> Contents

| 1.0 | Pin D  | escripti  | ion                                                                                                                      | 11         |

|-----|--------|-----------|--------------------------------------------------------------------------------------------------------------------------|------------|

| 2.0 | Main   | Feature   | 9S                                                                                                                       |            |

|     | 2.1    | Genera    | al                                                                                                                       | 93         |

|     | 2.1    | 2.1.1     | SONET/SDH Receiver Block                                                                                                 |            |

|     |        | 2.1.1     | SONET/SDH Transmitter Block                                                                                              |            |

|     |        | 2.1.2     | Receive ATM Cell Processor Block                                                                                         |            |

|     |        | 2.1.3     | Transmit ATM Cell Processor Block                                                                                        |            |

|     |        | 2.1.4     | Receive Byte-Synchronous HDLC Controller (Receive POS Block)                                                             |            |

|     |        | 2.1.5     | Transmit Byte-Synchronous HDLC Controller (Transmit POS Block)                                                           |            |

|     |        | 2.1.0     | ATM-UTOPIA Interface                                                                                                     |            |

|     |        | 2.1.7     | POS-UTOPIA Interface                                                                                                     |            |

|     |        |           |                                                                                                                          |            |

| 3.0 | Line S | Side Inte | erface                                                                                                                   |            |

|     | 3.1    | Differer  | ntial PECL Single Parallel Line Side Interface                                                                           | 101        |

|     | 3.2    | Differer  | ntial PECL Quad Serial Line Side Interface (155/51 Mbit/s)                                                               |            |

|     | 3.3    | TTL Sir   | ngle Parallel Line Side Interface                                                                                        |            |

|     | 3.4    | TTL Qu    | uad Parallel Line Side Interface                                                                                         |            |

|     | 3.5    | TTL Qu    | uad Serial Line Side Interface                                                                                           |            |

|     | 00115  | TODU      | Frances Black Franciscus I Baserintian                                                                                   | 404        |

| 4.0 |        |           | Framer Block Functional Description                                                                                      |            |

|     | 4.1    |           | of Operation                                                                                                             |            |

|     |        | 4.1.1     | Frame Format Configuration                                                                                               |            |

|     |        |           | 4.1.1.1 Concatenated Frames                                                                                              |            |

|     |        |           | 4.1.1.2 Non-Concatenated Frames                                                                                          |            |

|     |        | 4.1.2     | Operational Configuration                                                                                                |            |

|     |        |           | 4.1.2.1 Repeater Mode Configuration                                                                                      |            |

|     | 4.0    | <b>-</b>  | 4.1.2.2 Multiplexer Mode Configuration                                                                                   |            |

|     | 4.2    |           | nit Data Flow                                                                                                            |            |

|     | 4.3    |           | e Data Flow                                                                                                              |            |

|     |        | 4.3.1     | Reference Clocks                                                                                                         |            |

|     | 4.4    |           | ed Functional Description Per Channel                                                                                    |            |

|     |        | 4.4.1     | Receiver Default Operation Per Channel                                                                                   |            |

|     |        |           | 4.4.1.1 Line Interface Processing                                                                                        |            |

|     |        |           | 4.4.1.2 Framer                                                                                                           |            |

|     |        |           | 4.4.1.3 Regenerator Section Receiver                                                                                     |            |

|     |        |           | 4.4.1.4 Multiplexer Section Receiver                                                                                     |            |

|     |        |           | <ul><li>4.4.1.5 Pointer Recovery</li><li>4.4.1.6 Higher Order Path Receiver</li></ul>                                    |            |

|     |        | 110       | 4.4.1.6 Higher Order Path Receiver<br>Transmitter Default Operation Per Channel                                          | 124        |

|     |        | 4.4.2     | •                                                                                                                        |            |

|     |        |           | <ul><li>4.4.2.1 Higher Order Path Transmitter</li><li>4.4.2.2 Transmit Multiplexer Section Adaptation Function</li></ul> | /∠۱        |

|     |        |           | 4.4.2.3 Multiplexer Section Transmitter                                                                                  | 131<br>122 |

|     |        |           | 4.4.2.3 Multiplexel Section Transmitter                                                                                  |            |

|     |        |           | 4.4.2.5 Clock Distribution and Reference                                                                                 |            |

|     | 4.5    | Overhe    | ead Bytes and Alarms Serial Access                                                                                       |            |

|     | 4.0    | 4.5.1     | Section OverHead Access                                                                                                  |            |

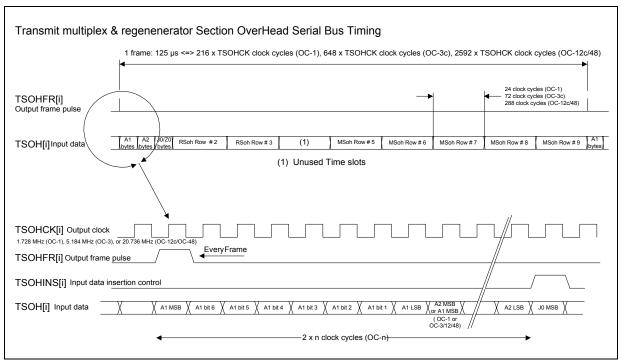

|     |        | 7.0.1     | 4.5.1.1 Transmit Side: TSOH Serial Bus                                                                                   |            |

|     |        |           |                                                                                                                          |            |

### intel®

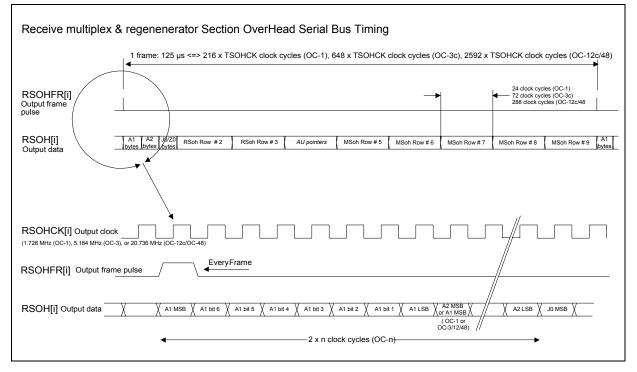

|     |       |                 | 4.5.1.2 F   | Receive Side: RSOH Serial Bus                                               | 139 |

|-----|-------|-----------------|-------------|-----------------------------------------------------------------------------|-----|

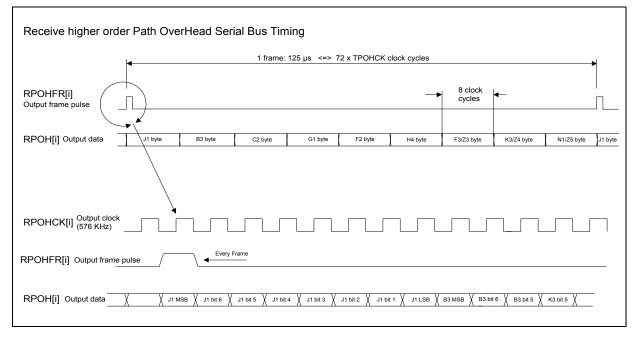

|     |       | 4.5.2           | Higher Ord  | ler Path OverHead Access                                                    | 140 |

|     |       |                 | 4.5.2.1 T   | Fransmit Side: TPOH Serial Bus                                              | 140 |

|     |       |                 | 4.5.2.2 F   | Receive Side: RPOH Serial Bus                                               | 141 |

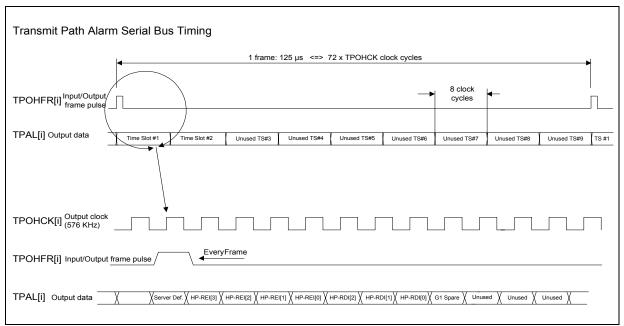

|     |       | 4.5.3           |             | ne) Alarms, APS and Ring Bus                                                |     |

|     |       |                 |             | Receive Side: RSAL Serial Bus                                               |     |

|     |       |                 |             | Fransmit Side: TSAL Serial Bus                                              |     |

|     |       | 4.5.4           |             | ns and Ring Bus                                                             |     |

|     |       |                 |             | Receive Side: RPAL Serial Bus                                               |     |

|     |       |                 |             | Transmit Side: TPAL Serial Bus                                              |     |

|     |       | 4.5.5           |             | Serial Accesses to DCC and Orderwires                                       |     |

|     |       |                 |             | D1 to D3 Data Communication Channel<br>D4 to D12 Data Communication Channel |     |

|     |       |                 |             | E1, E2, and F1 Section Orderwire Channel                                    |     |

|     |       |                 | 4.5.5.4 F   | F2 and F3 Path Orderwire Channel                                            | 156 |

|     |       |                 |             |                                                                             |     |

| 5.0 | ATM ( |                 |             | nctional Description                                                        |     |

|     | 5.1   |                 |             | Processing                                                                  |     |

|     |       | 5.1.1           |             | d Cell Delineation                                                          |     |

|     |       |                 |             | HEC Verification and HEC-Based Cell Filtering                               |     |

|     |       |                 |             | dle/Unassigned Cell Filtering                                               |     |

|     |       |                 |             | Cell Payload Descrambling                                                   |     |

|     |       |                 |             | GFC Processing<br>Performance Monitoring Counters                           |     |

|     |       |                 |             | Receive FIFO Control                                                        |     |

|     | 5.2   | Transm          |             | Processing                                                                  |     |

|     | 0.2   | 5.2.1           |             | IFO Control                                                                 |     |

|     |       | 5.2.2           |             | igned Cell Insertion                                                        |     |

|     |       | 5.2.3           |             | eration/Insertion                                                           |     |

|     |       | 5.2.4           |             | ad Scrambling                                                               |     |

|     |       | 5.2.5           |             | essing                                                                      |     |

|     |       | 5.2.6           |             | ce Monitoring Counters                                                      |     |

| ~ ~ |       |                 |             | -                                                                           |     |

| 6.0 |       |                 |             | Functional Description                                                      |     |

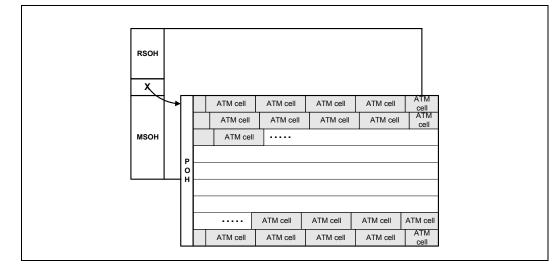

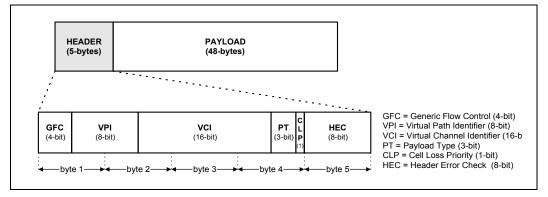

|     | 6.1   |                 |             | d ATM Cell Data Structure                                                   |     |

|     | 6.2   |                 |             | M Configuration                                                             |     |

|     | 6.3   |                 |             | PIA Interface                                                               |     |

|     |       | 6.3.1           |             | esponse Configuration                                                       |     |

|     |       | 6.3.2           |             | vice/Multiple-Device Configuration                                          |     |

|     | 6.4   | 6.3.3<br>Transm |             | TM-UTOPIA Interface Functional Timing Examples                              |     |

|     | 6.4   | 6.4.1           |             | esponse Configuration                                                       |     |

|     |       | 6.4.1           |             | vice/Multiple-Device Configuration                                          |     |

|     |       | 6.4.2<br>6.4.3  |             | TM-UTOPIA Interface Functional Timing Examples                              |     |

|     | 6.5   |                 |             | el 3/Level 2 Compatibility                                                  |     |

|     |       |                 |             |                                                                             |     |

| 7.0 | POSI  |                 |             | unctional Description                                                       |     |

|     | 7.1   |                 |             | me Processing                                                               |     |

|     |       | 7.1.1           |             | rambling                                                                    |     |

|     |       | 7.1.2           |             | me Delineation                                                              |     |

|     |       | 7.1.3           | Frame Intra | afilling Removal                                                            | 186 |

4

# intel®

|      |            | 7.1.4          | Control Escape Stuffing Removal (Byte Destuffing)                                                       |     |

|------|------------|----------------|---------------------------------------------------------------------------------------------------------|-----|

|      |            | 7.1.5          | User Data Descrambling                                                                                  |     |

|      |            | 7.1.6          | FCS Verification                                                                                        |     |

|      |            | 7.1.7          | Address and Control Fields                                                                              |     |

|      |            | 7.1.8          | Receive FIFO                                                                                            |     |

|      |            | 7.1.9          | Packet Length Checking                                                                                  |     |

|      | 7.0        |                | Performance Monitoring Counters                                                                         |     |

|      | 7.2        |                | it HDLC Frame Processing                                                                                |     |

|      |            | 7.2.1<br>7.2.2 | Transmit FIFO<br>Address and Control Fields                                                             |     |

|      |            | 7.2.2          | FCS Generation/Insertion                                                                                |     |

|      |            | 7.2.3          | User Data Scrambling                                                                                    |     |

|      |            | 7.2.5          | Control Escape Stuffing Insertion (Byte Stuffing)                                                       |     |

|      |            | 7.2.6          | Transmit Flow Control                                                                                   |     |

|      |            | 7.2.7          | SPE Scrambling                                                                                          |     |

|      |            | 7.2.8          | Performance Monitoring Counters                                                                         |     |

| ~ ~  | <b>DOO</b> |                |                                                                                                         |     |

| 8.0  | POS-       |                | Interface Functional Description                                                                        |     |

|      | 8.1        |                | us Width and Packet Data Structure                                                                      |     |

|      | 8.2        |                | e POS-UTOPIA Interface                                                                                  |     |

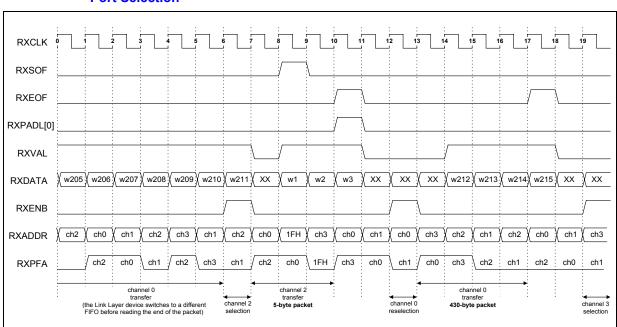

|      |            | 8.2.1          | Port Selection Mode                                                                                     |     |

|      |            | 8.2.2          | Decode-Response Configuration                                                                           |     |

|      |            | 8.2.3          | Single-Device/Multiple-Device Configuration                                                             |     |

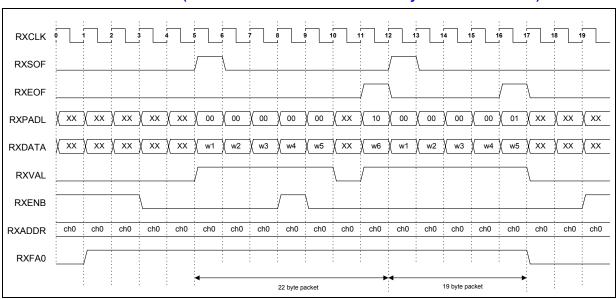

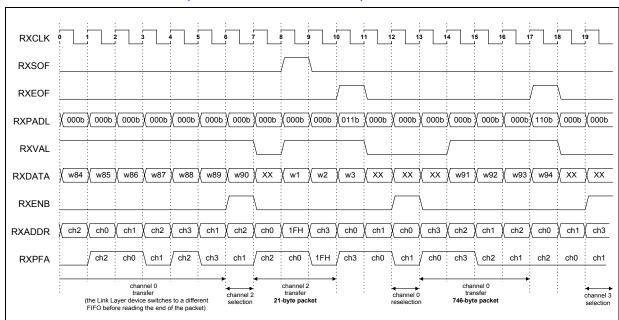

|      |            | 8.2.4          | Receive POS-UTOPIA Interface Functional Timing Examples                                                 |     |

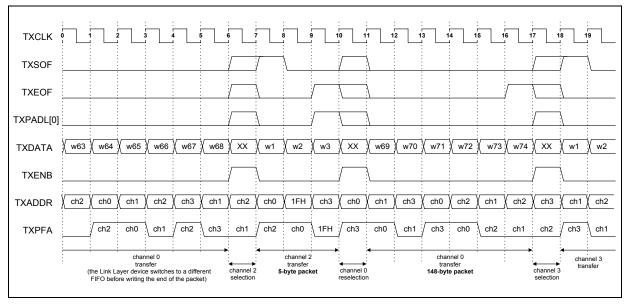

|      | 8.3        |                | it POS-UTOPIA Interface                                                                                 |     |

|      |            | 8.3.1          | Port Selection Mode                                                                                     |     |

|      |            | 8.3.2          | Decode-Response Configuration                                                                           |     |

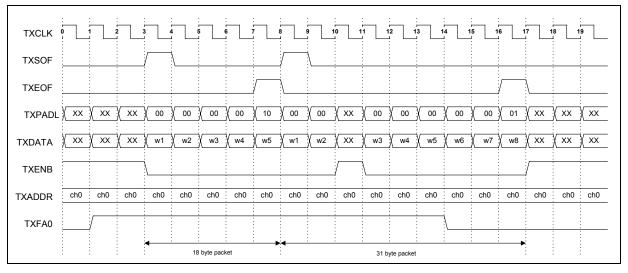

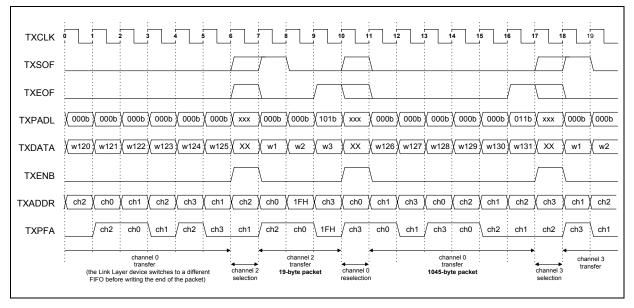

|      |            | 8.3.3<br>8.3.4 | Single-Device/Multiple-Device Configuration<br>Transmit POS-UTOPIA Interface Functional Timing Examples |     |

|      |            |                | <b>C</b> .                                                                                              |     |

| 9.0  |            | -              | Node Functional Description                                                                             |     |

|      | 9.1        |                | e Direction                                                                                             |     |

|      | 9.2        | Transm         | it Direction                                                                                            |     |

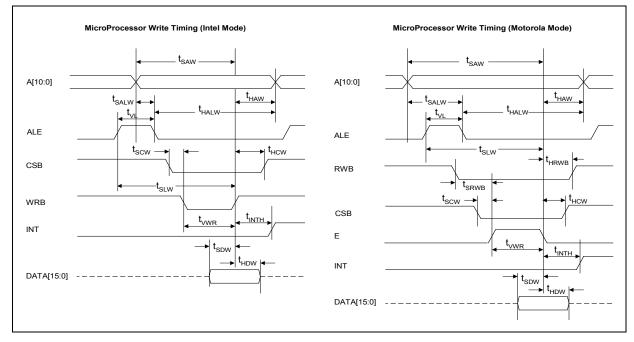

| 10.0 | Micro      | controll       | er Interface                                                                                            | 213 |

|      | 10.1       | Intel Int      | erface                                                                                                  | 213 |

|      | 10.2       |                | a* Interface                                                                                            |     |

|      | 10.3       |                | t Handling                                                                                              |     |

|      |            | 10.3.1         | Interrupt Sources                                                                                       | 214 |

|      |            | 10.3.2         | Interrupt Enables                                                                                       | 214 |

|      |            | 10.3.3         | Interrupt Clearing                                                                                      | 214 |

|      | 10.4       | Counter        | r Reading                                                                                               | 215 |

| 11.0 | Micro      | process        | or Register Description                                                                                 |     |

|      | 11.1       | •              | r Address Map                                                                                           |     |

|      | 11.2       | -              | Registers                                                                                               |     |

|      | 11.3       |                | A Interface Registers                                                                                   |     |

|      | 11.4       |                | VSDH Receive Regenerator Section Termination Channel Registers                                          |     |

|      | 11.5       |                | 7SDH Receive Multiplexer Section Termination Channel Registers                                          |     |

|      | 11.6       |                | 7SDH Receive Multiplexer Section Adaptation Channel Registers                                           |     |

|      | 11.7       |                | /SDH Receive High-Order Path Termination Channel Registers                                              |     |

|      |            |                |                                                                                                         |     |

#### Contents

### intel®

|      | 11.8   | SONET/SDH Transmit Regenerator and Multiplexer Section              | 000 |

|------|--------|---------------------------------------------------------------------|-----|

|      |        | Termination Channel Registers                                       |     |

|      | 11.9   | SONET/SDH Transmit Multiplexer Section Adaptation Channel Registers | 296 |

|      | 11.10  | SONET/SDH Transmit High-Order Path Termination Channel Registers    | 297 |

|      | 11.11  | ATM Receive Channel Registers                                       | 303 |

|      |        | ATM Transmit Channel Registers                                      |     |

|      |        | POS Receive Channel Registers                                       |     |

|      |        | POS Transmit Channel Registers                                      |     |

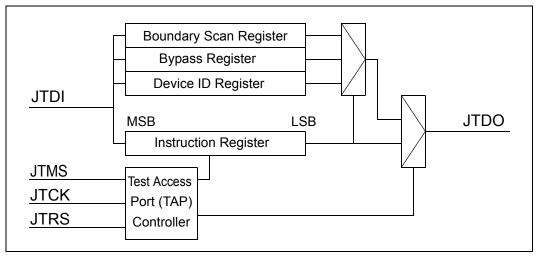

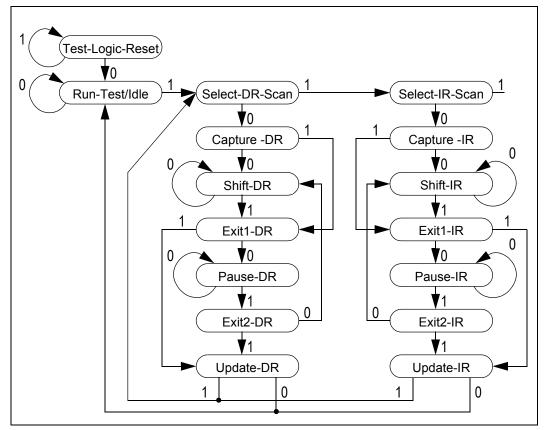

| 12.0 | Test S | Specifications                                                      | 326 |

| 13.0 | Testa  | bility                                                              | 346 |

|      | 13.1   | IEEE* 1149.1 Boundary Scan                                          | 346 |

|      |        | 13.1.1 Instruction Register and Definitions                         |     |

|      |        | 13.1.2 Boundary Scan Register                                       |     |

| 14.0 | Packa  | ge Information                                                      | 350 |

### **Figures**

| 1  | Block Diagram                                                       | 1     |

|----|---------------------------------------------------------------------|-------|

| 2  | Intel IXF6048 Application Diagram                                   | 11    |

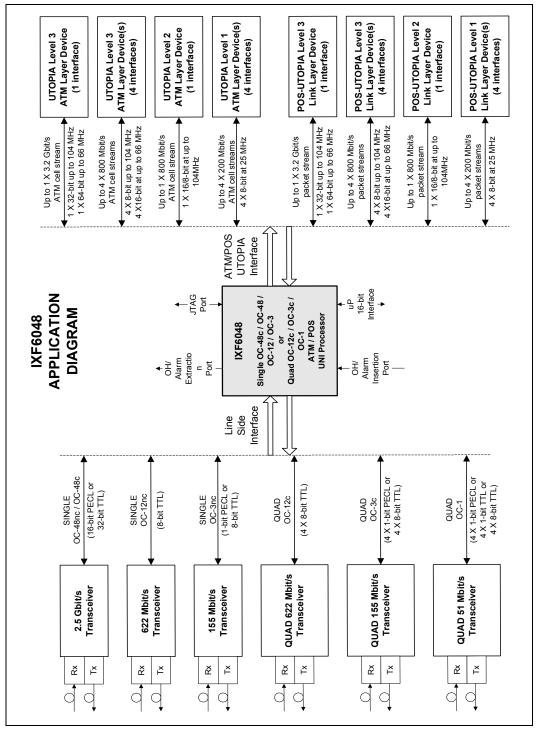

| 3  | 2488 Mbit/s Line Side Interface Example                             | . 101 |

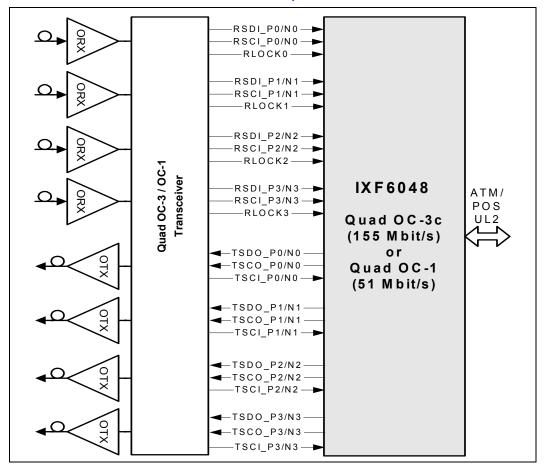

| 4  | Quad 155/51 Mbit/s Line Side Interface Example                      |       |

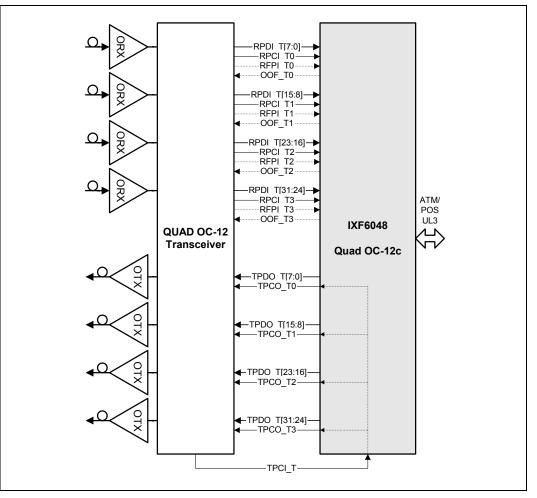

| 5  | Quad OC-12c Example: Four Independent 8-Bit Parallel TTL Interfaces | . 103 |

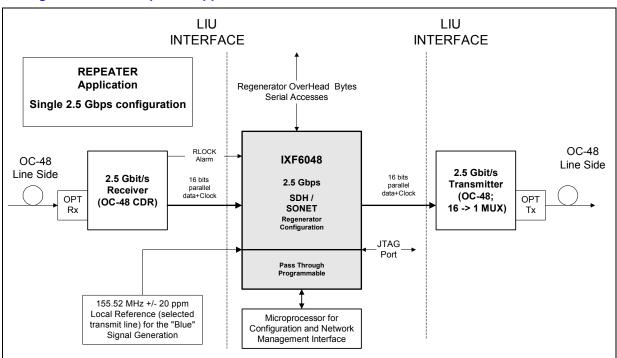

| 6  | OC-48 Repeater Application                                          | . 106 |

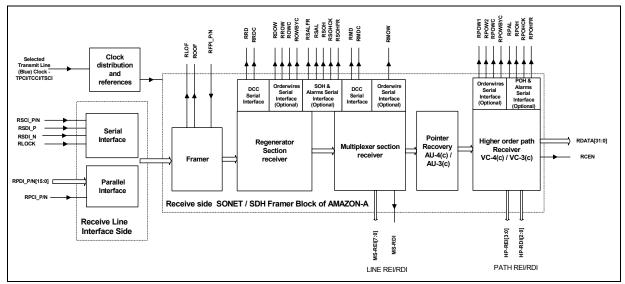

| 7  | SONET/SDH Receiver Blocks                                           | . 111 |

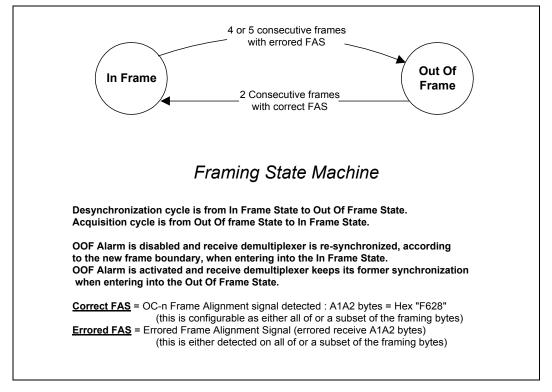

| 8  | Framing State Machine                                               |       |

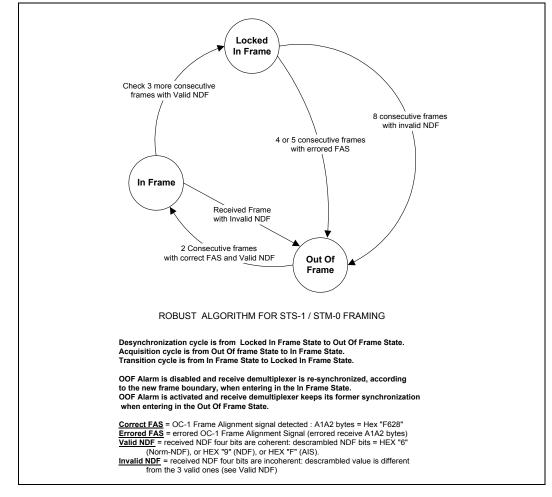

| 9  | STS-1/STM-0 Robust Framing State Machine                            | . 114 |

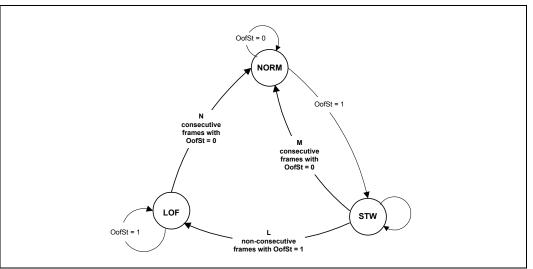

| 10 | LOF State Machine                                                   | . 115 |

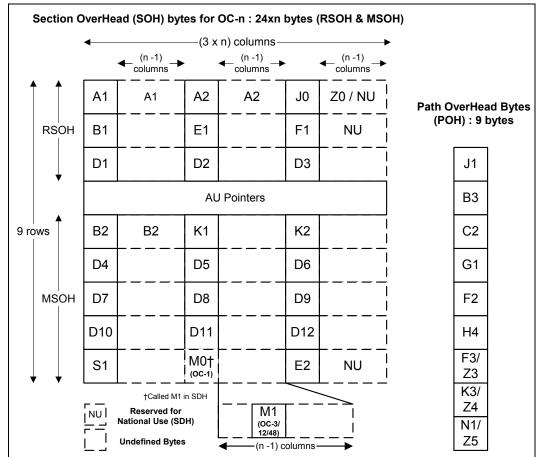

| 11 | Overhead Bytes for the OC-n                                         | . 116 |

| 12 | SONET/SDH Transmitter Blocks                                        | . 128 |

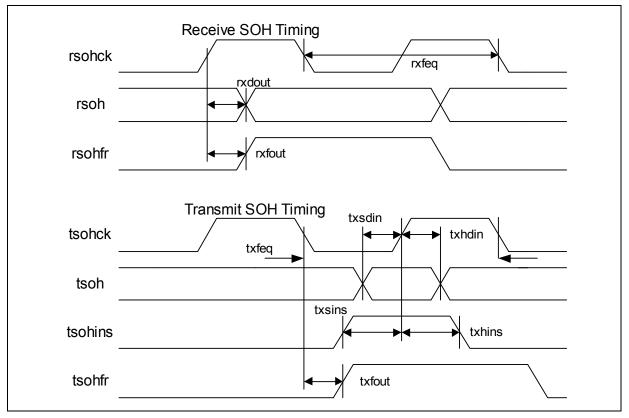

| 13 | Transmit TSOH Serial Bus Timing                                     | . 139 |

| 14 | Receive RSOH Timing                                                 | . 140 |

| 15 | Transmit HPOH Serial Bus Timing                                     | . 141 |

| 16 | Receive HPOH Serial Bus Timing                                      |       |

| 17 | Receive Section Alarm and APS Serial Bus Timing                     | . 145 |

| 18 | Transmit Section Alarm and APS Serial Bus Timing                    | . 147 |

| 19 | Receive Path Alarm Serial Bus Timing                                | . 149 |

| 20 | Transmit Path Alarm Serial Bus Timing                               | . 152 |

| 21 | Transmit D1 to D3 Timing                                            | . 153 |

| 22 | Receive D1 to D3 Timing                                             |       |

| 23 | Transmit D4 to D12 Timing                                           | . 154 |

| 24 | Receive D4 to D12 Timing                                            |       |

| 25 | Transmit Orderwire E1, E2, and F1 Timing                            | . 155 |

| 26 | Receive Section Orderwire E1, F1, and E2 Timing                     |       |

| 27 | Transmit F2 and F3 Orderwire Timing                                 | . 156 |

| 28 | Receive F2 and F3 Orderwire Timing                                  |       |

| 29 | ATM Cell Mapping                                                    |       |

| 30 | ATM Cell Format                                                     | . 158 |

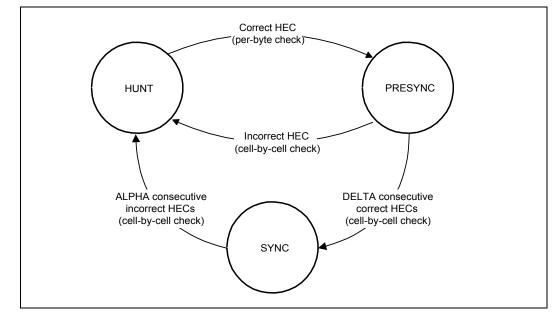

| 31 | Cell Delineation State Diagram                                      | . 160 |

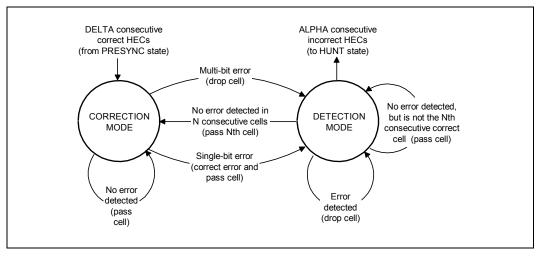

| 32 | HEC Verification State Diagram (While in SYNC State)                | . 161 |

|    |                                                                     |       |

# intel

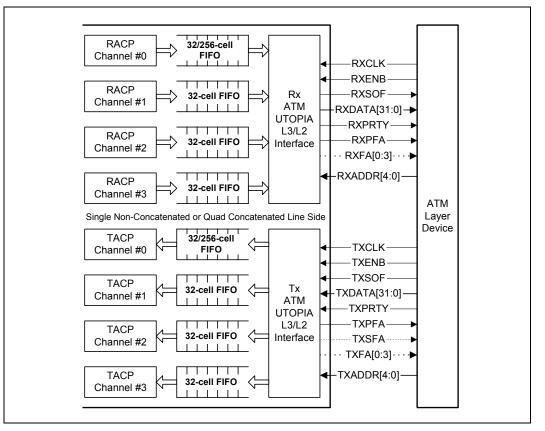

| 33        | Cell Rate Decoupling FIFOs in ATM-UTOPIA Multi-Channel Configuration                                                     | 165 |

|-----------|--------------------------------------------------------------------------------------------------------------------------|-----|

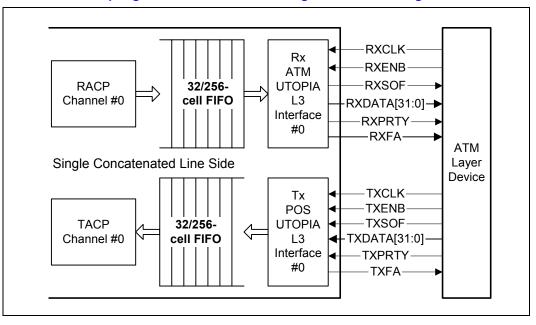

| 34        | Cell Rate Decoupling FIFO in ATM-UTOPIA Single-Channel Configuration                                                     | 165 |

| 35        | Four Independent ATM-UTOPIA Interfaces                                                                                   |     |

| 36        | ATM-UTOPIA Multiple Physical Device Mode                                                                                 | 167 |

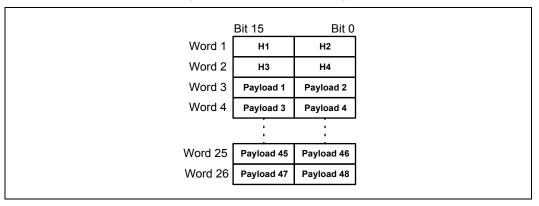

| 37        | 7-Word ATM Cell Structure (64-Bit UTOPIA Interface)                                                                      |     |

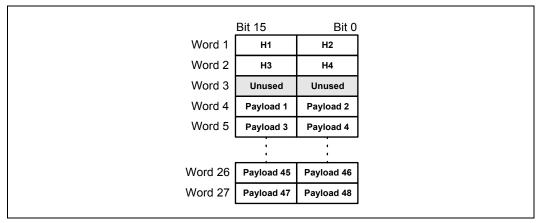

| 38        | 13-Word ATM Cell Structure (32-Bit UTOPIA Interface)                                                                     | 171 |

| 39        | 14-Word ATM Cell Structure (32-Bit UTOPIA Interface)                                                                     | 171 |

| 40        | 26-Word ATM Cell Structure (16-Bit UTOPIA Interface)                                                                     | 171 |

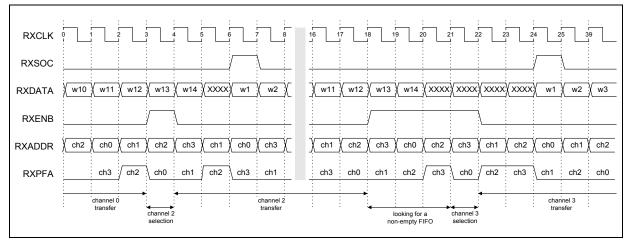

| 41        | 27-Word ATM Cell Structure (16-Bit UTOPIA Interface)                                                                     | 172 |

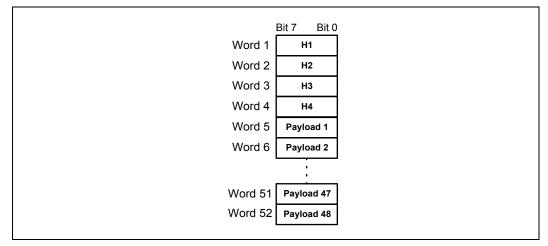

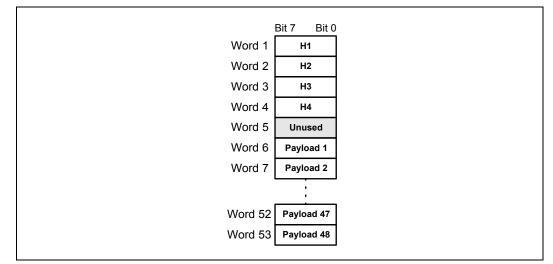

| 42        | 52-Word ATM Cell Structure (8-Bit UTOPIA Interface)                                                                      | 172 |

| 43        | 53-Word ATM Cell Structure (8-Bit UTOPIA Interface)                                                                      | 172 |

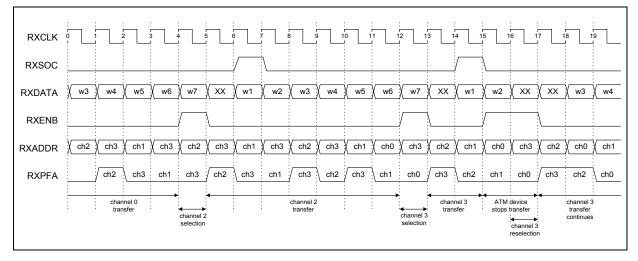

| 44        | Receive ATM-UTOPIA Interface as a Single PHY Device, 64-Bit Data Bus, and 56-                                            |     |

|           | Byte Cell Data Structure (ATM-UTOPIA Level 3)                                                                            | 178 |

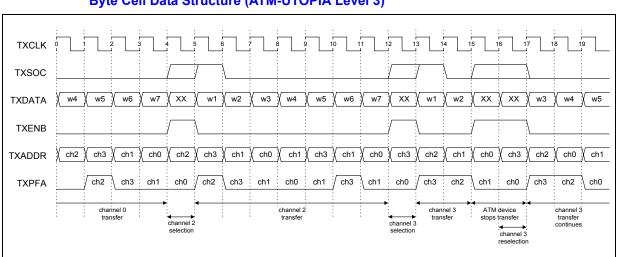

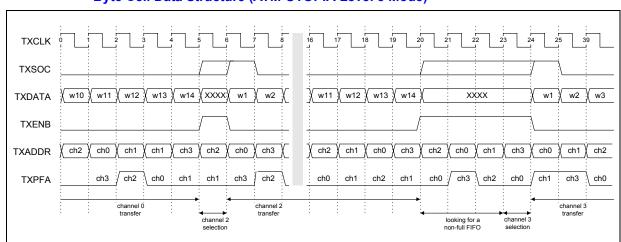

| 45        | Transmit ATM-UTOPIA Interface as a Single PHY Device, 64-Bit Data Bus, and 56-                                           |     |

|           | Byte Cell Data Structure (ATM-UTOPIA Level 3)                                                                            | 179 |

| 46        | Receive ATM-UTOPIA Interface as a Single PHY Device, 32-Bit Data Bus, and 56-                                            |     |

|           | Byte Cell Data Structure (ATM-UTOPIA Level 3 Mode)                                                                       | 179 |

| 47        | Transmit ATM-UTOPIA Interface as a Single PHY Device, 32-Bit Data Bus, and 56-                                           |     |

|           | Byte Cell Data Structure (ATM-UTOPIA Level 3 Mode)                                                                       | 180 |

| 48        | Receive ATM-UTOPIA Interface as a Multiple PHY Device, 32-Bit Data Bus, and 56-                                          |     |

|           | Byte Cell Data Structure                                                                                                 | 180 |

| 49        | Transmit ATM-UTOPIA Interface as a Multiple PHY Device, 32-Bit Data Bus, and 56-                                         |     |

|           | Byte Cell Data Structure                                                                                                 | 181 |

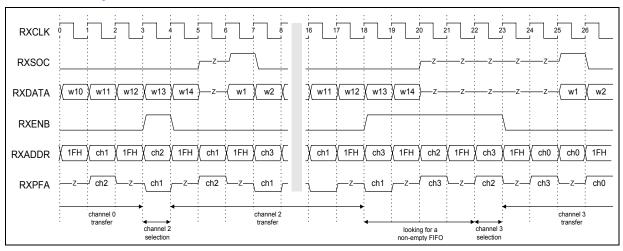

| 50        | Receive ATM-UTOPIA Interface as a Single PHY Device, 16-Bit Data Bus, and 54-                                            |     |

|           | Byte Cell Data Structure                                                                                                 | 181 |

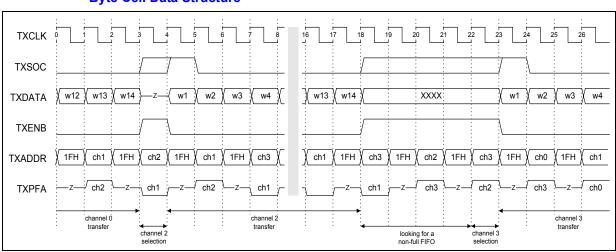

| 51        | Transmit ATM-UTOPIA Interface as a Single PHY Device, 16-Bit Data Bus, and 54-                                           |     |

|           | Byte Cell Data Structure                                                                                                 |     |

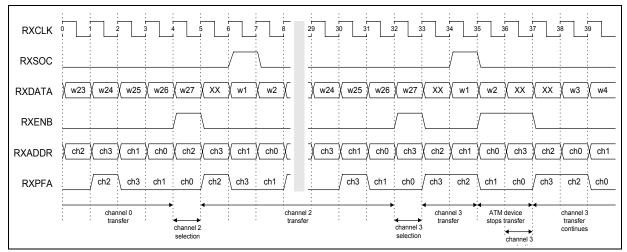

| 52        | Receive ATM-UTOPIA Interface as a Multiple PHY Device, 16-Bit Data Bus, and 54-                                          | 400 |

|           | Byte Cell Data Structure (ATM-UTOPIA Level 2 Mode)                                                                       | 182 |

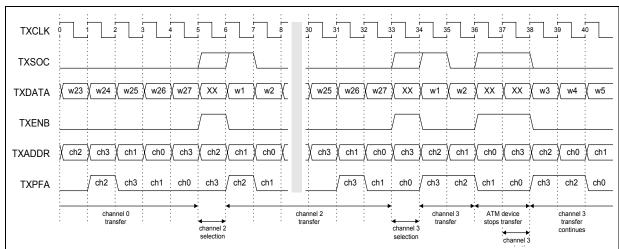

| 53        | Transmit ATM-UTOPIA Interface as a Multiple PHY Device, 16-Bit Data Bus, and 54-                                         | 400 |

| - 4       | Byte Cell Data Structure (ATM-UTOPIA Level 2 Mode)                                                                       |     |

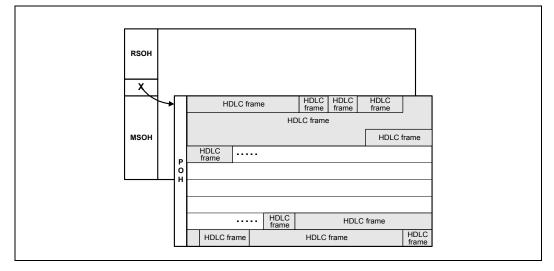

| 54        | HDLC Frame Mapping                                                                                                       |     |

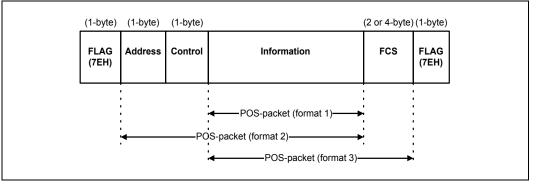

| 55        | HDLC Frame Format                                                                                                        |     |

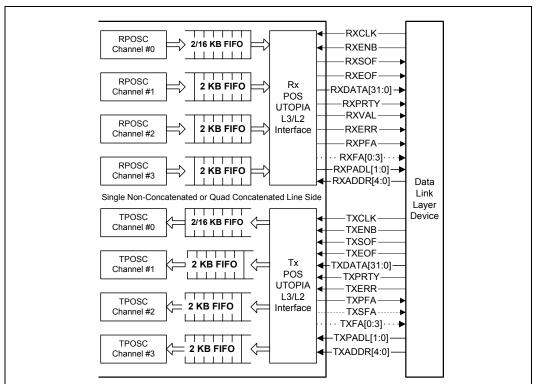

| 56        | POS-UTOPIA Physical Layer/Link Layer Rate Decoupling FIFOs in Multi-Channel                                              | 400 |

|           |                                                                                                                          | 193 |

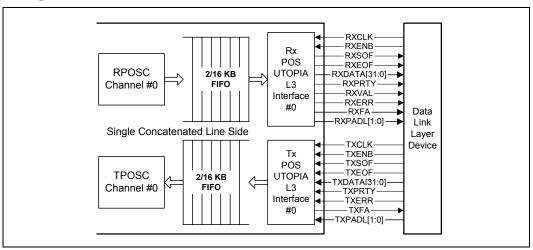

| 57        | POS-UTOPIA Physical Layer/Link Layer Rate Decoupling FIFO in Single-Channel                                              | 400 |

| <b>50</b> | Configuration                                                                                                            |     |

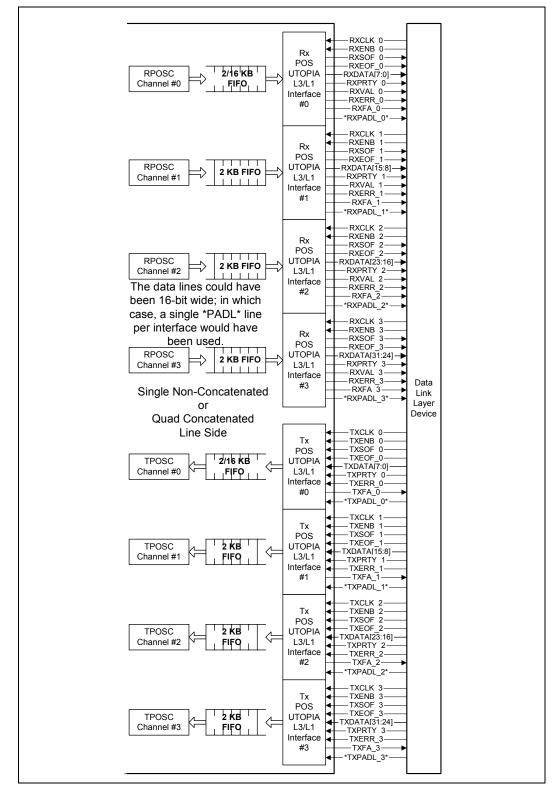

| 58        | Four Independent POS-UTOPIA Interfaces                                                                                   |     |

| 59        | POS-Packet Format.                                                                                                       |     |

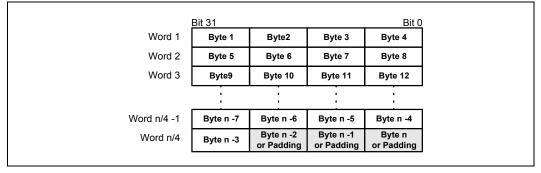

| 60        | POS-Packet Data Structure Using the 64-Bit UTOPIA Interface                                                              |     |

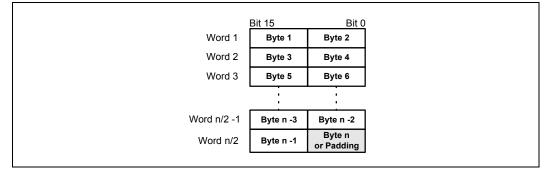

| 61        | POS-Packet Data Structure Using the 32-Bit UTOPIA Interface                                                              |     |

| 62        | POS-Packet Data Structure Using the 16-Bit UTOPIA Interface                                                              |     |

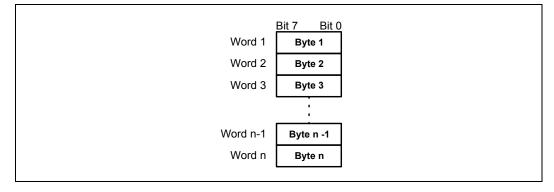

| 63        | POS-Packet Data Structure Using the 8-Bit UTOPIA Interface                                                               | 198 |

| 64        | Receive POS-UTOPIA Interface as a Single PHY Device with 32-Bit Data Bus Using                                           | 005 |

| ~-        | Port Selection (POS-UTOPIA Level 3 Mode and Only Channel 0 Is Used)                                                      | 205 |

| 65        | Transmit POS-UTOPIA Interface as a Single PHY Device with 32-Bit Data Bus Using                                          | 005 |

| ~~        | Port Selection (POS-UTOPIA Level 3 Mode and Only Channel 0 Is Used)                                                      | 205 |

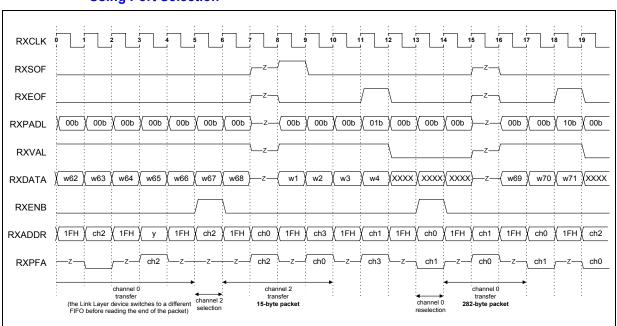

| 66        | Receive POS-UTOPIA Interface as a Single PHY Device with 64-Bit Data Bus Using                                           | 000 |

| 67        | Port Selection (POS-UTOPIA Level 3 Mode)                                                                                 | 206 |

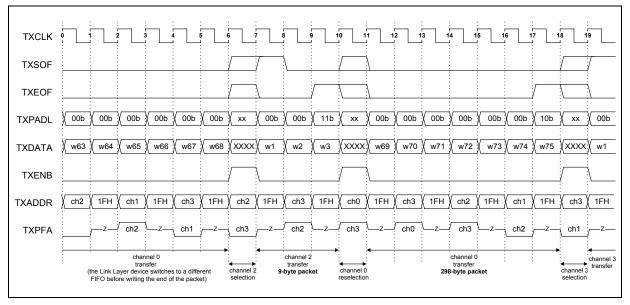

| 67        | Transmit POS-UTOPIA Interface as a Single PHY Device with 64-Bit Data Bus Using Port Selection (POS-UTOPIA Level 3 Mode) | 206 |

|           |                                                                                                                          |     |

#### Contents

### int<sub>el</sub>®

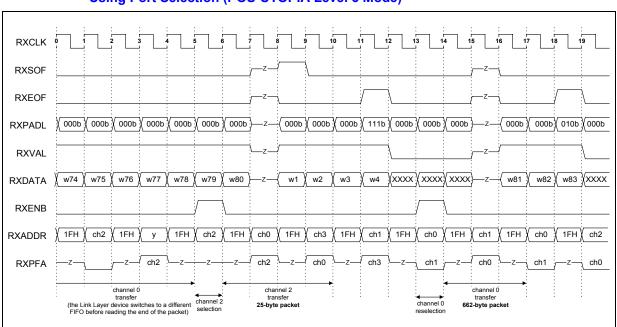

| 68  | Receive POS-UTOPIA Interface as a Multiple PHY Device with 64-Bit Data Bus<br>Using Port Selection (POS-UTOPIA Level 3 Mode)                    | 207 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

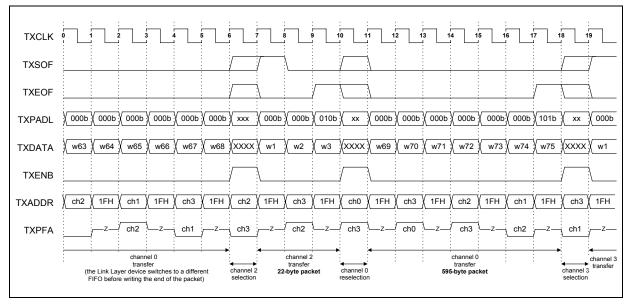

| 69  | Transmit POS-UTOPIA Interface as a Multiple PHY Device with 64-Bit Data Bus<br>Using Port Selection (POS-UTOPIA Level 3 Mode)                   |     |

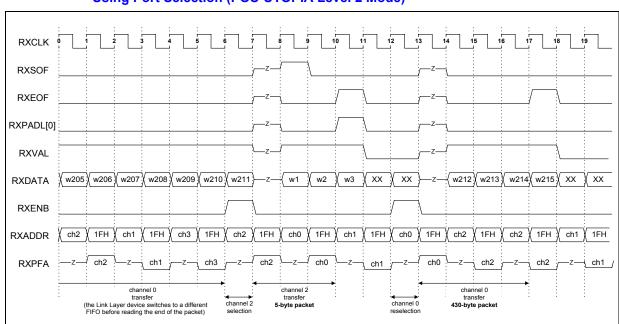

| 70  | Receive POS-UTOPIA Interface as a Single PHY Device with 32-Bit Data Bus Using Port Selection (POS-UTOPIA Level 3 Mode)                         | 208 |

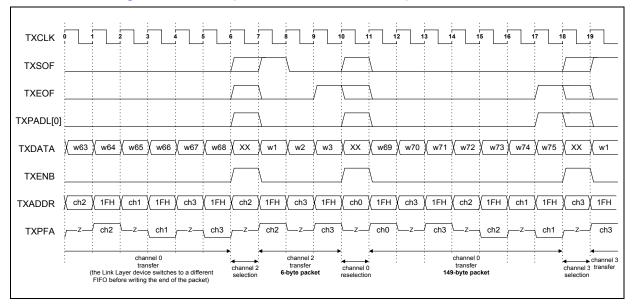

| 71  | Transmit POS-UTOPIA Interface as a Single PHY Device with 32-Bit Data Bus Using Port Selection (POS-UTOPIA Level 3 Mode)                        | 208 |

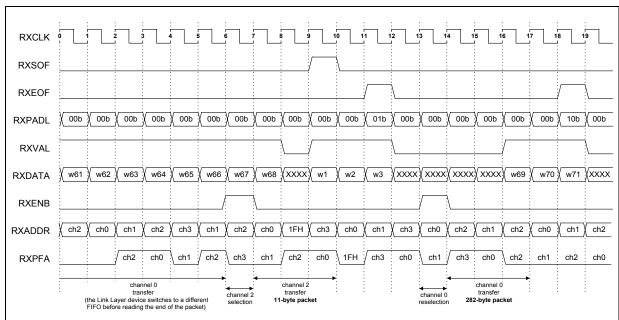

| 72  | Receive POS-UTOPIA Interface as a Multiple PHY Device with 32-Bit Data Bus<br>Using Port Selection                                              | 209 |

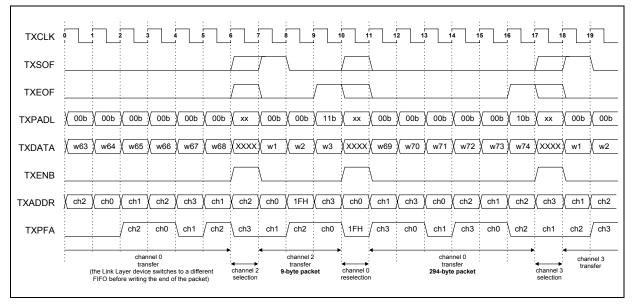

| 73  | Transmit POS-UTOPIA Interface as a Multiple PHY Device with 32-Bit Data Bus<br>Using Port Selection                                             | 209 |

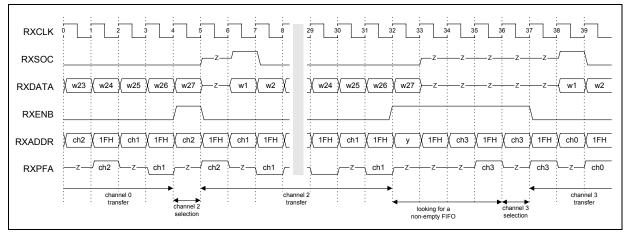

| 74  | Receive POS-UTOPIA Interface as a Multiple PHY Device with 16-Bit Data Bus<br>Using Port Selection (POS-UTOPIA Level 2 Mode)                    | 210 |

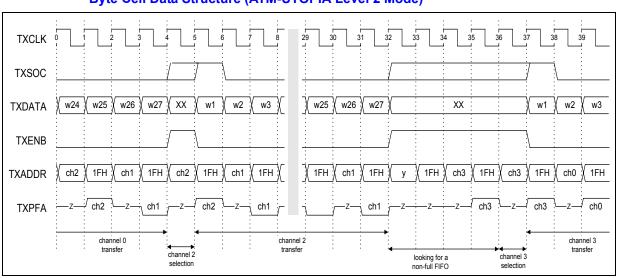

| 75  | Transmit POS-UTOPIA Interface as a Multiple PHY Device with 16-Bit Data Bus<br>Using Port Selection (POS-UTOPIA Level 2 Mode)                   | 210 |

| 76  | Receive POS-UTOPIA Interface as a Single PHY Device with 16-Bit Data Bus Using<br>Port Selection                                                | 211 |

| 77  | Transmit POS-UTOPIA Interface as a Single PHY Device with 16-Bit Data Bus Using Port Selection                                                  |     |

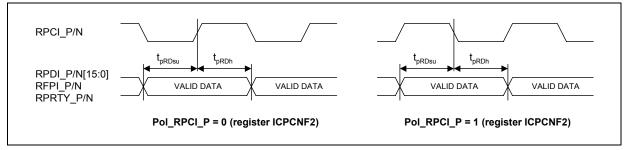

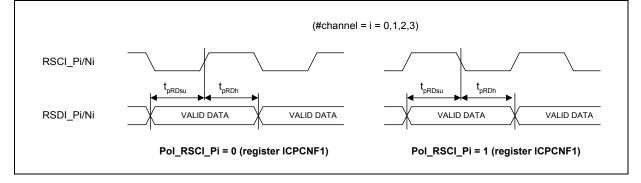

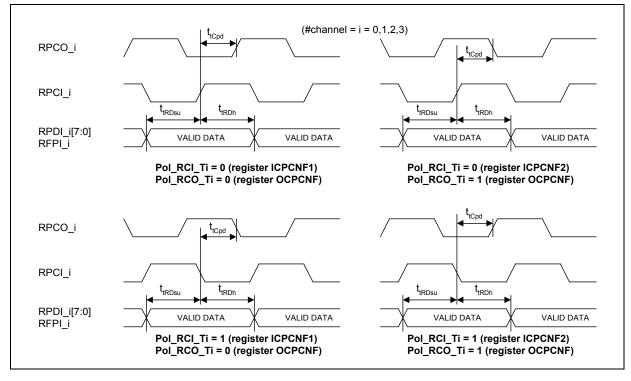

| 78  | Receive 16-bit Differential PECL Line Side Interface Timings                                                                                    |     |

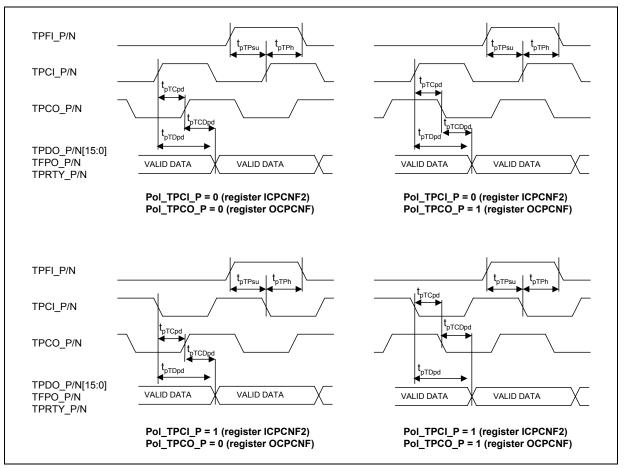

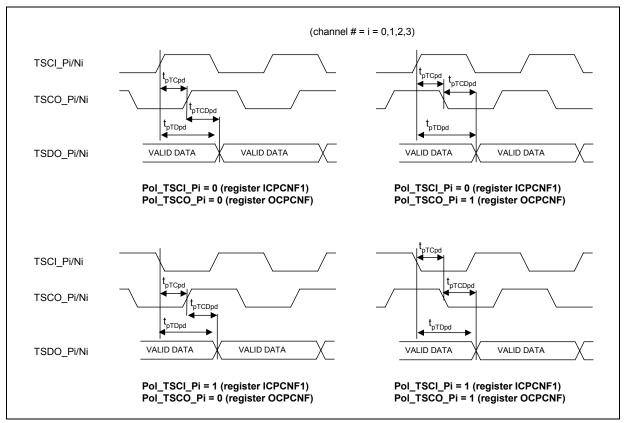

| 79  | Transmit 16-Bit Differential PECL Line Side Interface Timings                                                                                   | 329 |

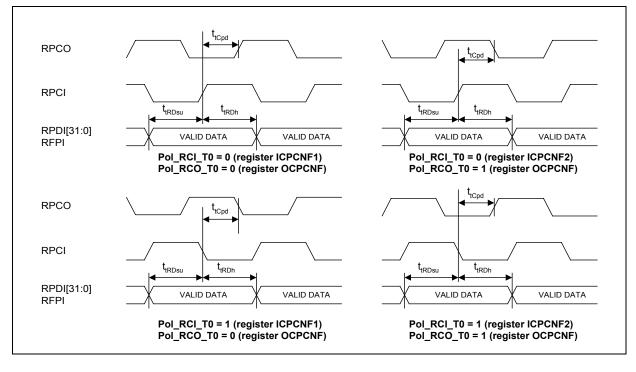

| 80  | Receive 1-Bit Differential PECL Line Side Interface Timings                                                                                     |     |

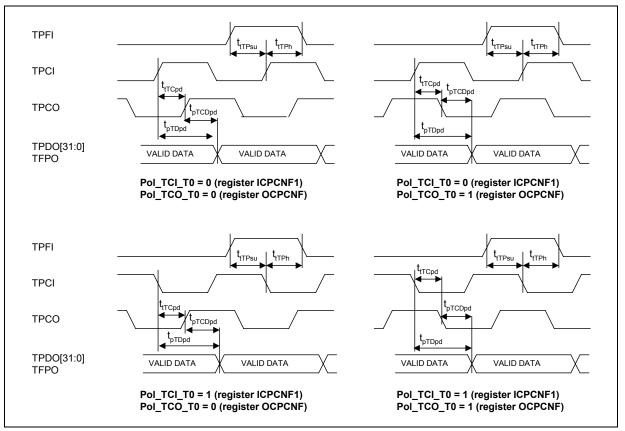

| 81  | Transmit 1-bit Differential PECL Line Side Interface Timings                                                                                    |     |

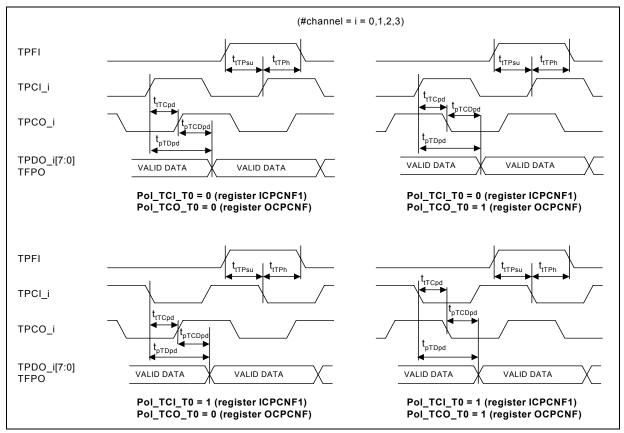

| 82  | Receive 32-Bit TTL Line Side Interface Timings                                                                                                  | 332 |

| 83  | Transmit 32-Bit TTL Line Side Interface Timings                                                                                                 | 333 |

| 84  | Receive 8-Bit TTL Line Side Interface Timings                                                                                                   | 334 |

| 85  | Transmit 8-Bit TTL Line Side Interface Timings                                                                                                  | 335 |

| 86  | Serial Overhead Timing Diagram                                                                                                                  | 336 |

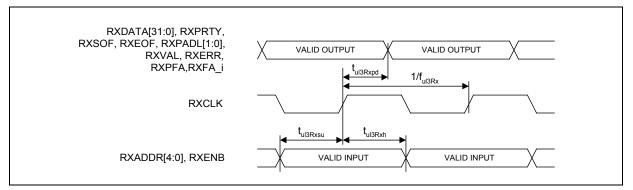

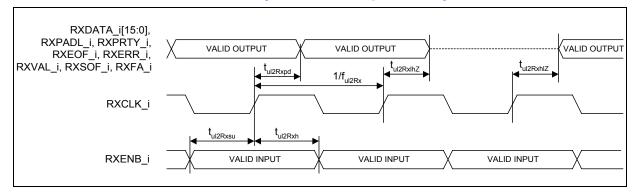

| 87  | Receive UTOPIA Single Interface Configured for 104 MHz Operation: 32/16/8-Bit                                                                   |     |

|     | Data Bus, Two Clock Cycle Decode-Response Delay and No High-Impedance Outputs                                                                   | 337 |

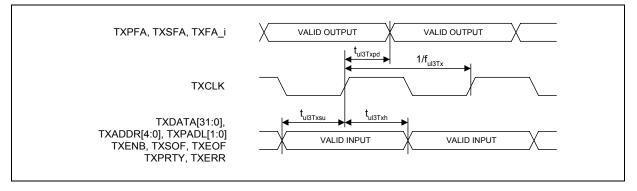

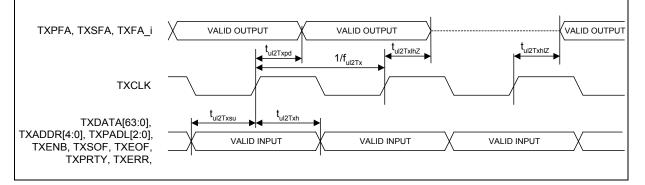

| 88  | Transmit UTOPIA Single Interface Configured for 104 MHz Operation: 32/16/8-Bit                                                                  |     |

|     | Data Bus, Two Clock Cycle Decode-Response Delay and No High-Impedance Outputs                                                                   | 337 |

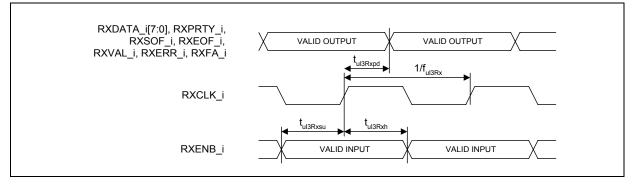

| 89  | Receive UTOPIA Quad Interface Configured for 104 MHz Operation: 8-Bit Data Bus,                                                                 |     |

|     | Two Clock Cycle Decode-Response Delay and No High-Impedance Outputs                                                                             | 338 |

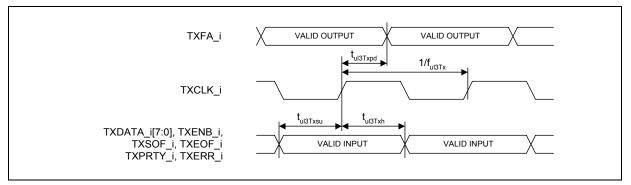

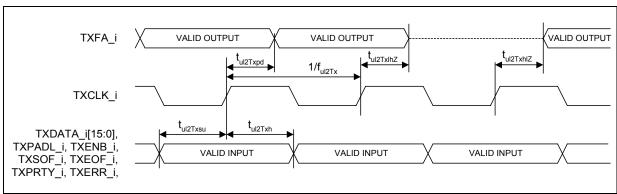

| 90  | Transmit UTOPIA Quad Interface Configured for 104 MHz Operation: 8-Bit Data                                                                     |     |

| ~ 1 | Bus, Two Clock Cycle Decode-Response Delay and No High-Impedance Outputs                                                                        | 339 |

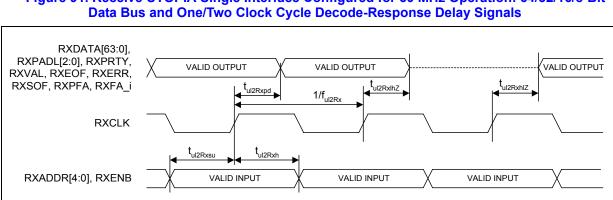

| 91  | Receive UTOPIA Single Interface Configured for 50 MHz Operation: 64/32/16/8-Bit Data Bus and One/Two Clock Cycle Decode-Response Delay Signals  | 340 |

| 92  | Transmit UTOPIA Single Interface Configured for 50 MHz Operation: 64/32/16/8-Bit Data Bus and One/Two Clock Cycle Decode-Response Delay Signals | 340 |

| 93  | Receive UTOPIA Quad Interface Configured for 50 MHz Operation: 16/8-Bit Data<br>Bus and One/Two Clock Cycle Decode-Response Delay               | 341 |

| 94  | Transmit UTOPIA Quad Interface Configured for 50 MHz Operation: 16/8-Bit Data                                                                   | 040 |

| 05  | Bus and One/Two Clock Cycle Decode-Response Delay                                                                                               |     |

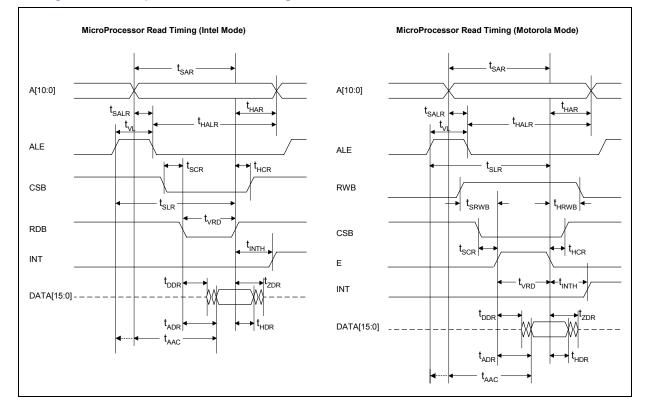

| 95  | Microprocessor Read Timing                                                                                                                      |     |

| 96  | Microprocessor Write Timing                                                                                                                     |     |

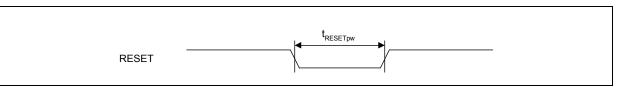

| 97  | Asynchronous Reset (RESET) Timing                                                                                                               |     |

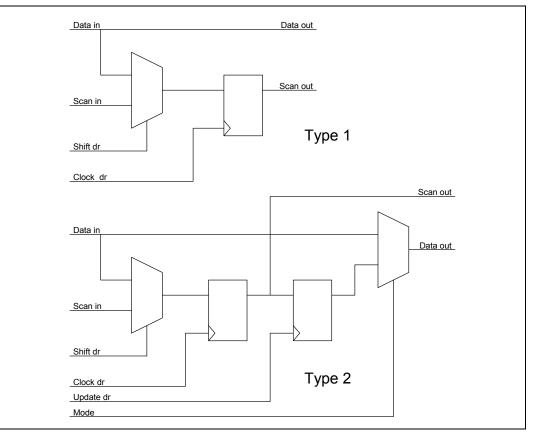

| 98  | JTAG Test Circuitry                                                                                                                             |     |

| 99  | TAP State Machine                                                                                                                               |     |

|     | Boundary Scan Cell Types                                                                                                                        |     |

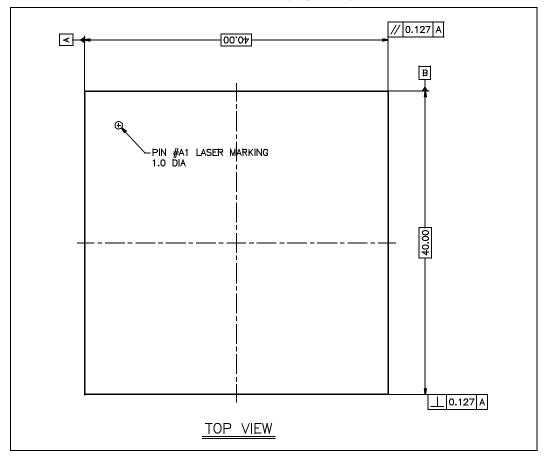

| 101 | Mechanical Information for the 600 TBGA (Top View)                                                                                              | 350 |

# intel®

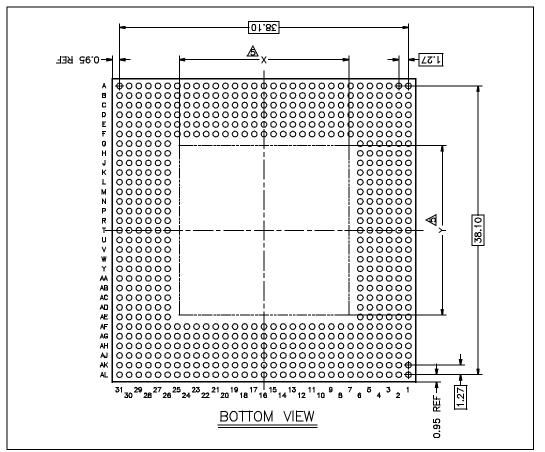

| 102 Mechanical Information for the 600 TBGA (Bottom View)          |  |

|--------------------------------------------------------------------|--|

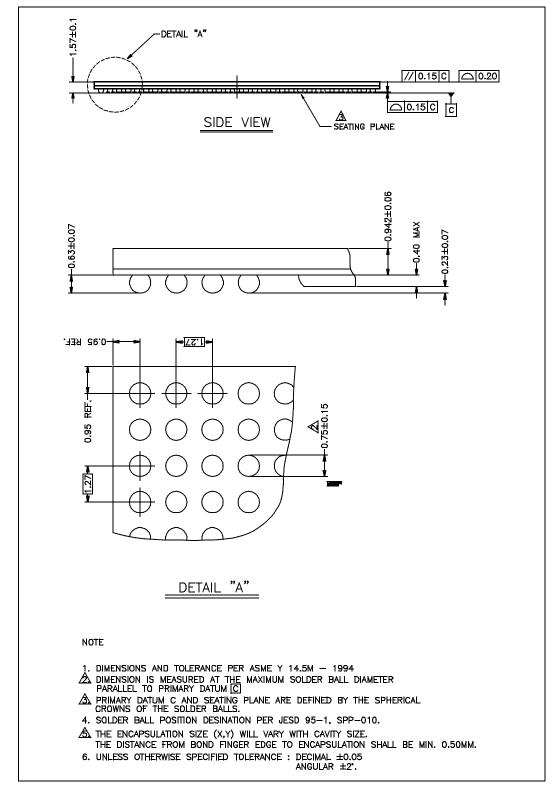

| 103 Mechanical Information for the 600 TBGA (Side and Detail View) |  |

### **Tables**

| 1  | Intel IXF6048 Main Configurations                                | 12  |

|----|------------------------------------------------------------------|-----|

| 2  | Intel IXF6048 Pin Diagram (Bottom View)                          |     |

| 3  | Intel IXF6048 Pin Diagram (Bottom View)                          |     |

| 4  | Pin Description                                                  |     |

| 5  | PECL I/O Pin Equivalence on the Line Side Interface              |     |

| 6  | I/O Pin Equivalence on the Receive TTL Line Side Interface       |     |

| 7  | I/O Pin Equivalence on the Transmit TTL Line Side Interface      |     |

| 8  | TTL I/O Pin Equivalence on the Receive OH/Alarm Extraction Ports |     |

| 9  | TTL I/O Pin Equivalence on the Transmit OH/Alarm Insertion Ports |     |

| 10 | TTL I/O Pin Equivalence on the Receive UTOPIA Interface          |     |

| 11 | TTL I/O Pin Equivalence on the Transmit UTOPIA Interface         |     |

| 12 | EED Register Settings                                            |     |

| 13 | DSD Registers Setting                                            |     |

| 14 | G1x RDI Bit Coding                                               |     |

| 15 | K2 RDI Bit Coding                                                |     |

| 16 | RSAL[i] Bus Frame                                                |     |

| 17 | TSAL[i] Bus Frame                                                |     |

| 18 | RPAL[i] Bus Frame                                                |     |

| 19 | TPAL[i] Bus Frame                                                |     |

| 20 | UTOPIA Receive Data Bus Width                                    |     |

| 21 | UTOPIA Transmit Data Bus Width                                   |     |

| 22 | Byte Destuffing                                                  |     |

| 23 | Byte Stuffing                                                    |     |

| 24 | UTOPIA Receive Data Bus Width                                    |     |

| 25 | UTOPIA Transmit Data Bus Width                                   |     |

| 26 | Register Address Map                                             |     |

| 27 | LCD Filter Configuration Examples                                |     |

| 28 | HDLC Flow Control Using XmtlPGRelEn = '1' and XmtlPGRelCnf = '0' |     |

| 29 | HDLC Flow Control Using XmtIPGRelEn = '1' and XmtIPGRelCnf = '1' |     |

| 30 | HDLC Flow Control Using XmtIPGAbsEn = '1' and XmtIPGAbsCnf = '0' | 323 |

| 31 | HDLC Flow Control Using XmtIPGAbsEn = '1' and XmtIPGAbsCnf = '1' | 323 |

| 32 | Absolute Maximum Ratings                                         | 326 |

| 33 | Recommended Operating Conditions                                 |     |

| 34 | DC Electrical Characteristics                                    |     |

| 35 | Receive 16-Bit Differential PECL Line Side Interface Timings     | 329 |

| 36 | Transmit 16-Bit Differential PECL Line Side Interface Timings    | 330 |

| 37 | Receive 1-Bit Differential PECL Line Side Interface Timings      |     |

| 38 | Transmit 1-Bit Differential PECL Line Side Interface Timings     |     |

| 39 | Receive 32-Bit TTL Line Side Interface Timings                   | 333 |

| 40 | Transmit 32-Bit TTL Line Side Interface Timings                  |     |

| 41 | Receive 8-Bit TTL Line Side Interface Timings                    | 335 |

| 42 | Transmit 8-Bit TTL Line Side Interface Timings                   |     |

| 43 | Serial Overhead Timing Parameters                                | 337 |

#### Contents

# intel

| 44 | Receive UTOPIA Single Interface Timings for the Configurations Supporting 104<br>MHz Operation: 32/16/8-Bit Wide Data Bus, Two Decode-Response Clock Cycles<br>and No High-Impedance Outputs  | . 338 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 45 | Transmit UTOPIA Single Interface Timings for the Configurations Supporting 104<br>MHz Operation: 32/16/8-Bit Wide Data Bus, Two Decode-Response Clock Cycles<br>and No High-Impedance Outputs | . 338 |

| 46 | Receive UTOPIA Quad Interface Timings for the Configurations Supporting 104<br>MHz Operation: 8-Bit Wide Data Bus, Two Decode-Response Clock Cycles and No<br>High-Impedance Outputs          | . 339 |

| 47 | Transmit UTOPIA Quad Interface Timings for the Configurations Supporting 104<br>MHz Operation: 8-Bit Wide Data Bus, Two Decode-Response Clock Cycles and No<br>High-Impedance Outputs         | . 339 |

| 48 | Receive UTOPIA Single Interface Timings for the Configurations Supporting 50 MHz<br>Operation: 64/32/16/8-Bit Wide Data Bus, One Decode-Response Clock Cycles or<br>High-Impedance Outputs.   | . 340 |

| 49 | Transmit UTOPIA Single Interface Timings for the Configurations Supporting 50<br>MHz Operation: 64/32/16/8-Bit Wide Data Bus, One Decode-Response Clock Cycles<br>or High-Impedance Outputs   | .341  |

| 50 | Receive UTOPIA Quad Interface Configured for 50 MHz Operation: 16/8-Bit Data<br>Bus and One/Two Clock Cycle Decode-Response Delay                                                             | . 342 |

| 51 | Transmit UTOPIA Quad Interface Configured for 50 MHz Operation: 16/8-Bit Data<br>Bus and One/Two Clock Cycle Decode-Response Delay                                                            | . 343 |

| 52 | Microprocessor Data Read Timing Parameters (Considering Outputs with a 50 pF Load)                                                                                                            |       |

| 53 | Microprocessor Data Write Timing Parameters                                                                                                                                                   |       |

| 54 | Asynchronous Reset (RESET) Timing                                                                                                                                                             |       |

| 55 | Boundary Scan Port                                                                                                                                                                            | . 346 |

### **Revision History**

| Date                                                                                  | Revision | Description                                                          |  |

|---------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------|--|

| September 2003 004 Please refer to the change bars.                                   |          | Please refer to the change bars.                                     |  |

| July 2003 003 Please refer to the change bars.                                        |          | Please refer to the change bars.                                     |  |

| January 2003 002 Corrected typographical errors. Removed the Xmt/Rcv PeclMsb_cnf bit. |          | Corrected typographical errors. Removed the Xmt/Rcv PeclMsb_cnf bit. |  |

| November 2001 001 Initial release.                                                    |          | Initial release.                                                     |  |

# intel®

### **1.0 Pin Description**

#### Table 1. Intel IXF6048 Main Configurations

| Operation Mode         | Line Side Interfaces                                         | ATM/POS-UTOPIA Interfaces                                             |

|------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|

| Single STS-48c/STM-16c | 1 x 16-bit PECL at 155.52 MHz<br>1 x 32-bit TTL at 77.76 MHz | 1 x 32-bit at up to 104 MHz (UL3)<br>1 x 64-bit at up to 52 MHz (UL3) |

|                        |                                                              | 1 x 32-bit at up to 104 MHz (UL3)                                     |

|                        | 1 x 16-bit PECL at 155.52 MHz                                | 1 x 64-bit at up to 52 MHz (UL3)                                      |

| Single STS-48/STM-16   | 1 x 32-bit TTL at 77.76 MHz                                  | 4 x 8-bit at up to 104 MHz (UL3)                                      |

|                        |                                                              | 4 x 16-bit at up to 52 MHz (UL2 x 4)                                  |

|                        |                                                              | 1 x 16-bit at up to 104 MHz (UL2)                                     |

| Single STS-12/STM-4    | 1 x 8-bit TTL at 77.76 MHz                                   | 1 x 8-bit at up to 104 MHz (UL2)                                      |

|                        |                                                              | 4 x 8-bit at up to 104 MHz (UL1 x 4)                                  |

|                        | 1 x 1-bit PECL at 155.52 MHz                                 | 1 x 8-bit at up to 104 MHz (UL2)                                      |

| Single STS-3/STM-1     | 1 x 8-bit TTL at 19.44 MHz                                   | 1 x 16-bit at up to 104 MHz (UL2)                                     |

|                        |                                                              | 3 x 8-bit at up to 104 MHz (UL1 x 3)                                  |

|                        |                                                              | 1 x 32-bit at up to 104 MHz (UL3)                                     |

| Quad STS-12c/STM-4c    | 4 x 8-bit TTL at 77.76 MHz                                   | 1 x 64-bit at up to 52 MHz (UL3)                                      |

|                        |                                                              | 4 x 8-bit at up to 104 MHz (UL3)                                      |

|                        |                                                              | 4 x 16-bit at up to 52 MHz (UL2 x 4)                                  |

| Quad STS-3c/STM-1      | 4 x 1-bit PECL at 155.52 MHz                                 | 1 x 16-bit at up to 104 MHz (UL2)                                     |

|                        | 4 x 8-bit TTL at 19.44 MHz                                   | 4 x 8-bit at up to 104 MHz (UL1 x 4)                                  |

|                        | 4 x 1-bit PECL at 51.84 MHz                                  | 1 x 8-bit at up to 104 MHz (UL2)                                      |

| Quad STS-1             | 4 x 1-bit TTL at 51.84 MHz                                   | 1 x 16-bit at up to 104 MHz (UL2)                                     |

|                        | 4 x 8-bit TTL at 6.48 MHz                                    | 4 x 8-bit at up to 104 MHz (UL1 x 3)                                  |

I.

| N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N         N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                          |                                          |                                          |                                          |                                          |                                          |                                          |                                         | -                                |                              |                          |                         |                         |                                  |                      |                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------|----------------------------------|------------------------------|--------------------------|-------------------------|-------------------------|----------------------------------|----------------------|------------------------|

| 0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Α                                        | В                                        | С                                        | D                                        | E                                        | F                                        | G                                        | н                                       | J                                | к                            | L                        | М                       | N                       | Р                                | R                    | Т                      |

| 2         00.0.10         000.0.10         000.0.10         000.0.10         000.0.00         000.0.00         000.0.00         000.0.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         0000.00         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  | GND_TTL                                  | GND_TTL                                  | TXDATA 1161                              | TXPRTY_2                                 | TXDATA[12]<br>TXDAT_0[12]<br>TXDATA_1[4] | VDD_CORE                                 | TXDATA[3]<br>TXDATA_0[3]                 | TXEOF<br>TXEOF_0                        | TDOW 3                           |                              |                          | TPOH_2<br>TXDATA[54]    | TOWC 0                  | TMOW_0<br>TXDATA[44]             | GND_TTL              | GND_TTL                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  | GND_TTL                                  | GND_TTL                                  | TXSOF_3                                  | TXDATA 1[1]                              | TXDAT 0(15)                              | GND_CORE                                 | _                                        | TXDATA[6]<br>TXDATA_0[6]                |                                  | VDD_CORE                     | TDOW 0                   | GND_CORE                | TOWC 3                  | TMOW_1<br>TXDATA[45]             | GND_TTL              | GND_TTL                |

| Discl. (1)         Discl. (2)         Discl. (2) <thdiscl. (2)<="" th="">         Discl. (2)         Discl. (</thdiscl.>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3  | TXDAT_1[11]<br>TXDATA_3[3]               | TXDATA_1[9]<br>TXDATA_3[1]               | VDD_CORE                                 | TXDATA_1[0]<br>TXDATA_2[0]               | -                                        | TXDAT_0[10]<br>TXDATA_1[2]               | TXDATA_Ò[8]<br>TXDATA_1[0]               | VDD_TTL                                 | TXDATA[1]<br>TXDATA_0[1]         | TXDATA[0]<br>TXDATA_0[0]     | TDOW 2                   | TPOHINS_0<br>TXDATA[56] | TPOH_0<br>TXDATA[52]    | TXDATA[46]                       | TROW_0<br>TXDATA[40] | TSALFR_3<br>TXDATA[39] |

| Local L                        | 4  | TXDATA[26]<br>TXDAT_1[10]<br>TXDATA_3[2] | TXDATA[31]<br>TXDAT_1[15]<br>TXDATA_3[7] | TXERR_3                                  | TXDATA_2[4]                              | TXDATA_1[3]<br>TXDATA_2[3]               | TXDAT 0[14]                              | TXDAT 0[13]                              | TXPRTY_1                                | TXDATA[5]<br>TXDATA_0[5]         |                              | GND_CORE                 | TPOHINS_1<br>TXDATA[57] | VDD_CORE                | TPOHCK_3<br>TMOW_3<br>TXDATA[47] | TROW 1               | TSALFR 0               |

| NEX.2         DDMA         VUILOUME         RADACCOME         DDMALAGE         DDMALAGE <thddmalage< th=""> <thddmalage< th="">         DDM</thddmalage<></thddmalage<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  | TXFA_1                                   | GND_CORE                                 | TXSFA                                    | VDD_TTL                                  | TXDATA[23]<br>TXDATA_1[7]<br>TXDATA_2[7] | TXDATA[18]<br>TXDATA_1[2]<br>TXDATA_2[2] | TXEOF_2                                  | TXDATA[9]<br>TXDATA_0[9]<br>TXDATA_1[1] | TXERR_1                          | TXSOF_1                      | TXDATA[2]<br>TXDATA_0[2] | TDOW 1                  | TPOH_1<br>TXDATA[53]    | TOWC 1                           | TROW 3               | TOWBYC 3               |

| Image: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  | TXFA_2                                   | TXPFA                                    | VDD_CORE                                 | _                                        | TXPRTY_3                                 | TXEOF_3                                  | TXDATA[21]<br>TXDATA_1[5]<br>TXDATA_2[5] | TXSOF_2                                 | TYDAT 01111                      | TXDATA[7]<br>TXDATA_0[7]     | TXDATA[4]<br>TXDATA_0[4] |                         | TPOHINS_2<br>TXDATA[58] | TOWC 2                           | TSAL 2               | TSALCK 2               |

| 8         10.000000         10000000         10000000         10000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         100000000         1000000000         1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7  | TXPADL[0]                                | TXPADL_3                                 | TXPADL[1]                                | TXDATA[28]<br>TXDAT_1[12]<br>TXDATA_3[4] | TXDATA 1181                              | TXDATA[29]<br>TXDAT_1[13]<br>TXDATA_3[5] |                                          |                                         |                                  |                              |                          |                         |                         |                                  |                      |                        |