|                   |                                                                                                                                   |          |          |                                   |                  |                 |    | I                              | REVISI | IONS                                                     |     |                                        |                    |        |          |              |      |      |      |    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------------------------|------------------|-----------------|----|--------------------------------|--------|----------------------------------------------------------|-----|----------------------------------------|--------------------|--------|----------|--------------|------|------|------|----|

| LTR               |                                                                                                                                   |          |          |                                   | [                | DESCR           |    | N                              |        |                                                          |     |                                        |                    | DATE ( | /R-MO-D  | A)           |      | APPR | OVED |    |

| А                 | Changes in accordance with NOR 5962-R075-95. – LTG                                                                                |          |          |                                   |                  |                 |    |                                |        | 95-03-30 Mo                                              |     |                                        | Monica L. Poelking |        |          |              |      |      |      |    |

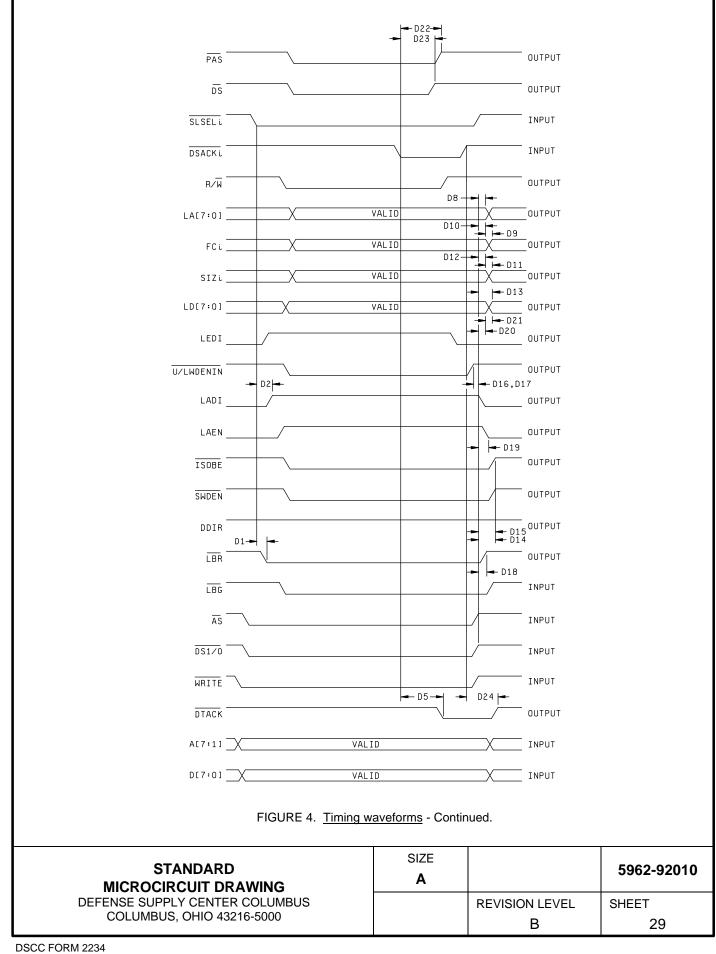

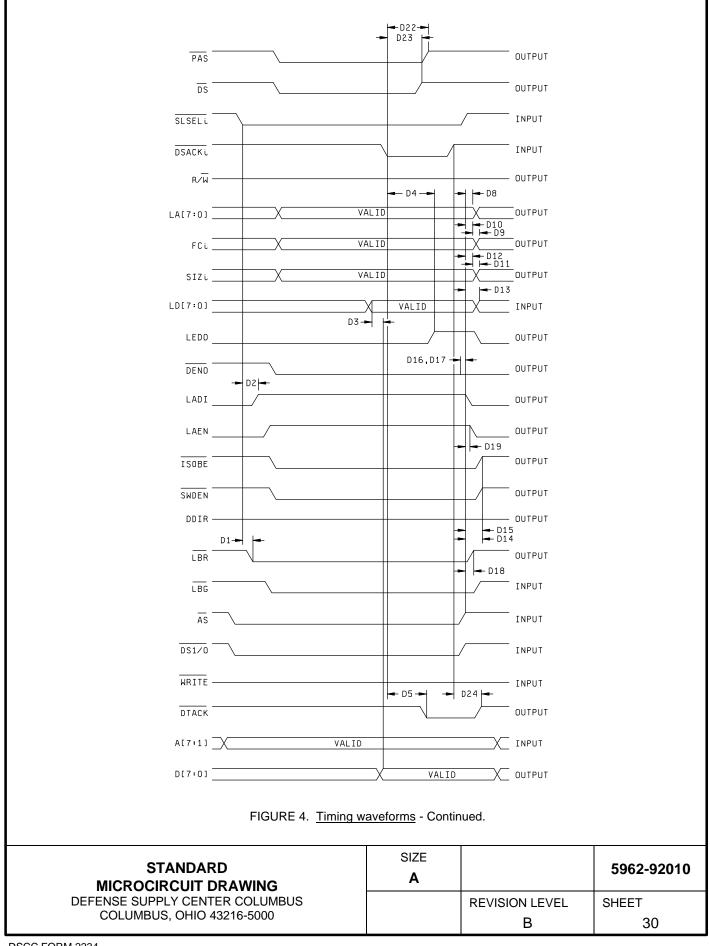

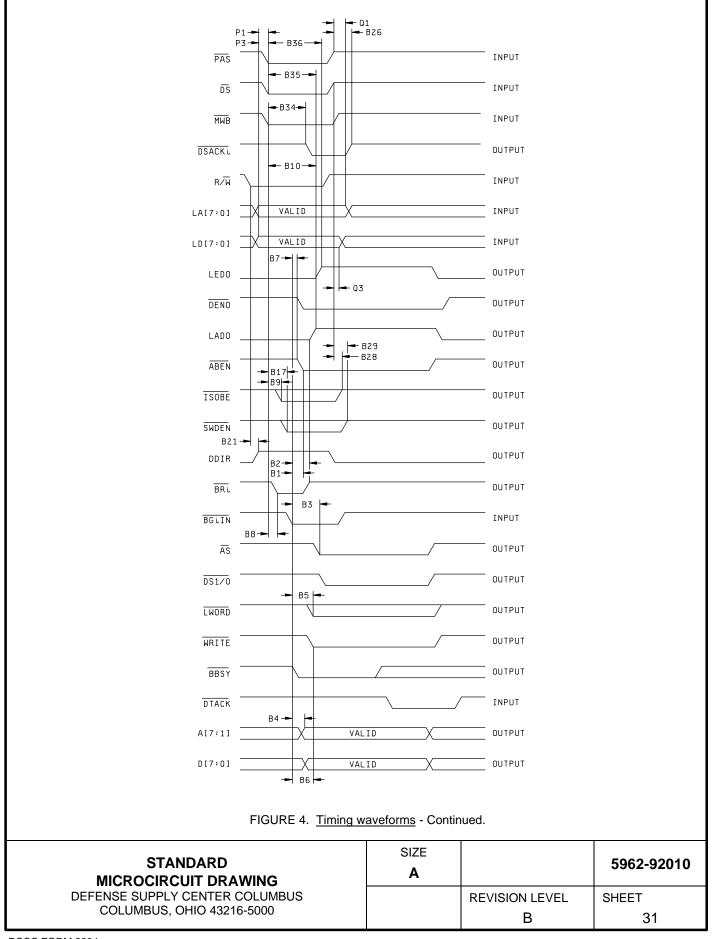

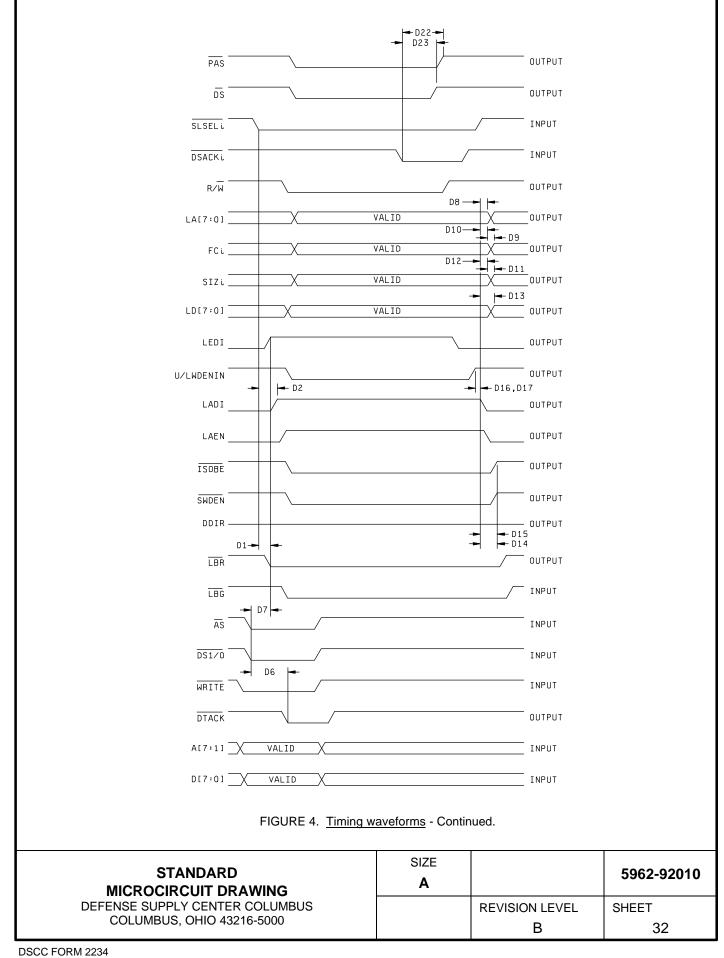

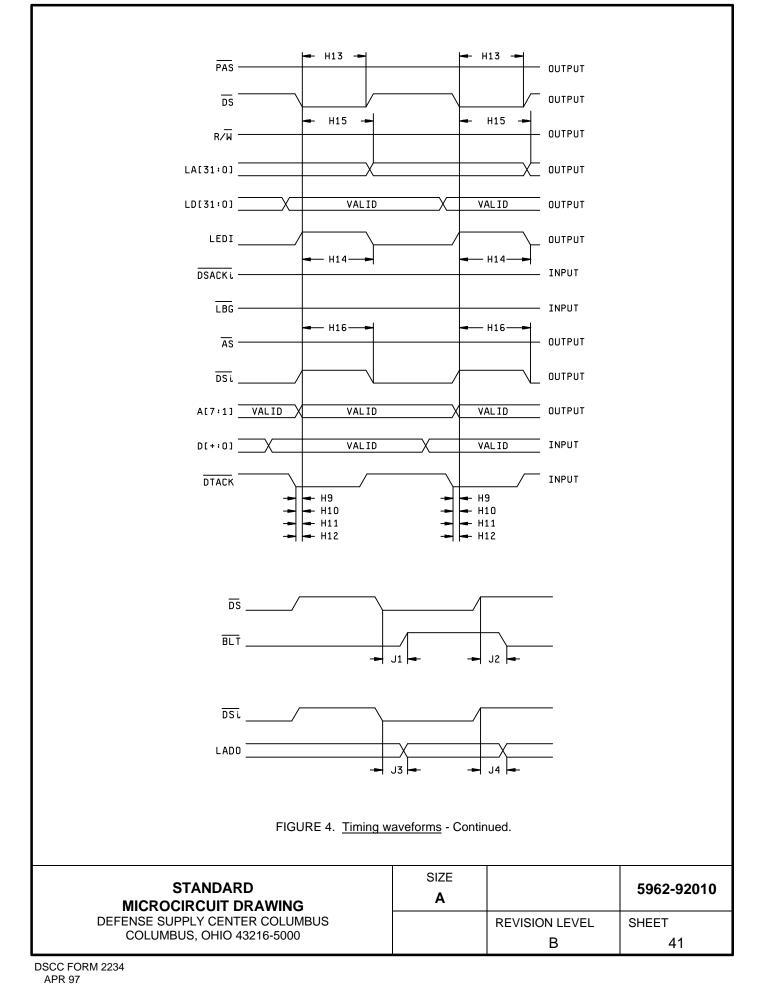

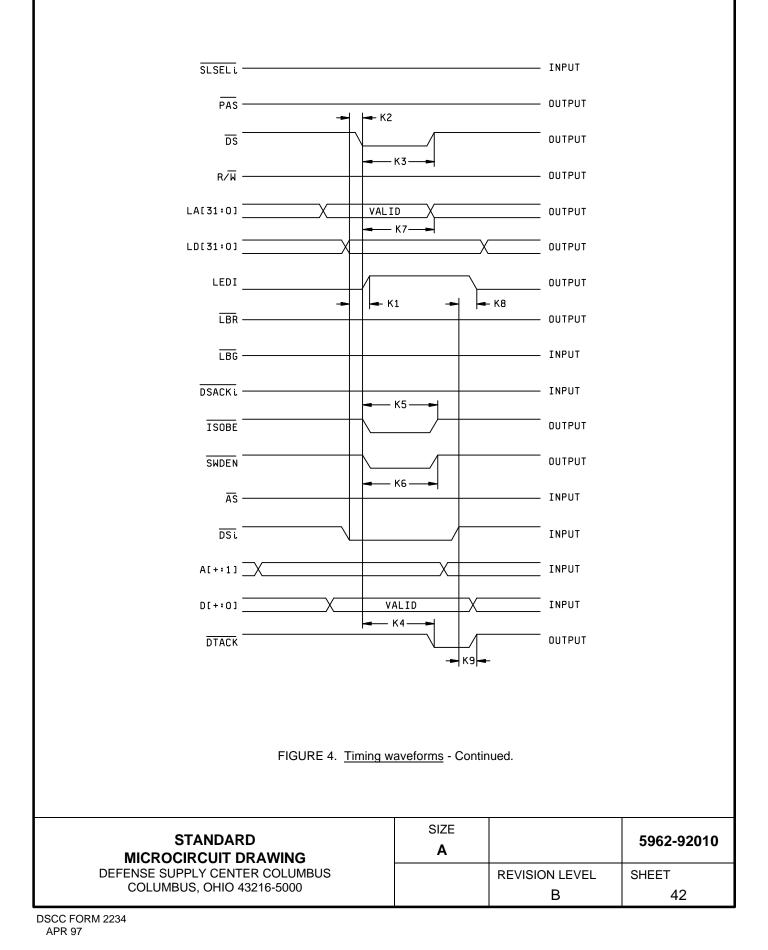

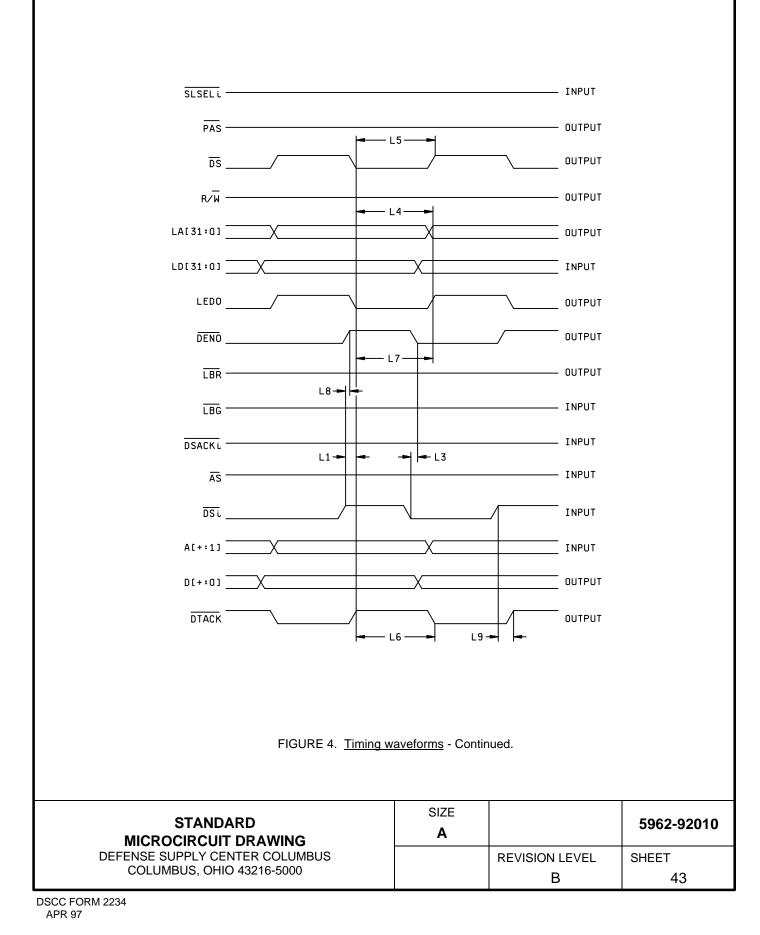

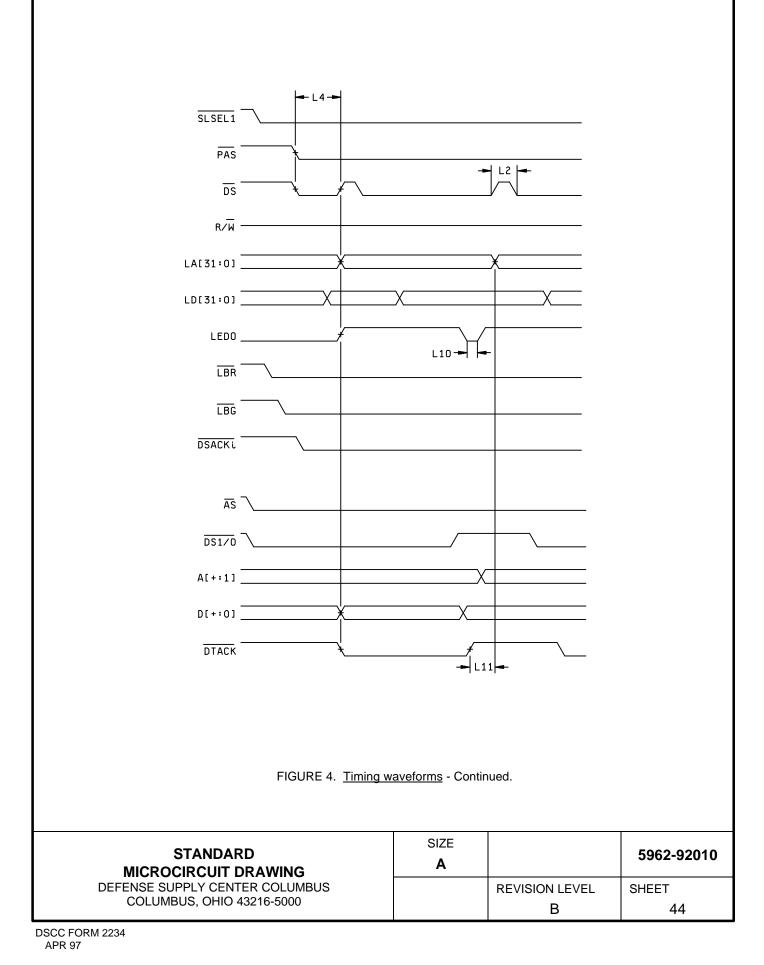

| В                 | Change AC limits in table I. Correct pin names in figure 2, fig<br>table III. Update boilerplate. Editorial changes throughout. – |          |          |                                   |                  |                 |    | gure 3, figure 4, and 01-02-23 |        |                                                          | -   | Thomas M. Hess                         |                    |        |          |              |      |      |      |    |

|                   |                                                                                                                                   |          |          |                                   |                  |                 |    |                                |        |                                                          |     |                                        |                    |        |          |              |      |      |      |    |

|                   | _                                                                                                                                 |          |          | 1                                 | 1                | 1               | T  | [                              |        | 1                                                        | I   | 1                                      | 1                  | [      |          | 1            | 1    | 1    |      |    |

| REV               | B                                                                                                                                 | B        |          |                                   |                  |                 |    |                                |        |                                                          |     |                                        |                    |        |          |              |      |      |      |    |

| SHEET<br>REV      | 55<br>B                                                                                                                           | 56<br>B  | В        | В                                 | В                | В               | В  | В                              | В      | В                                                        | В   | В                                      | В                  | В      | В        | В            | В    | В    | В    | В  |

| SHEET             | 35                                                                                                                                | 36       | 37       | 38                                | 39               | 40              | 41 | 42                             | 43     | 44                                                       | 45  | 46                                     | 47                 | 48     | 49       | 50           | 51   | 52   | 53   | 54 |

| REV               | B                                                                                                                                 | B        | B        | В                                 | В                | B               | B  | B                              | В      | В                                                        | B   | B                                      | -т,                | B      | В        | B            | В    | B    | В    | B  |

| SHEET             | 15                                                                                                                                | 16       | 17       | 18                                | 19               | 20              | 21 | 22                             | 23     | 24                                                       | 25  | 26                                     | 27                 | 28     | 29       | 30           | 31   | 32   | 33   | 34 |

| REV STATUS        |                                                                                                                                   | <u> </u> | <u> </u> | REV                               | /                | 1               | В  | В                              | В      | В                                                        | В   | В                                      | В                  | В      | В        | В            | В    | В    | В    | В  |

| OF SHEETS         |                                                                                                                                   |          |          | SHE                               | ET               |                 | 1  | 2                              | 3      | 4                                                        | 5   | 6                                      | 7                  | 8      | 9        | 10           | 11   | 12   | 13   | 14 |

| PMIC N/A          |                                                                                                                                   |          |          |                                   | PARED<br>omas M  | ) BY<br>1. Hess |    |                                |        | DEFENSE SUPPLY CENTER COLUMBUS<br>- COLUMBUS, OHIO 43216 |     |                                        |                    |        |          |              |      |      |      |    |

| STAN              |                                                                                                                                   |          |          | -                                 | CKED<br>omas N   | BY<br>1. Hess   |    |                                |        |                                                          |     |                                        |                    |        |          | HIO<br>cc.dl |      | )    |      |    |

| MICRO<br>DRA      |                                                                                                                                   |          |          |                                   | ROVED<br>nica L. | ) BY<br>Poelkin | g  |                                |        | мс                                                       | RUC | IRCU                                   | יים דו             |        | <u> </u> | 09.1         |      | 211  |      |    |

| THIS DRAWIN       | THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE                        |          |          | DRAWING APPROVAL DATE<br>93-01-22 |                  |                 |    |                                |        |                                                          |     | T, DIGITAL, CMOS, V<br>ONTROLLER, MONO |                    |        |          |              |      |      |      |    |

| DEPAR<br>AND AGEN |                                                                                                                                   |          |          | REVI                              | ISION I          | LEVEL           |    |                                |        | SIZE                                                     | 4   |                                        | E COD              |        |          | 5            | 962- | 920  | 10   |    |

| AMS               | SC N/A                                                                                                                            |          |          |                                   |                  | E               | 3  |                                |        | SHE                                                      | ET  | 1                                      | OF                 | 56     |          |              |      |      |      |    |

DSCC FORM 2233

APR 97 <u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

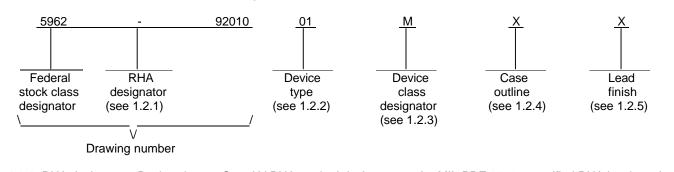

1.2 PIN. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function            |

|-------------|----------------|-----------------------------|

| 01          | VIC068A        | VMEbus interface controller |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class              |                                   | Device requireme                                                                                                                                                | nts documentation                   |  |  |  |  |

|---------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| М                         |                                   | Vendor self-certification to the requirements for MIL-STD-883 compliant,<br>non-JAN class level B microcircuits in accordance with MIL-PRF-38535,<br>appendix A |                                     |  |  |  |  |

| Q or V                    | Certification                     | and qualification to                                                                                                                                            | MIL-PRF-38535                       |  |  |  |  |

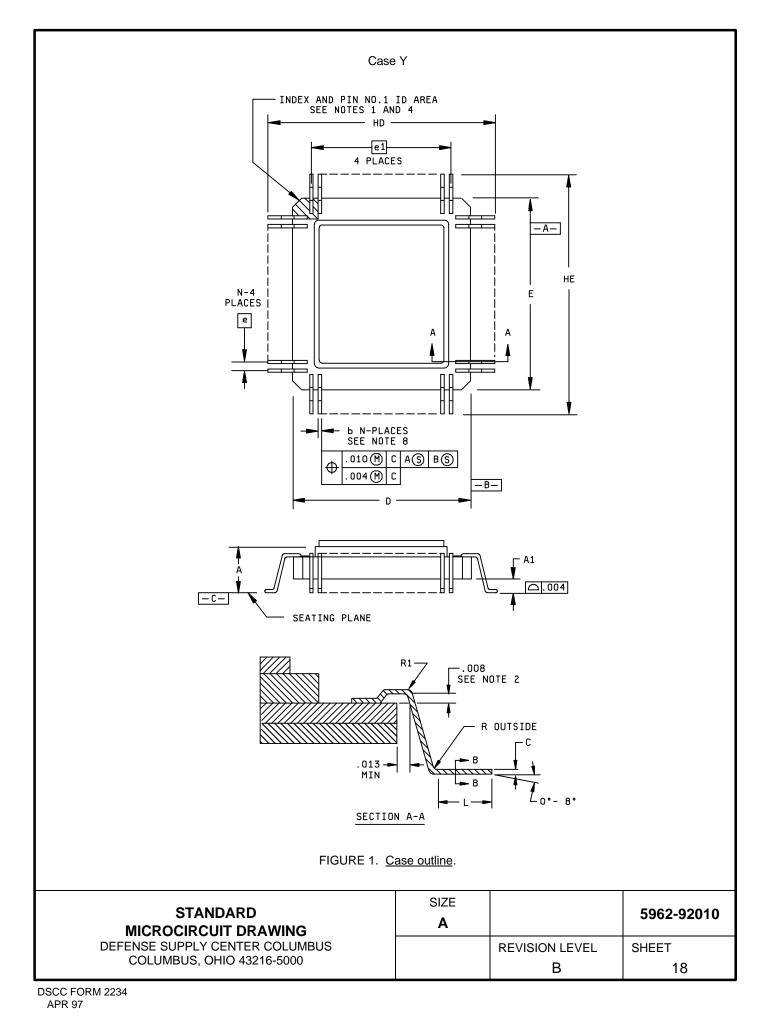

| 1.2.4 Case outline(s). Th | ne case outline(s) are as desigr  | nated in MIL-STD-183                                                                                                                                            | 5 and as follows:                   |  |  |  |  |

| Outline letter            | Descriptive designator            | Terminals                                                                                                                                                       | Package style                       |  |  |  |  |

| X<br>Y                    | CMGA7-P145<br>See figure 1        | 145<br>160                                                                                                                                                      | Pin grid array<br>Flat pack         |  |  |  |  |

| 1.2.5 Lead finish. The le | ad finish is as specified in MIL- | PRF-38535 for device                                                                                                                                            | e classes Q and V or MIL-PRF-38535, |  |  |  |  |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-92010 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 2          |

1.3 Absolute maximum ratings. 1/

| Voltage on any pin with respect to ground               |                  |

|---------------------------------------------------------|------------------|

| Power dissipation (P <sub>D</sub> )                     | 1.5 W            |

| Storage temperature range (T <sub>STG</sub> )           | 65°C to +150°C   |

| Lead temperature (soldering, 10 seconds)                | +260°C           |

| Thermal resistance, junction-to-case ( $\Theta_{JC}$ ): |                  |

| Case outline X                                          | See MIL-STD-1835 |

| Case outline Y                                          | 10°C/W           |

| Junction temperature (T <sub>J</sub> )                  | 175°C            |

| 1.4 <u>Recommended operating conditions</u> .           |                  |

| Supply voltage range (V <sub>CC</sub> )                 | 5.0 V dc ±10%    |

| Case operating temperature range | (T <sub>C</sub> ) | 55°C to +125°C |

|----------------------------------|-------------------|----------------|

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

#### SPECIFICATION

### DEPARTMENT OF DEFENSE

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

### STANDARDS

#### DEPARTMENT OF DEFENSE

| MIL-STD-883  | - | Test Methods and Procedures for Microelectronics.      |

|--------------|---|--------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines. |

### HANDBOOKS

#### DEPARTMENT OF DEFENSE

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's). MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                | 5962-92010 |

|-------------------------------------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |           | REVISION LEVEL | SHEET      |

|                                                             |           | D              | 3          |

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

# 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

3.2.1 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.4 and figure 1 herein.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

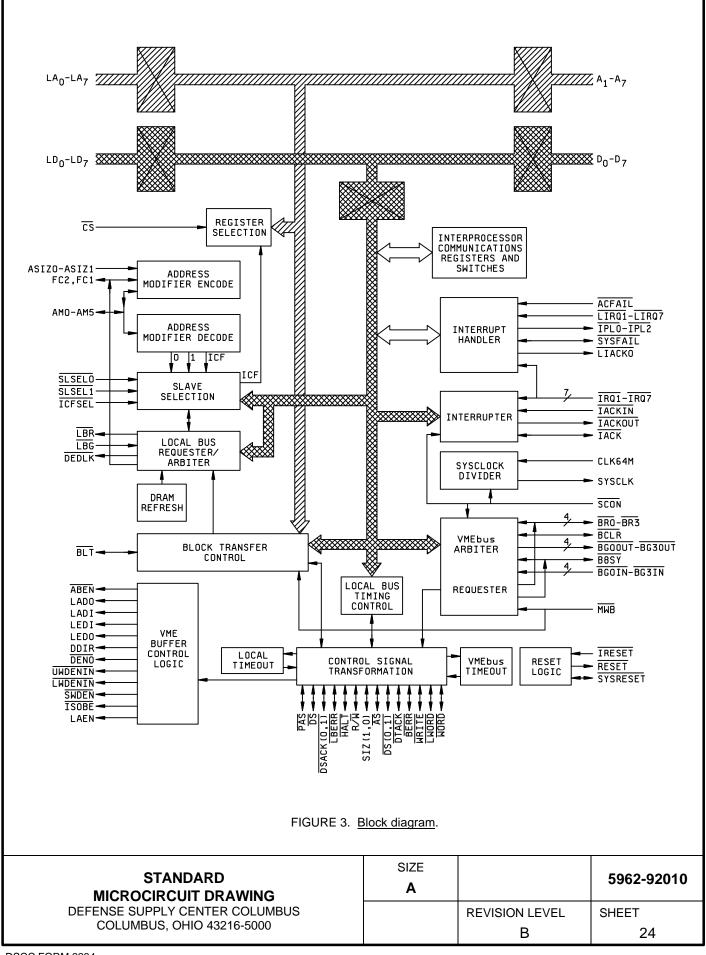

3.2.3 <u>Block diagram</u>. The block diagram shall be as specified on figure 3.

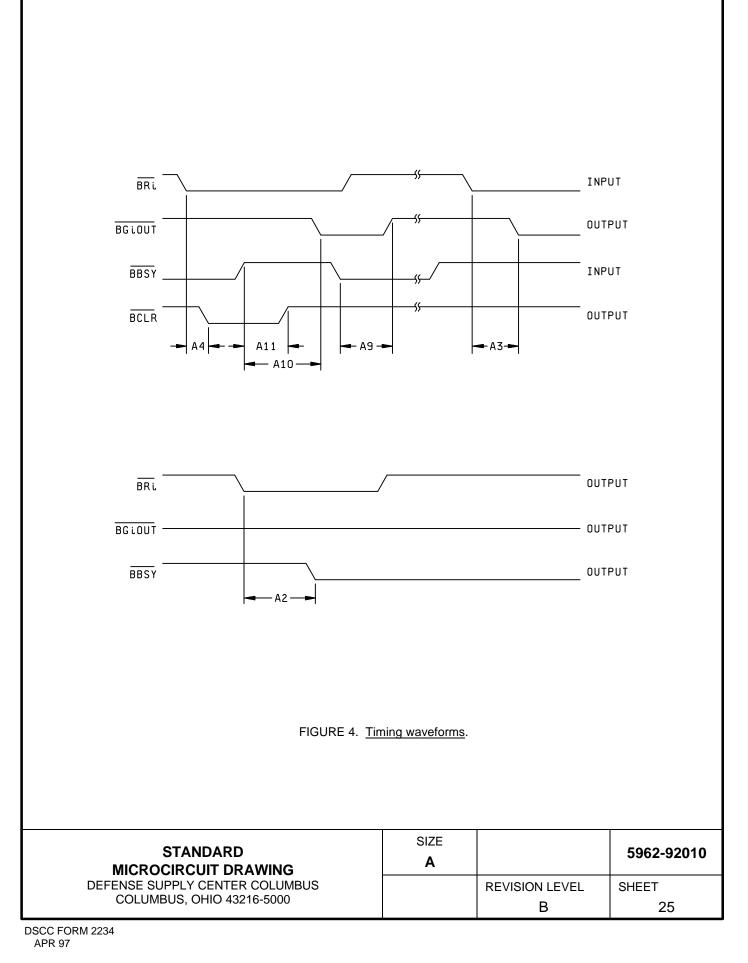

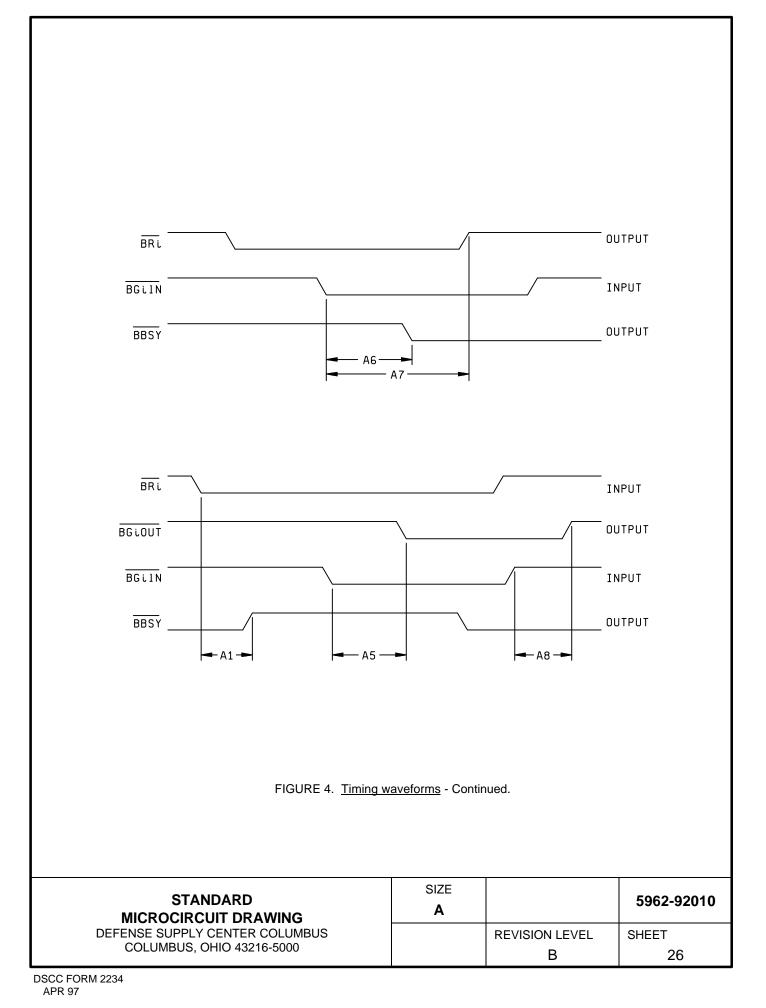

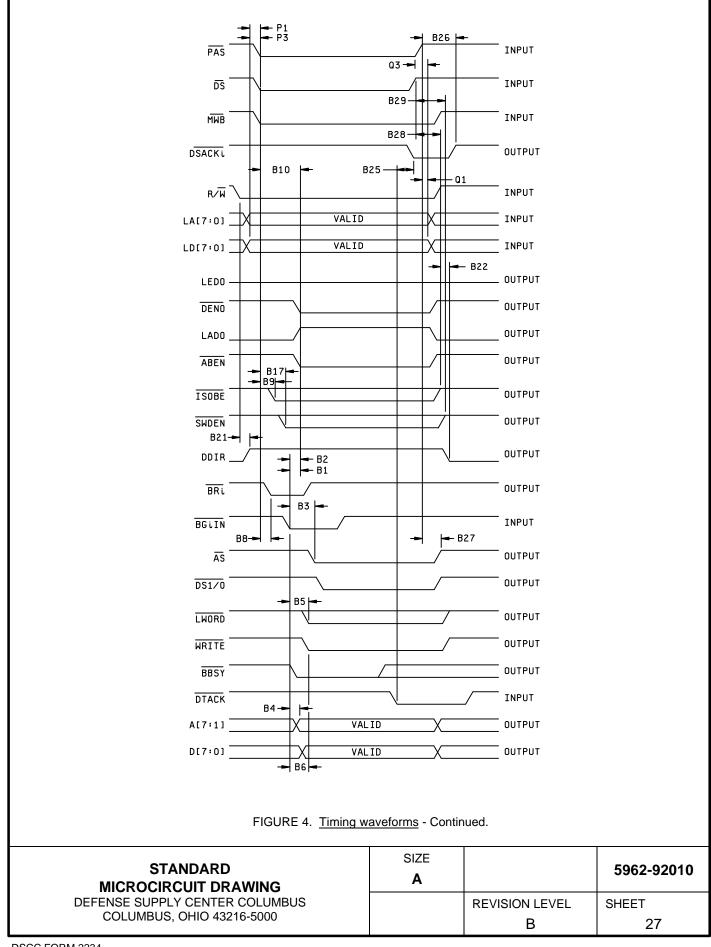

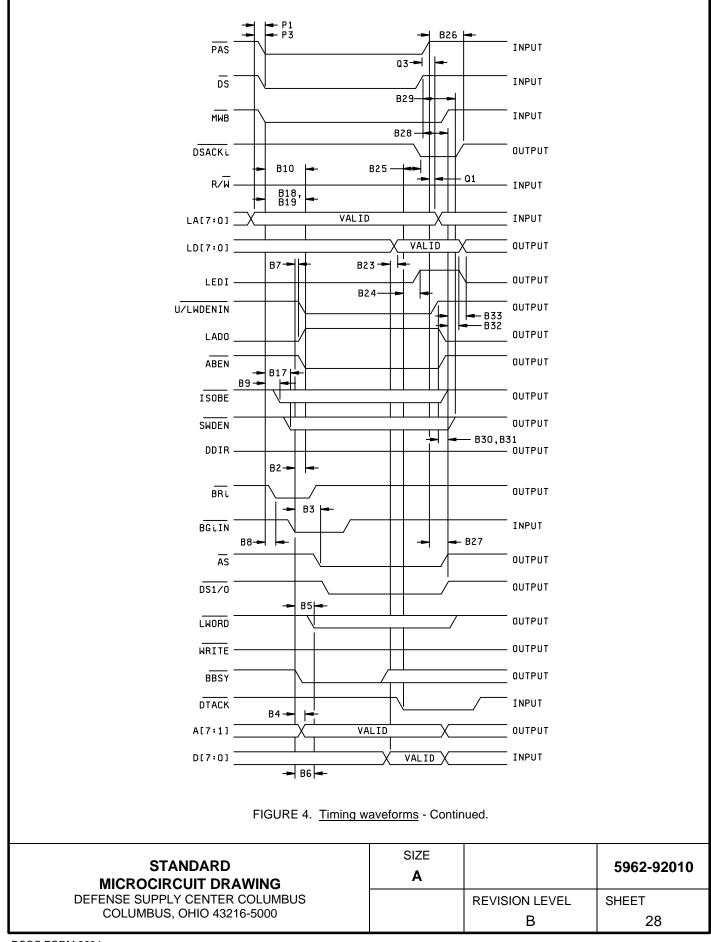

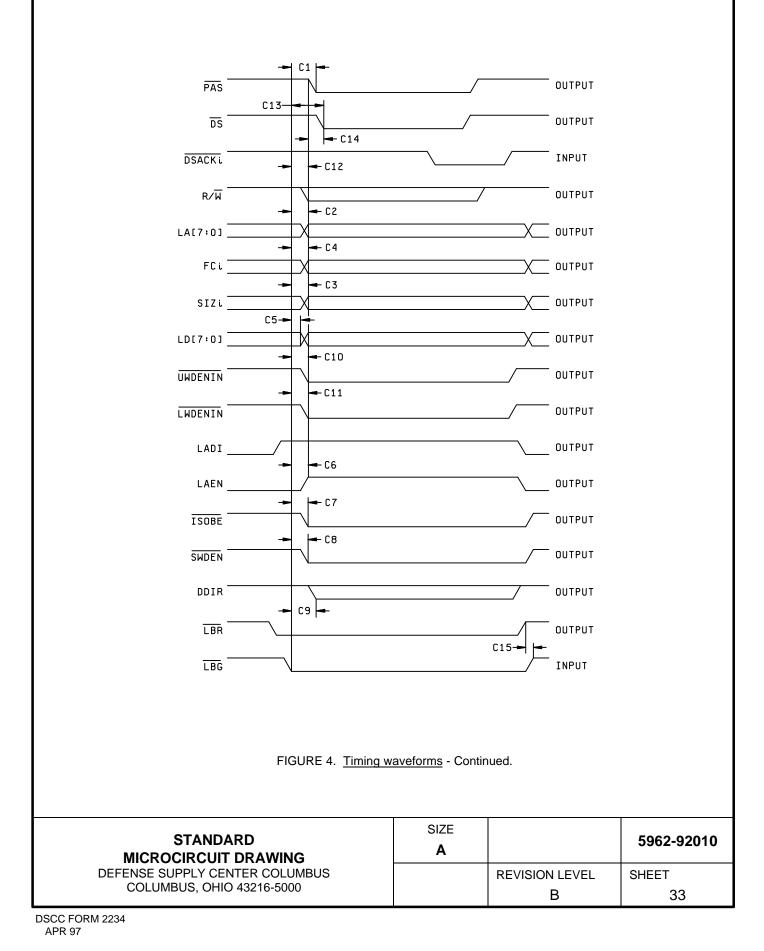

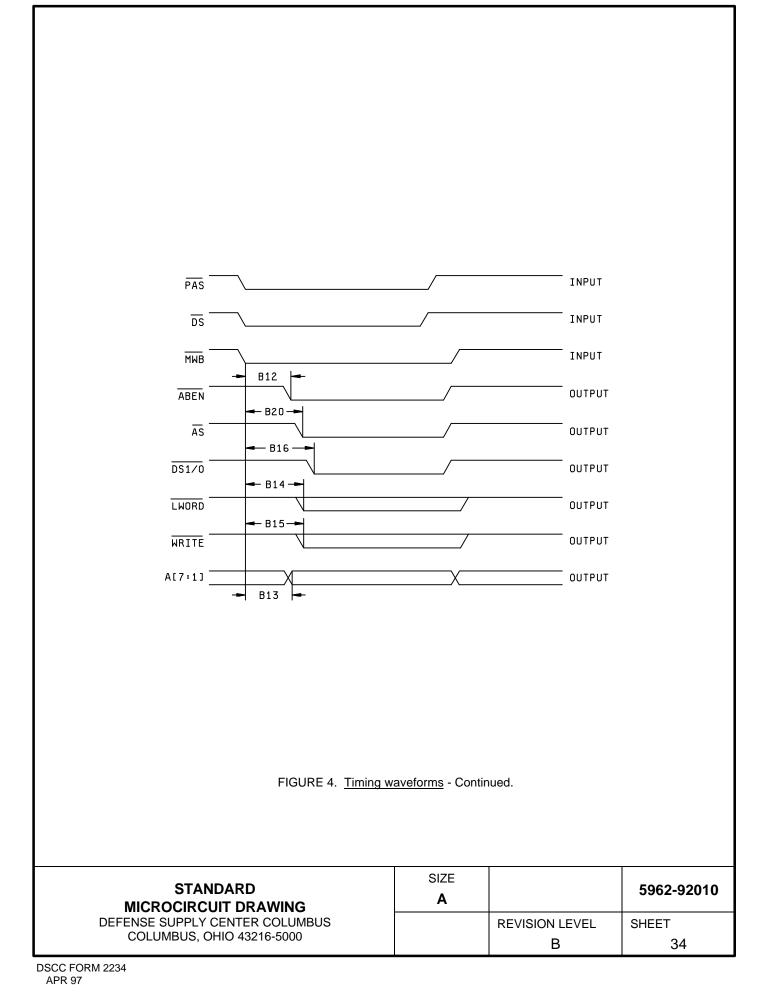

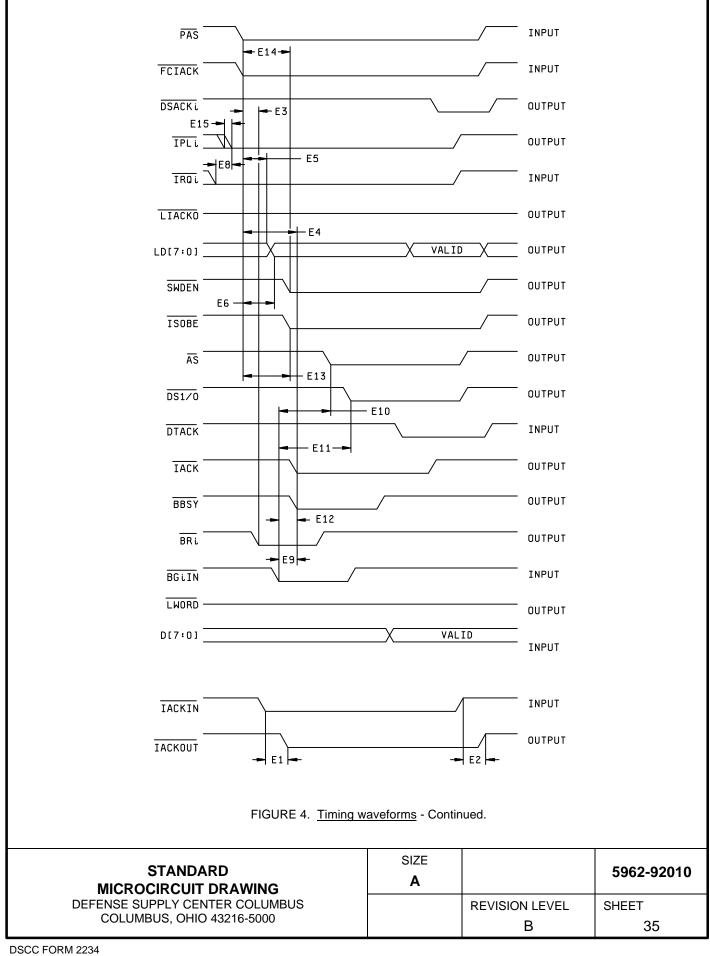

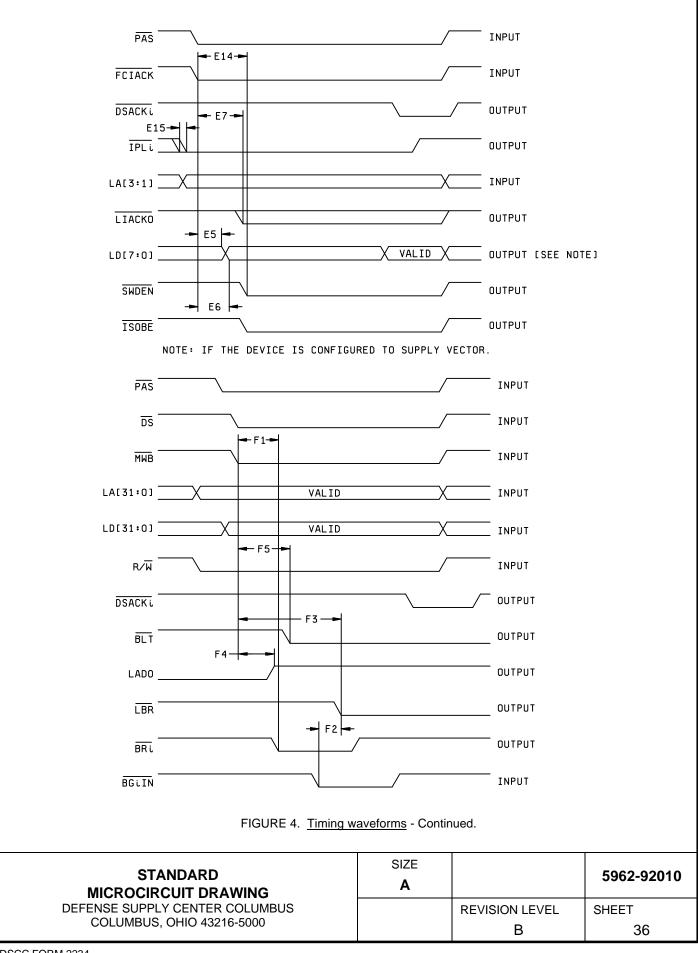

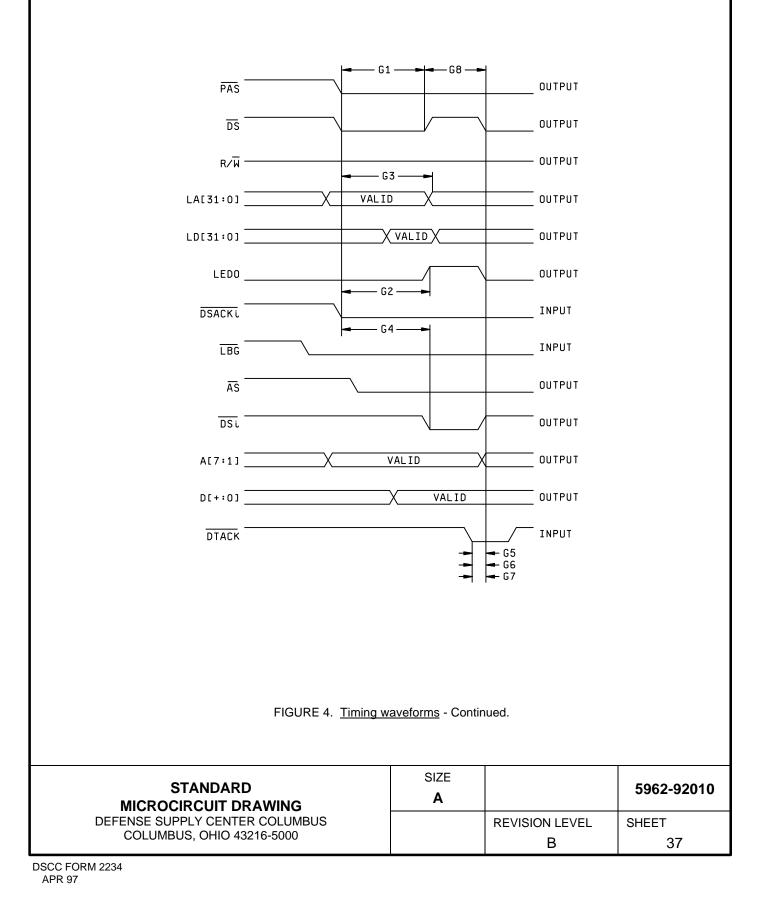

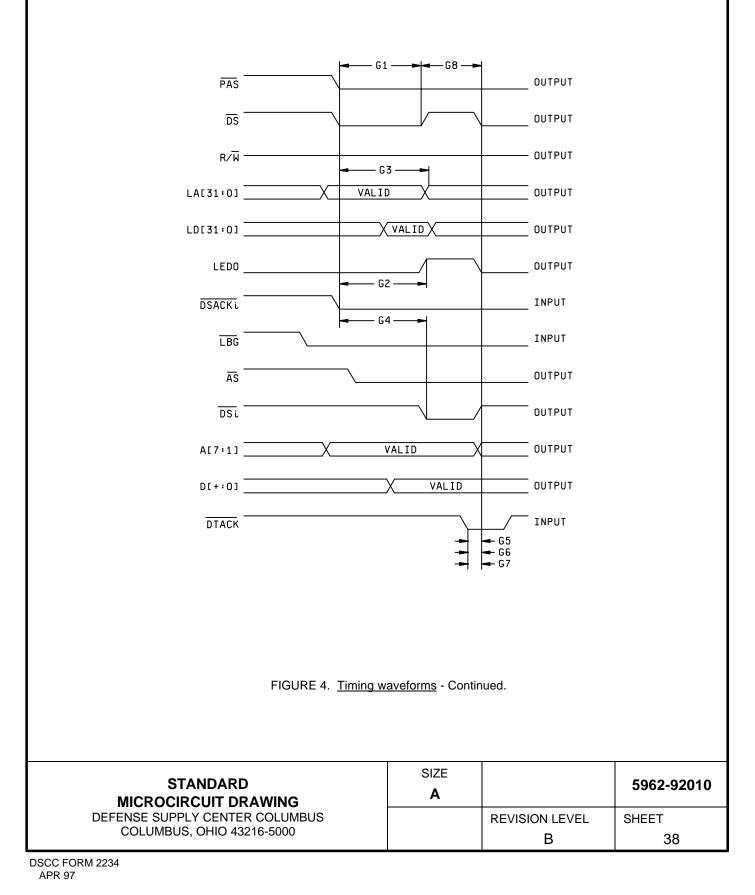

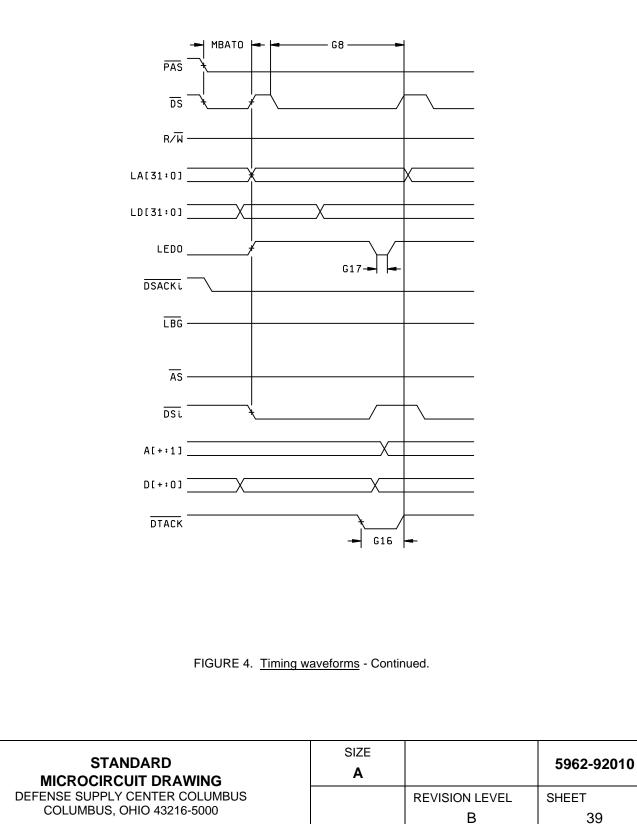

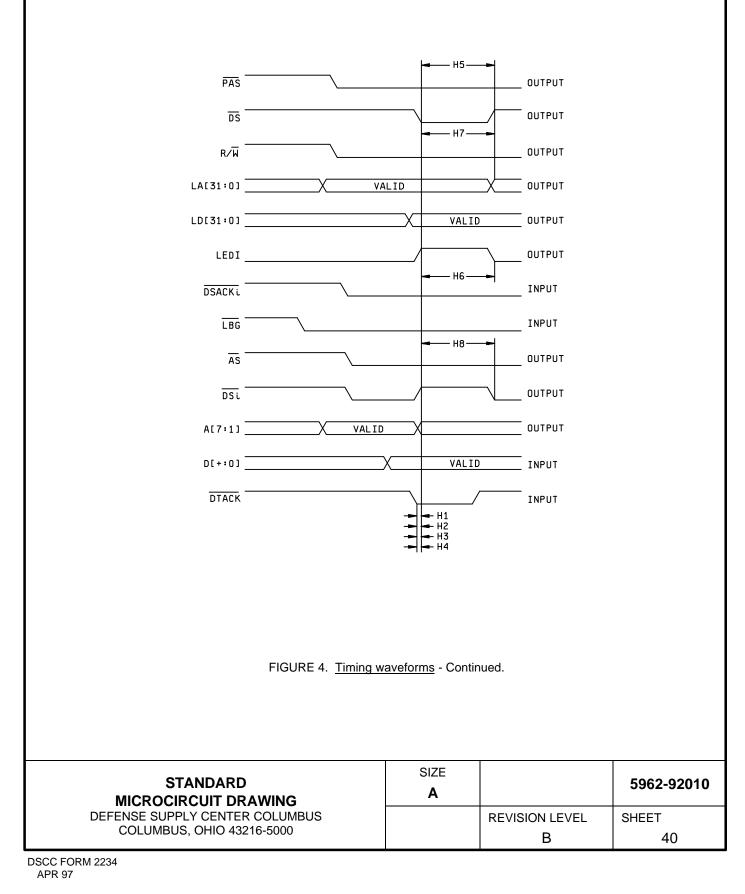

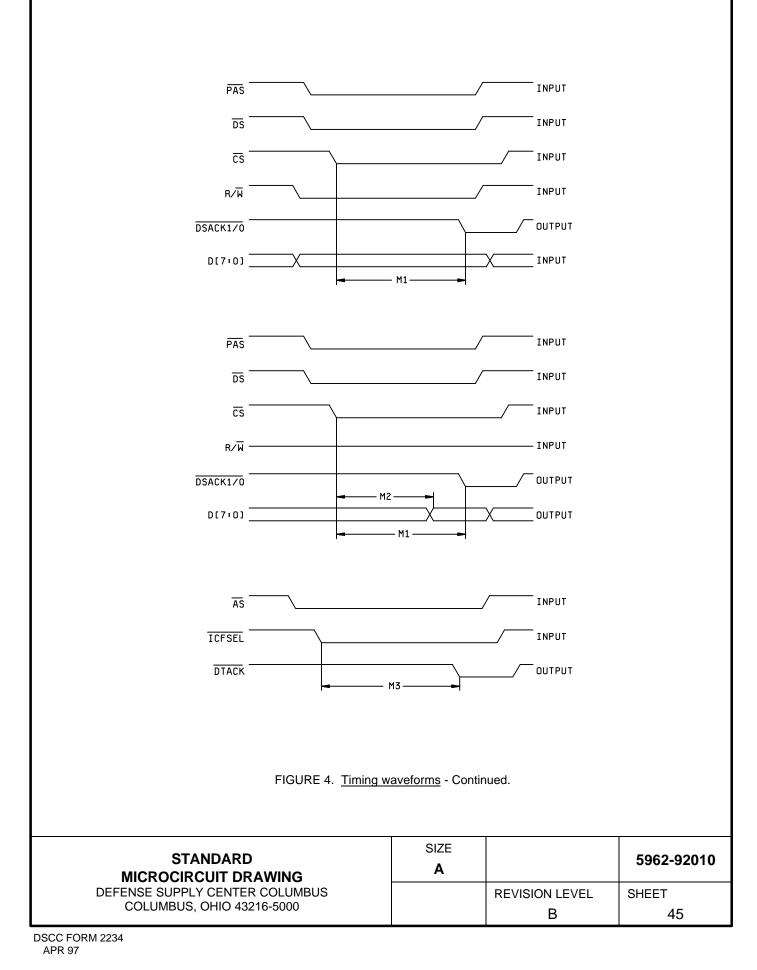

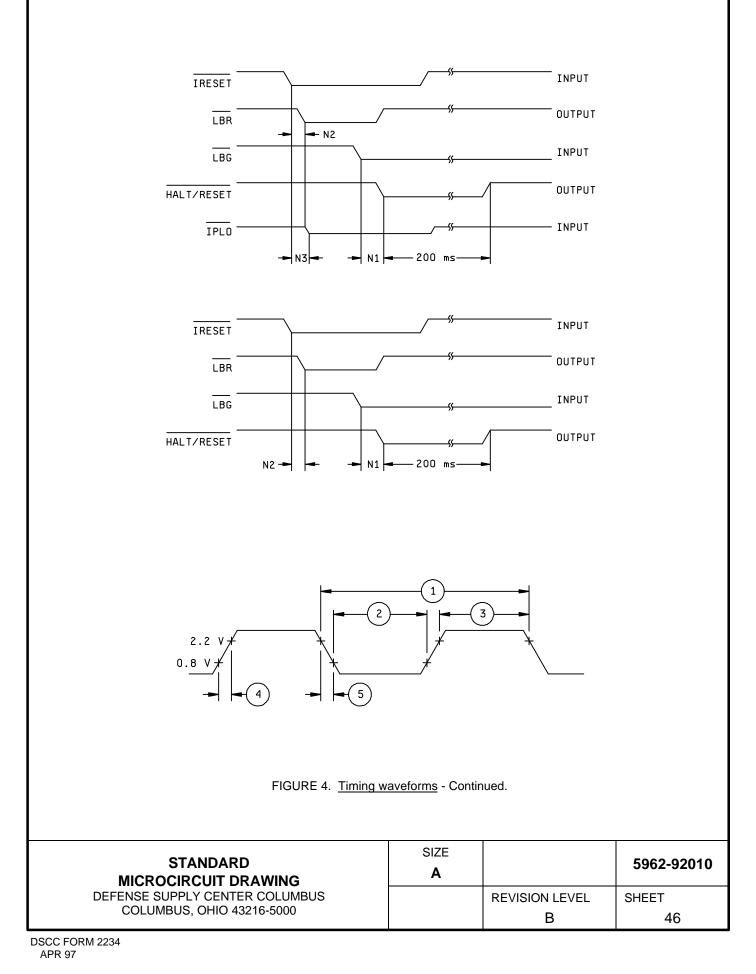

3.2.4 <u>Timing waveforms</u>. The timimg waveforms shall be as specified on figure 4.

3.2.5 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-92010 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |           | B              | 4          |

3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-PRF-38535, appendix A.

3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-PRF-38535, appendix A).

# 4. QUALITY ASSURANCE PROVISIONS

4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-92010 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |           | B              | 5          |

|                               |                 | 1                                                                                                                                                                    |                                  | 1                    |                |                      |            | -    |

|-------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------|----------------|----------------------|------------|------|

| Test                          | Symbol          |                                                                                                                                                                      | ditions <u>1</u> /               | Group A<br>subgroups | Device<br>type | Lim                  | it         | Unit |

|                               |                 | $\label{eq:constraint} \begin{array}{l} -55^\circ C \leq T_C \leq +125^\circ C \\ 4.5 \ V \leq V_{CC} \leq 5.5 \ V \\ \text{unless otherwise specified} \end{array}$ |                                  | Subgroups            | type           | Min                  | Max        |      |

| Input low voltage             | VIL             |                                                                                                                                                                      |                                  | 1, 2, 3              | All            |                      | 0.8        | V    |

| Input high voltage            | VIH             |                                                                                                                                                                      |                                  | 1, 2, 3              | All            | 2.0                  |            |      |

| Output low voltage            | V <sub>OL</sub> | $V_{CC} = MIN, I_{OL} = 8 \text{ mA} \ \underline{2}/$<br>$V_{CC} = MIN, I_{OL} = 48 \text{ mA} \ \underline{3}/$                                                    |                                  | 1, 2, 3              | All            |                      | 0.6        | V    |

|                               |                 |                                                                                                                                                                      |                                  |                      |                |                      | 0.6        |      |

| Output high voltage           | V <sub>OH</sub> | $V_{CC} = MIN, I_{CC}$                                                                                                                                               | <sub>он</sub> = -3 mA <u>3</u> / | 1, 2, 3              | All            | 2.4                  |            | V    |

|                               |                 | $V_{CC} = MIN, I_{OH} = -8 \text{ mA}  \underline{2}/$                                                                                                               |                                  |                      |                | 2.4                  |            |      |

| Input leakage current         | I <sub>IL</sub> | $V_{CC} = MAX$ $0.0 \ V \le V_{IN} \le V_{CC}$                                                                                                                       |                                  | 1, 2, 3              | All            | -10                  | +10        | μA   |

|                               |                 |                                                                                                                                                                      |                                  |                      |                |                      |            |      |

| Output leakage current        | ILO             | $V_{CC}$ = MAX, VMEbus pins<br>0.6 V $\leq V_{OUT} \leq 2.4$ V<br>$V_{CC}$ = MAX, other pins                                                                         |                                  | 1, 2, 3              | All            | -10                  | +10<br>+10 | μΑ   |

| (All output pins disabled)    |                 |                                                                                                                                                                      |                                  |                      |                |                      |            |      |

|                               |                 |                                                                                                                                                                      |                                  |                      |                | -10                  |            |      |

|                               |                 | $0.0 \ V \leq V_{OUT}$                                                                                                                                               | ≤ V <sub>CC</sub>                |                      |                |                      |            |      |

| Input clamp voltage           | V <sub>IK</sub> | $V_{CC} = MIN$                                                                                                                                                       | I <sub>IN</sub> = -18 mA         | 1, 2, 3              | All            |                      | -1.2       | V    |

|                               |                 |                                                                                                                                                                      | I <sub>IN</sub> = 18 mA          |                      |                | V <sub>CC</sub> +1.2 |            |      |

| Power supply current          | I <sub>CC</sub> | $V_{CC} = 5.5 V$                                                                                                                                                     |                                  | 1, 2, 3              | All            |                      | 150        | mA   |

|                               |                 | $V_{IN} = 0.0 V, 5$                                                                                                                                                  | 5.5 V                            |                      |                |                      |            |      |

| Input capacitance <u>4</u> /  | CIN             | $V_{CC} = 5.0 V$                                                                                                                                                     |                                  | 4                    | All            |                      | 10         | pF   |

| Output capacitance <u>4</u> / | COUT            | T <sub>C</sub> = 25°C, f<br>See 4.4.1c                                                                                                                               | = 1 MHZ                          |                      |                |                      | 15         |      |

| Functional testing            |                 | See 4.4.1b                                                                                                                                                           |                                  | 7, 8                 | All            |                      |            |      |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-92010 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |           | В              | 6          |

|                                 | TABLE I.         | Electrical performance char                                                            | acteristics -   | Conti | nued.          |        |            |      |

|---------------------------------|------------------|----------------------------------------------------------------------------------------|-----------------|-------|----------------|--------|------------|------|

| Test                            | Symbol           | Conditions $1/$<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +125°C                           | Group<br>subgro |       | Device<br>type | Li     | mit        | Unit |

|                                 |                  | $4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}$ unless otherwise specifie | d               |       |                | Min    | Max        |      |

| BRi[0] to BBSY[H] 5/            | t <sub>A1</sub>  | Arbitration signals                                                                    | 9, 10,          | 11    | All            | 2.5T+4 | 3T+31.5    | ns   |

| BRi[0] to BBSY[L] 6/            | t <sub>A2</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3T+7   | 3.5T+35    | ns   |

| BRi[0] to BGiOUT[L] 6/          | t <sub>A3</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3T+3   | 4T+28      | ns   |

| BRi[0] to BCLR[L]               | t <sub>A4</sub>  |                                                                                        | 9, 10,          | 11    | All            | 2      | 19         | ns   |

| BGiIN[0] TO BGiOUT[L]           | t <sub>A5</sub>  |                                                                                        | 9, 10,          | 11    | All            | 2      | 20         | ns   |

| BGilN[0] to BBSY[L] 7/          | t <sub>A6</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3      | 25         | ns   |

| BGilN[0] to BRi[H] 7/           | t <sub>A7</sub>  |                                                                                        | 9, 10,          | 11    | All            | 4      | 3T+31      | ns   |

| BGilN[1] to BGiOUT[H]           | t <sub>A8</sub>  |                                                                                        | 9, 10,          | 11    | All            | 2      | 23         | ns   |

| BBSY[0] to BGiOUT[H] 6/         | t <sub>A9</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3      | 24         | ns   |

| BBSY[1] to BGiOUT[L]            | t <sub>A10</sub> |                                                                                        | 9, 10,          | 11    | All            | 3T+3   | 4T+29      | ns   |

| BBSY[1] to BCLR[H]              | t <sub>A11</sub> |                                                                                        | 9, 10,          | 11    | All            | 1T+3   | 2T+27      | ns   |

| BGilN[0] to DENO[L] 7/ 8/       | t <sub>B1</sub>  | Master access signals                                                                  | 9, 10,          | 11    | All            | 6      | 3T+42      | ns   |

| BGilN[0] to LADO[H] 7/          | t <sub>B2</sub>  |                                                                                        | 9, 10,          | 11    | All            | 12     | 3T+67      | ns   |

| BGilN[0] to AS[L] 7/            | t <sub>B3</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3T+4   | 6T+31      | ns   |

| BGilN[0] to A[7:1] valid        | t <sub>B4</sub>  |                                                                                        | 9, 10,          | 11    | All            | 5      | 3T+37      | ns   |

| <u>7</u> /                      |                  |                                                                                        |                 |       |                |        |            |      |

| BGilN[0] to LWORD[H/L]          | t <sub>B5</sub>  |                                                                                        | 9, 10,          | 11    | All            | 5      | 3T+37      | ns   |

| <u>7</u> /                      |                  |                                                                                        |                 |       |                |        |            |      |

| BGilN[0] to WRITE[H/L]          | t <sub>B6</sub>  |                                                                                        | 9, 10,          | 11    | All            | 5      | 3T+37      | ns   |

| <u>7</u> /                      |                  |                                                                                        |                 |       |                |        |            |      |

| BGilN[0] to ABEN[L] 7/          | t <sub>B7</sub>  |                                                                                        | 9, 10,          | 11    | All            | 6      | 3T+38      | ns   |

| PAS[0] & MWB[0] to BRi[L]       | t <sub>B8</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3      | 24         | ns   |

| PAS[0] & MWB[0] to<br>ISOBE[L]  | t <sub>B9</sub>  |                                                                                        | 9, 10,          | 11    | All            | 3      | 25         | ns   |

| PAS[0] & MWB[0] to              | t <sub>B10</sub> | -                                                                                      | 9, 10,          | 11    | All            | 12     | 68         | ns   |

| LADO[H]                         |                  |                                                                                        | , ,             |       |                |        |            |      |

| PAS[0] & MWB[0] to BBSY[L]      | t <sub>B11</sub> |                                                                                        | 9, 10,          | 11    | All            | 5      | 36         | ns   |

| <u>9</u> /                      |                  |                                                                                        |                 |       |                |        |            |      |

| See footnotes at end of table.  |                  |                                                                                        |                 |       |                |        |            |      |

| STAN<br>MICROCIRCU              | DARD             | VING                                                                                   | SIZE<br>A       |       |                |        | 5962-92    | 2010 |

| DEFENSE SUPPLY (<br>COLUMBUS, O | CENTER C         | OLUMBUS                                                                                |                 | REV   | ISION LE<br>B  | VEL    | SHEET<br>7 |      |

|                                         | TABLE I.         | Electrical performance charac                                                                          | <u>steristics</u> - 0 | Continued.   |        |         |      |

|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------|-----------------------|--------------|--------|---------|------|

| Test                                    | Symbol           | $\begin{array}{l} Conditions  \underline{1}/\\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \end{array}$ | Group /<br>subgrou    |              | Li     | imit    | Unit |

|                                         |                  | $\begin{array}{l} 4.5 \ V \leq V_{CC} \leq 5.5 \ V \\ \text{unless otherwise specified} \end{array}$   |                       |              | Min    | Max     |      |

| PAS[0] & MWB[0] to ABEN[L]              | t <sub>B12</sub> | Master access signals                                                                                  | 9, 10, 1              | 1 All        | 1.5T+6 | 2.5T+41 | ns   |

| <u>9</u> /                              |                  | -                                                                                                      |                       |              |        |         |      |

| PAS[0] & MWB[0] to A(7:1)<br><u>9</u> / | t <sub>B13</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 1.5T+5 | 2.5T+41 | ns   |

| PAS[0] & MWB[0] to                      | t <sub>B14</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 1.5T+5 | 2.5T+41 | ns   |

| LWORD[H/L] <u>9</u> /                   |                  |                                                                                                        |                       |              |        |         |      |

| PAS[0] & MWB[0] to                      | t <sub>B15</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 1.5T+5 | 2.5T+41 | ns   |

| WRITE[H/L] <u>9</u> /                   |                  |                                                                                                        |                       |              |        |         |      |

| PAS[0] & MWB[0] & DS[0]                 | t <sub>B16</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 4.5T+9 | 5.5T+57 | ns   |

| to DS1/0[L] <u>9</u> /                  |                  |                                                                                                        |                       |              |        |         |      |

| PAS[0] & MWB[0] to<br>SWDEN[L]          | t <sub>B17</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 3      | 14      | ns   |

| PAS[0] & MWB[0] to                      | t <sub>B18</sub> | -                                                                                                      | 9, 10, 1              | 1 All        | 2      | 22      | ns   |

| LWDENIN[L] <u>10</u> /                  |                  |                                                                                                        |                       |              |        |         |      |

| PAS[0] & MWB[0] to                      | t <sub>B19</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 3      | 23      | ns   |

| UWDENIN[L] <u>10</u> /                  |                  |                                                                                                        |                       |              |        |         |      |

| PAS[0] & MWB[0] & DS[0]                 | t <sub>B20</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 4.5T+5 | 5.5T+32 | ns   |

| to AS[L] <u>9</u> /                     |                  |                                                                                                        |                       |              |        |         |      |

| R/W[0]to DDIR[H] <u>8</u> /             | t <sub>B21</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 2      | 25      | ns   |

| R/W[1] to DDIR[L] <u>8</u> /            | t <sub>B22</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 1      | 15      | ns   |

| D(7:0) to LD(7:0) valid <u>10</u> /     | t <sub>B23</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 2      | 22      | ns   |

| DTACK[0] to LEDI[H] <u>10</u> /         | t <sub>B24</sub> | -                                                                                                      | 9, 10, 1              | 1 All        | 3T+4   | 4T+32   | ns   |

| DTACK[0] to DSACKi[L]                   | t <sub>B25</sub> |                                                                                                        | 9, 10, 1              | , 10, 11 All | 3      | 36      | ns   |

| PAS[1] & DS[1] to                       | t <sub>B26</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 2      | 27      | ns   |

| DSACKi[H]                               |                  |                                                                                                        |                       |              |        |         |      |

| PAS[1] to AS[H]                         | t <sub>B27</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 5      | 41      | ns   |

| DS[1] to ISOBE[H]                       | t <sub>B28</sub> |                                                                                                        | 9, 10, 1              | 1 All        | 3      | 26      | ns   |

| DS[1] to SWDEN[H]                       | t <sub>B29</sub> | 1                                                                                                      | 9, 10, 1              | 1 All        | 2      | 13      | ns   |

| DS[1] to UWDENIN[H]                     | t <sub>B30</sub> | 1                                                                                                      | 9, 10, 1              | 1 All        | 2      | 22      | ns   |

| <u>10</u> /                             |                  |                                                                                                        |                       |              |        |         |      |

| See footnotes at end of table.          |                  |                                                                                                        |                       |              |        |         |      |

| STAN<br>MICROCIRC                       |                  |                                                                                                        | ize<br>A              |              |        | 5962-92 | 2010 |

| DEFENSE SUPPLY                          | CENTER C         | OLUMBUS                                                                                                |                       | REVISION LE  | EVEL   | SHEET   |      |

| COLUMBUS, C                             | HIO 43216        | -5000                                                                                                  |                       | В            |        | 8       |      |

| Test                                                 | Symbol           | Conditions $\frac{1}{-55^{\circ}C} \le T_{C} \le +125^{\circ}C$                       | Group A<br>subgroups | Device<br>type | Li   | mit   | Unit |

|------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|----------------------|----------------|------|-------|------|

|                                                      |                  | $4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$ unless otherwise specified |                      | 51             | Min  | Max   | -    |

| DS[1] to LWDENIN[H]<br><u>10</u> /                   | t <sub>B31</sub> | Master access signals                                                                 | 9, 10, 11            | All            | 2    | 22    | ns   |

| DS[1] to LD(7:0) invalid                             | t <sub>B32</sub> | -                                                                                     | 9, 10, 11            | All            | 2    | 28    | ns   |

| <u>10/</u><br>DS[1] to LD(7:0) Hi-Z<br><u>10</u> /   | t <sub>B33</sub> |                                                                                       | 9, 10, 11            | All            | 2    | 28    | ns   |

| DS[0] to DSACKi[L] <u>11</u> /                       | t <sub>B34</sub> |                                                                                       | 9, 10, 11            | All            | 5    | T+35  | ns   |

| DS[0] to LADO[H] <u>11</u> /                         | t <sub>B35</sub> |                                                                                       | 9, 10, 11            | All            | 7    | 43    | ns   |

| DS[0] to LEDO[H] <u>11</u> /                         | t <sub>B36</sub> |                                                                                       | 9, 10, 11            | All            | 3    | T+20  | ns   |

| LBG[0] to PAS[L]                                     | t <sub>C1</sub>  | Local bus timing signals                                                              | 9, 10, 11            | All            | 5T+5 | 6T+44 | ns   |

| LBG[0] to LA(7:0) valid                              | t <sub>C2</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+6 | 4T+46 | ns   |

| LBG[0] to SIZ(1:0) valid                             | t <sub>C3</sub>  |                                                                                       | 9, 10, 11            | All            | 1T+2 | 2T+28 | ns   |

| LBG[0] to FC(2:1) valid                              | t <sub>C4</sub>  |                                                                                       | 9, 10, 11            | All            | 1T+2 | 2T+27 | ns   |

| LBG[0] to LD(7:0) driven <u>8</u> /                  | t <sub>C5</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+7 | 4T+48 | ns   |

| LBG[0] to LAEN[H]                                    | t <sub>C6</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+8 | 4T+48 | ns   |

| LBG[0] to ISOBE[L]                                   | t <sub>C7</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+7 | 4T+42 | ns   |

| LBG[0] to SWDEN[L]                                   | t <sub>C8</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+7 | 4T+45 | ns   |

| LBG[0] to DDIR[H] <u>8</u> /                         | t <sub>C9</sub>  |                                                                                       | 9, 10, 11            | All            | 3T+7 | 4T+42 | ns   |

| LBG[0] to UWDENIN[L] 8/                              | t <sub>C10</sub> | -                                                                                     | 9, 10, 11            | All            | 3T+6 | 4T+42 | ns   |

| LBG[0] to LWDENIN[L] 8/                              | t <sub>C11</sub> |                                                                                       | 9, 10, 11            | All            | 3T+5 | 4T+38 | ns   |

| LBG[0] & DS1/0[0] &<br>WRITE[0] to R/W[L] <u>8</u> / | t <sub>C12</sub> | -                                                                                     | 9, 10, 11            | All            | 3T+7 | 4T+47 | ns   |

| LBG[0] & DS1/0[0] to DS[L]                           | t <sub>C13</sub> |                                                                                       | 9, 10, 11            | All            | 5T+7 | 6T+56 | ns   |

| PAS[0] to DS[L] <u>12</u> /                          | t <sub>C14</sub> | 1                                                                                     | 9, 10, 11            | All            | 0    | 15    | ns   |

| LBR[H] to LBG[1] <u>4</u> /                          | t <sub>C15</sub> |                                                                                       | 9, 10, 11            | All            |      | Т     | ns   |

| See footnotes at end of table.                       |                  |                                                                                       |                      |                |      |       |      |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-92010 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |           | B              | 9          |

| Test                                       | Symbol           | Conditions $\frac{1}{-55^{\circ}C} \le T_{C} \le +125^{\circ}C$            | Group A<br>subgroups | Device<br>type | Li    | mit              | Unit |

|--------------------------------------------|------------------|----------------------------------------------------------------------------|----------------------|----------------|-------|------------------|------|

|                                            |                  | $4.5 \text{ V} \le V_{CC} \le 5.5 \text{ V}$<br>unless otherwise specified | Subgroups            | type           | Min   | Max              | -    |

| SLSELi[0] & AS[0] to LBR[L]                | t <sub>D1</sub>  | Slave access signals                                                       | 9, 10, 11            | All            | 6     | 40               | ns   |

| SLSELi[0] & AS[0] & DS1/0<br>to LADI[H]    | t <sub>D2</sub>  |                                                                            | 9, 10, 11            | All            | 4     | 29               | ns   |

| LD(7:0) to D(7:0) <u>10</u> /              | t <sub>D3</sub>  |                                                                            | 9, 10, 11            | All            | 2     | 18               | ns   |

| DSACKI[0] to LEDO[H] <u>10</u> /           | t <sub>D4</sub>  | -                                                                          | 9, 10, 11            | All            | SAT+6 | SAT+39<br>+ 0.5T | ns   |

| DSACKI[0] to DTACK[L]                      | t <sub>D5</sub>  |                                                                            | 9, 10, 11            | All            | SAT+9 | SAT+53<br>+ 0.5T | ns   |

| DS1/0[0] to DTACK[L]                       | t <sub>D6</sub>  | Slave access signals                                                       | 9,10,11              | All            | 2T+4  | 3.5T+33          | ns   |

| DS1/0[0] to LEDI[H]                        | t <sub>D7</sub>  | Slave write post only                                                      | 9, 10, 11            | All            | 8     | 47               | ns   |

| AS[1] to LA(7:0), R/W invalid              | t <sub>D8</sub>  | Slave access signals                                                       | 9, 10, 11            | All            | 4     | 55               | ns   |

| AS[1] to LA(7:0), R/W Hi-Z                 | t <sub>D9</sub>  |                                                                            | 9, 10, 11            | All            | 4     | 55               | ns   |

| AS[1] to FC2/1 invalid                     | t <sub>D10</sub> |                                                                            | 9, 10, 11            | All            | 8     | 56               | ns   |

| AS[1] & DSACKi[1] to FC2/1<br>Hi-Z         | t <sub>D11</sub> |                                                                            | 9, 10, 11            | All            | 8     | 56               | ns   |

| AS[1] to SIZ1/0 invalid                    | t <sub>D12</sub> |                                                                            | 9, 10, 11            | All            | 6     | 37               | ns   |

| As[1] & DSACKi[1] to<br>SIZ1/0, Hi-Z       | t <sub>D13</sub> |                                                                            | 9, 10, 11            | All            | 2     | 1T+24            | ns   |

| AS[1] to ISOBE[H]                          | t <sub>D14</sub> | -                                                                          | 9, 10, 11            | All            | 5     | 34               | ns   |

| AS[1] to SWDEN[H]                          | t <sub>D15</sub> | -                                                                          | 9, 10, 11            | All            | 3     | 27               | ns   |

| AS[1] to UWDENIN[H] 8/                     | t <sub>D16</sub> | -                                                                          | 9, 10, 11            | All            | 4     | 30               | ns   |

| AS[1] to LWDENIN[H] 8/                     | t <sub>D17</sub> | -                                                                          | 9, 10, 11            | All            | 4     | 30               | ns   |

| AS[1] & DSACKi[1] to LBR[H]                | t <sub>D18</sub> | -                                                                          | 9, 10, 11            | All            | 4     | 30               | ns   |

| AS[1] to LAEN[L]                           | t <sub>D19</sub> |                                                                            | 9, 10, 11            | All            | 7     | 56               | ns   |

| DS1/0[1] to LD(7:0) invalid<br><u>8</u> /  | t <sub>D20</sub> |                                                                            | 9, 10, 11            | All            | 2     | 39               | ns   |

| <br>DS1/0[1] to LD(7:0) Hi-Z<br><u>8</u> / | t <sub>D21</sub> |                                                                            | 9, 10, 11            | All            | 2     | 39               | ns   |

| See footnotes at end of table.             | _                |                                                                            | _                    |                |       |                  |      |

| STAN<br>MICROCIRCU                         | DARD<br>JIT DRAV |                                                                            | ZE<br>A              |                |       | 5962-92          | 2010 |

|                                            |                  |                                                                            | RE                   | VISION LE      | VEL   | SHEET            |      |

В

10

COLUMBUS, OHIO 43216-5000

| Test                                                              | Symbol           | $\begin{array}{l} Conditions  \underline{1}/\\ -55^{\circ}C \leq T_{C} \leq +125 \end{array}$ |           |     | Device<br>type | Li     | mit              | Unit |

|-------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|-----------|-----|----------------|--------|------------------|------|

|                                                                   |                  | $4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5$ unless otherwise spe                         |           |     |                | Min    | Max              |      |

| DSACKi[0] to PAS[H]                                               | t <sub>D22</sub> | Slave access signals                                                                          | 9, 10,    | 11  | All            | SAT+8  | SAT+56<br>+ 0.5T | ns   |

| DSACKi[0] to DS[H]                                                | t <sub>D23</sub> |                                                                                               | 9, 10,    | 11  | All            | SAT+7  | SAT+48<br>+ 0.5T | ns   |

| DSACKi[1] to DTACK[H]                                             | t <sub>D24</sub> |                                                                                               | 9, 10,    | 11  | All            | 3      | 35               | ns   |

| IACKIN[0] to IACKOUT[L]                                           | t <sub>E1</sub>  | Interrupt signals                                                                             | 9, 10,    | 11  | All            | 2      | 18               | ns   |

| IACKIN[1] to IACKOUT[H]                                           | t <sub>E2</sub>  |                                                                                               | 9, 10,    | 11  | All            | 2      | 20               | ns   |

| FCIACK[0] & PAS[0] to<br>BRi[L]                                   | t <sub>E3</sub>  |                                                                                               | 9, 10,    | 11  | All            | 5T+7   | 6T+48            | ns   |

| FCIACK[0] & PAS[0] to<br>IACK[L] <u>9</u> /                       | t <sub>E4</sub>  |                                                                                               | 9, 10,    | 11  | All            | 7.5T+6 | 8.5T+39          | ns   |

| FCIACK[0] & PAS[0] to<br>LD(7:0) driven <u>13</u> /               | t <sub>E5</sub>  |                                                                                               | 9, 10,    | 11  | All            | 5T+10  | 6T+57            | ns   |

| FCIACK[0] & PAS[0] to<br>LD(7:0) valid <u>14</u> /                | t <sub>E6</sub>  | -                                                                                             | 9, 10,    | 11  | All            | 9T+4   | 10T+37           | ns   |

| FCIACK[0] & PAS[0] to<br>LIACKO[L] <u>15</u> /                    | t <sub>E7</sub>  |                                                                                               | 9, 10,    | 11  | All            | 5T+5   | 6T+36            | ns   |

| IRQi[0] to IPL                                                    | t <sub>E8</sub>  |                                                                                               | 9, 10,    | 11  | All            | 4      | 37               | ns   |

| BGiIN[0] to BBSY[L]                                               | t <sub>E9</sub>  |                                                                                               | 9, 10,    | 11  | All            | 5      | 36               | ns   |

| BGiiN[0] to AS[L]                                                 | t <sub>E10</sub> |                                                                                               | 9, 10,    | 11  | All            | 3T+4   | 4T+31            | ns   |

| BGiIN[0] to DS1/0[L]                                              | t <sub>E11</sub> |                                                                                               | 9, 10,    | 11  | All            | 3T+8   | 4T+55            | ns   |

| BGiIN[0] to IACK[L] 14/                                           | t <sub>E12</sub> |                                                                                               | 9, 10,    | 11  | All            | 44     |                  | ns   |

| PAS[0] to ISOBE[L]                                                | t <sub>E13</sub> |                                                                                               | 9, 10,    | 11  | All            | 5T+7   | 6T+44            | ns   |

| PAS[0] to SWDEN[L]                                                | t <sub>E14</sub> |                                                                                               | 9, 10,    | 11  | All            | 5T+6   | 6T+42            | ns   |

| IPLi to IPLi <u>4</u> / <u>12</u> /                               | t <sub>E15</sub> |                                                                                               | 9, 10,    | 11  | All            |        | 12               | ns   |

| MWB[0] & PAS[0] & DS[0]<br>to BRi[L]                              | t <sub>F1</sub>  | Master block transfer<br>with local DMA signals                                               | 9, 10,    | 11  | All            | T+5    | 2T+38            | ns   |

|                                                                   | t <sub>E2</sub>  | (Initiation cycle)                                                                            | 9, 10,    | 11  | All            | 4T+8   | 5T+50            | ns   |

| to BRi[L]<br>BGiIN[0] to LBR[L]<br>See footnotes at end of table. | t <sub>F2</sub>  | (initiation cycle)                                                                            | 9, 10,    | 11  | All            | 4T+8   | 5T+50            | n    |

| STAI<br>MICROCIRC                                                 |                  | VING                                                                                          | SIZE<br>A |     |                |        | 5962-92          | 2010 |

| DEFENSE SUPPLY                                                    |                  |                                                                                               |           | RE∖ | ISION LE       | VEL    | SHEET            |      |

| AII<br>AII<br>AII<br>AII<br>AII | Min<br>5T+8<br>T+6<br>T+4<br>MBAT0+7<br>MBAT0+6 | Max<br>6T+50<br>2T+39<br>2T+37<br>MBAT0+<br>0.5T+52               | ns<br>ns<br>ns<br>ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|-------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AII<br>AII<br>AII<br>AII        | T+6<br>T+4<br>MBAT0+7                           | 2T+39<br>2T+37<br>MBAT0+<br>0.5T+52                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All<br>All<br>All               | T+4<br>MBAT0+7                                  | 2T+37<br>MBAT0+<br>0.5T+52                                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All                             | MBAT0+7                                         | MBAT0+<br>0.5T+52                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| All                             |                                                 | 0.5T+52                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | MBAT0+6                                         |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| All                             |                                                 | MBAT0+<br>0.5T+40                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | MBAT0+T+<br>9                                   | MBAT0+<br>1.5T+40                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All                             | MBAT0+3T<br>+5                                  | MBAT0+<br>3.5T+42                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All                             | 6                                               | 38                                                                | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All                             | 9                                               | 56                                                                | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| All                             | 9                                               | 64                                                                | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 |                                                 |                                                                   | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | 1.5T-15                                         | 1.5T-4                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |