# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## MOS INTEGRATED CIRCUIT

μ**PD6450**

# 12 LINE × 24 COLUMN ON-SCREEN CHARACTER DISPLAY **CMOS LSI FOR VTR**

#### DESCRIPTION

The µPD6450 is on-screen character display CMOS LSI which is combined with microcomputers and used for VTR and video disks to display program reserved information, chapter numbers, etc. on monitor screens.

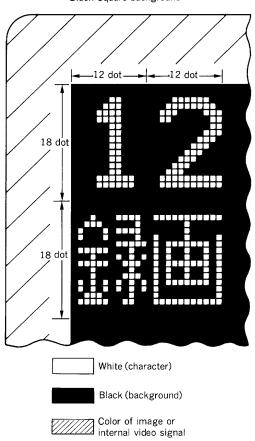

Character format is 12 x 18 dots, and one character enables displaying numbers kanji and hiragana. Since this LSI has builtin video switches, video signals can be input and output by composite video signals, and video signals can be generated internally so that characters can be displayed with no external signals.

NEC provides two standard types  $-\mu PD6450CX-002$  and  $\mu PD6450GT-102$ .

Using same characters, μPD6450CX-002 is 18-pin DIP and μPD6450GT-102 is a 20-pin SOP package.

#### **FEATURES**

Number of displayed character

: 12 lines 24 columns

Kinds of character

: 128 (ROM)

Character size

: 1 dot - 1H, 2H, 3H, or 4H

Dot matrix

: 12 x 18 dots - with no clearance between neighboring characters

Blinking ratio

: 1:1, 3:1, or 1:3

Input/Output of image signal Background

: Composite video signal

Internal video signals

: No background, black fringe, black square background, or black solid background : Characters can be displayed on internal simplified video signal (white, black, red,

green or blue) by commands. Internal video signal is noninterlaced video signal.

Mask pulse

Vertical direction for each row (This pulse is available with mask code option.)

Character signal output

: It is possible to output only character signal will mix with video signal. (This

function is available with mask code option.)

Interface with microcomputer

: 8-bit serial input format with BUSY signal

Power supply

: +5 V single power supply

Structure

: Low-power-consumption CMOS

#### ORDERING INFORMATION

| PART NUMBER   | PACKAGE                      |

|---------------|------------------------------|

| μPD6450CX-002 | 18-pin plastic DIP (300 mil) |

| μPD6450GT-102 | 20-pin plastic SOP (375 mil) |

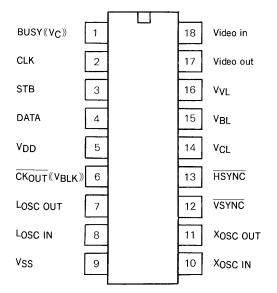

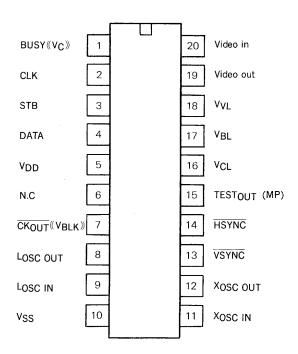

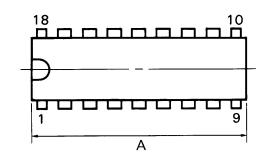

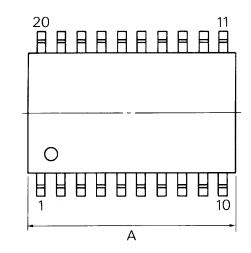

#### **CONNECTION DIAGRAM (Top View)**

#### (1) $\mu$ PD6450CX-002

#### (2) μPD6450GT-102

Note: This single bracket shows terminal arrangement for the mask code option when terminal 15 of  $\mu$ PD6450GT-xxx is used for mask pulse. And this double bracket shows terminals arrangement for the mask code option when terminal 1 is used for character signal output, terminal 6 of  $\mu$ PD6450CX-xxx and terminal 7 of  $\mu$ PD6450GT-xxx are used for blanking signal output.

It is possible to select 3 ways of mask code option with  $\mu PD6450CX$  and 4 ways of mask code option with  $\mu PD6450GT$  and select one way at the following table.

#### Mask Code Option Selection Table

|           | Combination of mask code option                | Selection posibility | Note                                                                                                                                                                         |

|-----------|------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Non mask pulse function and BUSY signal output | 0                    | The functions are similar to standard type. (terminal 1 : BUSY, terminal 6 : CK <sub>OUT</sub> )                                                                             |

| BD64E06V  | Mask pulse function and BUSY signal output     | ×                    | _                                                                                                                                                                            |

| μPD6450CX | Non mask pulse function and BUSY signal output | 0                    | All character signal and all blanking signal are outed at V $_{C}$ (terminal 1) and V $_{BLK}$ (terminal 6).                                                                 |

|           | Mask pulse function and BUSY signal output     | 0                    | Character signal and blanking signal of lines without mask pulse are outed at $V_C$ (terminal 1) and $V_{BLK}$ (terminal 6).                                                 |

|           | Non mask pulse function and BUSY signal output | 0                    | The functions are similar to standard type. (terminal 1 : BUSY, terminal 7 : CK <sub>OUT</sub> , terminal 15 : TEST OUT)                                                     |

| "BDC4F0CT | Mask pulse function and BUSY signal output     | 0                    | Mask pulse output : terminal 15 (terminal 1 : BUSY, terminal 7 : CK <sub>OUT</sub> )                                                                                         |

| μPD6450GT | Non mask pulse function and BUSY signal outut  | 0                    | All character signal and all blanking signal are outed at $V_C$ (terminal 1) and $V_{BLK}$ (terminal 7, terminal 15 : TEST OUT)                                              |

|           | Mask pulse function<br>and BUSY signal output  | 0                    | Character signal and blanking signal of line without mask pulse are outed at V <sub>C</sub> (terminal 1) and V <sub>BLK</sub> (terminal 7). (mask pulse output: terminal 15) |

Note: As using mask pulse function at μPD6450CX, this product doesn't have mask pulse output terminal. So in this case, please use mask pulse function and character signal output function at same time.

### PIN DESCRIPTION

| SYMBOL                          | PIN NAME                                            | FUNCTION                                                                                                                                                                                                                               |

|---------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $v_{DD}$                        | Power Supply Terminal                               | Supplies power (+5 V)                                                                                                                                                                                                                  |

| V <sub>SS</sub>                 | Ground Terminal                                     | Connected to system ground.                                                                                                                                                                                                            |

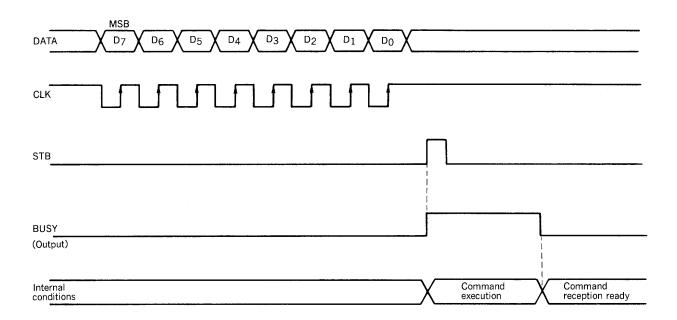

| DATA                            | Serial Data Input Terminal                          | Input terminal for control data.  Data is read synchronized with clock pulse at CLK terminal.                                                                                                                                          |

| CLK                             | Clock Input Terminal                                | Input terminal for data reading clock.  Data at data terminal is read at rising edge clock pulse.                                                                                                                                      |

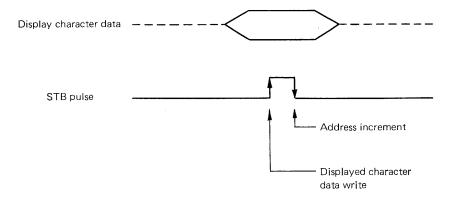

| STB                             | Strobe Input Terminal                               | Terminal for strobe input after serial data input. Eight-bit data is read at rising edge of pulse applied to STB terminal. If the eight-bit data is character data, the data address is incremented by 1 at the falling edge of pulse. |

| BUSY                            | BUSY Signal Output Terminal                         | This terminal tells the microcomputer whether or not STB input is ready. Input is feasible at low level,                                                                                                                               |

| Vc Note 1)                      | Character Signal Output Terminal                    | Output terminal for character signal of rows without mask pulse.  Output is feasible at high level.                                                                                                                                    |

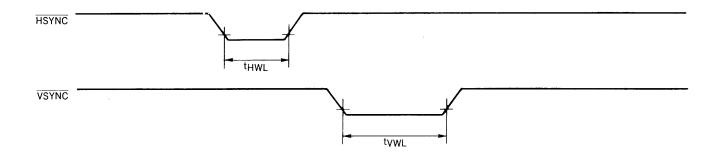

| HSYNC                           | Horizontal Synchronization Signal<br>Input Terminal | This is input terminal for horizontal synchronization signal. Oscillation occurs when HSYNC is at high level and oscillation synchronizes with the rising edge of HSYNC. Data is input at Active Low.                                  |

| VSYNC                           | Vertical Synchronization Signal Input Terminal      | Input terminal for vertical synchronization signal. Data should be input at Active Low.                                                                                                                                                |

| L <sub>OSC</sub> IN<br>Losc out | LC Oscillation Terminal                             | Connection terminal for coil and capacitor of dot clock generating oscillator.                                                                                                                                                         |

| XOSC IN<br>XOSC OUT             | Crystal Oscillation Terminal                        | Crystal connecting terminal for Oscillator which generates internal synchronization signals.                                                                                                                                           |

| V <sub>video in</sub>           | Video Signal Input Terminal                         | Input terminal for composite video signal. Data is to be input when the synchronization signal is negative and the image signal is positive.                                                                                           |

| V <sub>video out</sub>          | Video Signal Output Terminal                        | Output terminal for composite video signal mixing with character signal.                                                                                                                                                               |

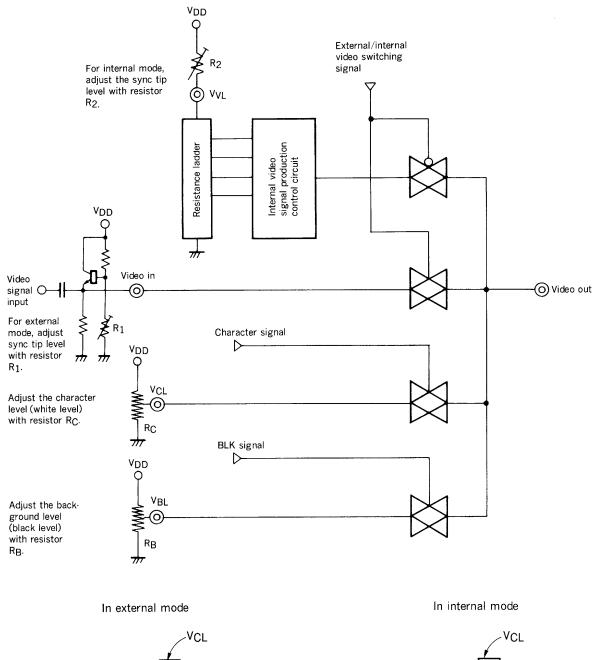

| V <sub>CL</sub>                 | Character Level Adjusting<br>Terminal               | Input terminal for adjusting character signal level (white level).                                                                                                                                                                     |

| V <sub>BL</sub>                 | Background Level Adjusting<br>Terminal              | Input terminal for adjusting background signal level (black level)                                                                                                                                                                     |

| VVL                             | Simplified Video Signal Level<br>Adjusting Terminal | Input terminal for adjusting signal level of video signal (sync tip level) which is produced in internal mode.                                                                                                                         |

| ck <sub>out</sub>               | Clock Out Terminal                                  | Inverted OSC OUT terminal. This terminal is used for checking oscillation frequency.  This terminal is a test input terminal as well, so it should be used after format reset.                                                         |

| V <sub>BLK</sub> Note 1)        | Blanking Signal Output Terminal                     | Output terminal for the blanking signal to cut the video signal of rows without mask pulse.  Output is feasible at high level.                                                                                                         |

| TESTOUT Note 2)                 | Test Out Terminal                                   | Test out terminal. (This terminal is usually open.)                                                                                                                                                                                    |

Note 1: In case of selected character signal output function in mask code option.

Note 2: This terminals can be covered to mask pulse output terminal in mask code option only for  $\mu$ PD6450GT. The  $\mu$ PD6450CX-002 and  $\mu$ PD6450GT-102 don't use a mask pulse and character signal output, and terminal 15 of  $\mu$ PD6450GT-102 is "TEST OUT." This terminal is usually open.

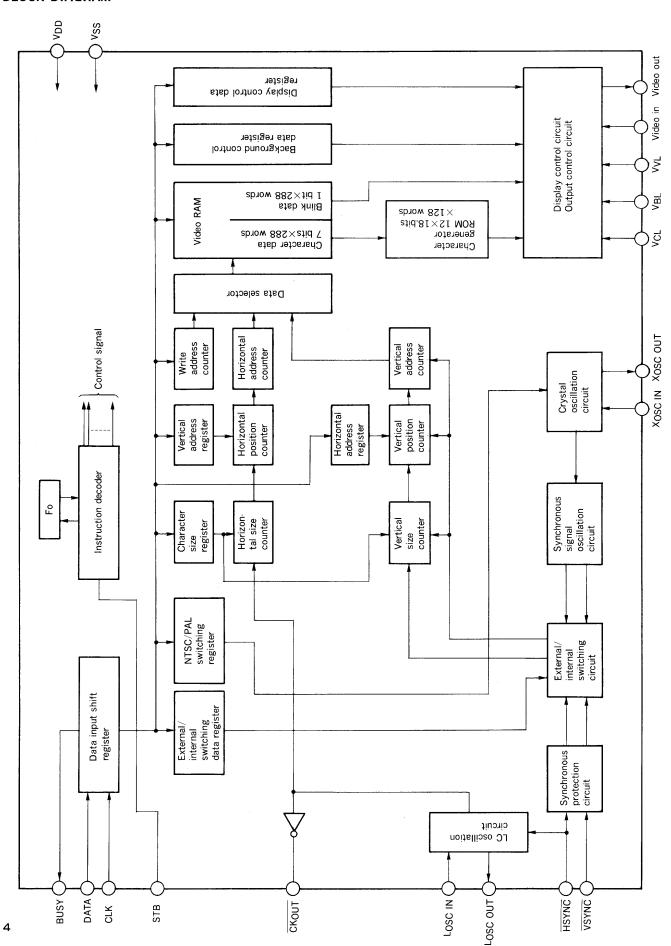

#### **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Ta = 25 $^{\circ}$ C)

| Supply Voltage        | $V_{DD}-V_{SS}$  | . 7                                                       | V  |

|-----------------------|------------------|-----------------------------------------------------------|----|

| Input Voltage         | $V_{IN}$         | $V_{ m DD}$ +0.3 $>$ $V_{ m IN}$ $>$ $V_{ m SS}$ $-0.3$   | V  |

| Output Voltage        | $v_{out}$        | $V_{ m DD}$ +0.3 $>$ $V_{ m OUT}$ $>$ $V_{ m SS}$ $-$ 0.3 | V  |

| Operation Temperature | $T_{opt}$        | -20 to +75                                                | °C |

| Storage Temperature   | T <sub>stg</sub> | -40 to +125                                               | °C |

| Output Current        | I <sub>D</sub>   | ±5                                                        | mΑ |

### RECOMMENDED OPERATION RANGE

| CHARACTERISTIC                                  | SYMBOL                           | MIN. | TYP. | MAX.            | UNIT |

|-------------------------------------------------|----------------------------------|------|------|-----------------|------|

| Supply Voltage                                  | V <sub>DD</sub> -V <sub>SS</sub> | 4.5  | 5.0  | 5.5             | V    |

| LC Oscillation Frequency                        | f <sub>osc</sub>                 | 4    | 7    | 10              | MNz  |

| Control Input High-level Voltage                | ViH                              | 2.4  |      |                 | V    |

| Control Input Low-level Voltage                 | VIL                              |      |      | 0.8             | · V  |

| Synchronization Signal Input High-level Voltage | V <sub>IH</sub>                  | 2.4  |      |                 | V    |

| Synchronization Signal Input Low-level Voltage  | VIL                              |      |      | 8.0             | V    |

| External Vido Signal Input Voltage              | Vi                               | 0    |      | V <sub>DD</sub> | V    |

| Character Signal Level Set Voltage              | V <sub>CL</sub>                  | 0    |      | V <sub>DD</sub> | V    |

| Background Signal Level Set Voltage             | V <sub>BL</sub>                  | 0    |      | V <sub>DD</sub> | V    |

| Internal Video Signal Level Set Voltage         | V <sub>V</sub> L                 | 2.5  |      | V <sub>DD</sub> | V    |

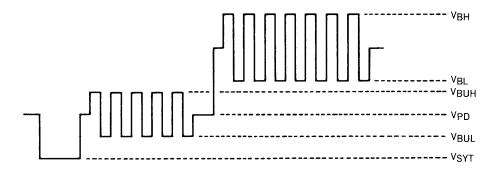

#### INTERNAL SIMPLIFIED VIDEO SIGNAL

### **Type of Command**

Control commands are eight-bit serial input types. Commands are executed by STB pulse input after serial input of eight-bit data. Before executing a program always issue a format reset command (format assignment command "FR = 1") to release the test mode.

### COMMAND LIST FOR $\mu$ PD6450

| CONTENT                                                                            | F <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D4              | D <sub>3</sub>  | D <sub>2</sub>  | D <sub>1</sub>  | D <sub>0</sub>  |

|------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

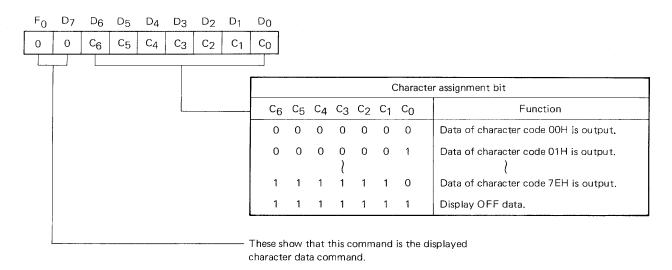

| Display Character Data                                                             | 0              | 0              | c <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub>  | C <sub>3</sub>  | C <sub>2</sub>  | C <sub>1</sub>  | C <sub>0</sub>  |

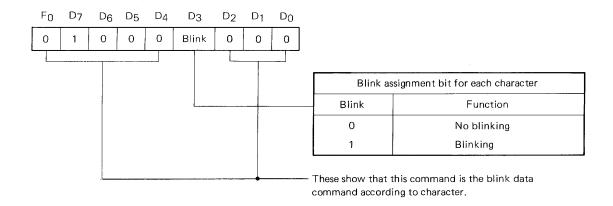

| Blink Data for Each Character                                                      | 0              | 1              | 0              | 0              | 0               | Blink           | 0               | 0               | 0               |

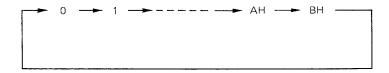

| Character Display Line Address                                                     | 0              | 1              | 0              | 0              | 1               | AR <sub>3</sub> | AR <sub>2</sub> | AR <sub>1</sub> | AR <sub>0</sub> |

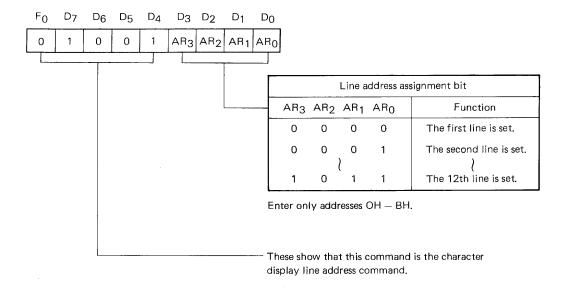

| Character Display Column Address                                                   | 0              | 1              | 0              | 1              | AC4             | AC <sub>3</sub> | AC <sub>2</sub> | AC <sub>1</sub> | AC <sub>0</sub> |

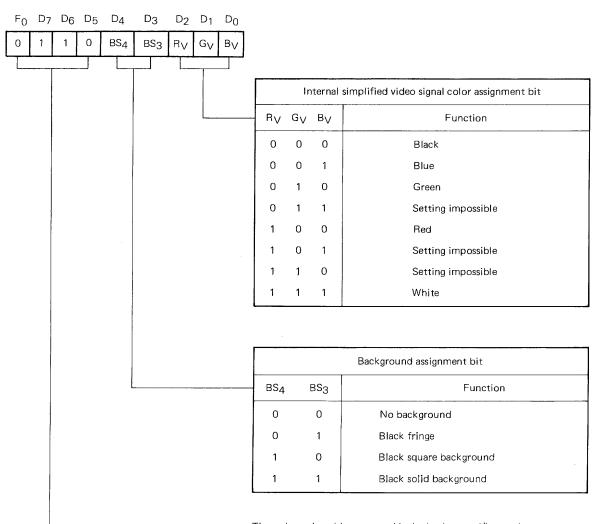

| Color Assignment for Background/<br>Internal Video Signal                          | 0              | 1              | 1              | 0              | BS <sub>4</sub> | BS <sub>3</sub> | R <sub>V</sub>  | GV              | ву              |

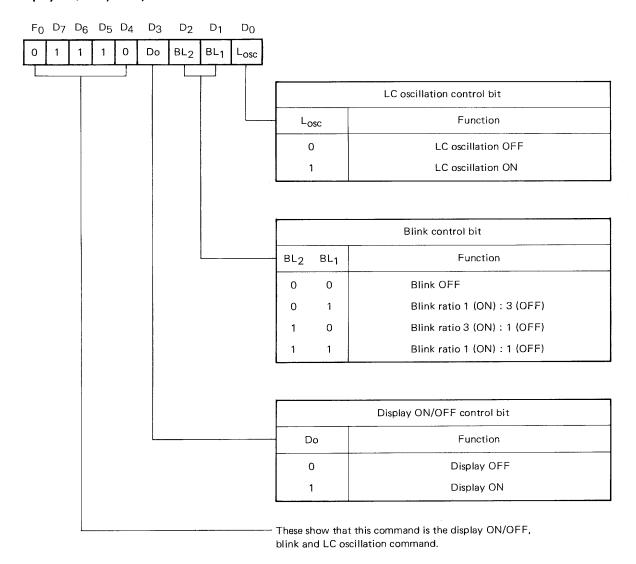

| Display ON/OFF, Blink, LC Oscillation<br>Control                                   | 0              | 1              | 1              | 1              | 0               | DO              | BL <sub>2</sub> | BL1             | Losc            |

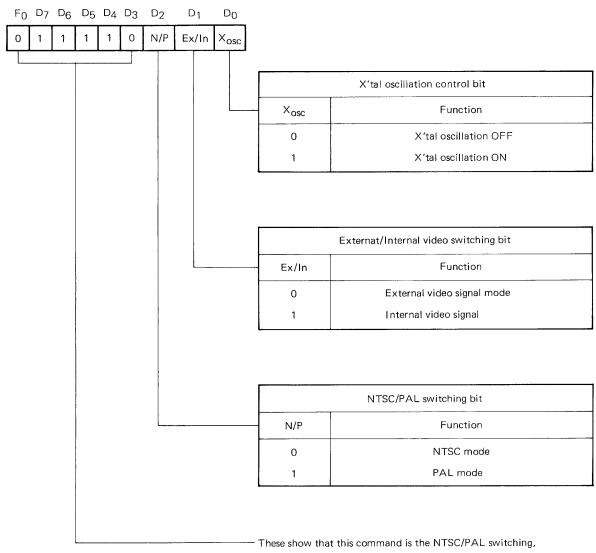

| NTSC/PAL Switching, External/Internal Video Switching, Crystal Oscillation Control | 0              | 1              | 1              | 1              | 1               | 0               | N/P             | Ex/In           | xosc            |

| Format Assignment                                                                  | х              | 1              | 1              | 1              | 1               | 1               | 1               | F <sub>0</sub>  | FR              |

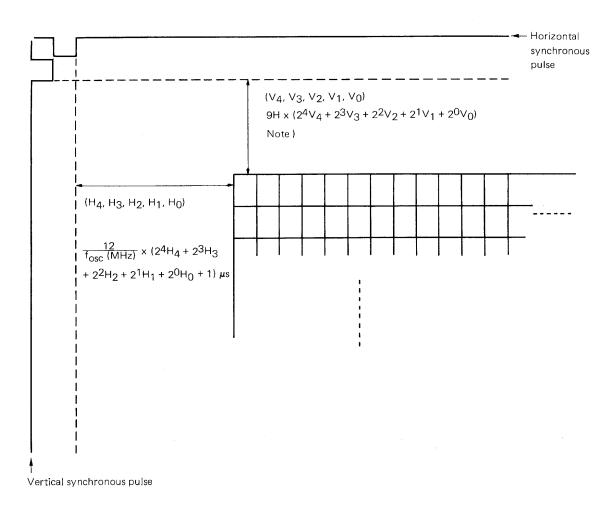

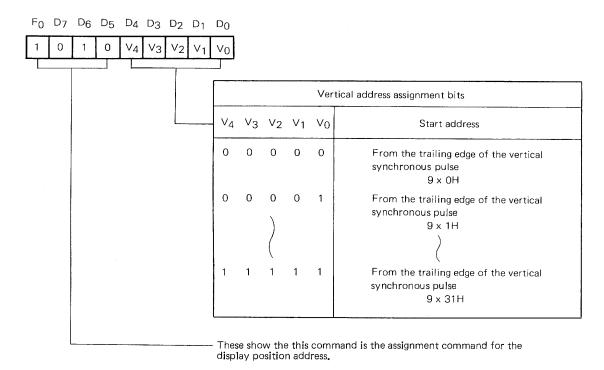

| Display Position Vertical Address                                                  | 1              | 0              | 1              | 0              | V <sub>4</sub>  | V <sub>3</sub>  | V <sub>2</sub>  | V <sub>1</sub>  | V <sub>0</sub>  |

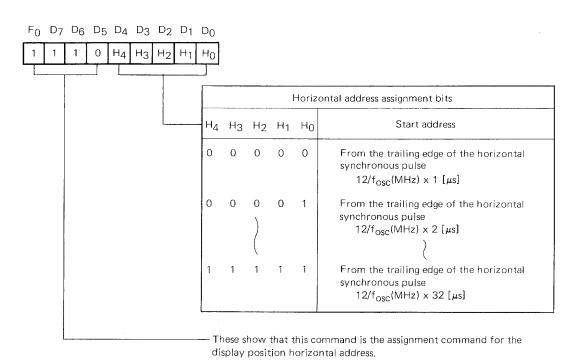

| Display Position Horizontal Address                                                | 1              | 1              | 1              | 0              | Н4              | Нз              | H <sub>2</sub>  | H <sub>1</sub>  | H <sub>0</sub>  |

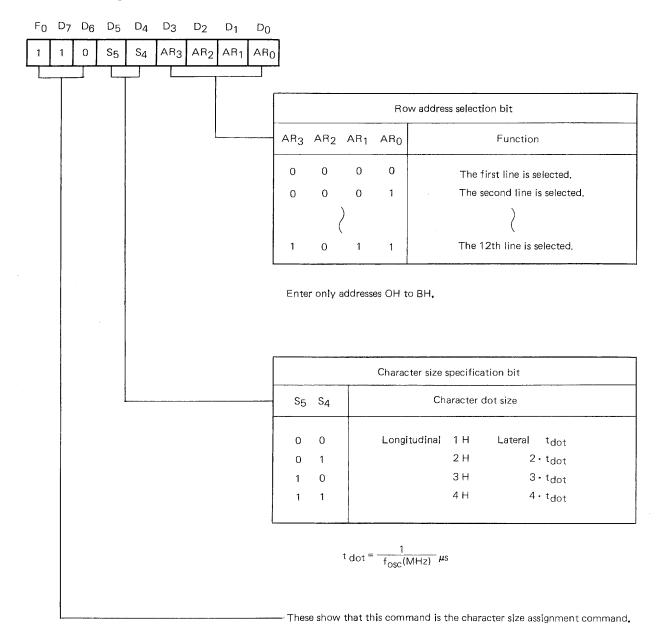

| Character Size Assignment Note                                                     | 1              | 1              | 0              | S <sub>5</sub> | S <sub>4</sub>  | AR <sub>3</sub> | AR <sub>2</sub> | AR <sub>1</sub> | AR <sub>0</sub> |

| Test Mode Set                                                                      | 1              | 1              | 1              | 1              | 0               | Тз              | T <sub>2</sub>  | T <sub>1</sub>  | То              |

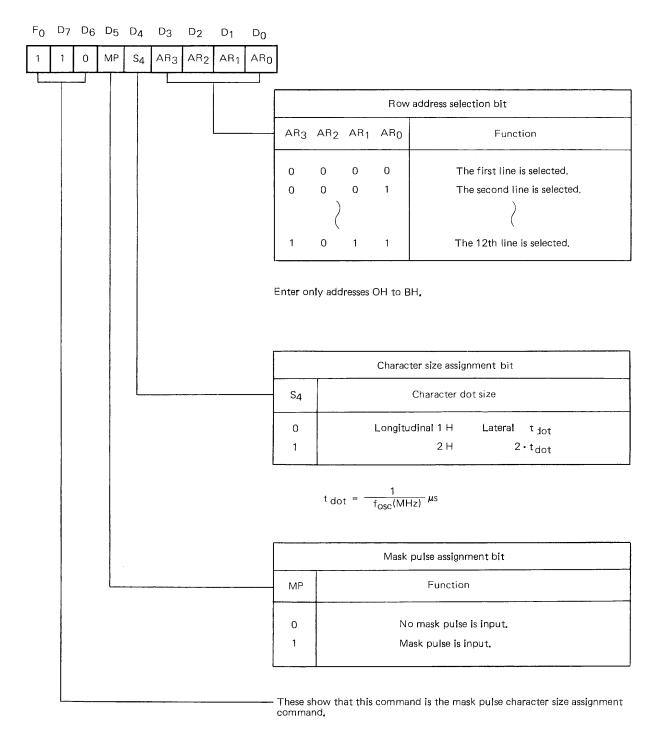

Note: Change of command because of mask pulse.

In case of selecting mask pulse function in mask code option at  $\mu$ PD6450CX/GT, the command of character size is changed as shown below and this command is used some command with the command of mask pulse.

(The kind of character sizes is changed from 4 to 2.)

As using mask pulse function at  $\mu$ PD6450CX, this product doesn't have mask pulse output terminal. So in this case, please use mask pulse function and character signal output function at same time.

| CONTENT                              | F <sub>0</sub> | D7 | D6 | D <sub>5</sub> | D4             | D <sub>3</sub>  | D <sub>2</sub>  | D <sub>1</sub>  | D <sub>0</sub>  |

|--------------------------------------|----------------|----|----|----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| Character Size/Mask Pulse Assignment | 1              | 1  | 0  | MP             | S <sub>4</sub> | AR <sub>3</sub> | AR <sub>2</sub> | AR <sub>1</sub> | AR <sub>0</sub> |

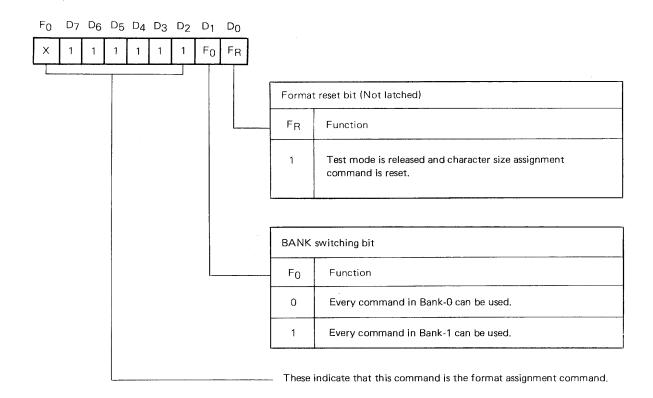

#### Format Assignment and Format Reset (Test Mode Release)

Although commands for  $\mu$ PD6450 consist of nine bits, they are separated into two banks because serial interface shift register uses eight bits. Switching of banks is made by bit 1 (F<sub>0</sub>) of the format assignment command.

#### Command for bank '0' $(F_0 = 0)$

- O Displayed character data

- Blink data for each character

- Character display line address

- Character display column address

- Color assignment for background/internal video signal

- O Display ON/OFF, Blink, LC Oscillation Control

- o NTSC/PAL Switching, External/Internal Video Switching, Crystal Oscillation Control

### Command for bank '1' $(F_0 = 1)$

- O Display position vertical address

- O Display position horizontal address

- O Character size assignment

- Test mode set

#### Format Reset (Test Mode Release)

Setting bit 0 (F<sub>R</sub>) of format assignment command to "1" releases the test command mode and resets the following command. Since the test command mode stops normal commands from being received, always perform format reset to release test command mode before program execution.

#### Reset Command

Size register (AR<sub>0.3</sub>) on every line is set to " $(S_5, S_4) = (0, 0)$ ."

(Minimum size is assigned on every line.)

In case of selecting mask pulse function in mask code option at  $\mu PD6450CX/GT$ , size register (AR<sub>0.3</sub>) is set to (S<sub>4</sub>) = (0) on every lines and no mask pulse is output on any line (MP = (0)).

To release the test command mode without resetting the command above, use the test command mode release statement  $(F_0, D_7, D_6, D_5, D_4, D_3, D_2, D_1, D_0) = (1, 1, 1, 1, 0, 0, 0, 0, 0)$ .

Note: As using mask pulse function at  $\mu$ PD6450CX, this product doesn't have mask pulse output terminal. So in this case, please use mask pulse function and character signal output function at same time.

### Format Assignment Command

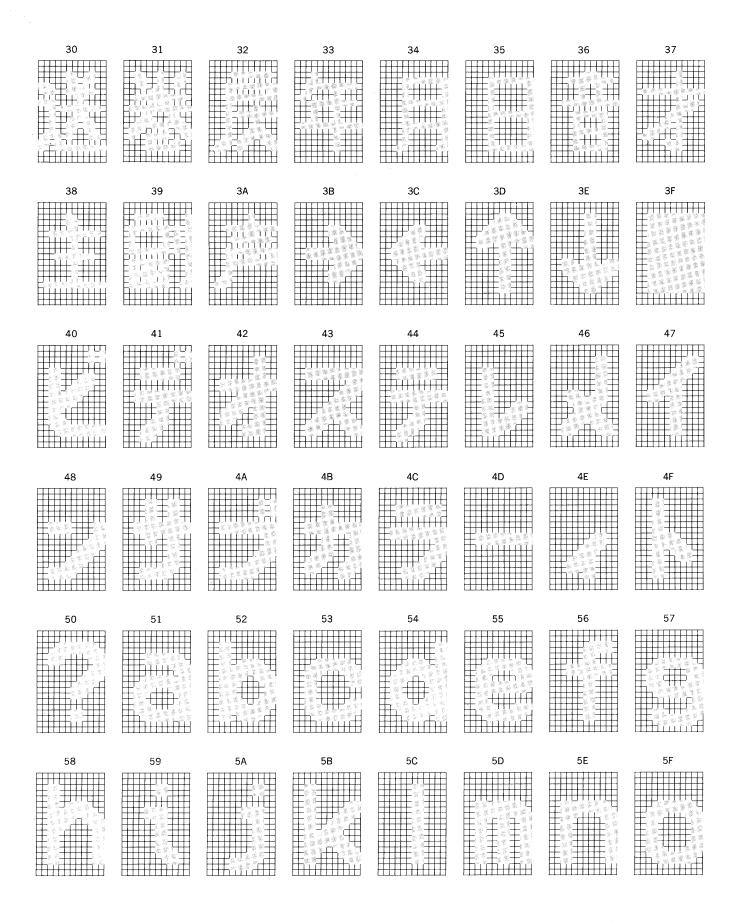

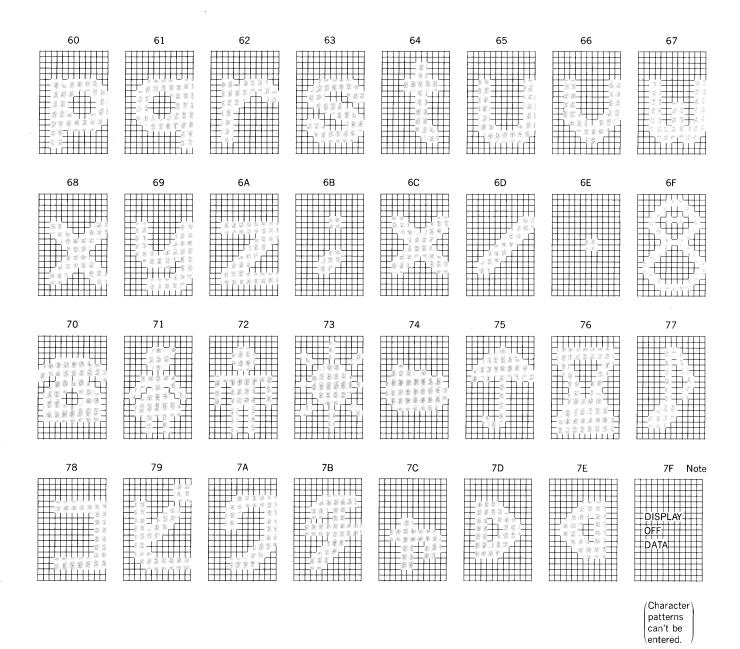

# Character Patterns of $\mu$ PD6450CX-002 & 6450GT-102

| 00         | 01 | 02 | 03 | 04 | 05 | 06  | 07         |

|------------|----|----|----|----|----|-----|------------|

| 08         | 09 | OA | OB | OC | OD | OE. | OF         |

| 10 (Blank) | 11 | 12 | 13 | 14 | 15 | 16  | 17         |

| (=         |    |    |    |    |    |     |            |

| 18         | 19 | 1A | 18 | 1C | 10 | 1E  | 1下<br>大學 在 |

| 20         | 21 | 22 | 23 | 24 | 25 | 1E  | 1F         |

Note: In black block background and total black background mode, blank data (10H) generates background but no characters. DISPLAY OFF DATA (7FH) doesn't generate background or characters. If no-background or black trimmed character background mode is selected, BLANK DATA (10H) and DISPLAY OFF DATA (7FH) don't generate background or characters.

#### **Character Display**

There 12 lines by 24 columns of characters displayed (288 characters in all) as follows:

| AC4, AC3, AC2, AC | 1, AC0 | 00000 | 00001 | 00010 | 00011 | 00100 | 00101 | 00110 | 00111 | 01000 | 01001 | 01010 | 01011 | 01100 | 01101 | 01110 | 01111 | 10000 | 10001 | 10010 | 10011 | 10100 | 10101 | 10110 | 10111 |

|-------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| AR3               | 0000   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| AR2<br>AR1        | 0001   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

| AR0               | 0010   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 0011   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 0100   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 0101   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 0110   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 0111   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 1000   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 1001   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 1010   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|                   | 1011   |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

#### Writing Displayed Character Data and Blink Data for Each Character

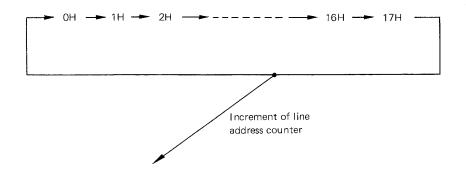

The data write address can be set directly into the address counter by the character display line address command and character display column address command. After setting write address, feed blink data for each character with the blink data command. Blink data is stored by character in an internal register. After that, input displayed character data with the displayed character data command. Blink data and displayed character data which has been stored in an internal register is written in video RAM at the rise of the STB pulse input at the end of displayed character data command. The write address is incremented as follows at rising edge of the STB pulse generated when displayed character data is input. To continue to write displayed character data without changing blink data, input the displayed character data command.

Column address counter AC<sub>4</sub>, AC<sub>3</sub>, AC<sub>2</sub>, AC<sub>1</sub>, AC<sub>0</sub>

Line address counter AR<sub>3</sub>, AR<sub>2</sub>, AR<sub>1</sub>, AR<sub>0</sub>

### Character Display Line Address Command

### **Character Display Column Address Command**

#### Blink Data Command for Each Character

#### **Displayed Character Data Command**

#### **Turning Total Display ON or OFF**

The display can be partially turned off with Blank data or display off data. The total display turned off with display ON/ OFF, blink, and LC oscillation control commands. When display OFF is set with this command, characters and backgrounds are not output.

#### Character Blinking

This IC enables blinking for each character with display ON/OFF, blink, and LC oscillation control commands. Blinking characters are determined with the character blink data command. The blinking period is about 1 second (64 times longer than 1 vertical cycle), and three blinking ratios (1:1, 3:1, and 1:3) are available.

#### **LC Oscillation Control**

Since this IC enables control of LC oscillation with display ON/OFF, blink, and LC oscillation control commands, oscillation can be suspended while characters aren't displayed, so that power can be saved. Since character output isn't reliable after suspension of oscillation, set the display ON/OFF control bit (Do) to "O" (display OFF).

Note: When display is ON, the oscillation synchronizes  $\overline{H_{SYNC}}$ , so the oscillation is stopping at the low level term of  $\overline{H_{SYNC}}$ . When display is OFF, the oscillation keeps on irrespective of  $\overline{H_{SYNC}}$ .

### Display ON/OFF, Blink, and LC Oscillation Commands

#### **Character Display Address**

Character display starting address is determined as follows with values assigned by both the display position vertical address command ( $F_0$ ,  $D_7$ ,  $D_6$ ,  $D_5$ ,  $D_4$ ,  $D_3$ ,  $D_2$ ,  $D_1$ ,  $D_0$ ) = (1, 0, 1, 1,  $V_4$ ,  $V_3$ ,  $V_2$ ,  $V_1$ ,  $V_0$ ) and the display position horizontal address command ( $F_0$ ,  $F_0$ ,

Note: Vertical address counter is incremented by the leading edge of the horizontal synchronous pulse.

#### **Assignment Command for Display Position Vertical Address**

### **Assignment Command for Display Position Horizontal Address**

### **Assignment of Character Size**

Character size for each line can be selected from 1H, 2H, 3H or 4H of 1 dot. Line and character size is assigned with the character size assignment command. Note that there are two character sizes (1H or 2H of 1 dot) when the mask pulse function is selected in mask code option

#### **Character Size Assignment Command**

#### External/Internal Video Switching

When TV broadcasting signal can't be received or when unprerecorded tape is being played, synchronization is poor and mixing of the character signal results in poor character display. In such cases an internal video signal (raster signal of one color out of white, black, red, green and blue) should be generated with NTSC/PAL switching, external/internal video switching, or crystal oscillation control command, so that mixing of the character signal becomes possible. When an external video signal is used, crystal oscillation can be stopped by setting the crystal oscillation control bit (X<sub>osc</sub>) to "0." This reduces power consumption. Internal video signal is noninterlaced video signal.

#### NTSC/PAL Switching

The internal video signal shown above can be used in both NTSC and PAL systems by changing NTSC/PAL switching bit with the NTSC/PAL switching, external/internal video switching, or crystal oscillation control command and by changing the external X'tal (14.318 18 MHz for NTSC, 17.734 476 MHz for PAL).

#### External/Internal Video Switching, X'tal Oscillation Control Command

external/internal video switching, crystal oscillation control command.

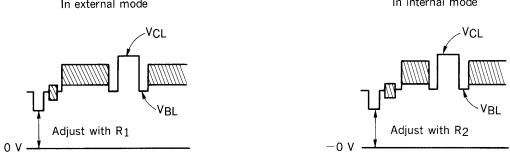

## Adjusting Sync tip level, Character level, and Background level

Note: Since there is no built-in pedestal clamp circuit for external video signal, connect direct current clamp circuit in front of "video in."

#### Background Assignment and Color Changing of Internal Video Signal

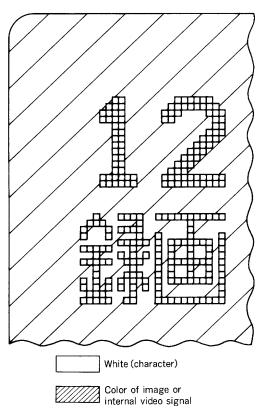

The background can be selected for each screen image from no-background, black-fringe, black square background, and black-solid background by the background internal video signal color assignment command. The background color is black.

When an internal video signal is used because of NTSC/PAL switching, external/internal video switching, and X'tal oscillation control command, raster color is switched by this background internal video signal color assignment command as well. In this case, white, black, red, green, or blue can be selected. Internal video signal is noninterlaced video signal.

| 0 | No background           | Character is totally surrounded by image or internal video signal.        |

|---|-------------------------|---------------------------------------------------------------------------|

| 0 | Black fringe            | Characters are trimmed with 1 dot-minimum character (1H/1 dot).           |

| 0 | Black square background | The 12 line x 24 column block displaying characters has a black back-     |

|   |                         | ground.                                                                   |

| 0 | Black solid background  | Image signal or internal video signal is totally omitted and whole screen |

|   |                         | has a black background.                                                   |

### **Background Internal Video Signal Color Assignment Command**

These show that this command is the background/internal video signal color assignment command.

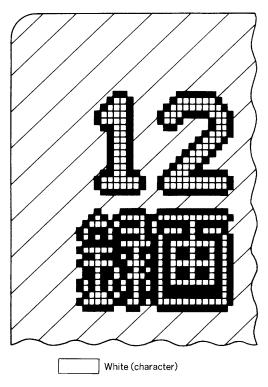

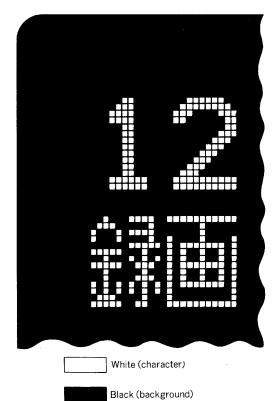

### **Display in Various Background Modes**

No background

Black Square background

Black fringe

Black (background)

Color of image or internal video signal

Black solid background

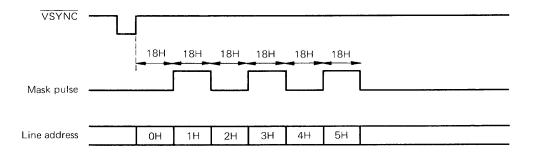

#### Mask Pulse Function

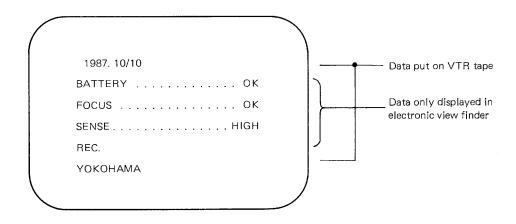

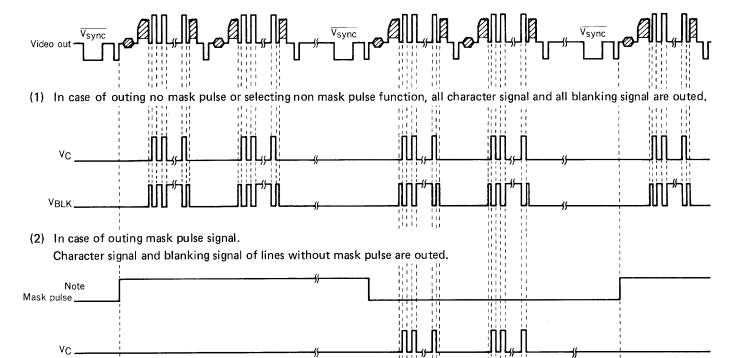

If an on-screen IC is used for VTR cameras, there are two types of data such as dates and titles to be put onto the VTR tapes and data such as battery, focus, sensitivity, and mode to be displayed in the electronic view finder. To sort these two data, this product can out character signal and blanking signal of lines without mask pulse (character signal output function: mask code option). And µPD6450GT is possible to use '15' terminal as mask pulse output terminal in mask code option.

When the mask pulse is generated at line addresses 1H, 3H, and 5H with vertical address "OH" and with character size in all lines "2H/dot".

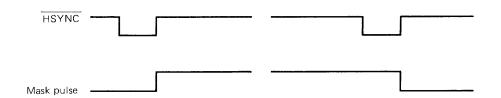

Leading and trailing edges of mask pulse are synchronized with trailing edge of HSYNC.

**VBLK**

Outputs of  $V_C$ ,  $V_{BLK}$  terminals, in case of selected character signal output function in mask code option.

Note: As using mask pulse function at μPD6450CX, this product doesn't have mask pulse output terminal. So in this case, please use mask pulse function and character signal output function at same time.

#### Mask Pulse, Character Size Assignment Command

(Used only when mask pulse function is selected for  $\mu$ PD6450GT by mask code option.)

Note: μPD6450CX-002 and μPD6450GT-102 don't use the mask pulse and character signal output, and this command can't be used for it.

As using mask pulse function at μPD6450CX, this product doesn't have mask pulse output terminal. So in this case, please use mask pulse function and character signal output function at same time.

For format data, a busy signal is generated after the internal conditions are completely determined. When writing data in VRAM, a busy signal is generated after the completion of writing in VRAM. When the VRAM write period extends into the horizontal retrace line period, the busy signal becomes longer than usual, so be careful. (This is because oscillation is suspended during the horizontal retrace line period, so writing in VRAM becomes impossible.)

Note: As the character signal output function is selected in mask code option, the 1st-terminal can't output the BUSY-signal.

Please take care of the data transmitting and keep the recommended operation timing.

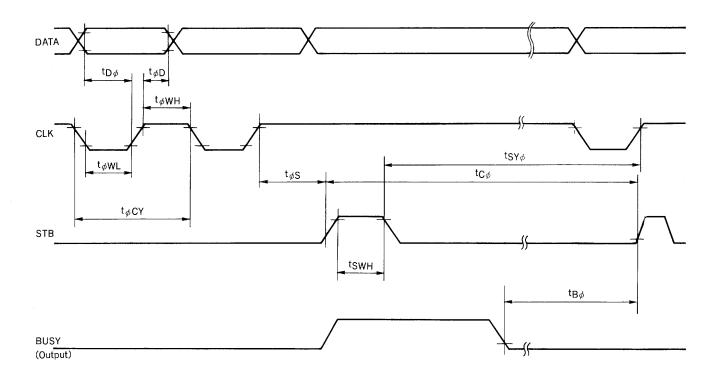

# RECOMMENDED OPERATION TIMING ( $T_a = 25$ °C, $V_{DD} - V_{SS} = 5.0$ V)

| ITEM                         | SYMBOL                    | MIN. | TYP. | MAX. | UNIT | TEST CONDITIONS                                                                                                                                                                                       |

|------------------------------|---------------------------|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min. Setup Time              | t <sub>Dφ</sub>           | 200  |      |      | ns   |                                                                                                                                                                                                       |

| Min. Hold Time               | t <sub></sub> dD          | 200  |      |      | ns   |                                                                                                                                                                                                       |

| Min. Clock Low-level Width   | <sup>†</sup> φ <b>W</b> L | 700  |      |      | ns   |                                                                                                                                                                                                       |

| Min. Clock High-level Width  | <sup>t</sup> $\phi$ WH    | 700  |      |      | ns   |                                                                                                                                                                                                       |

| Min. Clock → Strobe Time     | t <sub>φ</sub> S          | 400  |      |      | ns   |                                                                                                                                                                                                       |

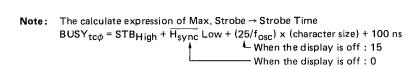

| Min. Strobe High-level Width | <sup>t</sup> SWH          | 1    |      |      | μs   |                                                                                                                                                                                                       |

| Clock Cycle                  | <sup>t</sup> φCY          | 1.6  |      |      | μs   |                                                                                                                                                                                                       |

| Min. Busy → Strobe Time      | $t_{B\phi}$               | 100  |      |      | ns   |                                                                                                                                                                                                       |

| Min. VSYNC Low-level Width   | t∨WL                      | 4    |      |      | μs   |                                                                                                                                                                                                       |

| Min. HSYNC Low-level Width   | tHWL                      | 4    |      |      | μs   |                                                                                                                                                                                                       |

|                              |                           | 14.4 |      |      | μs   | Displayed Character Data Command transmits at display ON with following conditions. Strobe high-level Width: 1 $\mu$ s $H_{sync}$ low-level Width: 5 $\mu$ s $f_{osc}$ : 6 MHz Character size: 2H/dot |

| Max. Strobe → Strobe Time    | <sup>†</sup> Cφ           | 11.1 |      |      | μς   | Displayed Character Data Command transmits at display OFF with following conditions. Strobe high-level Width: 1   Hsync low level Width: 5   fosc: 6 MHz Character size: 2H/dot                       |

| Min. Strobe → Clock Time     | <sup>t</sup> SY $\phi$    | 4    |      |      | μs   | Commands except Displayed<br>Character Data Command<br>transmit.                                                                                                                                      |

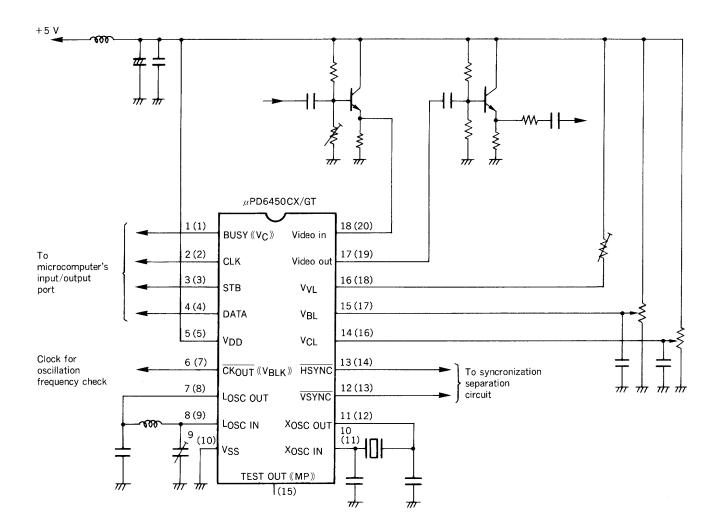

### ADOPTED CIRCUIT

Numbers in single brackets are terminal numbers for  $\mu$ PD6450GT and don't connect 6th and 15th terminals for code products which don't use the mask pulse.

This double brackets shows terminal arrangement for the mask code option when selecting Mask pulse function and Character signal output function. Take care of connection of this terminals.

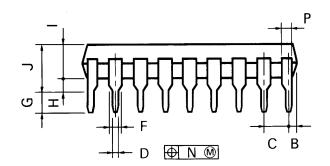

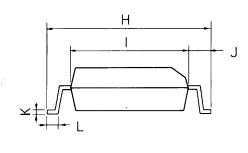

### $\mu$ PD6450CX-002

# 18PIN PLASTIC DIP (300 mil)

P18C-100-300B

### **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES        |

|------|-----------------------|---------------|

| Α    | 22.86 MAX.            | 0.900 MAX.    |

| В    | 1.27 MAX.             | 0.050 MAX.    |

| С    | 2.54 (T.P.)           | 0.100 (T.P.)  |

| D    | 0.50 <sup>±0.10</sup> | 0.020 + 0.004 |

| F    | 1.2 MIN.              | 0.047 MIN.    |

| G    | 3.2 <sup>± 0.3</sup>  | 0.126 ±0.012  |

| Н    | 0.51 MIN.             | 0.020 MIN.    |

| ı    | 4.31 MAX.             | 0.170 MAX.    |

| J    | 5.08 MAX.             | 0.200 MAX.    |

| К    | 7.62 (T.P.)           | 0.300 (T.P.)  |

| L    | 6.4                   | 0.252         |

| М    | 0.25 -0.10            | 0.010 + 0.004 |

| N    | 0.25                  | 0.01          |

| Р    | 1.0 MIN.              | 0.039 MIN.    |

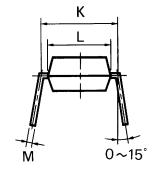

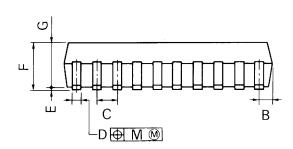

$\mu$ PD6450GT-102

# 20PIN PLASTIC SOP (375 mil)

### P20GM-50-375B-1

### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS          | INCHES        |

|------|----------------------|---------------|

| Α    | 13.00 MAX.           | 0.512 MAX.    |

| В    | 0.78 MAX.            | 0.031 MAX.    |

| С    | 1.27 (T.P.)          | 0.050 (T.P.)  |

| D    | 0.40 +0.10           | 0.016-0.004   |

| Е    | 0.1 + 0.2            | 0.004 +0.008  |

| F    | 2.9 MAX.             | 0.115 MAX.    |

| G    | 2.50                 | 0.098         |

| Н    | 10.3 <sup>±0.3</sup> | 0.406 0.013   |

| ı    | 7.2                  | 0.283         |

| J    | 1.6                  | 0.063         |

| К    | 0.15 + 0.10          | 0.006 + 0.004 |

| L    | 0.8 +0.2             | 0.031-0.008   |

| М    | 0.12                 | 0.005         |

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or of others.