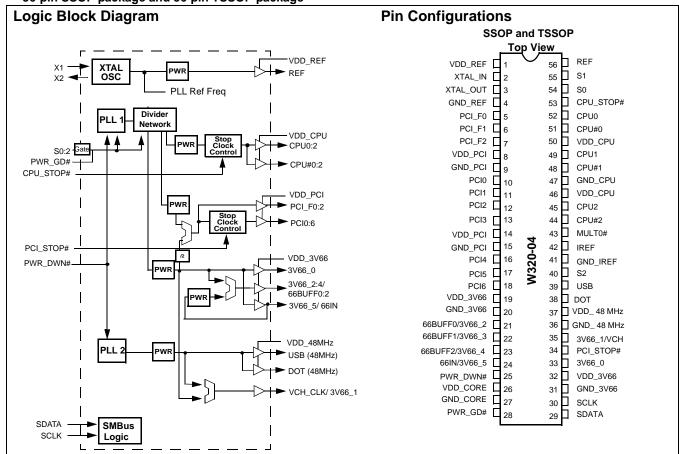

# 200 MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs

#### **Features**

- Compliant with Intel<sup>®</sup> CK-Titan clock synthesizer/driver specifications

- · Multiple output clocks at different frequencies

- Three pairs of differential CPU outputs, up to 200 MHz

- Ten synchronous PCI clocks, three free-running

- Six 3V66 clocks

- Two 48 MHz clocks

- One reference clock at 14.318 MHz

- One VCH clock

- Spread Spectrum clocking (down spread)

- Power-down features (PCI\_STOP#, CPU\_STOP# PWR\_DWN#)

- Three Select inputs (Mode select and IC Frequency Select)

- OE and Test Mode support

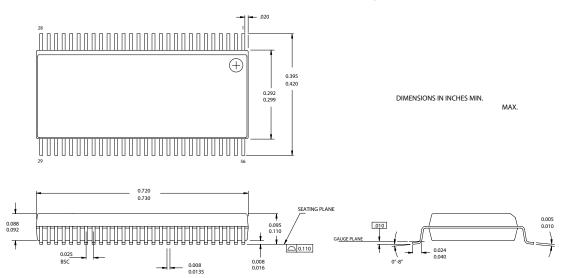

- 56-pin SSOP package and 56-pin TSSOP package

#### **Benefits**

- Supports next-generation Pentium<sup>®</sup> processors using differential clock drivers

- · Motherboard clock generator

- Supports multiple CPUs and a chipset

- Support for PCI slots and chipset

- Supports AGP, DRCG reference, and Hub Link

- Supports USB host controller and graphic controller

- Supports ISA slots and I/O chip

- Enables reduction of electromagnetic interference (EMI) and overall system cost

- Enables ACPI-compliant designs

- · Supports up to four CPU clock frequencies

- Enables ATE and "bed of nails" testing

- · Widely available standard package enables lower cost

www.SpectraLinear.com

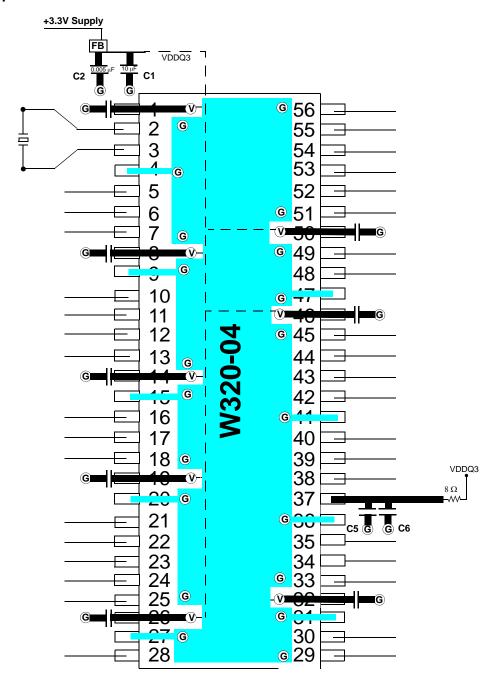

# **Pin Summary**

| Name                                                | Pins                         | Description                                                                                                                                                                                                      |

|-----------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF                                                 | 56                           | 3.3V 14.318-MHz clock output.                                                                                                                                                                                    |

| XTAL_IN                                             | 2                            | 14.318-MHz crystal input.                                                                                                                                                                                        |

| XTAL_OUT                                            | 3                            | 14.318-MHz crystal input.                                                                                                                                                                                        |

| CPU, CPU# [0:2]                                     | 44, 45, 48, 49, 51, 52       | Differential CPU clock outputs.                                                                                                                                                                                  |

| 3V66_0                                              | 33                           | 3.3V 66-MHz clock output.                                                                                                                                                                                        |

| 3V66_1/VCH                                          | 35                           | 3.3V selectable through SMBus to be 66 MHz or 48 MHz.                                                                                                                                                            |

| 66IN/3V66_5                                         | 24                           | 66-MHz input to buffered 66BUFF and PCI or 66-MHz clock from internal VCO.                                                                                                                                       |

| 66BUFF [2:0] /3V66 [4:2]                            | 21, 22, 23                   | 66-MHz buffered outputs from 66Input or 66-MHz clocks from internal VCO.                                                                                                                                         |

| PCI_F [0:2]                                         | 5, 6, 7,                     | 33-MHz clocks divided down from 66Input or divided down from 3V66.                                                                                                                                               |

| PCI [0:6]                                           | 10, 11, 12, 13, 16, 17, 18   | PCI clock outputs divided down from 66Input or divided down from 3V66.                                                                                                                                           |

| USB                                                 | 39                           | Fixed 48-MHz clock output.                                                                                                                                                                                       |

| DOT                                                 | 38                           | Fixed 48-MHz clock output.                                                                                                                                                                                       |

| S2                                                  | 40                           | Special 3.3V 3-level input for Mode selection.                                                                                                                                                                   |

| S1, S0                                              | 54, 55                       | 3.3V LVTTL inputs for CPU frequency selection.                                                                                                                                                                   |

| IREF                                                | 42                           | A precision resistor is attached to this pin, which is connected to the internal current reference.                                                                                                              |

| MULT0                                               | 43                           | 3.3V LVTTL input for selecting the current multiplier for the CPU outputs.                                                                                                                                       |

| PWR_DWN#                                            | 25                           | 3.3V LVTTL input for Power_Down# (active LOW).                                                                                                                                                                   |

| PCI_STOP#                                           | 34                           | 3.3V LVTTL input for PCI_STOP# (active LOW).                                                                                                                                                                     |

| CPU_STOP#                                           | 53                           | 3.3V LVTTL input for CPU_STOP# (active LOW).                                                                                                                                                                     |

| PWRGD#                                              | 28                           | 3.3V LVTTL input is a level sensitive strobe used to determine when S[2:0] and MULTI0 inputs are valid and OK to be sampled (Active LOW). Once PWRGD# is sampled LOW, the status of this output will be ignored. |

| SDATA                                               | 29                           | SMBus compatible SDATA.                                                                                                                                                                                          |

| SCLK                                                | 30                           | SMBus compatible SCLK.                                                                                                                                                                                           |

| VDD_REF, VDD_PCI,<br>VDD_3V66, VDD_CPU              | 1, 8, 14, 19, 32, 46, 50     | 3.3V power supply for outputs.                                                                                                                                                                                   |

| VDD_48 MHz                                          | 37                           | 3.3V power supply for 48 MHz.                                                                                                                                                                                    |

| VDD_CORE                                            | 26                           | 3.3V power supply for PLL.                                                                                                                                                                                       |

| GND_REF, GND_PCI,<br>GND_3V66, GND_IREF,<br>VDD_CPU | 4, 9, 15, 20, 31, 36, 41, 47 | Ground for outputs.                                                                                                                                                                                              |

| GND_CORE                                            | 27                           | Ground for PLL.                                                                                                                                                                                                  |

Rev 1.0, November 25, 2006 Page 2 of 16

## Function Table<sup>[1]</sup>

| <b>S2</b> | <b>S</b> 1 | S0 | CPU<br>(MHz) | 3V66[0:1]<br>(MHz) | 66BUFF[0:2]/<br>3V66[2:4]<br>(MHz) | 66IN/3V66_5<br>(MHz) | PCI_F/PCI<br>(MHz) | REF0(MHz)  | USB/DOT<br>(MHz) | Notes   |

|-----------|------------|----|--------------|--------------------|------------------------------------|----------------------|--------------------|------------|------------------|---------|

| 1         | 0          | 0  | 66 MHz       | 66 MHz             | 66IN                               | 66 MHz Input         | 66IN/2             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 1         | 0          | 1  | 100 MHz      | 66 MHz             | 66IN                               | 66 MHz Input         | 66IN/2             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 1         | 1          | 0  | 200 MHz      | 66 MHz             | 66IN                               | 66 MHz Input         | 66IN/2             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 1         | 1          | 1  | 133 MHz      | 66 MHz             | 66IN                               | 66 MHz Input         | 66IN/2             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 0         | 0          | 0  | 66 MHz       | 66 MHz             | 66 MHz                             | 66 MHz               | 33 MHz             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 0         | 0          | 1  | 100 MHz      | 66 MHz             | 66 MHz                             | 66 MHz               | 33 MHz             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 0         | 1          | 0  | 200 MHz      | 66 MHz             | 66 MHz                             | 66 MHz               | 33 MHz             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| 0         | 1          | 1  | 133 MHz      | 66 MHz             | 66 MHz                             | 66 MHz               | 33 MHz             | 14.318 MHz | 48 MHz           | 2, 3, 4 |

| Mid       | 0          | 0  | Hi-Z         | Hi-Z               | Hi-Z                               | Hi-Z                 | Hi-Z               | Hi-Z       | Hi-Z             | 1, 5    |

| Mid       | 0          | 1  | TCLK/2       | TCLK/4             | TCLK/4                             | TCLK/4               | TCLK/8             | TCLK       | TCLK/2           | 5, 6, 7 |

| Mid       | 1          | 0  | Reserved     | Reserved           | Reserved                           | Reserved             | Reserved           | Reserved   | Reserved         | _       |

| Mid       | 1          | 1  | Reserved     | Reserved           | Reserved                           | Reserved             | Reserved           | Reserved   | Reserved         | _       |

# **Swing Select Functions**

| Mult0 | Board Target Trace/Term Z | Reference R, IREF <sub>=</sub> V <sub>DD</sub> /(3*Rr) | Output Current           | V <sub>OH</sub> @ Z |

|-------|---------------------------|--------------------------------------------------------|--------------------------|---------------------|

| 0     | 50Ω                       | Rr = 221 1%, IREF = 5.00 mA                            | I <sub>OH</sub> = 4*IREF | 1.0V @ 50           |

| 1     | 50Ω                       | Rr = 475 1%, IREF = 2.32 mA                            | I <sub>OH</sub> = 6*IREF | 0.7V @ 50           |

## **Clock Driver Impedances**

|                    |                       |             | Impedance     |               |        |

|--------------------|-----------------------|-------------|---------------|---------------|--------|

| <b>Buffer Name</b> | V <sub>DD</sub> Range | Buffer Type | Min. $\Omega$ | Typ. $\Omega$ | Max. Ω |

| CPU, CPU#          |                       | Type X1     |               | 50            |        |

| REF                | 3.135–3.465           | Type 5      | 12            | 30            | 55     |

| PCI, 3V66, 66BUFF  | 3.135-3.465           | Type 5      | 12            | 30            | 55     |

| USB                | 3.135-3.465           | Type 3A     | 12            | 30            | 60     |

| DOT                | 3.135-3.465           | Type 3B     | 12            | 30            | 60     |

## **Clock Enable Configuration**

| PWR_DWN# | CPU_STOP# | PCI_STOP# | CPU    | CPU#  | 3V66 | 66BUFF | PCI_F | PCI | USB/DOT | VCOS/ OSC |

|----------|-----------|-----------|--------|-------|------|--------|-------|-----|---------|-----------|

| 0        | Х         | Х         | IREF*2 | FLOAT | LOW  | LOW    | LOW   | LOW | LOW     | OFF       |

| 1        | 0         | 0         | ON     | FLOAT | ON   | ON     | ON    | OFF | ON      | ON        |

| 1        | 0         | 1         | ON     | LOW   | ON   | ON     | ON    | ON  | ON      | ON        |

| 1        | 1         | 0         | ON     | ON    | ON   | ON     | ON    | OFF | ON      | ON        |

| 1        | 1         | 1         | ON     | ON    | ON   | ON     | ON    | ON  | ON      | ON        |

## Note:

- 1. TCLK is a test clock driven in on the XTALIN input in test mode.

- 2. "Normal" mode of operation

- 3. Range of reference frequency allowed is min. = 14.316, nom. = 14.31818 MHz, max. = 14.32 MHz.

- 4. Frequency accuracy of 48 MHz must be +167PPM to match USB default.

- 5. Mid. is defined a Voltage level between 1.0V and 1.8V for three-level input functionality. Low is below 0.8V. High is above 2.0V.

- 6. Required for DC output impedance verification.

- 7. These modes are to use the SAME internal dividers as the CPU = 200 MHz mode. The only change is to slow down the internal VCO to allow under clock margining.

Rev 1.0, November 25, 2006

#### Serial Data Interface (SMBus)

To enhance the flexibility and function of the clock synthesizer, a two-signal SMBus interface is provided according to SMBus specification. Through the Serial Data Interface, various device functions such as individual clock output buffers, can be individually enabled or disabled. W320-04 supports both block read and block write operations.

The registers associated with the Serial Data Interface initialize to their default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required. The interface can also be used during system operation for power management functions.

#### **Data Protocol**

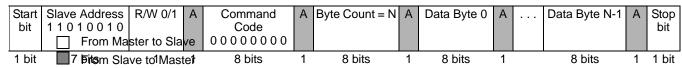

The clock driver serial protocol accepts only block writes from the controller. The bytes must be accessed in sequential order from lowest to highest byte, (most significant bit first) with the ability to stop after any complete byte has been transferred. Indexed bytes are not allowed.

A block write begins with a slave address and a WRITE condition. The R/W bit is used by the SMBus controller as a data direction bit. A zero indicates a WRITE condition to the clock device. The slave receiver address is 11010010 (D2h).

A command code of 0000 0000 (00h) and the byte count bytes are required for any transfer. After the command code, the core logic issues a byte count which describes number of additional bytes required for the transfer, not including the command code and byte count bytes. For example, if the host has 20 data bytes to send, the first byte would be the number 20 (14h), followed by the 20 bytes of data. The byte count byte is required to be a minimum of 1 byte and a maximum of 32 bytes It may not be 0. *Figure 1* shows an example of a block write.

A transfer is considered valid after the acknowledge bit corresponding to the byte count is read by the controller.

Figure 1.

Figure 1. An Example of a Block Write

#### **Data Byte Configuration Map**

#### Data Byte 0: Control Register (0 = Enable, 1 = Disable)

| Bit   | Affected<br>Pin#                                     | Name                               | Description                                                        | Туре | Power On<br>Default |

|-------|------------------------------------------------------|------------------------------------|--------------------------------------------------------------------|------|---------------------|

| Bit 7 | 5, 6, 7, 10,<br>11, 12, 13,<br>16, 17, 18,<br>33, 35 | PCI [0:6]<br>CPU[2:0]<br>3V66[1:0] | Spread Spectrum Enable<br>0 = Spread Off, 1 = Spread On            | R/W  | 0                   |

| Bit 6 | _                                                    | TBD                                | TBD                                                                | R    | 0                   |

| Bit 5 | 35                                                   | 3V66_1/VCH                         | VCH Select 66 MHz/48 MHz<br>0 = 66 MHz, 1 = 48 MHz                 | R/W  | 0                   |

| Bit 4 | 44, 45, 48,<br>49, 51, 52                            | CPU [2:0]<br>CPU# [2:0]            | CPU_STOP# Reflects the current value of the external CPU_STOP# pin | R    | N/A                 |

| Bit 3 | 10, 11, 12,<br>13, 16, 17,<br>18                     | PCI [6:0]                          | PCI_STOP#<br>(Does not affect PCI_F [2:0] pins)                    | R/W  | N/A                 |

| Bit 2 | _                                                    | -                                  | S2<br>Reflects the value of the S2 pin sampled on power-up         | R    | N/A                 |

| Bit 1 | _                                                    | _                                  | S1 Reflects the value of the S1 pin sampled on power-up            | R    | N/A                 |

| Bit 0 | -                                                    | -                                  | S0<br>Reflects the value of the S1 pin sampled on power-up         | R    | N/A                 |

# Data Byte 1

| Bit   | Pin#       | Name          | Description                                                                              | Туре | Power On<br>Default |

|-------|------------|---------------|------------------------------------------------------------------------------------------|------|---------------------|

| Bit 7 | _          | N/A           | CPU Mult0 Value                                                                          | R    | N/A                 |

| Bit 6 | 52, 49, 45 | CPU0:2        | Three-State CPU0:2 during power down 0 = Normal; 1 = Three-stated                        | R/W  | 0                   |

| Bit 5 | 44, 45     | CPU2<br>CPU2# | Allow Control of CPU2 with assertion of CPU_STOP# 0 = Not free running; 1 = Free running | R/W  | 0                   |

| Bit 4 | 48, 49     | CPU1<br>CPU1# | Allow Control of CPU1 with assertion of CPU_STOP# 0 = Not free running;1 = Free running  | R/W  | 0                   |

| Bit 3 | 51, 52     | CPU0<br>CPU0# | Allow Control of CPU0 with assertion of CPU_STOP# 0= Not free running; 1 = Free running  | R/W  | 0                   |

| Bit 2 | 44, 45     | CPU2<br>CPU2# | CPU2 Output Enable<br>1 = Enabled; 0 = Disabled                                          | R/W  | 1                   |

| Bit 1 | 48, 49     | CPU1<br>CPU1# | CPU1Output Enable<br>1 = Enabled; 0= Disabled                                            | R/W  | 1                   |

| Bit 0 | 51, 52     | CPU0<br>CPU0# | CPU0 Output Enable<br>1 = Enabled; 0 = Disabled                                          | R/W  | 1                   |

## Data Byte 2

| Bit   | Pin# | Name | Pin Description                                 | Туре | Power On<br>Default |

|-------|------|------|-------------------------------------------------|------|---------------------|

| Bit 7 | _    | N/A  | N/A                                             | R    | 0                   |

| Bit 6 | 18   | PCI6 | PCI6 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 5 | 17   | PCI5 | PCI5 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 4 | 16   | PCI4 | PCI4 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 3 | 13   | PCI3 | PCI3 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 2 | 12   | PCI2 | PCI2 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 1 | 11   | PCI1 | PCI1 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

| Bit 0 | 10   | PCI0 | PCI0 Output Enable<br>1 = Enabled; 0 = Disabled | R/W  | 1                   |

## Data Byte 3

| Bit   | Pin# | Name   | Pin Description                                                                                  | Туре | Power On<br>Default |

|-------|------|--------|--------------------------------------------------------------------------------------------------|------|---------------------|

| Bit 7 | 38   | DOT    | DOT 48-MHz Output Enable                                                                         | R/W  | 1                   |

| Bit 6 | 39   | USB    | USB 48-MHz Output Enable                                                                         | R/W  | 1                   |

| Bit 5 | 7    | PCI_F2 | Allow control of PCI_F2 with assertion of PCI_STOP# 0 = Free running; 1 = Stopped with PCI_STOP# | R/W  | 0                   |

| Bit 4 | 6    | PCI_F1 | Allow control of PCI_F1 with assertion of PCI_STOP# 0 = Free running; 1 = Stopped with PCI_STOP# | R/W  | 0                   |

| Bit 3 | 5    | PCI_F0 | Allow control of PCI_F0 with assertion of PCI_STOP# 0 = Free running; 1 = Stopped with PCI_STOP# | R/W  | 0                   |

| Bit 2 | 7    | PCI_F2 | PCI_F2 Output Enable                                                                             | R/W  | 1                   |

| Bit 1 | 6    | PCI_F1 | PCI_F1Output Enable                                                                              | R/W  | 1                   |

| Bit 0 | 5    | PCI_F0 | PCI_F0 Output Enable                                                                             | R/W  | 1                   |

# Data Byte 4

| Bit   | Pin# | Name        | Pin Description                                                                                                                                                                       | Туре | Power On<br>Default |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|

| Bit 7 | _    | TBD         | N/A                                                                                                                                                                                   | R    | 0                   |

| Bit 6 | _    | TBD         | N/A                                                                                                                                                                                   | R    | 0                   |

| Bit 5 | 33   | 3V66_0      | 3V66_0 Output Enable<br>1 = Enabled; 0 = Disabled                                                                                                                                     | R/W  | 1                   |

| Bit 4 | 35   | 3V66_1/VCH  | 3V66_1/VCH Output Enable<br>1 = Enabled; 0 = Disabled                                                                                                                                 | R/W  | 1                   |

| Bit 3 | 24   | 66IN/3V66_5 | 3V66_5 Output Enable 1 = Enable; 0 = Disable NOTE: This bit should be used when pin 24 is configured as 3v66_5 output. Do not clear this bit when pin 24 is configured as 66in input. | R/W  | 1                   |

| Bit 2 | 23   | 66BUFF2     | 66-MHz Buffered 2 Output Enable<br>1 = Enabled; 0 = Disabled                                                                                                                          | R/W  | 1                   |

| Bit 1 | 22   | 66BUFF1     | 66-MHz Buffered 1 Output Enable<br>1 = Enabled; 0 = Disabled                                                                                                                          |      | 1                   |

| Bit 0 | 21   | 66BUFF0     | 66-MHz Buffered 0 Output Enable<br>1 = Enabled; 0 = Disabled                                                                                                                          | R/W  | 1                   |

## Data Byte 5

| Bit   | Pin# | Name         | Pin Description                              | Туре | Power On<br>Default |

|-------|------|--------------|----------------------------------------------|------|---------------------|

| Bit 7 |      | N/A          | N/A                                          | R    | 0                   |

| Bit 6 |      | N/A          | N/A                                          | R    | 0                   |

| Bit 5 |      | 66BUFF [2:0] | Tpd 66IN to 66BUFF propagation delay control | R/W  | 0                   |

| Bit 4 |      | 66BUFF [2:0] |                                              | R/W  | 0                   |

| Bit 3 |      | DOT          | DOT edge rate control                        | R/W  | 0                   |

| Bit 2 |      | DOT          |                                              | R/W  | 0                   |

| Bit 1 |      | USB          | USB edge rate control                        | R/W  | 0                   |

| Bit 0 |      | USB          |                                              | R/W  | 0                   |

# Byte 6: Vendor ID

| Bit   | Description         | Туре | Power On Default |

|-------|---------------------|------|------------------|

| Bit 7 | Revision Code Bit 3 | R    | 0                |

| Bit 6 | Revision Code Bit 2 | R    | 0                |

| Bit 5 | Revision Code Bit 1 | R    | 0                |

| Bit 4 | Revision Code Bit 0 | R    | 0                |

| Bit 3 | Vendor ID Bit 3     | R    | 1                |

| Bit 2 | Vendor ID Bit 2     | R    | 0                |

| Bit 1 | Vendor ID Bit 1     | R    | 0                |

| Bit 0 | Vendor ID Bit 0     | R    | 0                |

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Supply Voltage......-0.5 to +7.0V

| Storage Temperature (Non-Condensing)–65°C to +150°C             |

|-----------------------------------------------------------------|

| Max. Soldering Temperature (10 sec) +260°C                      |

| Junction Temperature+150°C                                      |

| Package Power Dissipation1 $\Omega$                             |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) > 2000V |

# Operating Conditions<sup>[8]</sup> Over which Electrical Parameters are Guaranteed

| Parameter                                                                                                         | Description                                      | Min.   | Max.     | Unit |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|----------|------|

| V <sub>DD_REF</sub> , V <sub>DD_PCI</sub> ,V <sub>DD_CORE</sub> ,<br>V <sub>DD_3V66</sub> , V <sub>DD_CPU</sub> , | 3.3V Supply Voltages                             | 3.135  | 3.465    | V    |

| V <sub>DD_48 MHz</sub>                                                                                            | 48-MHz Supply Voltage                            | 2.85   | 3.465    | V    |

| T <sub>A</sub>                                                                                                    | Operating Temperature, Ambient                   | 0      | 70       | °C   |

| C <sub>in</sub>                                                                                                   | Input Pin Capacitance                            |        | 5        | pF   |

| C <sub>XTAL</sub>                                                                                                 | XTAL Pin Capacitance                             |        | 22.5     | pF   |

| CL                                                                                                                | Max. Capacitive Load on USBCLK, REF PCICLK, 3V66 |        | 20<br>30 | pF   |

| f <sub>(REF)</sub>                                                                                                | Reference Frequency, Oscillator Nominal Value    | 14.318 | 14.318   | MHz  |

## **Electrical Characteristics** Over the Operating Range

| Parameter          | Description               | Test Conditions                                                              |                                  | Min.       | Max. | Unit |

|--------------------|---------------------------|------------------------------------------------------------------------------|----------------------------------|------------|------|------|

| V <sub>IH</sub>    | High-level Input Voltage  | Except Crystal Pads. Threshold Voltage for Crystal Pads = V <sub>DD</sub> /2 |                                  | 2.0        |      | V    |

| $V_{IL}$           | Low-level Input Voltage   | Except Crystal Pads                                                          |                                  |            | 0.8  | V    |

| V <sub>OH</sub>    | High-level Output Voltage | USB, REF, 3V66                                                               | I <sub>OH</sub> = -1 mA          | 2.4        |      | V    |

|                    |                           | PCI                                                                          | I <sub>OH</sub> = -1 mA          | 2.4        |      | V    |

| $V_{OL}$           | Low-level Output Voltage  | USB, REF, 3V66                                                               | I <sub>OL</sub> = 1 mA           |            | 0.4  | V    |

|                    |                           | PCI                                                                          | I <sub>OL</sub> = 1 mA           |            | 0.55 | V    |

| I <sub>IH</sub>    | Input HIGH Current        | $0 \le V_{IN} \le V_{DD}$                                                    |                                  | <b>-</b> 5 | 5    | mA   |

| $I_{\parallel L}$  | Input LOW Current         | $0 \le V_{IN} \le V_{DD}$                                                    |                                  | <b>-</b> 5 | 5    | mA   |

| I <sub>OH</sub>    | High-level Output Current | CPU<br>For I <sub>OH</sub> =6*IRef Configuration                             | Type X1, V <sub>OH</sub> = 0.65V | 12.9       |      | mΑ   |

|                    |                           |                                                                              | Type X1, $V_{OH} = 0.74V$        |            | 14.9 |      |

|                    |                           | REF, DOT, USB                                                                | Type 3, V <sub>OH</sub> = 1.00V  | -29        |      |      |

|                    |                           |                                                                              | Type 3, $V_{OH} = 3.135V$        |            | -23  |      |

|                    |                           | 3V66, DOT, PCI, REF                                                          | Type 5, V <sub>OH</sub> = 1.00V  | -33        |      |      |

|                    |                           |                                                                              | Type 5, $V_{OH} = 3.135V$        |            | -33  |      |

| I <sub>OL</sub>    | Low-level Output Current  | REF, DOT, USB                                                                | Type 3, V <sub>OL</sub> = 1.95V  | 29         |      | mA   |

|                    |                           |                                                                              | Type 3, V <sub>OL</sub> = 0.4V   |            | 27   |      |

|                    |                           | 3V66, PCI, REF                                                               | Type 5, V <sub>OL</sub> = 1.95 V | 30         |      |      |

|                    |                           |                                                                              | Type 5, V <sub>OL</sub> = 0.4V   |            | 38   |      |

| I <sub>OZ</sub>    | Output Leakage Current    | Three-state                                                                  |                                  |            | 10   | mΑ   |

| I <sub>DD3</sub>   | 3.3V Power Supply Current | VDD_CORE/VDD3.3 = 3.465V, F <sub>CPU</sub> = 133 MHz                         |                                  |            | 360  | mA   |

| I <sub>DDPD3</sub> | 3.3V Shut-down Current    | VDD_CORE/VDD3.3 = 3.465V and @ IREF = 2.32 mA                                |                                  |            | 25   | mΑ   |

| I <sub>DDPD3</sub> | 3.3V Shut-down Current    | VDD_CORE/VDD3.3 = 3.465V and @ IREF = 5.0 mA                                 |                                  |            | 45   | mA   |

#### Note:

Rev 1.0, November 25, 2006 Page 7 of 16

<sup>8.</sup> The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

# Switching Characteristics[9] Over the Operating Range

| Parameter                          | Output          | Description                                   | Test Conditions                                                           | Min. | Max.  | Unit |

|------------------------------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------|------|-------|------|

| t <sub>1</sub>                     | All             | Output Duty Cycle <sup>[10]</sup>             | Measured at 1.5V                                                          | 45   | 55    | %    |

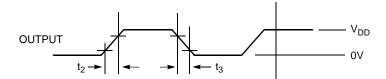

| t <sub>3</sub>                     | USB, REF, DOT   | Falling Edge Rate                             | Between 2.4V and 0.4V                                                     | 0.5  | 2.0   | ns   |

| t <sub>3</sub>                     | PCI,3V66        | Falling Edge Rate                             | Between 2.4V and 0.4V                                                     | 1.0  | 4.0   | V/ns |

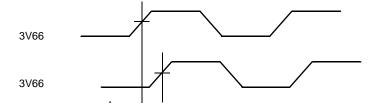

| t <sub>5</sub>                     | 3V66[0:1]       | 3V66-3V66 Skew                                | Measured at 1.5V                                                          |      | 500   | ps   |

| t <sub>5</sub>                     | 66BUFF[0:2]     | 66BUFF-66BUFF Skew                            | Measured at 1.5V                                                          |      | 175   | ps   |

| t <sub>6</sub>                     | PCI             | PCI-PCI Skew                                  | Measured at 1.5V                                                          |      | 500   | ps   |

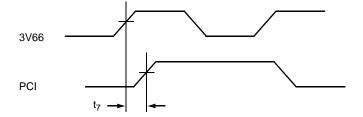

| t <sub>7</sub>                     | 3V66, PCI       | 3V66-PCI Clock Jitter                         | 3V66 leads. Measured at 1.5V                                              | 1.5  | 3.5   | ns   |

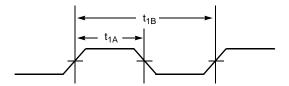

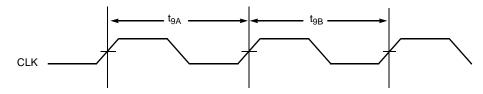

| t <sub>9</sub>                     | 3V66            | Cycle-Cycle Clock Jitter                      | Measured at 1.5V t <sub>9</sub> = t <sub>9A</sub> - t <sub>9B</sub>       |      | 250   | ps   |

| t <sub>9</sub>                     | USB, DOT        | Cycle-Cycle Clock Jitter                      | Measured at 1.5V t <sub>9</sub> = t <sub>9A</sub> - t <sub>9B</sub>       |      | 350   | ps   |

| t <sub>9</sub>                     | PCI             | Cycle-Cycle Clock Jitter                      | Measured at 1.5V t <sub>9</sub> = t <sub>9A</sub> - t <sub>9B</sub>       |      | 500   | ps   |

| t <sub>9</sub>                     | REF             | Cycle-Cycle Clock Jitter                      | Measured at 1.5V t <sub>9</sub> = t <sub>9A</sub> - t <sub>9B</sub>       |      | 1000  | ps   |

| CPU 1.0V S                         | witching Charac | teristics                                     |                                                                           | •    | •     |      |

| t <sub>2</sub>                     | CPU             | Rise Time                                     | Measured differential waveform from –0.35V to +0.35V                      | 175  | 467   | ps   |

| t <sub>3</sub>                     | CPU             | Fall Time                                     | Measured differential waveform from<br>-0.35V to +0.35V                   | 175  | 467   | ps   |

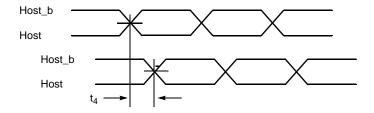

| t <sub>4</sub>                     | CPU             | CPU-CPU Skew                                  | Measured at Crossover                                                     |      | 150   | ps   |

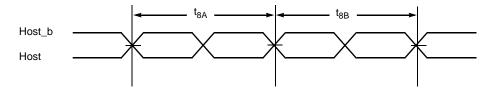

| t <sub>8</sub>                     | CPU             | Cycle-Cycle Clock Jitter                      | Measured at Crossover t <sub>8</sub> = t <sub>8A</sub> - t <sub>8B</sub>  |      | 150   | ps   |

|                                    | CPU             | Rise/Fall Matching                            | Measured with test loads <sup>[11]</sup>                                  |      | 325   | mV   |

| V <sub>oh</sub>                    | CPU             | High-level Output Voltage including overshoot | Measured with test loads <sup>[11]</sup>                                  | 0.92 | 1.45  | V    |

| V <sub>ol</sub>                    | CPU             | Low-level Output Voltage including undershoot | Measured with test loads <sup>[11]</sup>                                  | -0.2 | 0.35  | V    |

| V <sub>crossover</sub>             | CPU             | Crossover Voltage                             | Measured with test loads <sup>[11]</sup>                                  | 0.51 | 0.76  | V    |

| CPU 0.7V Switching Characteristics |                 |                                               |                                                                           |      |       |      |

| t <sub>2</sub>                     | CPU             | Rise Time                                     | Measured single ended waveform from 0.175V to 0.525V                      | 175  | 700   | ps   |

| t <sub>3</sub>                     | CPU             | Fall Time                                     | Measured single ended waveform from 0.175V to 0.525V                      | 175  | 700   | ps   |

| t <sub>4</sub>                     | CPU             | CPU-CPU Skew                                  | Measured at Crossover                                                     |      | 150   | ps   |

| t <sub>8</sub>                     | CPU             | Cycle-Cycle Clock Jitter                      | Measured at Crossover $t_8 = t_{8A} - t_{8B}$<br>With all outputs running |      | 150   | ps   |

|                                    | CPU             | Rise/Fall Matching                            | Measured with test loads <sup>[12, 13]</sup>                              |      | 20    | %    |

| V <sub>oh</sub>                    | CPU             | High-level Output Voltage Including Overshoot | Measured with test loads <sup>[13]</sup>                                  |      | 0.85  | V    |

| V <sub>ol</sub>                    | CPU             | Low-level Output Voltage Including Undershoot | Measured with test loads <sup>[13]</sup>                                  |      | -0.15 | V    |

| V <sub>crossover</sub>             | CPU             | Crossover Voltage                             | Measured with test loads <sup>[13]</sup>                                  | 0.28 | 0.43  | V    |

## Notes:

<sup>9.</sup> All parameters specified with loaded outputs.

10. Duty cycle is measured at 1.5V when V<sub>DD</sub> = 3.3V. When V<sub>DD</sub> = 2.5V, duty cycle is measured at 1.25V.

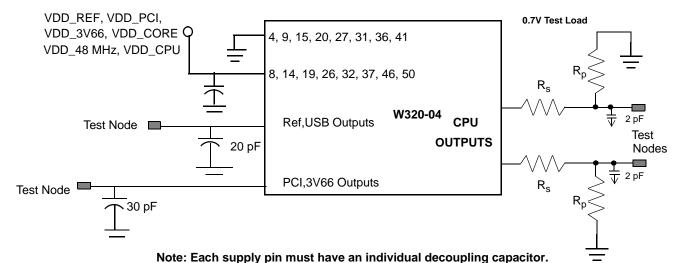

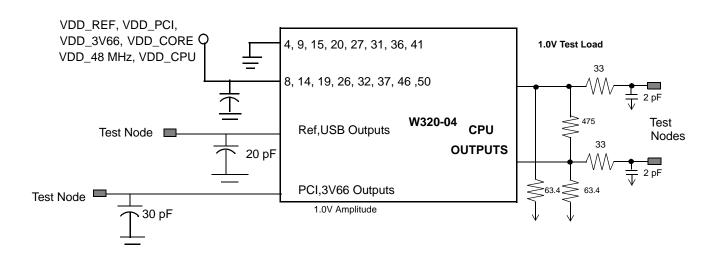

11. The 1.0V test load is shown on the test circuit page.

12. Determined as a fraction of 2\*(Trp – Trn)/(Trp +Trn) Where Trp is a rising edge and Trp is an intersecting falling edge.

13. The 0.7V test load is R<sub>s</sub> = 33.2 ohm, R<sub>p</sub> = 49.9 ohm in test circuit.

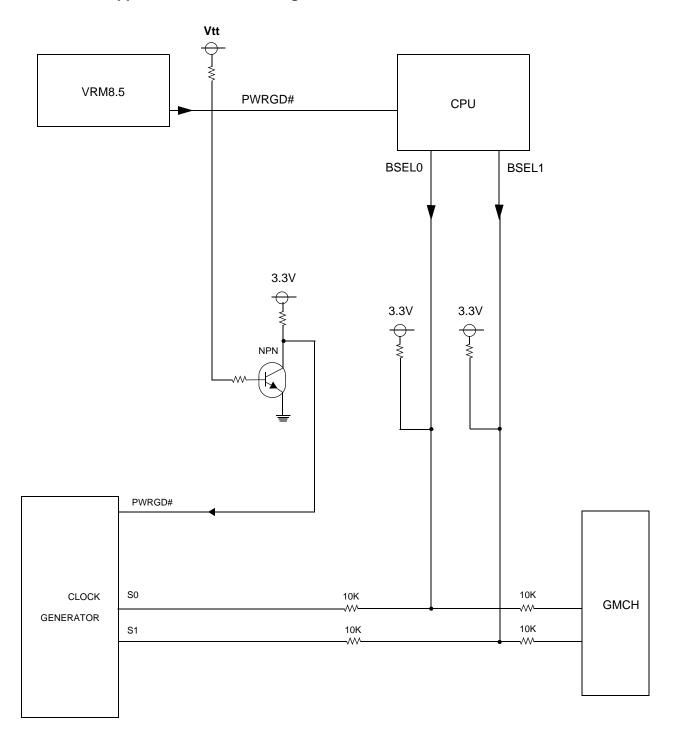

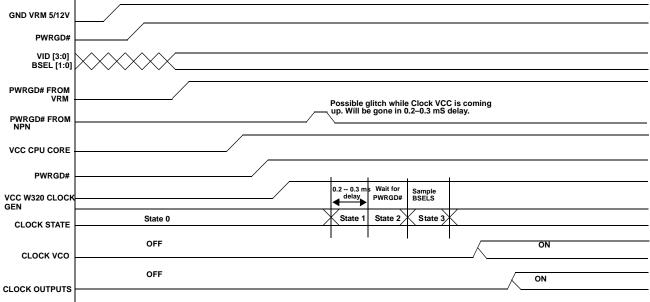

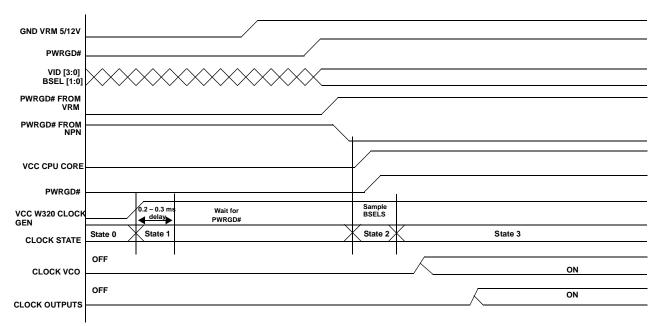

# **Definition and Application of PWRGD# Signal**

# **Switching Waveforms**

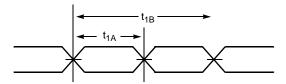

## **Duty Cycle Timing (Single-ended Output)**

## **Duty Cycle Timing (CPU Differential Output)**

#### All Outputs Rise/Fall Time

## **CPU-CPU Clock Skew**

#### 3V66-3V66 Clock Skew

## **PCI-PCI Clock Skew**

# Switching Waveforms (continued)

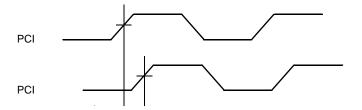

#### **3V66-PCI Clock Skew**

# **CPU Clock Cycle-Cycle Jitter**

## **Cycle-Cycle Clock Jitter**

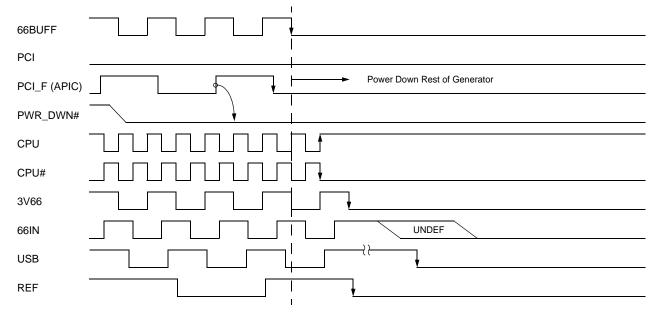

## **PWRDWN# Assertion**

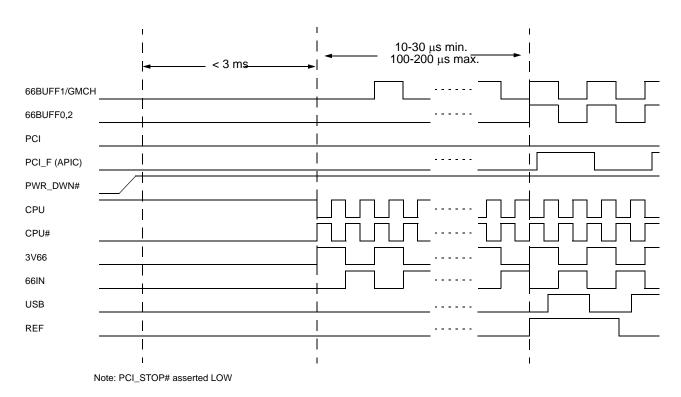

Note: PCI\_STOP# asserted LOW

#### **PWRDWN#** Deassertion

## **PWRGD# Timing Diagrams**

Figure 2. CPU Power Before Clock Power

Figure 3. CPU Power After Clock Power

# **Layout Example**

FB = Dale ILB1206 - 300 or 2TDKACB2012L-120 or 2 Murata BLM21B601S.

Ceramic Caps C1 = 10–22  $\mu F$  C2 = 0.005  $\mu F$  C5 = 0.1  $\mu F$  C6 = 10  $\mu F$  G = VIA to GND plane layer.  $\hat{V}$  = VIA to respective supply plane layer.

Note: Each supply plane or strip should have a ferrite bead and capacitors.

#### **Test Circuit**

Note: Each supply pin must have an individual decoupling capacitor.  $\blacksquare$ Note: All capacitors must be placed as close to the pins as is physically possible. 0.7V amplitude:  $R_S = 33$  ohm,  $R_P = 50$  ohm

#### **Ordering Information**

| Ordering Code | Package Type                 | Operating Range        |

|---------------|------------------------------|------------------------|

| W320-04H      | 56-pin SSOP                  | Commercial 0°C TO 70°C |

| W320-04HT     | 56-pin SSOP - Tape and Reel  | Commercial 0°C TO 70°C |

| W320-04X      | 56-pin TSSOP                 | Commercial 0°C TO 70°C |

| W320-04XT     | 56-pin TSSOP - Tape and Reel | Commercial 0°C TO 70°C |

| Lead-Free     | ·                            |                        |

| CYW320OXC-4   | 56-pin SSOP                  | Commercial 0°C TO 70°C |

| CYW320OXC-4T  | 56-pin SSOP - Tape and Reel  | Commercial 0°C TO 70°C |

| CYW320ZXC-4   | 56-pin TSSOP                 | Commercial 0°C TO 70°C |

| CYW320ZXC-4T  | 56-pin TSSOP - Tape and Reel | Commercial 0°C TO 70°C |

Rev 1.0, November 25, 2006

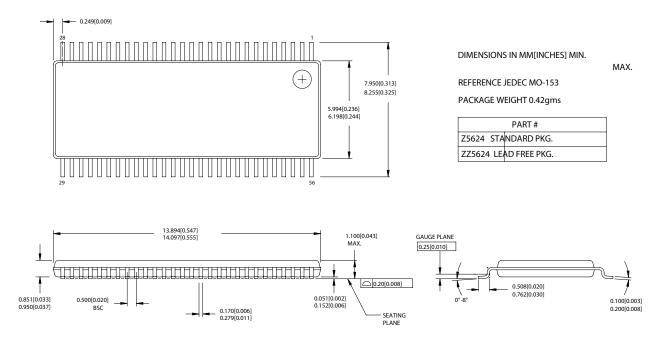

#### **Package Diagrams**

#### 56-Lead Shrunk Small Outline Package O56

56-Lead Thin Shrunk Small Outline Package, Type II (6 mm x 12 mm) Z56

While SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any circuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other application requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.

Rev 1.0, November 25, 2006 Page 16 of 16