# QUICKSWITCH<sup>®</sup> PRODUCTS LAST VALUE LATCH 20 ACTIVE BUS TERMINATORS (BUS HOLD)

# IDTQS3389

## FEATURES:

- · Active termination pulls bus pins to rails

- · Holds last value of input signal

- Ideal replacement for resistive termination

- Ultra low 3µA DC quiescent current

- Bus-hold eliminates floating bus lines and reduces static power consumption

- · Low power QCMOS technology

- Operates over 2.7V to 5.5V Vcc range

- TTL-compatible input and output levels

- No added noise or ground bounce

- 20 independent terminator circuits

- Available in QSOP package

## **APPLICATIONS:**

- Bus termination

- Extend data hold time

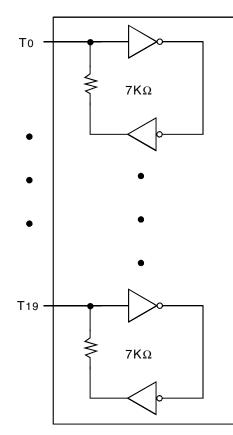

# FUNCTIONAL BLOCK DIAGRAM

# DESCRIPTION:

The QS3389 provides a set of 20 active termination circuits which pull data bus signals to the voltage rails. This feature prevents bus signals from floating in the threshold region of standard TTL I/O devices. The QS3389 can replace resistor termination solutions which add DC power dissipation and increase component count. Input clamp diodes help to reduce reflections and undershoot in transmission line environments. Importantly, the terminator circuits pull signals to whichever logic state the signal previously held (high or low). For this reason, this device is also referred to as a last value latch. This device is appropriate for data bus applications where interfacing devices have CMOS inputs with low input currents. These terminators provide sufficient drive to overcome leakage currents and drive corresponding signals away from the TTL threshold region.

The QS3389 is characterized for operation at 0°C to +70°C.

$\label{eq:constraint} The \, \text{IDT}\, \text{logo}\, \text{is}\, a\, \text{registered}\, \text{trademark}\, of\, \text{Integrated}\, \text{Device}\, \text{Technology}, \, \text{Inc}.$

COMMERCIAL TEMPERATURE RANGE

#### LAST VALUE LATCH 20 ACTIVE TERMINATORS (BUS HOLD)

#### **COMMERCIAL TEMPERATURE RANGE**

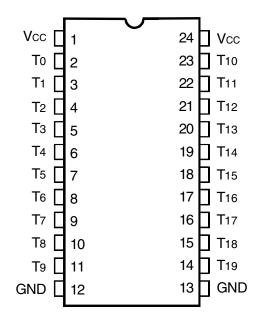

## PINCONFIGURATION

QSOP TOP VIEW

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol               | Description                             | Мах         | Unit |  |

|----------------------|-----------------------------------------|-------------|------|--|

| VTERM <sup>(2)</sup> | Supply Voltage to Ground                | –0.5 to +7  | V    |  |

| VTERM <sup>(3)</sup> | DC Switch Voltage Vs -0.5 to +7         |             |      |  |

| VAC                  | AC Input Voltage (pulse width ≤20ns) –3 |             | V    |  |

| Ιουτ                 | DC Output Current                       | 120         | mA   |  |

| Рмах                 | Maximum Power Dissipation (TA = 85°C)   | 0.5         | W    |  |

| Tstg                 | Storage Temperature                     | -65 to +150 | °C   |  |

NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Vcc terminals.

3. All terminals except Vcc .

#### CAPACITANCE (TA = $+25^{\circ}$ C, f = 1MHz, VIN = 0V, VOUT = 0V)

| Pins   | Тур. | Max. <sup>(1)</sup> | Unit |

|--------|------|---------------------|------|

| T19-T0 | 3    | 4                   | pF   |

NOTE:

1. This parameter is guaranteed but not production tested.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Commercial: TA =  $0^{\circ}$ C to +70°C, VCC = 5V ± 5%

| Symbol | Parameter                                          | Test Conditions                        | Min. | Тур. <sup>(1)</sup> | Max.                | Unit |

|--------|----------------------------------------------------|----------------------------------------|------|---------------------|---------------------|------|

| Vih    | Input HIGH Voltage                                 | Guaranteed Logic HIGH for Control Pins | 2    | —                   | _                   | V    |

| VIL    | Input LOW Voltage                                  | Guaranteed Logic LOW for Control Pins  | —    | —                   | 0.8                 | V    |

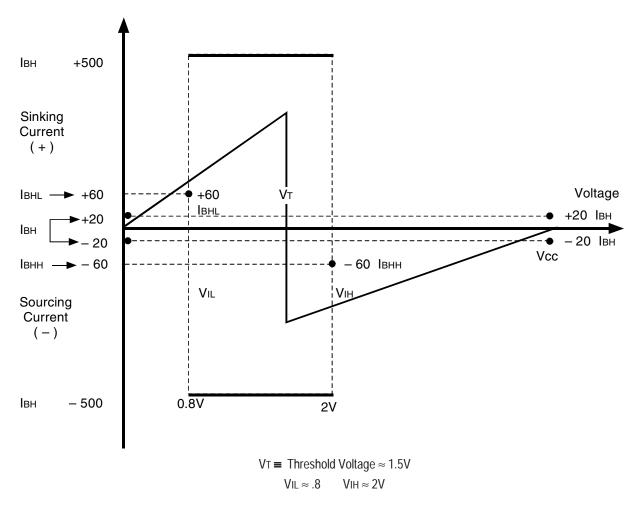

| Vт     | Threshold Voltage                                  |                                        | —    | 1.5                 | -                   | V    |

| lin    | Input Leakage Current <sup>(2)</sup>               | VIN = Vcc or GND                       | —    | —                   | ±5                  | μA   |

| Івн    | Input Current <sup>(5)</sup>                       | Vcc = Max., VIN = 0V or Vcc            | _    | _                   | ±20                 | μA   |

|        | Input HIGH or LOW Bus Hold Inputs <sup>(2,3)</sup> | Vcc = Max., 0.8V < VIN < 2V            | _    | _                   | ±500 <sup>(4)</sup> |      |

| Івнн   | Bus Hold Sustaining Current <sup>(6,7)</sup>       | Vcc = Min., VIN = 2V                   | -60  | —                   | _                   | μA   |

| Ibhl   | Bus Hold Inputs                                    | Vcc = Min., VIN = 0.8V                 | +60  | —                   | _                   | μA   |

| Rτ     | Terminator Resistance                              |                                        | —    | 7k                  | _                   | Ω    |

#### NOTES:

1. Typical values are at Vcc = 5.0V, TA =  $25^{\circ}C$ .

- 2. Trip current definition (see Functional Block Diagram):

- An external driver must source at least ITL to switch the node from LOW to HIGH.

An external driver must sink at least ITH to switch the node from HIGH to LOW.

3. Hold current definition (see Functional Block Diagram):

- $I_{\rm HH}\,$  is the Maximum Curent the QS3389 can sink without raising the node above ViL max.

- $I{\scriptscriptstyle HL}\,$  is the Maximum Curent the QS3389 can source without lowering the node below V\_IH min.

- 4. An external driver must provide at least IBH during transition to guarantee that the Bus-Hold input will change states.

- 5.  $\ensuremath{\mathsf{IBH}}$  is the magnitude of the input current specified under two conditions:

- a) Input voltage at GND or Vcc. This indicates the input current under steady-state condition.

- b) Input voltage between 0.8V and 2V (TTL input threshold range). This indicates the maximum input current during transient condition. The driver connected to the input must overcome this current requirement in order to switch the logic state of the bus-hold circuit.

6. IBHL is the minimum sustaining "sink" current at the input for VIN = 0.8V. This parameter signifies the latching capability of the bus-hold circuit in logic LOW state.

7. IBHH is the minimum sustaining "source" current at the input for VIN = 2V. This parameter signifies the latching capability of the bus-hold circuit in logic HIGH state.

## **POWER SUPPLY CHARACTERISTICS**

| Symbo | Parameter                      | Test Conditions <sup>(1)</sup>      | Max. | Unit |

|-------|--------------------------------|-------------------------------------|------|------|

| lcco  | Quiescent Power Supply Current | Vcc = Max., VIN = GND or Vcc, f = 0 | 1.5  | mA   |

#### NOTE:

1. For conditions shown as Min. or Max., use the appropriate values specified under DC Electrical Characteristics.

## ACTIVE TERMINATOR OR 'BUS-HOLD' CIRCUIT

The Active Terminator circuit, also known as the Bus-hold circuit, is configured as a "weak latch" with positive feedback. When connected to a TTL or CMOS input port, the Bus-hold circuit holds the last logic state at the input when the input is "disconnected" from the driver. When the output of a device connected to such an input attempts a logic level transition, it will over-drive the Bus-hold circuit. The primary benefit of this circuit is that it prevents CMOS inputs from floating, a situation which should be avoided to prevent spurious switching of inputs and unnecessary power dissipation. Bus-hold is a better solution than the traditional approach of using resistive termination to Vcc or GND to prevent bus floating, because the Bus-hold circuit does not consume any static power.

# V-I CHARACTERISTICS OF BUS-HOLD CIRCUIT

The figure above shows the input V-I characteristics of a Bus-hold implementation. The input characteristics resemble a resistor. As the input voltage is increased from 0 volts, the 'sink' current increases linearly. When the TTL threshold of the circuit is reached (typically 1.5 volts), the latch changes the logic state due to positive feedback and the direction of current is reversed. As the voltage is further increased towards Vcc, the input 'source' current begins to decrease, reaching the lowest level at VIN = Vcc.

*CORPORATE HEADQUARTERS* 6024 Silver Creek Valley Road San Jose, CA 95138 for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com for Tech Support: logichelp@idt.com