# 12-Bit, 125 MSPS High Performance TxDAC® D/A Converter

AD9752\*

#### **FEATURES**

High Performance Member of Pin-Compatible TxDAC Product Family 125 MSPS Update Rate 12-Bit Resolution

Excellent Spurious Free Dynamic Range Performance

SFDR to Nyquist @ 5 MHz Output: 79 dBc Differential Current Outputs: 2 mA to 20 mA

Power Dissipation: 185 mW @ 5 V Power-Down Mode: 20 mW @ 5 V

On-Chip 1.20 V Reference

CMOS-Compatible +2.7 V to +5.5 V Digital Interface

Package: 28-Lead SOIC and TSSOP

**Edge-Triggered Latches**

### **APPLICATIONS**

**Wideband Communication Transmit Channel:**

Direct IF

Basestations

Wireless Local Loop

Digital Radio Link

Direct Digital Synthesis (DDS)

### PRODUCT DESCRIPTION

The AD9752 is a 12-bit resolution, wideband, second generation member of the TxDAC series of high performance, low power CMOS digital-to-analog-converters (DACs). The TxDAC family, which consists of pin compatible 8-, 10-, 12-, and 14-bit DACs, is specifically optimized for the transmit signal path of communication systems. All of the devices share the same interface options, small outline package and pinout, thus providing an upward or downward component selection path based on performance, resolution and cost. The AD9752 offers exceptional ac and dc performance while supporting update rates up to 125 MSPS.

The AD9752's flexible single-supply operating range of 4.5 V to 5.5 V and low power dissipation are well suited for portable and low power applications. Its power dissipation can be further reduced to a mere 65 mW, without a significant degradation in performance, by lowering the full-scale current output. Also, a power-down mode reduces the standby power dissipation to approximately 20 mW.

The AD9752 is manufactured on an advanced CMOS process. A segmented current source architecture is combined with a proprietary switching technique to reduce spurious components and enhance dynamic performance. Edge-triggered input latches and a 1.2 V temperature compensated bandgap reference have been integrated to provide a complete monolithic DAC solution. The digital inputs support +2.7 V to +5 V CMOS logic families.

TxDAC is a registered trademark of Analog Devices, Inc.

\*Protected by U.S. Patents Numbers 5450084, 5568145, 5689257, 5612697 and 5703519. Other patents pending.

### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

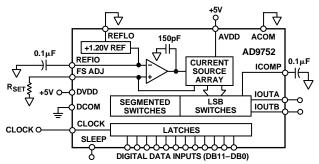

### **FUNCTIONAL BLOCK DIAGRAM**

The AD9752 is a current-output DAC with a nominal full-scale output current of 20 mA and > 100 k $\Omega$  output impedance.

Differential current outputs are provided to support single-ended or differential applications. Matching between the two current outputs ensures enhanced dynamic performance in a differential output configuration. The current outputs may be tied directly to an output resistor to provide two complementary, single-ended voltage outputs or fed directly into a transformer. The output voltage compliance range is 1.25 V.

The on-chip reference and control amplifier are configured for maximum accuracy and flexibility. The AD9752 can be driven by the on-chip reference or by a variety of external reference voltages. The internal control amplifier, which provides a wide (>10:1) adjustment span, allows the AD9752 full-scale current to be adjusted over a 2 mA to 20 mA range while maintaining excellent dynamic performance. Thus, the AD9752 may operate at reduced power levels or be adjusted over a 20 dB range to provide additional gain ranging capabilities.

The AD9752 is available in 28-lead SOIC and TSSOP packages. It is specified for operation over the industrial temperature range.

### PRODUCT HIGHLIGHTS

- 1. The AD9752 is a member of the wideband TxDAC product family that provides an upward or downward component selection path based on resolution (8 to 14 bits), performance and cost. The entire family of TxDACs is available in industry standard pinouts.

- Manufactured on a CMOS process, the AD9752 uses a proprietary switching technique that enhances dynamic performance beyond that previously attainable by higher power/cost bipolar or BiCMOS devices.

- 3. On-chip, edge-triggered input CMOS latches interface readily to +2.7 V to +5 V CMOS logic families. The AD9752 can support update rates up to 125 MSPS.

- 4. A flexible single-supply operating range of 4.5 V to 5.5 V and a wide full-scale current adjustment span of 2 mA to 20 mA allow the AD9752 to operate at reduced power levels.

- 5. The current output(s) of the AD9752 can be easily configured for various single-ended or differential circuit topologies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

## AD9752-SPECIFICATIONS

# $\textbf{DC SPECIFICATIONS} \text{ ($T_{MIN}$ to $T_{MAX}$, $AVDD = +5$ V$, $DVDD = +5$ V$, $I_{OUTFS} = 20$ mA, unless otherwise noted)}$

| Parameter                                                                                                                                                                                     | Min                              | Тур                        | Max                               | Units                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------------------|-----------------------------------------------------------|

| RESOLUTION                                                                                                                                                                                    | 12                               |                            |                                   | Bits                                                      |

| DC ACCURACY <sup>1</sup> Integral Linearity Error (INL)                                                                                                                                       |                                  |                            |                                   |                                                           |

| $T_A = +25^{\circ}C$ $T_{MIN}$ to $T_{MAX}$ Differential Nonlinearity (DNL)                                                                                                                   | -1.5<br>-2.0                     | ±0.5                       | +1.5<br>+2.0                      | LSB<br>LSB                                                |

| $T_A = +25^{\circ}C$ $T_{MIN}$ to $T_{MAX}$                                                                                                                                                   | -0.75<br>-1.0                    | ±0.25                      | +0.75<br>+1.0                     | LSB<br>LSB                                                |

| ANALOG OUTPUT                                                                                                                                                                                 |                                  |                            |                                   |                                                           |

| Offset Error Gain Error (Without Internal Reference) Gain Error (With Internal Reference) Full-Scale Output Current <sup>2</sup> Output Compliance Range Output Resistance Output Capacitance | -0.02<br>-2<br>-5<br>2.0<br>-1.0 | ±0.5<br>±1.5               | +0.02<br>+2<br>+5<br>20.0<br>1.25 | % of FSR<br>% of FSR<br>% of FSR<br>mA<br>V<br>kΩ<br>pF   |

| REFERENCE OUTPUT Reference Voltage Reference Output Current <sup>3</sup>                                                                                                                      | 1.14                             | 1.20<br>100                | 1.26                              | V<br>nA                                                   |

| REFERENCE INPUT Input Compliance Range Reference Input Resistance Small Signal Bandwidth                                                                                                      | 0.1                              | 1<br>0.5                   | 1.25                              | V<br>MΩ<br>MHz                                            |

| TEMPERATURE COEFFICIENTS Offset Drift Gain Drift (Without Internal Reference) Gain Drift (With Internal Reference) Reference Voltage Drift                                                    |                                  | 0<br>±50<br>±100<br>±50    |                                   | ppm of FSR/°C<br>ppm of FSR/°C<br>ppm of FSR/°C<br>ppm/°C |

| POWER SUPPLY<br>Supply Voltages                                                                                                                                                               |                                  |                            |                                   |                                                           |

| AVDD DVDD  Analog Supply Current $(I_{AVDD})^4$ Digital Supply Current $(I_{DVDD})^5$ Supply Current Sleep Mode $(I_{AVDD})^6$                                                                | 4.5<br>2.7                       | 5.0<br>5.0<br>34<br>3<br>4 | 5.5<br>5.5<br>39<br>5<br>8        | V<br>V<br>mA<br>mA<br>mA                                  |

| Power Dissipation <sup>5</sup> (5 V, I <sub>OUTFS</sub> = 20 mA) Power Supply Rejection Ratio <sup>7</sup> —AVDD Power Supply Rejection Ratio <sup>7</sup> —DVDD                              | -0.4<br>-0.025                   | 185                        | 220<br>+0.4<br>+0.025             | mW<br>% of FSR/V<br>% of FSR/V                            |

| OPERATING RANGE                                                                                                                                                                               | -40                              |                            | +85                               | °C                                                        |

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup>Measured at IOUTA, driving a virtual ground.

$<sup>^2</sup>$  Nominal full-scale current,  $I_{\rm OUTFS}$ , is 32  $\times$  the  $I_{\rm REF}$  current.  $^3$  Use an external buffer amplifier to drive any external load.

$<sup>^4</sup>Requires +5$  V supply.  $^5Measured at f_{\rm CLOCK} = 25$  MSPS and  $I_{\rm OUT}$  = static full scale (20 mA).  $^6Logic$  level for SLEEP pin must be referenced to AVDD. Min  $V_{\rm IH} = 3.5$  V.

<sup>&</sup>lt;sup>7</sup>±5% Power supply variation.

# **DYNAMIC SPECIFICATIONS** ( $T_{MIN}$ to $T_{MAX}$ , AVDD = +5 V, DVDD = +5 V, $I_{OUTFS}$ = 20 mA, Differential Transformer Coupled Output, 50 $\Omega$ Doubly Terminated, unless otherwise noted)

| Parameter                                                                | Min | Тур | Max | Units          |

|--------------------------------------------------------------------------|-----|-----|-----|----------------|

| DYNAMIC PERFORMANCE                                                      |     |     |     |                |

| Maximum Output Update Rate (f <sub>CLOCK</sub> )                         | 125 |     |     | MSPS           |

| Output Settling Time $(t_{ST})$ (to 0.1%) <sup>1</sup>                   |     | 35  |     | ns             |

| Output Propagation Delay (t <sub>PD</sub> )                              |     | 1   |     | ns             |

| Glitch Impulse                                                           |     | 5   |     | pV-s           |

| Output Rise Time (10% to 90%) <sup>1</sup>                               |     | 2.5 |     | ns             |

| Output Fall Time (10% to 90%) <sup>1</sup>                               |     | 2.5 |     | ns             |

| Output Noise (I <sub>OUTES</sub> = 20 mA)                                |     | 50  |     | $pA/\sqrt{Hz}$ |

| Output Noise ( $I_{OUTFS} = 2 \text{ mA}$ )                              |     | 30  |     | $pA/\sqrt{Hz}$ |

| AC LINEARITY                                                             |     |     |     |                |

| Spurious-Free Dynamic Range to Nyquist                                   |     |     |     |                |

| $f_{CLOCK} = 25$ MSPS; $f_{OUT} = 1.00$ MHz                              |     |     |     |                |

| 0 dBFS Output                                                            |     |     |     |                |

| $T_A = +25^{\circ}C$                                                     | 75  | 84  |     | dBc            |

| -6 dBFS Output                                                           |     | 76  |     | dBc            |

| -12 dBFS Output                                                          |     | 81  |     | dBc            |

| $f_{CLOCK}$ = 50 MSPS; $f_{OUT}$ = 1.00 MHz                              |     | 81  |     | dBc            |

| $f_{\text{CLOCK}} = 50 \text{ MSPS}; f_{\text{OUT}} = 2.51 \text{ MHz}$  |     | 81  |     | dBc            |

| $f_{\text{CLOCK}} = 50 \text{ MSPS}; f_{\text{OUT}} = 5.02 \text{ MHz}$  |     | 76  |     | dBc            |

| $f_{\text{CLOCK}} = 50 \text{ MSPS}; f_{\text{OUT}} = 14.02 \text{ MHz}$ |     | 62  |     | dBc            |

| $f_{CLOCK} = 50 \text{ MSPS}; f_{OUT} = 20.2 \text{ MHz}$                |     | 60  |     | dBc            |

| $f_{\text{CLOCK}} = 100 \text{ MSPS}; f_{\text{OUT}} = 2.5 \text{ MHz}$  |     | 78  |     | dBc            |

| $f_{CLOCK} = 100 \text{ MSPS}; f_{OUT} = 5 \text{ MHz}$                  |     | 76  |     | dBc            |

| $f_{\text{CLOCK}} = 100 \text{ MSPS}; f_{\text{OUT}} = 20 \text{ MHz}$   |     | 63  |     | dBc            |

| $f_{CLOCK} = 100 \text{ MSPS}; f_{OUT} = 40 \text{ MHz}$                 |     | 55  |     | dBc            |

| Spurious-Free Dynamic Range within a Window                              |     |     |     |                |

| $f_{CLOCK} = 25 \text{ MSPS}$ ; $f_{OUT} = 1.00 \text{ MHz}$             | 84  | 93  |     | dBc            |

| $f_{CLOCK}$ = 50 MSPS; $f_{OUT}$ = 5.02 MHz; 2 MHz Span                  |     | 86  |     | dBc            |

| $f_{CLOCK}$ = 100 MSPS; $f_{OUT}$ = 5.04 MHz; 4 MHz Span                 |     | 86  |     | dBc            |

| Total Harmonic Distortion                                                |     |     |     |                |

| $f_{CLOCK}$ = 25 MSPS; $f_{OUT}$ = 1.00 MHz                              |     |     |     |                |

| $T_A = +25^{\circ}C$                                                     |     | -82 | -74 | dBc            |

| $f_{CLOCK} = 50 \text{ MHz}$ ; $f_{OUT} = 2.00 \text{ MHz}$              |     | -76 |     | dBc            |

| $f_{CLOCK} = 100 \text{ MHz}$ ; $f_{OUT} = 2.00 \text{ MHz}$             |     | -76 |     | dBc            |

| Multitone Power Ratio (8 Tones at 110 kHz Spacing)                       |     |     |     |                |

| $f_{CLOCK}$ = 20 MSPS; $f_{OUT}$ = 2.00 MHz to 2.99 MHz                  |     |     |     |                |

| 0 dBFS Output                                                            |     | 81  |     | dBc            |

| -6 dBFS Output                                                           |     | 81  |     | dBc            |

| –12 dBFS Output                                                          |     | 85  |     | dBc            |

| –18 dBFS Output                                                          |     | 86  |     | dBc            |

NOTES

Specifications subject to change without notice.

REV. 0 -3-

$<sup>^{1}</sup>$ Measured single ended into 50  $\Omega$  load.

### AD9752

### **DIGITAL SPECIFICATIONS** ( $T_{MIN}$ to $T_{MAX}$ , AVDD = +5 V, DVDD = +5 V, $I_{OUTFS}$ = 20 mA, unless otherwise noted)

| Parameter                                                         | Min | Typ | Max | Units |

|-------------------------------------------------------------------|-----|-----|-----|-------|

| DIGITAL INPUTS                                                    |     |     |     |       |

| Logic "1" Voltage @ DVDD = $+5 \text{ V}^1$                       | 3.5 | 5   |     | V     |

| Logic "1" Voltage @ DVDD = +3 V                                   | 2.1 | 3   |     | V     |

| Logic "0" Voltage $\widehat{\text{(a)}}$ DVDD = +5 V <sup>1</sup> |     | 0   | 1.3 | V     |

| Logic "0" Voltage @ DVDD = +3 V                                   |     | 0   | 0.9 | V     |

| Logic "1" Current                                                 | -10 |     | +10 | μA    |

| Logic "0" Current                                                 | -10 |     | +10 | μA    |

| Input Capacitance                                                 |     | 5   |     | pF    |

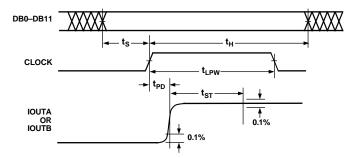

| Input Setup Time (t <sub>S</sub> )                                | 2.0 |     |     | ns    |

| Input Hold Time (t <sub>H</sub> )                                 | 1.5 |     |     | ns    |

| Latch Pulsewidth (t <sub>LPW</sub> )                              | 3.5 |     |     | ns    |

#### NOTES

<sup>1</sup>When DVDD = +5 V and Logic 1 voltage ≈3.5 V and Logic 0 voltage ≈1.3 V. IVDD can increase by up to 10 mA, depending on f<sub>CLOCK</sub>. Specifications subject to change without notice.

Figure 1. Timing Diagram

### ABSOLUTE MAXIMUM RATINGS\*

| Parameter            | With<br>Respect to | Min  | Max        | Units |

|----------------------|--------------------|------|------------|-------|

|                      |                    |      |            |       |

| AVDD                 | ACOM               | -0.3 | +6.5       | V     |

| DVDD                 | DCOM               | -0.3 | +6.5       | V     |

| ACOM                 | DCOM               | -0.3 | +0.3       | V     |

| AVDD                 | DVDD               | -6.5 | +6.5       | V     |

| CLOCK, SLEEP         | DCOM               | -0.3 | DVDD + 0.3 | V     |

| Digital Inputs       | DCOM               | -0.3 | DVDD + 0.3 | V     |

| IOUTA, IOUTB         | ACOM               | -1.0 | AVDD + 0.3 | V     |

| ICOMP                | ACOM               | -0.3 | AVDD + 0.3 | V     |

| REFIO, FSADJ         | ACOM               | -0.3 | AVDD + 0.3 | V     |

| REFLO                | ACOM               | -0.3 | +0.3       | V     |

| Junction Temperature |                    |      | +150       | °C    |

| Storage Temperature  |                    | -65  | +150       | °C    |

| Lead Temperature     |                    |      |            |       |

| (10 sec)             |                    |      | +300       | °C    |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

### ORDERING GUIDE

| Model     | Temperature<br>Range | Package<br>Description | Package<br>Options* |

|-----------|----------------------|------------------------|---------------------|

| AD9752AR  | −40°C to +85°C       | 28-Lead 300 Mil SOIC   | R-28                |

| AD9752ARU | −40°C to +85°C       | 28-Lead TSSOP          | RU-28               |

| AD9752-EB |                      | Evaluation Board       |                     |

<sup>\*</sup>R = Small Outline IC; RU = Thin Shrink Small Outline Package.

### THERMAL CHARACTERISTICS

### Thermal Resistance

28-Lead 300 Mil SOIC

$\theta_{IA} = 71.4$ °C/W

$\theta_{\rm JC} = 23^{\circ} \text{C/W}$

28-Lead TSSOP

$\theta_{JA} = 97.9^{\circ}C/W$

$\theta_{\rm IC} = 14.0^{\circ} \rm C/W$

### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9752 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.