# Example\_Timer24\_Capture CY3210-PSoCEVAL1 and MiniEval Board Project

# Project Objective

To demonstrate the operation of a 24-bit Timer24 User Module (UM) using the PSoC® device and PSoC Designer<sup>™</sup> software.

# Overview

A 24-bit timer UM works as a stopwatch. Upon each switch closure at P1[4], the time elapsed in milliseconds will be sent to an LCD. A fresh count is started immediately.

The following changes were made to the default settings in the Device Editor:

### Select User Modules

- Select a Timer24 UM from the Timers category and rename it as Timer24.

- Select a LCD UM from Misc Digital category and rename it as LCD.

### **Place User Modules**

- 1. Select Timer24 and place it on digital blocks DBB00, DBB01 and DCB02.

- 2. Select LCD and select Port-2 for LCD output.

Set the global resources and UM parameters in the Device Editor as shown under **Project Settings** ahead.

Upon program execution all hardware settings from the device configuration are loaded into the device and *main.asm* is executed.

The 24 MHz system clock is divided by 16 (VC1) and 15 (VC2) and in turn divided by 100 (VC3) to produce a 1 kHz clock. This is given as input clock to the Timer24, which has a period of 1000, effectively producing an output of 1 Hz. (Each count of the timer will be equal to 1 ms). A compare true interrupt occurs at an interval of one second because the compare value is set as 0. In the ISR a variable (seconds counter) is incremented and output to the LCD.

Further information on the user modules is provided in the specific user module data sheet included with PSoC Designer.

A rising edge on the capture input (pin P1[4]) causes the count register to be transferred to the compare register and a compare true interrupt is forced. At this ISR, the time elapsed is calculated in milliseconds and output to LCD. The timer restarts immediately and will wait for the next capture pulse.

#### **Clock Routing**

None.

# **Circuit Connections**

In the device interface, the capture input of Timer24 is routed from Port\_1\_4 through GlobalInOdd\_4 and Row\_0\_Input\_0.

# **Project Settings**

#### **Global Resources**

| CPU_Clock   | =12 MHz | Divide SysClock by 2.                         |

|-------------|---------|-----------------------------------------------|

| VC1         | =16     | Divide 24 MHz SysClock by 16.                 |

| VC2         | =15     | Divide VC1 by 15.                             |

| VC3 Source  | =VC2    | Set the source for VC3 as VC2.                |

| VC3 Divider | =100    | Divide VC2 by 100 (to produce a 1 kHz clock). |

# **User Module Parameters**

| <b>Timer24</b><br>Clock<br>Capture<br>TerminalCountOut<br>CompareOut<br>Period | =VC3<br>=Row_0_Input_0<br>=None<br>=1000 | Input 1 kHz clock from VC3.<br>Routed from P1[4].<br>Not used.<br>Not used.<br>Set to 1000 and count down<br>to 0. |

|--------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Compare Value                                                                  | =0                                       | Default value of compare<br>register is set to 0, so that a<br>timeout occurs after one<br>second.                 |

| Compare Type                                                                   | =Less Than or Equal                      | When the counter value is less than or equal to zero, trigger an interrupt.                                        |

| Interrupt Type                                                                 | =CompareTrue                             | To generate interrupt after the count reaches 0 or as soon as a capture input is received.                         |

| Clock Sync                                                                     | =Sync To SysClk                          | Synchronize to system clock.                                                                                       |

| TC_PulseWidth                                                                  | =Full width                              | Generate a full pulse width at<br>every terminal count.                                                            |

| InvertCapture                                                                  | =Normal                                  | Not used.                                                                                                          |

|                                                                                |                                          |                                                                                                                    |

| Input                                                                          |                                          |                                                                                                                    |

| mput  |        |               |                              |

|-------|--------|---------------|------------------------------|

| Pin   | Select | Drive         | Description                  |

| P1[4] | High Z | GlobalInOdd_4 | Configured for switch input. |

**Note**: This project uses an external switch at P1[4], which connects to Vdd when closed. As a result, P1[4] must be pulled down externally. The same input is routed to the capture input of Timer24 through a global bus. The pin drive is set at High Z.

## Output

| Pin                | Select | Drive  | Description |

|--------------------|--------|--------|-------------|

| P2 [0] - P2<br>[6] | StdCPU | Strong | LCD Output  |

# Evaluate the Project with the Target Board CY3210-PSoCEVAL1

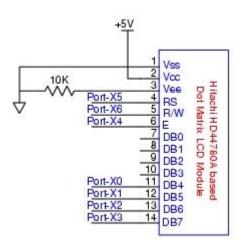

Connect an industry standard Hitachi HD44780-Based LCD Module in the LCD header.

For input, connect a 4.7k resistor from the ground pin of J5 to the breadboard point X. From the same point X, connect a jumper wire to P1[4]. Again, from X, connect a jumper wire to SW (switch) of J5 (P1[4] is pulled down externally to ground through a resistor and connected to a switch, which then connects to Vdd when closed).

For output, connect LCD at J9.

### MiniEval

In JP1, 1 and 2 must be connected (for 28-pin operation).

For the MiniEval1 board, the switch is readily connected to P1[4]. This pin has to be pulled down externally for this project. To accomplish this, connect a 4.7k resistor from P1[4] (pin 17 of PSoC) to Vss (pin 14 of PSoC).

**Note**: The CY3210-MiniEval1 board does not have an LCD. It is up to the user to connect a Hitachi HD44780-Based LCD Module to the port pins specified below. Do not forget to connect Vdd and ground to the LCD. For nominal contrast, ground the contrast control pin of the LCD through the 1.5K resistor.

| Port Pins | LCD Pin |

|-----------|---------|

| P2 [0]    | LCD_D4  |

| P2 [1]    | LCD_D5  |

| P2 [2]    | LCD_D6  |

| P2 [3]    | LCD_D7  |

| P2 [4]    | LCD_E   |

| P2 [5]    | LCD_RS  |

| P2 [6]    | LCD_RW  |

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com

© Cypress Semiconductor Corporation, 2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.