| LTR         DESCRIPTION         DATE (YR-MO-DA)         APPROVED           A         Added device types 03, 04, 05, and 06. Added electrical test limits for device physes 03, 04, 05, and 06. Added electrical test limits for device physes 07, 08, 08, and 01. Added electrical parameters testing to the parameter testing to the table in device physes 07, 08, 08, and 10. Added electrical parameters testing to the table in device physes 07, 08, 08, and 10. Added electrical parameters testing to the table in device physes 07, 08, 08, and 10. Added electrical parameters testing to the table in device physes 07, 08, 08, and 10. Added electrical parameters testing to the table in device physes 07, 09, 08, and 10. Added electrical parameters testing to the table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, and 10. Added electrical testing to table in device physes 07, 08, 08, 08, 08, 08, 08, 08, 08, 08, 08                                                          |                 |                                                                                                                                                                         |            |           |          |         |         |                     | F                  | REVISI                                        | ONS                       |       |                    |    |        |        |     |        |         |        |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|----------|---------|---------|---------------------|--------------------|-----------------------------------------------|---------------------------|-------|--------------------|----|--------|--------|-----|--------|---------|--------|----|

| types 0.9, 05, and 06 to table 1. Added vendor CAGE code 34335. Editorial independence to so 07, 09, and 10. Added electrical parameters testing to table 0. 200-25         Monica L. Poelking           B         Added device types 07, 08, 09, and 10. Added electrical parameters testing to table 0. 200-25         Nonica L. Poelking           C         Added vendor CAGE code 0.C7V7. Update bollerplate to MIL-PRF-38635         02-12-18         Thomes M. Hess           SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LTR             |                                                                                                                                                                         |            |           |          | [       | DESCF   | RIPTION             | ١                  |                                               |                           |       |                    | DA | TE (YF | R-MO-E | DA) |        | APPR    | OVED   |    |

| table I for device types 07, 08, 09, and 10. Added a new package for device         Image: Colspan="2">C           C         Added vendor CAGE code 0C7V7. Update bollerplate to ML-PRF-38535         02-12-18         Thomas M. Hess           SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         I         <thi< th=""></thi<></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A               | types                                                                                                                                                                   | s 03, 04   | l, 05, ai | nd 06 to |         |         |                     |                    |                                               |                           |       |                    |    | 90-0   | 95-09  |     | Willia | am K. H | leckma | ın |

| REV         Image: Constraint of the second sec | В               | table I for device types 07, 08, 09, and 10. Added a new patype 07. Editorial changes throughout.         C       Added vendor CAGE code 0C7V7. Update boilerplate to M |            |           |          |         |         | cal para<br>ew pacł | ameters<br>kage fo | neters testing to 92-03-25 Mon age for device |                           |       | Monica L. Poelking |    |        |        |     |        |         |        |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         I</thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | С               |                                                                                                                                                                         |            |           |          | e 0C7V  | ′7. Upd | ate boil            | erplate            | to MIL                                        | -PRF-3                    | 38535 |                    |    | 02-1   | 2-18   |     | Thor   | nas M.  | Hess   |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         I</thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                                                                                                                                                                         |            |           |          |         |         |                     |                    |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I <thi< th="">         I         I</thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REV             |                                                                                                                                                                         |            |           |          |         |         |                     |                    |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| SHEET       15       16       17       18       19       20       21       22       23       24       25       26       27       28       Image:                                                                                                                                       |                 |                                                                                                                                                                         |            |           |          |         |         |                     |                    |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| REV STATUS         REV         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C         C <t< td=""><td>REV</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td>С</td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REV             | С                                                                                                                                                                       | С          | С         | С        | С       | С       | С                   | С                  | С                                             | С                         | С     | С                  | С  | С      |        |     |        |         |        |    |

| OF SHEETS       SHEET       1       2       3       4       5       6       7       8       9       10       11       12       13       14         PMIC N/A       PREPARED BY<br>Tim H. Noh       PREPARED BY<br>Tim H. Noh       PREPARED BY<br>Tim H. Noh       DEFENSE SUPPLY CENTER COLUMBUS,<br>COLUMBUS, OHIO 43216<br>http://www.dscc.dla.mil       DEFENSE SUPPLY CENTER COLUMBUS,<br>COLUMBUS, OHIO 43216<br>http://www.dscc.dla.mil       I       12       13       14         MICROCIRCUIT<br>DRAWING       CHECKED BY<br>Tim H.Noh       CHECKED BY<br>William K. Heckman       MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON       MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON       V         AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE<br>AMSC N/A       DRAWING APPROVAL DATE<br>89-02-06       SIZE       CAGE CODE<br>A       5962-88689         AMSC N/A       REVISION LEVEL<br>C       SIZE       CAGE CODE<br>A       5962-88689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SHEET           | 15                                                                                                                                                                      | 16         | 17        | 18       | 19      | 20      | 21                  | 22                 | 23                                            | 24                        | 25    | 26                 | 27 | 28     |        |     |        |         |        |    |

| PMIC N/A       PREPARED BY<br>Tim H. Noh       DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216<br>http://www.dscc.dla.mil         STANDARD<br>MICROCIRCUIT<br>DRAWING       CHECKED BY<br>Tim H.Noh       CHECKED BY<br>Tim H.Noh       DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216<br>http://www.dscc.dla.mil         THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS       APPROVED BY<br>William K. Heckman       MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON         AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE       DRAWING APPROVAL DATE<br>89-02-06       MICROCIRCUIT, SILICON         AMSC N/A       REVISION LEVEL<br>C       SIZE       CAGE CODE<br>A G7268       5962-88689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REV STATUS      |                                                                                                                                                                         |            |           | REV      | /       |         | С                   | С                  | С                                             | С                         | С     | С                  | С  | С      | С      | С   | С      | С       | С      | С  |

| Tim H. Noh     DEFENSE SUPPLY CENTER COLUMBUS       STANDARD<br>MICROCIRCUIT<br>DRAWING     CHECKED BY<br>Tim H.Noh     DEFENSE SUPPLY CENTER COLUMBUS       THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS     APPROVED BY<br>William K. Heckman     MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON       AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE     DRAWING APPROVAL DATE<br>89-02-06     MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON       AMSC N/A     REVISION LEVEL<br>C     SIZE<br>A     CAGE CODE<br>67268     5962-88689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OF SHEETS       |                                                                                                                                                                         |            |           | SHE      | ET      |         | 1                   | 2                  | 3                                             | 4                         | 5     | 6                  | 7  | 8      | 9      | 10  | 11     | 12      | 13     | 14 |

| MICROCIRCUIT<br>DRAWINGTim H.Nohhttp://www.dscc.dla.milTHIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTSAPPROVED BY<br>William K. HeckmanMICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICONAND AGENCIES OF THE<br>DEPARTMENT OF DEFENSEDRAWING APPROVAL DATE<br>89-02-06MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICONAMSC N/AREVISION LEVEL<br>CSIZE<br>ACAGE CODE<br>672685962-88689SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PMIC N/A        |                                                                                                                                                                         |            |           |          |         |         | 1                   |                    |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS       William K. Heckman       MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON         AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE       DRAWING APPROVAL DATE<br>89-02-06       MICROCIRCUIT, DIGITAL, CMOS, SERIAL<br>COMMUNICATION CONTROLLER,<br>MONOLITHIC SILICON         AMSC N/A       REVISION LEVEL<br>C       SIZE<br>A       CAGE CODE<br>67268       5962-88689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MICRO           | CIRC                                                                                                                                                                    | CUIT       |           |          |         |         |                     |                    |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| DEPARTMENT OF DEFENSE<br>AMSC N/A REVISION LEVEL C SIZE CAGE CODE 67268 5962-88689 SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FOR US<br>DEPAR | SE BY /<br>RTMEN                                                                                                                                                        | ALL<br>ITS |           |          |         |         | kman                |                    |                                               | COMMUNICATION CONTROLLER, |       |                    |    |        |        |     |        |         |        |    |

| C A 67268 5962-88689                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                                                                                                                                                                         |            |           | DRA      | WING    |         |                     | ATE                |                                               |                           |       |                    |    |        |        |     |        |         |        |    |

| SHEET 1 OF 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AM              | SC N/A                                                                                                                                                                  |            |           | REV      | ISION I |         |                     |                    |                                               |                           |       |                    |    |        |        | Ę   | 5962-  | 8868    | 9      |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |                                                                                                                                                                         |            |           |          |         |         |                     |                    |                                               | SHE                       | ET    | 1                  | 1  | OF     | 28     |     |        |         |        |    |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited

5962-E130-03

| 1 | S | С      | റ      | Р | F |

|---|---|--------|--------|---|---|

|   | J | $\sim$ | $\sim$ |   | _ |

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

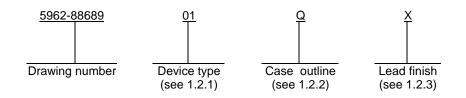

1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | <u>Generic number</u> | Frequency | Circuit function                                                  |

|-------------|-----------------------|-----------|-------------------------------------------------------------------|

| 01          | Z85C3006              | 6.0 MHz   | Serial communication controller                                   |

| 02          | Z85C3008              | 8.0 MHz   | Serial communication controller 2/                                |

| 03          | AM85C30-10            | 10.0 MHz  | Serial communication controller with SDLC enhancements <u>1</u> / |

| 04          | AM85C30-12            | 12.0 MHz  | Serial communication controller with SDLC enhancements            |

| 05          | AM85C30-16            | 16.0 MHz  | Serial communication controller with SDLC enhancements <u>1</u> / |

| 06          | AM85C30-08            | 8.0 MHz   | Serial communication controller with SDLC enhancements <u>1</u> / |

| 07          | Z85C3010              | 10.0 MHz  | Serial communication controller <u>3</u> /                        |

| 08          | Z8523010              | 10.0 MHz  | Serial communication controller with SDLC enhancements <u>1</u> / |

| 09          | Z8523016              | 16.0 MHz  | Serial communication controller with SDLC enhancements <u>1</u> / |

| 10          | Z8523008              | 8.0 MHz   | Serial communication controller with SDLC enhancements <u>1</u> / |

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| Q              | GDIP1-T40 or CDIP2-T40 | 40               | Dual-in-line package         |

| Х              | GQCC1-J44              | 44               | Square "J" lead chip carrier |

| Y              | CQCC1-N44              | 44               | Square leadless chip carrier |

1.2.3 Lead finish. The lead finish is as specified in MIL-PRF-38535, appendix A.

1/ Device types 03, 05, 06, 08, 09, and 10 are not functionally identical.

2/ Device type 02 is not functionally identical with device types 06 or 10.

$\underline{3}$  Device type 07 is not functionally identical with device types 03 or 08.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-88689 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>C | SHEET 2    |

### 1.3 Absolute maximum ratings.

| V <sub>CC</sub> supply voltage range (referenced to ground) | -0.3 V dc to +7.0 V dc |

|-------------------------------------------------------------|------------------------|

| Voltage on any pin (referenced to ground)                   | -0.3 V dc to +7.0 V dc |

| Storage temperature range (T <sub>STG</sub> )               | -65°C to +150°C        |

| Maximum power dissipation (P <sub>D</sub> )                 | . 0.5 W                |

| Lead temperature (soldering, 10 seconds)                    | . +270°C               |

| Maximum operating junction temperature (T <sub>J</sub> )    | . +180°C               |

| Thermal resistance, junction-to-case (θ <sub>JC</sub> )     | See MIL-STD-1835       |

1.4 Recommended operating conditions.

| Supply voltage ( $V_{CC}$ )<br>Minimum high level input voltage ( $V_{IH}$ )<br>Maximum low level input voltage ( $V_{IL}$ )<br>Frequency of operation: | 2.2 V dc                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Device type 01<br>Device types 02, 06, 10<br>Device types 03, 07, 08<br>Device type 04                                                                  | 0.5 MHz to 8.0 MHz<br>0.5 MHz to 10 MHz |

| Device type 04<br>Device types 05 and 09<br>Case operating temperature range (T <sub>C</sub> )<br>Clock rise and fall times:                            | 0.5 MHz to 16.4 MHz                     |

| Device type 09<br>Device type 05<br>Device types 01, 02, 03, 04, 06, 07, 08, 10                                                                         | 8 ns maximum                            |

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solicitation.

### SPECIFICATION

DEPARTMENT OF DEFENSE

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

**STANDARDS**

DEPARTMENT OF DEFENSE

| MIL-STD-883  | - | Test Method Standard Microcircuits.                    |

|--------------|---|--------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines. |

#### HANDBOOKS

## DEPARTMENT OF DEFENSE

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88689 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 3          |

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.2 herein.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

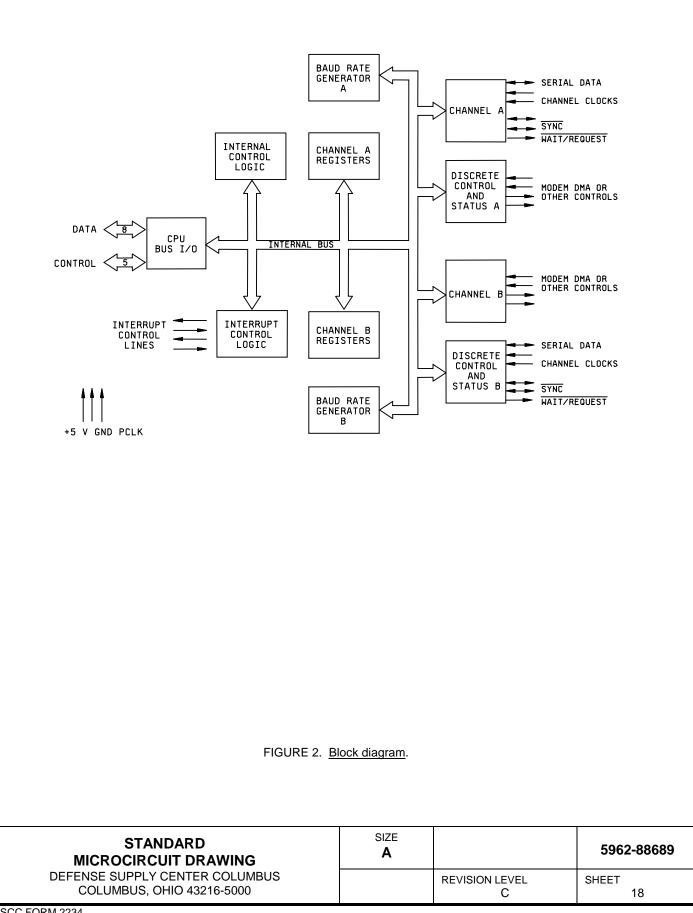

3.2.3 <u>Block diagram</u>. The block diagram shall be as specified on figure 2.

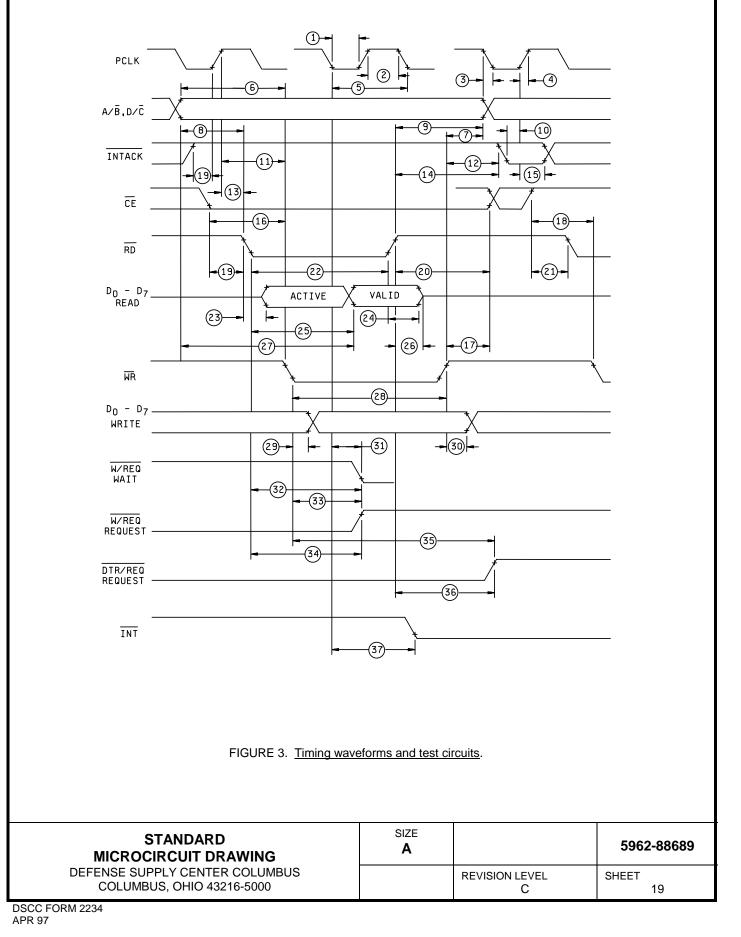

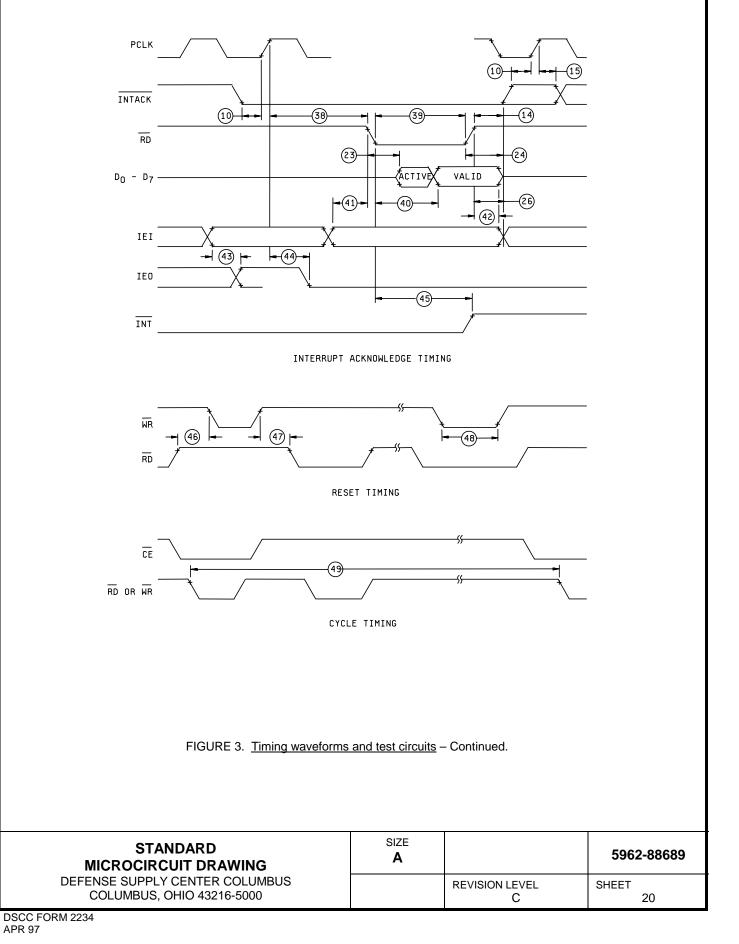

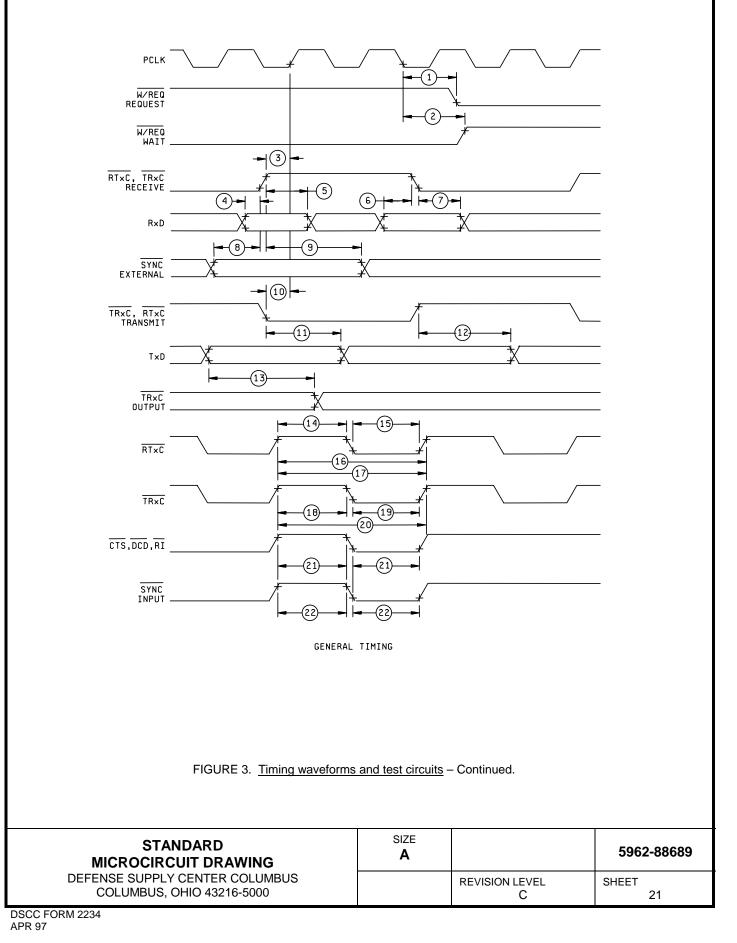

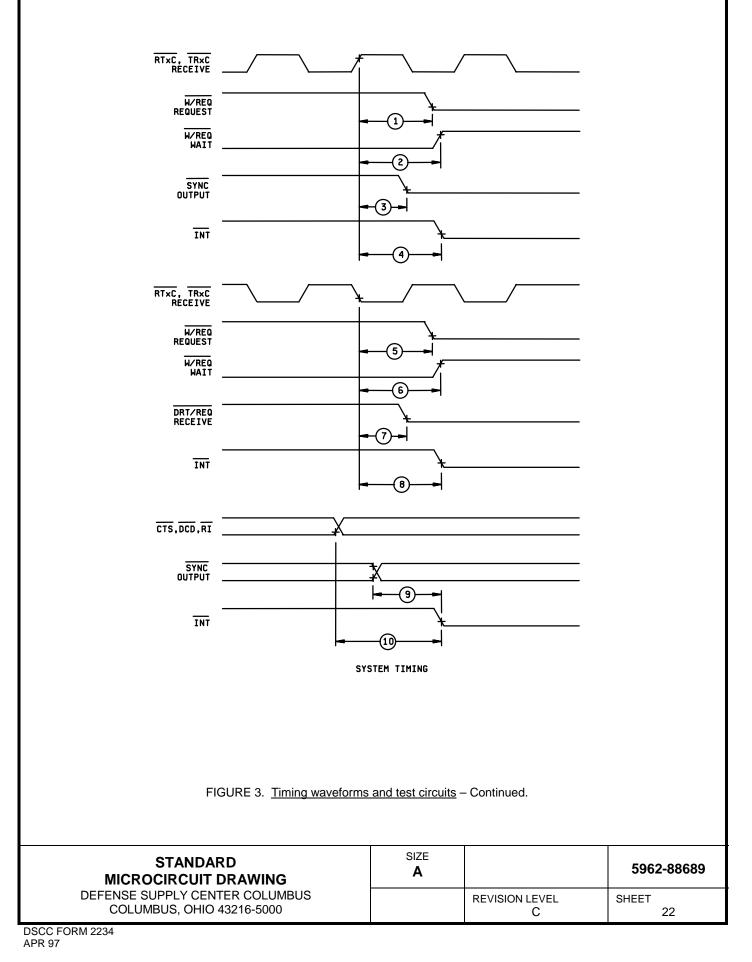

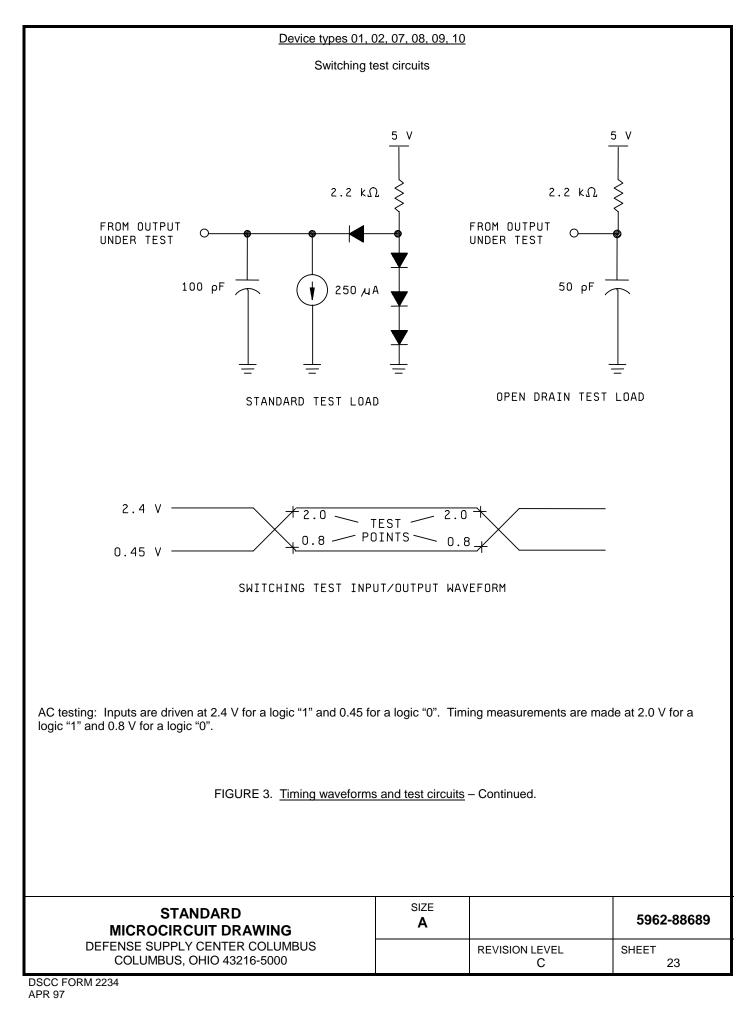

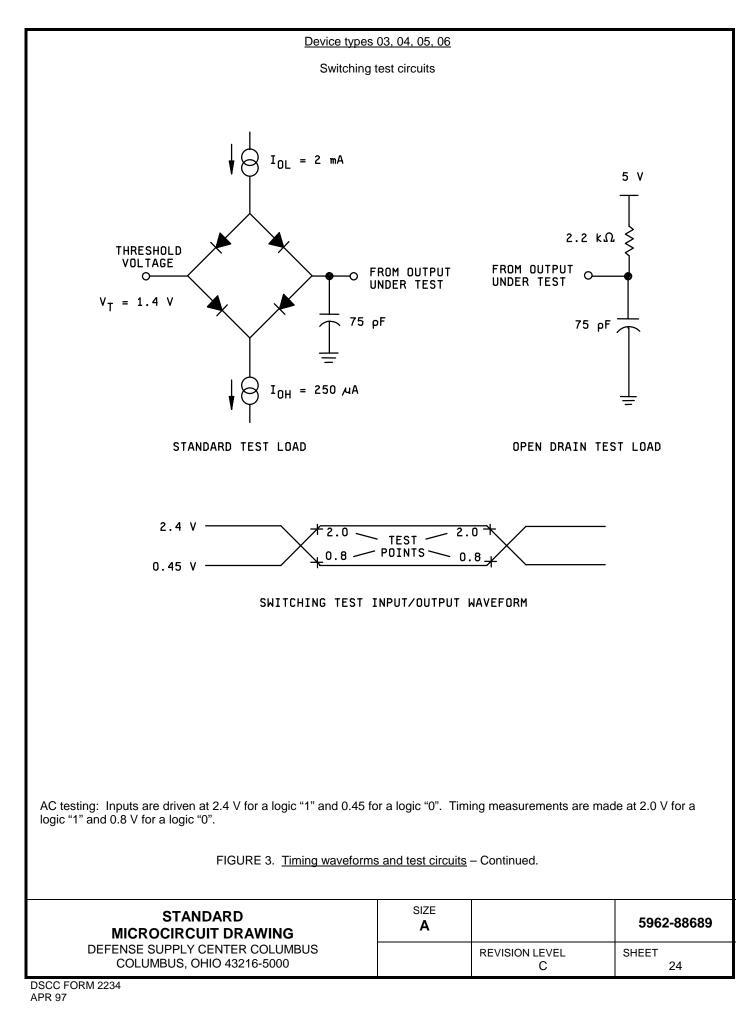

3.2.4 Timing waveforms and test circuits. The timing waveforms and test circuits shall be as specified on figure 3.

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103 (see 6.6 herein). For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device.

3.5.1 <u>Certification/compliance mark</u>. A compliance indicator "C" shall be marked on all non-JAN devices built in compliance to MIL-PRF-38535, appendix A. The compliance indicator "C" shall be replaced with a "Q" or "QML" certification mark in accordance with MIL-PRF-38535 to identify when the QML flow option is used.

3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 and QML-38535 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 <u>Notification of change</u>. Notification of change to DSCC-VA shall be required in accordance with MIL-PRF-38535, appendix A.

3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

017E

| STANDARD                       |

|--------------------------------|

| MICROCIRCUIT DRAWING           |

| DEFENSE SUPPLY CENTER COLUMBUS |

| COLUMBUS, OHIO 43216-5000      |

| A |                     | 5962-88689 |

|---|---------------------|------------|

|   | REVISION LEVEL<br>C | SHEET<br>4 |

| Test                           | Symbol           | $\begin{array}{l} Conditions \ \underline{1}/\\ -55^\circ C \leq T_C \leq +125^\circ C\\ V_{CC} = 5.0 \ V \ \pm 10\%\\ \text{unless otherwise specified} \end{array}$ | Group A<br>subgroups | Device<br>type | Li                       | Unit                       |     |

|--------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|--------------------------|----------------------------|-----|

|                                |                  |                                                                                                                                                                       |                      |                | Min                      | Max                        |     |

| High input voltage             | V <sub>IH</sub>  |                                                                                                                                                                       | 1, 2, 3              | All            | 2.2                      | V <sub>CC</sub> +0.3<br>2/ | V   |

| Low input voltage              | V <sub>IL</sub>  |                                                                                                                                                                       | 1, 2, 3              | All            | -0.3 <u>2</u> /          | 0.8                        | V   |

| Logic low output voltage       | V <sub>OL</sub>  | $I_{OL} = 2.0 \text{ mA}, V_{CC} = 4.5 \text{ V}$                                                                                                                     | 1, 2, 3              | All            |                          | 0.5                        | V   |

|                                | V <sub>OH1</sub> | $I_{OH} = -1.6 \text{ mA}, V_{CC} = 4.5 \text{ V}$                                                                                                                    | 1, 2, 3              | All            | 2.4                      |                            | V   |

| Logic high output voltage      | V <sub>OH2</sub> | $I_{OH} = -250 \ \mu A, \ V_{CC} = 4.5 \ V$                                                                                                                           | 1, 2, 3              | All            | V <sub>CC</sub> -<br>0.8 |                            | V   |

| Power supply current           | Icc              | $V_{IH} = 4.8 V$<br>$V_{IL} = 0.2 V$<br>$V_{CC} = 5.0 V$<br>Oscillator off                                                                                            | 1, 2, 3              | 01,02,06       |                          | 30                         | mA  |

|                                |                  |                                                                                                                                                                       | 1, 2, 3              | 03,07,08       |                          | 18                         | -   |

|                                |                  |                                                                                                                                                                       | 1, 2, 3              | 04,05,09       |                          | 22                         |     |

|                                |                  |                                                                                                                                                                       | 1, 2, 3              | 10             |                          | 15                         |     |

| Output leakage current<br>low  | I <sub>LOL</sub> | $V_{OUT} = 0.4 \text{ V}, V_{CC} = 5.5 \text{ V}$                                                                                                                     | 1, 2, 3              | All            | -10                      |                            | μΑ  |

| Output leakage current<br>high | I <sub>LOH</sub> | $V_{OUT} = 2.4 \text{ V}, V_{CC} = 5.5 \text{ V}$                                                                                                                     | 1, 2, 3              | All            |                          | +10                        |     |

| Input low current              | IIL              | $V_{IN} = 0.4 \text{ V}, \ V_{CC} = 5.5 \text{ V}$                                                                                                                    | 1, 2, 3              | All            | -10                      |                            |     |

| Input high current             | I <sub>IH</sub>  | $V_{IN} = 2.4 \text{ V}, V_{CC} = 5.5 \text{ V}$                                                                                                                      | 1, 2, 3              | All            |                          | +10                        |     |

| Input capacitance              | C <sub>IN</sub>  | fc = 1.0 MHz                                                                                                                                                          | 4                    | All            |                          | 10                         | pF  |

| Output cpacitance              | COUT             | See 4.3.1c                                                                                                                                                            | 4                    | All            |                          | 15                         | _   |

| Bidirectional capacitance      | CI/O             |                                                                                                                                                                       | 4                    | All            |                          | 20                         |     |

| Functional test                |                  | See 4.3.1d<br>V <sub>CC</sub> = 4.5 V, 5.5 V                                                                                                                          | 7, 8                 | All            |                          |                            |     |

|                                |                  |                                                                                                                                                                       |                      | 05, 09         | 16.0                     |                            | MHz |

| Maximum frequency              | f <sub>MAX</sub> | See figure 3                                                                                                                                                          | 9, 10, 11            | 04             | 12.0                     |                            |     |

|                                |                  | $V_{CC} = 4.5 V$                                                                                                                                                      |                      | 03,07,08       | 10.0                     |                            |     |

|                                |                  |                                                                                                                                                                       |                      | 02,06,10       | 8.0                      |                            |     |

|                                |                  |                                                                                                                                                                       |                      | 01             | 6.0                      |                            |     |

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88689 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 5          |

|                                        | т                   | ABLE I. Electrical performanc                                                                                                                                       | e characteristic     | <u>cs</u> – Cor | ntinued.                         |     |            |      |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|----------------------------------|-----|------------|------|

| Test                                   | Symbol              | $\begin{array}{l} Conditions \ \underline{1}/\\ -55^\circ C \leq T_C \leq +125^\circ C\\ V_{CC} = 5.0 \ V \pm 10\%\\ \text{unless otherwise specified} \end{array}$ | Group A<br>subgroups | Ref<br>no.      | Device<br>type                   | Li  | mits       | Unit |

|                                        |                     |                                                                                                                                                                     |                      |                 |                                  | Min | Max        |      |

| PCLK low width                         | t <sub>wPCL</sub>   | See figure 3, read and                                                                                                                                              | 9, 10, 11            | 1               | 01                               | 70  | 1000       | ns   |

|                                        |                     | write, interrupt, reset, and cycle timings.                                                                                                                         |                      |                 | 02,06,10                         | 50  | 1000       |      |

|                                        |                     | $C_{L} = 50 \text{ pF} \pm 10\%$                                                                                                                                    |                      |                 | 03,07,08                         | 40  | 1000       |      |

|                                        |                     | $V_{CC} = 4.5 V$                                                                                                                                                    |                      |                 | 04                               | 34  | 1000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05, 09                           | 26  | 1000       |      |

| PCLK high width                        | t <sub>wPCH</sub>   |                                                                                                                                                                     | 9, 10, 11            | 2               | 01                               | 70  | 1000       | ns   |

|                                        |                     |                                                                                                                                                                     |                      |                 | 02,06,10                         | 50  | 1000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 03,07,08                         | 40  | 1000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 04                               | 34  | 1000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05, 09                           | 26  | 1000       |      |

| PCLK fall time <u>2</u> / <u>3</u> /   | t <sub>fPC</sub>    |                                                                                                                                                                     | 9, 10, 11            | 3               | 01,02,03,<br>04,06,07,<br>08, 10 |     | 10         | ns   |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05                               |     | 8          |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 09                               |     | 5          |      |

| PCLK rise time <u>2/</u><br><u>3</u> / | t <sub>rPC</sub>    |                                                                                                                                                                     | 9, 10, 11            | 4               | 01,02,03,<br>04,06,07,<br>08, 10 |     | 10         | ns   |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05                               |     | 8          |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 09                               |     | 5          |      |

| PCLK cycle time                        | t <sub>cPC</sub>    |                                                                                                                                                                     | 9, 10, 11            | 5               | 01                               | 165 | 2000       | ns   |

|                                        |                     |                                                                                                                                                                     |                      |                 | 02,06,10                         | 125 | 2000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 03,07,08                         | 100 | 2000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 04                               | 80  | 2000       |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05, 09                           | 61  | 2000       |      |

| Address to $\overline{WR}\downarrow$   | t <sub>sA(WR)</sub> |                                                                                                                                                                     | 9, 10, 11            | 6               | 01                               | 80  |            | ns   |

| setup time                             |                     |                                                                                                                                                                     | 9, 10, 11            | 0               | 02,06,10                         | 70  |            |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 03,07,08                         | 50  |            |      |

|                                        |                     |                                                                                                                                                                     |                      |                 | 04                               | 45  |            | _    |

|                                        |                     |                                                                                                                                                                     |                      |                 | 05, 09                           | 35  |            |      |

| Address to WR ↑<br>hold time           | t <sub>hA(WR)</sub> |                                                                                                                                                                     | 9, 10, 11            | 7               | All                              | 0   |            | ns   |

| See footnotes at end o                 | of table.           |                                                                                                                                                                     |                      |                 |                                  |     |            |      |

|                                        |                     | RD<br>DRAWING<br>TER COLUMBUS                                                                                                                                       | SIZE<br>A            |                 |                                  |     | 5962-8     | 8689 |

|                                        |                     | 43216-5000                                                                                                                                                          |                      | REVI            | SION LEVEL<br>C                  |     | SHEET<br>6 |      |

|                                                 | Т                                                           | ABLE I. Electrical performanc                                                                                                                                       | e characteristic     | <u>cs</u> – Cor | itinued.                     |     |            |       |

|-------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|------------------------------|-----|------------|-------|

| Test                                            | Symbol                                                      | $\begin{array}{l} Conditions \ \underline{1}/\\ -55^\circ C \leq T_C \leq +125^\circ C\\ V_{CC} = 5.0 \ V \pm 10\%\\ \text{unless otherwise specified} \end{array}$ | Group A<br>subgroups | Ref<br>no.      | Device<br>type               | Li  | mits       | Unit  |

|                                                 |                                                             |                                                                                                                                                                     |                      |                 |                              | Min | Max        |       |

| Address to RD ↓                                 | t <sub>sA(RD)</sub>                                         | See figure 3, read and write, interrupt, reset, and cycle timings.                                                                                                  | 9, 10, 11            | 8               | 01                           | 80  |            | ns    |

| setup time                                      |                                                             | $C_L = 50 \text{ pF} \pm 10\%$                                                                                                                                      |                      |                 | 02,06,10                     | 70  |            |       |

|                                                 |                                                             | $V_{CC} = 4.5 V$                                                                                                                                                    |                      |                 | 03,07,08                     | 50  |            | _     |

|                                                 |                                                             |                                                                                                                                                                     |                      |                 | 04                           | 45  |            |       |

|                                                 |                                                             | -                                                                                                                                                                   |                      |                 | 05, 09                       | 35  |            |       |

| Address to RD ↑<br>hold time                    | t <sub>hA(RD)</sub>                                         |                                                                                                                                                                     | 9, 10, 11            | 9               | All                          | 0   |            | ns    |

| INTACK to PCLK $\uparrow$ setup time <u>4</u> / | t <sub>sIA(PC)</sub>                                        |                                                                                                                                                                     | 9, 10, 11            | 10              | 01,02,03,<br>06,07,08,<br>10 | 20  |            | ns    |

|                                                 |                                                             | -                                                                                                                                                                   |                      |                 | 04,05,09                     | 15  |            |       |

| INTACK to WR↓                                   | t <sub>sIAi(WR)</sub>                                       |                                                                                                                                                                     | 9, 10, 11            | 11              | 01                           | 160 |            | ns    |