#### SG923-0010 Evaluation Kit for SG901-1091 Radio Module

#### Overview

SG923-0010 Is an evaluation Kit used to simplify the rapid evaluation and software integration of the SG901-1091 Radio Module. The EVK allows for easy access to the SDIO interface via a standard SDIO hardware connector The SDIO connector is designed to plug into processor development boards for rapid software testing.

The SG901-1080 Carrier board which hosts the SG901-1091 board also contains a debug connector which supports 1.8V UART signaling.

The evaluation kit is powered and provides power to the module from a 3.3V SDIO socket or external input for instrumentation. A 2.4GHz antenna connection port as well as an optional external Antenna diversity interface allow for complete system testing.

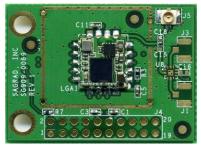

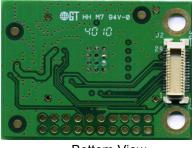

The Kit consists of a SG901-1091 soldered into a Carrier Board, Sagrad Part Number SG901-1080, Figure 1 and a SDIO Adapter Board, Sagrad Part number SG901-1042 depicted on Figure 2.

#### **Features**

- Easy to use SDIO connector for common processors EVK.

- Full application circuit example.

- Standard 3.3V Powered SDIO on Insert

- On board Regulator and Sleep Clock

Oscillator

- Simple Client application

- Versatile SDIO Bus

#### **Ordering Information**

| Packaging      | Order Number |

|----------------|--------------|

| Evaluation Kit | SG923-0010   |

#### **Software Support and Drivers**

An approval process and SLA is required to obtain the software package. Updated versions of all software are available at: www.sagrad.com/support/1091

#### **Full Assembly View**

1-321-255-0515

#### WWW.SAGRAD.COM

**FIGURE 1**: SG901-1080 Carrier Board (Includes the SG901-1091 Module)

Top View

Bottom View

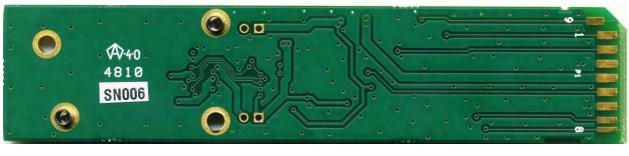

FIGURE 2: SG901-1069 Adapter Board

Top View

**Bottom View**

1-321-255-0515

WWW.SAGRAD.COM

# SG923-0010 Evaluation Kit Boards Main Components **Optional Diversity** J4 **Antenna Access** SG901-1091 Radio including Switch Module module **MOLEX** Connector **SDIO INSERT** Direct Antenna Connector 94 V-0 SDIO 3.3V-1.8V TRANSLATOR SG909-0032 REV 2 I/O Voltage Sleep Clock translator Oscillator 2.4GHz

1-321-255-0515

WWW.SAGRAD.COM

#### **Connector Descriptions**

# **SDIO INSERT Pin Descriptions**

| SIGNAL NAME                                                                    | PIN<br>NUMBER | DESCRIPTION           | NOTES                                                                                                                                                                              |  |

|--------------------------------------------------------------------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDIO_DAT[3]                                                                    | 1             | SDIO DATA3            | Voltage translated and mapped to SDD3_CS Pin 13 on<br>SG901-1091 Module                                                                                                            |  |

| SDIO_CMD                                                                       | 2             | SDIO CMD              | Voltage translated Mapped to CMD_MOSI Pin 11 on<br>SG901-1091 Module                                                                                                               |  |

| VSS1                                                                           | 3             | VSS, Ground Return    |                                                                                                                                                                                    |  |

| VDD                                                                            | 4             | SDIO_VDD, 3.3V Supply | Connected to a 3.3 to 1.8V regulator generating the VHIO 1.8V supply for the the SG901-1091. It is also connected directly to the VBAT Pin 8 on SG901-1091 Module. Fuse Protected. |  |

| CLK                                                                            | 5             | SDIO Clock            | Voltage translated and mapped to CLK Pin 10 on<br>SG901-1091 Module                                                                                                                |  |

| VSS2                                                                           | 6             | VSS, Ground Return    |                                                                                                                                                                                    |  |

| SDIO_DAT[0]                                                                    | 7             | SDIO DATA0            | Voltage translated and mapped to SDD0_MISO Pin 4<br>on SG901-1091 Module                                                                                                           |  |

| SDIO_DAT[1]                                                                    | 8             | SDIO DATA1            | Voltage translated and mapped to SDD1_IRQ Pin 3 on SG901-1091 Module                                                                                                               |  |

| SDIO_DAT[2]                                                                    | 9             | SDIO DATA2            | Voltage translated and mapped to SDD2_HSEL Pin 1<br>on SG901-1091 Module                                                                                                           |  |

| NOTE: Pin 9 of the standard SDIO pin out is recessed and collocated with pin 1 |               |                       |                                                                                                                                                                                    |  |

### **J4 Pin Descriptions**

| SIGNAL<br>NAME | PIN NUMBER        | DESCRIPTION      | NOTES                                                                                                                                                                                  |

|----------------|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBG RXD        | 1                 | DBG RXD          | Mapped to DBG_RXD Pin 15 on SG901-1091 Module. 1.8V UART Debug                                                                                                                         |

| RSTn           | 2                 | Reset            | Mapped to RST Pin 2 input on SG901-1091 Module. A pull up of 100K is tied to the VHIO supply                                                                                           |

| DBG_TXD        | 3                 | DBG TXD          | Mapped to DBG_TXD Pin 17 on SG901-1091 Module. 1.8V UART Debug                                                                                                                         |

| 3.3V           | 10                | SDIO 3.3V        | Access to the 3.3V SDIO Supply                                                                                                                                                         |

| FEM_CTRL1      | 11                | FEM CTRL         | Optional FEM Control Access (For populated Front End Module FEM)                                                                                                                       |

| VHIO           | 12                | VHIO Access      | Access to the VHIO voltage regulator output                                                                                                                                            |

| SLEEPCLK       | 17                | Sleep Clock      | Access to the Sleep Clock output from the 32768Hz Oscillator                                                                                                                           |

| POWERUP        | 20                | Power Up<br>WIFI | Mapped to POWERUP Pin 14 on SG901-1091 Module. This pin is normally high in the adapter board by an internal resistor divider to 3.3V. Use a low level input to disable the SG901-1091 |

| GND            | 4,6,8,16,18       | Ground<br>Return |                                                                                                                                                                                        |

| NC             | 5,7,9,13,14,15,19 | No Connect       |                                                                                                                                                                                        |

1-321-255-0515

WWW.SAGRAD.COM

### **SDIO Host application**

For SDIO applications simply insert the assembly into the SDIO socket available in most Host processor application/development boards. There are no external supplies or clocks required. The Kit is powered by the SDIO source in the Host development board.

#### SPI Host application (In development)

For SPI applications, the user is required to access the Bus using the SDIO connector in the adapter board. An external 3.3V power supply is required to power the evaluation kit assembly.

1-321-255-0515

WWW.SAGRAD.COM

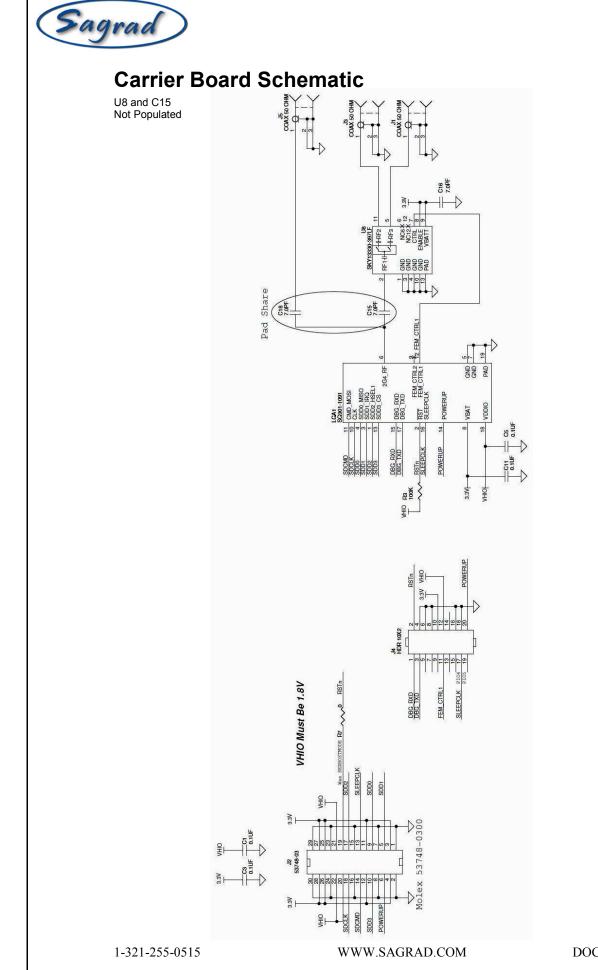

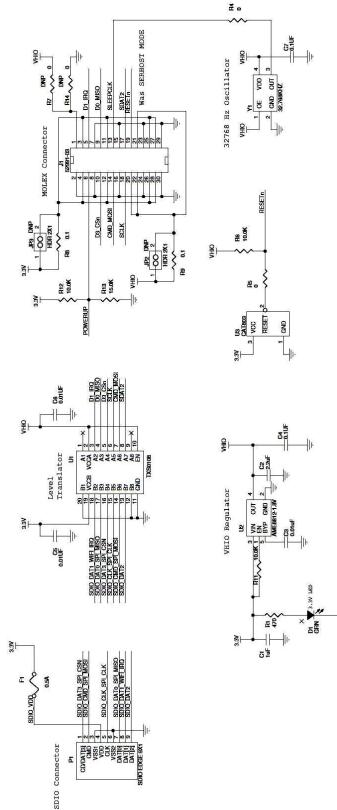

Adapter Board Schematic

1-321-255-0515

WWW.SAGRAD.COM

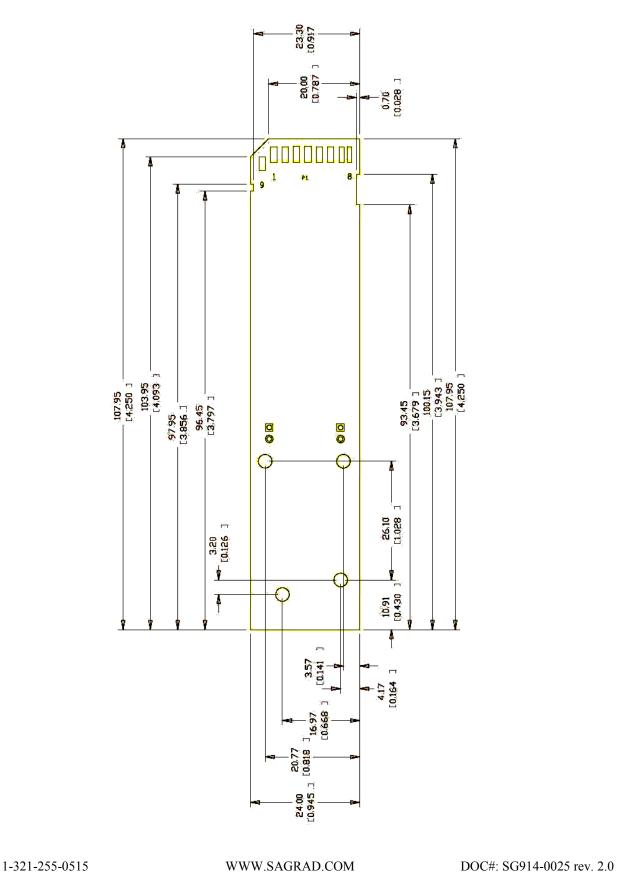

#### Adapter Board Dimensions

Downloaded from Elcodis.com electronic components distributor