Microcontrollers

Never stop thinking

## **Edition**

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2008. All Rights Reserved.

#### **LEGAL DISCLAIMER**

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# AP32114 Design Guideline for TC1797 Microcontroller Board Layout

| AP32114           |                                              |      |

|-------------------|----------------------------------------------|------|

| Revision History: | 2008-11                                      | V2.4 |

| Previous Version: | V2.3                                         |      |

| Page              | Subjects (major changes since last revision) |      |

| 7                 | Fig. 2 changed.                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

|                   |                                              |      |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

# AP32114 Design Guideline for TC1797 Microcontroller Board Layout

| Table of Contents |                            |   |

|-------------------|----------------------------|---|

| 1                 | Overview                   |   |

| 1.1               | General Information        | E |

| 1.2               | Pinout of TC1797           |   |

| 2                 | PCB Design Recommendations |   |

| 2.1               | Decoupling                 |   |

| 2.2               | Decoupling Capacitor List: |   |

## 1 Overview

The TC1797 is a 32-Bit microcontroller in a BGA-416 package, which requires a PCB carefully designed for electromagnetic compatibility. In addition to the Infineon PCB Design Guidelines for Microcontrollers (AP24026), which gives general design rule informations for PCB design, some product-specific recommendations and guidelines for the TC1797 are discussed here.

#### 1.1 General Information

The microcontroller has four supply domains (VDD=1.5V for Core, VDDP=3.3V for I/O Pad, VDDEBU=2.5V-3.3V for EBU, VDDM=3.3V or 5V for ADC), which should be decoupled individually.

The power supply feeding from the regulator outputs to each domain can be made on a supply layer (POWER).

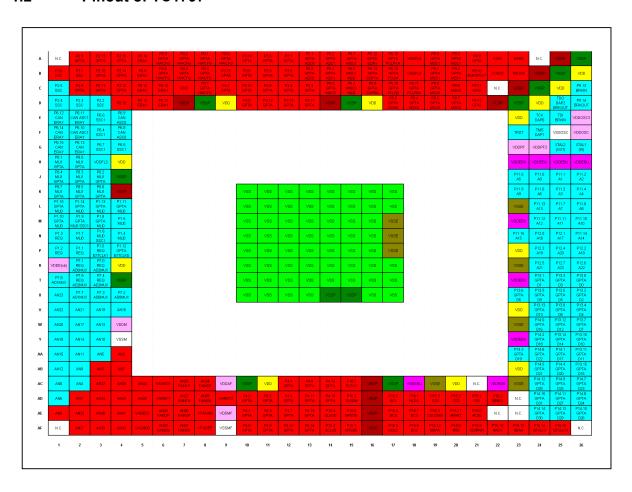

## 1.2 **Pinout of TC1797**

Figure 1 Pinout of TC1797 (BGA-416):

# 2 PCB Design Recommendations

- To minimize the EMI radiation on the PCB the following signals have to be considered as critical:

- BFCLKOUT: EBU clock output

- LVDS Pins

- MLI Pins

Application Note 5 V2.4, 2008-11

- MSC Pins

- ERAY Pins

- Supply Pins

Route these signals with adjacent ground reference and avoid signal and reference layer changes.

Route them as short as possible.

Routing ground on each side can help to reduce coupling to other signals.

■ For unused "Output, Supply, Input and I/O " pins following points must be considered:

| 1. Supply Pins (Modules)                  | See the User's Manual.                                                                                                                                                                                                                                 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. I/O-Pins                               | Should be configured as output and driven to static low in the weakest driver mode in order to improve EMI behaviour. Confuguration of the I/O as input with pullup is also possible.                                                                  |

|                                           | Solderpad should be left open and not be connected to any other net (layout isolated PCB-pad only for soldering).                                                                                                                                      |

| 3. Output Pins including LVDS             | Should be driven static in the weakest driver mode.                                                                                                                                                                                                    |

|                                           | If static output level is not possible, the output driver should be disabled.                                                                                                                                                                          |

|                                           | Solderpad should be left open and not be connected to any other net (layout isolated PCB-pad only for soldering).                                                                                                                                      |

| 4.Input Pins without internal pull device | For pins with alternate function see product target specification to define the necessary logic level.                                                                                                                                                 |

|                                           | <ul> <li>Should be connected with high-ohmic resistor to GND (range<br/>10k – 1Meg) wherever possible. No impact on design is<br/>however expected if a direct connection to GND is made.</li> </ul>                                                   |

|                                           | Groups of 8 pins can be used to reduce number of external pull-up/down devices (keep in mind leakage current).                                                                                                                                         |

| 5. Input Pins with internal pull device   | For pins with alternate function see product specification to define the necessary logic level                                                                                                                                                         |

|                                           | <ul> <li>Should be configured as pull-down and should be activated<br/>static low (exception: if the User's Manual requires high level<br/>for alternate functions). No impact on design is expected if<br/>static high level is activated.</li> </ul> |

|                                           | Solderpad should not be connected to any other net (isolated PCB-pad only for soldering)                                                                                                                                                               |

- The ground system must be designed as follows:

- Separate analog and digital grounds.

- The analog ground must be separated into two groups:

- 1. Ground for OSC and PLL (VSSOSC for VDDOSC, VDDOSC3, VDDPF and VDDPF3) as common star point.

- 2. Ground for ADC (VSSM for VDDM, VSSMF for VDDMF/VDDAF) as common star point.

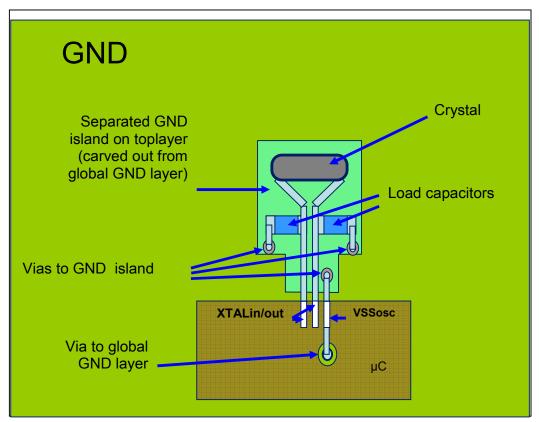

- To reduce the radiation / coupling from the oscillator circuit, a separated ground island on the GND layer should be made. This ground island can be connected at one point to the GND layer. This helps to keep noise generated by the oscillator circuit locally on this separated island. The ground connections

of the load capacitors and VSSOSC should also be connected to this island. Traces for the load capacitors and Xtal should be as short as possible.

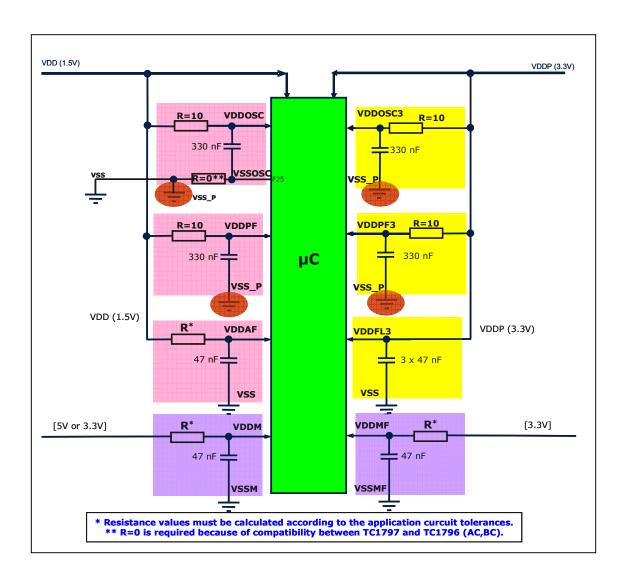

- The power distribution from the regulator to each power plane should be made over filters (see Figure 2).

- RC Filters can be inserted in the supply paths at the regulator output and at the branchings to other module supply pins like VDDOSC, VDDOSC3, VDDFL3, VDDPF, VDDPF3, VDDM, VDDMF, VDDAF (see Figure 2). Using inductance or ferrite beads (5 10 µH) instead of the resistors can improve the EME behaviour of the circuit and reduce the radiation up to ~10dBµV on the related supply net.

- OCDS must be disabled.

- Select weakest possible driver strengths and slew rates for all I/Os (see Scalable Pads AppNote AP32111).

- Use lowest possible frequency for SYSCLK.

- Avoid cutting the GND plane by via groups. A solid GND plane must be designed.

Figure 2 Filtering of VDDOSC, VDDOSC3, VDDFL3, VDDPF, VDDPF3, VDDM, VDDMF, VDDAF supply pins

# 2.1 Decoupling

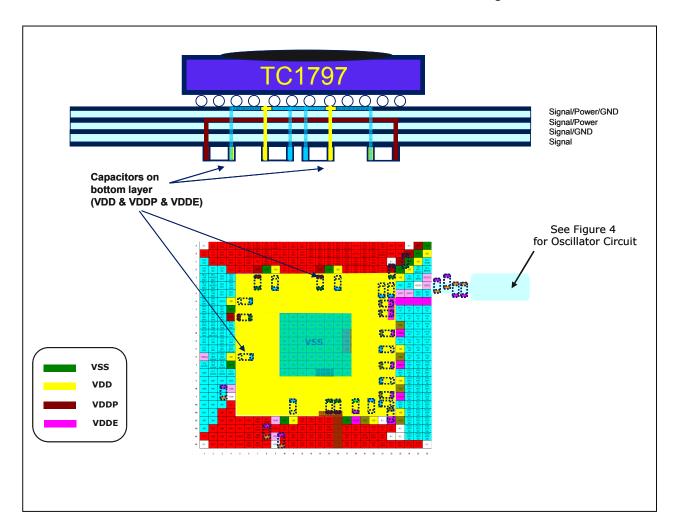

- The three supply domains VDD, VDDP and VDDEBU of TC1797 should be decoupled separately (see decoupling placement example in Figure 3).

- Type of capacitors:

- Values: 10 nF, 47 nF, 100 nF, 330 nF

- X7R Ceramic Multilayer (low ESR and low ESL)

- All supply pins should be connected first to the dedicated decoupling capacitor and then from the capacitors over vias to the power planes.

- All VSS pins should be connected to the GND.

- The decoupling capacitors should be placed directly under the IC or if necessary, some capacitors can be placed on top layer close to the supply pins of the IC.

- Ground plane on bottom layer can be used to connect the capacitors. If no plane is used, they should be connected with vias to the GND layer.

- Multiple vias should be used at capacitors to get a low impedance connection between capacitors and POWER/GND planes or pins.

- All capacitors must be placed as close as possible to the related supply pin group.

In Figure 3 shown examples are based on device power supply concept and implementation. Alternative implementations are also acceptable and must be evaluated within application by customer.

Figure 3 Capacitor Placement Example for Decoupling of TC1797 (BGA-416)

Figure 4 Layout Proposal Oscillator Circuit

# 2.2 Decoupling Capacitor List:

| Capacitor | Supply  | Pins(BGA-416) |

|-----------|---------|---------------|

| 100 nF    | VDD     | D16           |

| 100 nF    | VDD     | D9            |

| 100 nF    | VDD     | H4            |

| 100 nF    | VDD     | R4            |

| 100 nF    | VDD     | AC11          |

| 100 nF    | VDD     | AC20          |

| 100 nF    | VDD     | AB23          |

| 100 nF    | VDD     | V23           |

| 100 nF    | VDD     | P23           |

| 100 nF    | VDD     | E23           |

| 10 nF     | VDD     | D24           |

| 10 nF     | VDDP    | C23           |

| 100 nF    | VDDP    | D22           |

| 100 nF    | VDDP    | D14           |

| 100 nF    | VDDP    | D7            |

| 100 nF    | VDDP    | K4            |

| 100 nF    | VDDP    | AC16          |

| 100 nF    | VDDP    | AC16          |

| 100 nF    | VDDE    | AC18          |

| 100 nF    | VDDE    | AC22          |

| 100 nF    | VDDE    | Y23           |

| 100 nF    | VDDE    | T23           |

| 100 nF    | VDDE    | M23           |

| 100 nF    | VDDE    | H23           |

| 10 nF     | VDDE    | H23           |

| 330 nF    | VDDOSC  | F26           |

| 330 nF    | VDDOSC3 | E26           |

| 47 nF     | VDDFL3  | A18           |

| 47 nF     | VDDFL3  | B18           |

| 47 nF     | VDDFL3  | H3            |

| 330 nF    | VDDPF   | G23           |

| 330 nF    | VDDPF3  | G24           |

| 47 nF     | VDDM    | W4            |

| 47 nF     | VDDMF   | AE9           |

| 47 nF     | VDDAF   | AC9           |

<u>Note:</u> This application note contains design recommendations from Infineon Technologies point of view. Effectiveness and performance of the final application implementation must be validated by customer, based on dedicated implementation choices.