Rel. 1.3, 18.12.2009

Device TC1797

Marking/Step EES-AC, ES-AC, AC

Package P/PG-BGA-416-10

### 01710AERRA

This Errata Sheet describes the deviations from the current user documentation.

#### **Table 1** Current Documentation

| TC1797 User's Manual | V1.1 | May 2009 |

|----------------------|------|----------|

|----------------------|------|----------|

TC1797 Data Sheet V1.2 September 2009

TriCore 1 Architecture V1.3.8 January 2008

Make sure you always use the corresponding documentation for this device (User's Manual, Data Sheet, Documentation Addendum (if applicable), TriCore Architecture Manual, Errata Sheet) available in category 'Documents' at www.infineon.com/TC1797.

Each erratum identifier follows the pattern **Module\_Arch.TypeNumber**:

- Module: subsystem, peripheral, or function affected by the erratum

- Arch: microcontroller architecture where the erratum was firstly detected

- AI: Architecture Independent

- CIC: Companion ICs

- TC: TriCore

- X: XC166 / XE166 / XC2000 Family

- XC8: XC800 Family

- [none]: C166 Family

- Type: category of deviation

- [none]: Functional Deviation

- P: Parametric Deviation

- H: Application Hint

- D: Documentation Update

- Number: ascending sequential number within the three previous fields. As

this sequence is used over several derivatives, including already solved

deviations, gaps inside this enumeration can occur.

- Note: Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only.

Note: This device is equipped with a TriCore "TC1.3.1" Core. Some of the errata have workarounds which are possibly supported by the tool vendors. Some corresponding compiler switches need possibly to be set. Please see the respective documentation of your compiler.

For effects of issues related to the on-chip debug system, see also the documentation of the debug tool vendor.

The specific test conditions for EES and ES are documented in a separate Status Sheet.

## 1 History List / Change Summary

| Table 2 | History List |                                                                                                                                                                                                                                     |

|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version | Date         | Remark                                                                                                                                                                                                                              |

| 1.0     | 22.09.2008   |                                                                                                                                                                                                                                     |

| 1.1     | 04.12.2008   |                                                                                                                                                                                                                                     |

| 1.2     | 01.07.2009   | Updated Documentation Reference:- TC1797<br>User's Manual V1.1 2009-05- TC1797 Data<br>Sheet V1.1 2009-04Removed BROM_TC.H001<br>(Frequency RatiofSYS = fOSC/2 for Bootstrap<br>Loaders), see p.7-4 in TC1797 User's Manual<br>V1.1 |

| 1.3     | 18.12.2009   | Updated Documentation Reference:- TC1797 Data Sheet V1.2 2009-09. Removed FLASH_TC.036 (DFLASH Margin Control Register MARD), updated description see p.5-69 in TC1797 User's Manual V1.1                                           |

Note: Changes to the previous errata sheet version are particularly marked in column "Change" in the following tables.

Table 3 Errata fixed in this step

| Errata | Short Description | Change |

|--------|-------------------|--------|

| Errata | Snort Description | Cnange |

**Table 4** Functional Deviations

| Functional Deviation | Short Description                                                             | Cha<br>nge | Pa<br>ge |

|----------------------|-------------------------------------------------------------------------------|------------|----------|

| BCU_TC.006           | Polarity of Bit SVM in Register ECON                                          | New        | 13       |

| BROM_TC.005          | Power-on reset (PORST) while no external clock is available                   |            | 13       |

| CPU_TC.105           | User / Supervisor mode not staged correctly for Store Instructions            |            | 13       |

| CPU_TC.106           | Incorrect PSW update for certain IP instructions dual-issued with MTCR PSW    |            | 14       |

| CPU_TC.107           | SYSCON.FCDSF may not be set after FCD Trap                                    |            | 15       |

| CPU_TC.108           | Incorrect Data Size for Circular Addressing mode instructions with wraparound |            | 16       |

| CPU_TC.109           | Circular Addressing Load can overtake conflicting Store in Store Buffer       |            | 19       |

| CPU_TC.110           | Register Banks may be out of sync after FCU Trap                              |            | 22       |

| CPU_TC.111           | Imprecise Return Address for FCU Trap                                         |            | 24       |

| CPU_TC.113           | Interrupt may be taken during Trap entry sequence                             |            | 25       |

| CPU_TC.114           | CAE Trap may be generated by UPDFL instruction                                |            | 28       |

| CPU_TC.115           | Interrupt may be taken on exit from Halt mode with Interrupts disabled        |            | 29       |

| DMA_TC.013           | DMA-LMB-Master Access to Reserved Address Location                            |            | 31       |

| DMI_TC.014           | Problems with Parity Handling in TriCore Data Memories                        | Upd<br>ate | 32       |

| DMI_TC.015           | LDRAM Access Limitations for 2KByte Data Cache Configurations                 |            | 33       |

Table 4

Functional Deviations (cont'd)

| Functional     | Short Description                                                                                     | Cha        | Pa |

|----------------|-------------------------------------------------------------------------------------------------------|------------|----|

| Deviation      |                                                                                                       | nge        | ge |

| DMI_TC.016     | <b>CPU Deadlock possible when Cacheable access encounters Flash Double-Bit Error</b>                  | Upd<br>ate | 34 |

| DMI_TC.017     | DMI line buffer is not invalidated by a write to OVC_OCON.DCINVAL if cache off.                       |            | 35 |

| EBU_TC.020     | BAA Delay Options Controlled by Wrong<br>Register Field                                               |            | 37 |

| EBU_TC.021     | Incorrect delay calculation accessing Asynchronous memories                                           |            | 38 |

| EBU_TC.022     | Write Data Delay Control for<br>Asynchronous Memory Accesses                                          |            | 38 |

| FADC_TC.005    | Equidistant multiple channel-timers                                                                   |            | 39 |

| FIRM_TC.010    | Data Flash Erase Suspend Function                                                                     | New        | 41 |

| FLASH_TC.027   | Flash erase time out of specification                                                                 |            | 42 |

| FLASH_TC.035   | Flash programing time out of specification                                                            |            | 44 |

| FlexRay_Al.056 | In case eray_bclk is below eray_sclk/2,<br>TEST1.CERA/B may fail to report a<br>detected coding error |            | 44 |

| FlexRay_Al.062 | Sync frame reception after noise or aborted frame before action point                                 |            | 45 |

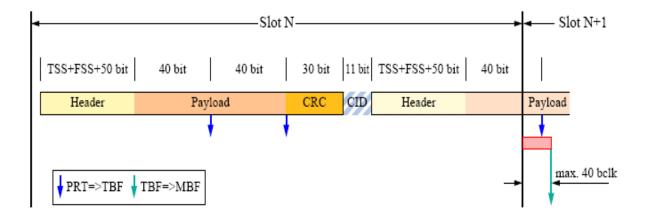

| FlexRay_Al.064 | Valid frame detection at slot boundary                                                                |            | 45 |

| FlexRay_Al.065 | For sync nodes the error interrupt flag EIR.SFO may be set too late                                   |            | 46 |

| FlexRay_Al.066 | Time stamp of the wrong channel may be used for offset correction term                                |            | 47 |

| FlexRay_Al.067 | Reception of more than gSyncNodeMax different sync frames per double cycle                            |            | 48 |

| FlexRay_Al.069 | Update of Aggregated Channel Status ACS in dynamic segment in minislots following slot ID 2047        |            | 49 |

Table 4

Functional Deviations (cont'd)

| Functional Deviation | Short Description                                                                                                            | Cha<br>nge | Pa<br>ge  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| FlexRay_Al.070       | Cycle counter MTCCV.CCV is updated erroneously in dedicated startup states                                                   | 90         | 49        |

| FlexRay_Al.071       | Faulty update of LDTS.LDTA, LDTB[10:0] due to parity error                                                                   |            | 50        |

| FlexRay_Al.072       | Improper resolution of startup collision                                                                                     |            | <b>51</b> |

| FlexRay_Al.073       | Switching from loop-back test mode at low bit rate to normal active takes longer then expected                               |            | 51        |

| FlexRay_Al.074       | Integration successful on X and integration abort on Y at the same point in time leads to inconsistent states of SUC and GTU |            | 52        |

| FlexRay_Al.075       | Detection of parity errors outside immediate scope                                                                           |            | 53        |

| FlexRay_Al.076       | CCSV.SLM [1:0] delayed to CCSV.POCS[5:0] on transitions between states WAKEUP and READY.                                     |            | 54        |

| FlexRay_Al.077       | Wakeup listen counter started one bit time early                                                                             |            | 54        |

| FlexRay_Al.078       | Payload corruption after reception of valid frame followed by slot boundary crossing frame                                   |            | 55        |

| FlexRay_Al.080       | CLEAR_RAMS command does not clear the 1st RAM word                                                                           |            | 56        |

| FlexRay_Al.081       | Write accesses to ERAY_NDIC* and ERAY_MSIC* can fail if ERAY_CLC.FMC >= 2                                                    |            | 57        |

| FlexRay_Al.082       | After detecting low level beyond gdWakeupSymbolRxWindow, the node may complete                                               |            | 57        |

Table 4

Functional Deviations (cont'd)

| <b>Functional</b> | Short Description                                                                             | Cha | Pa |

|-------------------|-----------------------------------------------------------------------------------------------|-----|----|

| Deviation         |                                                                                               | nge | ge |

| FlexRay_Al.083    | Irregular sync frame list exported in state Coldstart_Gap                                     |     | 58 |

| FlexRay_Al.084    | Corruption of frame received in slot N by second frame reception before action point          |     | 58 |

| FlexRay_Al.085    | Cycle filtering in slot 1                                                                     |     | 59 |

| FlexRay_AI.086    | Bit IBFS of Register CUST1 always 0 <sub>B</sub>                                              |     | 60 |

| FlexRay_Al.088    | A sequence of received WUS may generate redundant SIR.WUPA/B events                           |     | 61 |

| FlexRay_Al.089    | Rate correction set to zero in case of SyncCalcResult=MISSING_TERM                            |     | 61 |

| FlexRay_Al.092    | Initial rate correction value of an integrating node is zero if pMicroInitialOffsetA,B = 0x00 |     | 62 |

| FlexRay_Al.093    | Acceptance of startup frames received after reception of more than gSyncNodeMax sync frames   |     | 63 |

| FlexRay_Al.094    | Sync frame overflow flag EIR.SFO may be set if slot counter is greater than 1024              |     | 64 |

| FlexRay_Al.095    | Register RCV displays wrong value                                                             |     | 64 |

| FlexRay_Al.096    | Noise following a dynamic frame that delays idle detection may fail to stop slot              |     | 65 |

| FlexRay_Al.097    | Loop back mode operates only at 10 MBit/s                                                     |     | 66 |

| OCDS_AI.001       | DAP restart lost when DAP0 inactive                                                           |     | 66 |

| OCDS_AI.002       | JTAG Instruction must be 8 bit long                                                           |     | 67 |

| OCDS_TC.014       | Triggered Transfer does not support half word bus transactions                                |     | 68 |

| OCDS_TC.015       | IOCONF register bits affected by Application Reset                                            |     | 68 |

Table 4

Functional Deviations (cont'd)

| Functional  | Short Description                                                                | Cha | Pa |

|-------------|----------------------------------------------------------------------------------|-----|----|

| Deviation   |                                                                                  | nge | ge |

| OCDS_TC.016 | Triggered Transfer dirty bit repeated by IO_READ_TRIG                            |     | 68 |

| OCDS_TC.018 | Startup to Bypass Mode requires more than five clocks with TMS=1                 |     | 69 |

| OCDS_TC.020 | ICTTA not used by Triggered Transfer to External Address                         |     | 69 |

| OCDS_TC.021 | TriCore breaks on de-assertion instead of assertion of break bus                 |     | 70 |

| OCDS_TC.024 | Loss of Connection in DAP three-pin Mode                                         |     | 71 |

| OCDS_TC.025 | PC corruption when entering Halt mode after a MTCR to DBGSR                      |     | 72 |

| OCDS_TC.026 | PSW.PRS updated too late after a RFM instruction.                                |     | 72 |

| OCDS_TC.027 | BAM breakpoints with associated halt action can potentially corrupt the PC.      |     | 74 |

| PCP_TC.023  | JUMP sometimes takes an extra cycle                                              |     | 75 |

| PCP_TC.027  | Longer delay when clearing R7.IEN before atomic PRAM instructions                |     | 75 |

| PCP_TC.032  | Incorrect PCP behaviour following FPI timeouts (as a slave)                      |     | 75 |

| PCP_TC.034  | Usage of R7 requires delays between operations                                   |     | 76 |

| PCP_TC.035  | Atomic PRAM operation right after COPY/BCOPY                                     |     | 76 |

| PCP_TC.036  | Unexpected behaviour after failed posted FPI write                               |     | 77 |

| PCP_TC.038  | PCP atomic PRAM operations may operate incorrectly                               |     | 77 |

| PCP_TC.039  | PCP posted error interrupt to CPU may be lost when the queue is full in 2:1 mode |     | 78 |

Table 4

Functional Deviations (cont'd)

| Functional   | Short Description                                                                            | Cha | Pa |

|--------------|----------------------------------------------------------------------------------------------|-----|----|

| Deviation    |                                                                                              | nge | ge |

| RESET_TC.001 | SCU_RSTSTAT.PORST not set by a combined Debug / System / Application Reset                   |     | 79 |

| SCU_TC.016   | Reset Value of Registers ESRCFG0/1                                                           | New | 80 |

| SSC_AI.022   | Phase error detection switched off too early at the end of a transmission                    |     | 80 |

| SSC_AI.023   | Clock phase control causes failing data transmission in slave mode                           |     | 81 |

| SSC_AI.024   | SLSO output gets stuck if a reconfig from slave to master mode happens                       |     | 81 |

| SSC_AI.025   | First shift clock period will be one PLL clock too short because not syncronized to baudrate |     | 81 |

| SSC_AI.026   | Master with highest baud rate set generates erroneous phase error                            |     | 82 |

Table 5

Deviations from Electrical- and Timing Specification

| AC/DC/ADC    | Short Description                                                                                           | Cha | Pa |

|--------------|-------------------------------------------------------------------------------------------------------------|-----|----|

| Deviation    |                                                                                                             | nge | ge |

| DTS_TC.P001  | Test Conditions for Sensor Accuracy T <sub>TSA</sub>                                                        | New | 83 |

| FADC_TC.P003 | Incorrect test condition specified in datasheet for FADC parameter "Input leakage current at $V_{FAGND}$ ". |     | 83 |

| PLL_TC.P005  | PLL Parameters for f <sub>VCO</sub> > 780 MHz                                                               |     | 83 |

Table 6 Application Hints

| Hint             | Short Description                                                                     | Cha<br>nge | Pa<br>ge |

|------------------|---------------------------------------------------------------------------------------|------------|----------|

| ADC_AI.H002      | Minimizing Power Consumption of an ADC Module                                         | New        | 84       |

| CPU_TC.H004      | PCXI Handling Differences in TriCore1.3.1                                             |            | 84       |

| EBU_TC.H005      | Potential live-lock situation on concurrent CPU and PCP accesses to external memories |            | 86       |

| EBU_TC.H008      | Use of EBU standby mode                                                               |            | 87       |

| EBU_TC.H009      | Legal Parameters Allow an Invalid Page Mode Access to be Configured                   |            | 87       |

| FIRM_TC.H000     | Reading the Flash Microcode Version                                                   | New        | 88       |

| FlexRay_Al.H002  | Timer 1 Precision                                                                     |            | 88       |

| FlexRay_Al.H003  | Select upper-/lower page for IBF1/IBF2 in RAM test mode                               |            | 89       |

| FlexRay_AI.H004  | Only the first message can be received in External Loop Back mode                     |            | 89       |

| FPI_TC.H001      | FPI bus may be monopolized despite starvation protection                              |            | 90       |

| HYS_TC.H001      | Effective Hysteresis in Application Environment                                       |            | 90       |

| MSC_TC.H007      | Start Condition for Upstream Channel                                                  |            | 90       |

| MSC_TC.H008      | The LVDS pads require a settling time when coming up from pad power-down state.       |            | 91       |

| MultiCAN_AI.H005 | TxD Pulse upon short disable request                                                  |            | 92       |

| MultiCAN_AI.H006 | Time stamp influenced by resynchronization                                            |            | 92       |

| MultiCAN_TC.H002 | Double Synchronization of receive input                                               |            | 93       |

## Table 6 Application Hints (cont'd)

| Hint             | Short Description                                                                               | Cha<br>nge | Pa<br>ge |

|------------------|-------------------------------------------------------------------------------------------------|------------|----------|

| MultiCAN_TC.H003 | Message may be discarded before transmission in STT mode                                        |            | 93       |

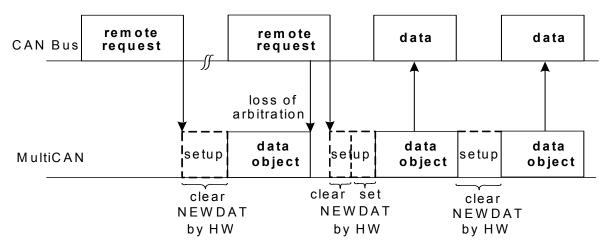

| MultiCAN_TC.H004 | Double remote request                                                                           |            | 93       |

| OCDS_TC.H001     | IOADDR may increment after aborted IO_READ_BLOCK                                                |            | 94       |

| OCDS_TC.H002     | Setting IOSR.CRSYNC during Application Reset                                                    |            | 94       |

| OCDS_TC.H003     | Application Reset during host communication                                                     |            | 95       |

| OCDS_TC.H004     | Device Identification by Application Software                                                   |            | 96       |

| PCP_TC.H004      | Invalid parity error generated by FPI write to PRAM                                             |            | 96       |

| PCP_TC.H005      | Unexpected parity errors when address 0 of CMEM is faulty                                       |            | 97       |

| PCP_TC.H006      | BCOPY address alignment error may affect next channel FPI operation                             |            | 97       |

| PCP_TC.H007      | Do not use priority 0 to post interrupt to CPU                                                  |            | 97       |

| PORTS_TC.H004    | Using LVDS Ports in CMOS Mode                                                                   |            | 98       |

| PORTS_TC.H005    | Pad Input Registers do not capture<br>Boundary-Scan data when BSD-mode<br>signal is set to high |            | 98       |

| PWR_TC.H005      | Current Peak on V <sub>DDP</sub> during Power-up                                                |            | 98       |

| SSC_AI.H001      | Transmit Buffer Update in Slave Mode after Transmission                                         |            | 99       |

| SSC_AI.H002      | Transmit Buffer Update in Master Mode during Trailing or Inactive Delay Phase                   |            | 100      |

| SSC_AI.H003      | Transmit Buffer Update in Slave Mode during Transmission                                        |            | 100      |

## Table 6 Application Hints (cont'd)

| Hint        | Short Description                        | Cha<br>nge | Pa<br>ge |

|-------------|------------------------------------------|------------|----------|

| SSC_TC.H003 | Handling of Flag STAT.BSY in Master Mode |            | 101      |

## 2 Functional Deviations

## BCU TC.006 Polarity of Bit SVM in Register ECON

The polarity of bit SVM (State of FPI Bus Supervisor Mode Signal) in the SBCU Error Control Capture register SBCU\_ECON is inverted compared to its description in the User's Manual.

Actually, it is implemented as follows:

- SVM = 0<sub>B</sub>: Transfer was initiated in user modes

- SVM = 1<sub>B</sub>: Transfer was initiated in supervisor mode

## BROM\_TC.005 Power-on reset (PORST) while no external clock is available

In case no stable clock is present at the oscillator input pin (XTAL1) after PORST, the device will wait indefinitely, i.e. it hangs and is not able to execute application code or enter one of the bootstrap loader modes.

This behavior occurs only after PORST during initialization of the FlexRay module by the internal Startup Software.

#### Workaround

Proper device start-up after PORST is only possible if a stable clock signal from an external crystal, ceramic resonator or an external clock source is to available at the XTAL1 pin of the device

## <u>CPU\_TC.105</u> User / Supervisor mode not staged correctly for Store Instructions

Bus transactions initiated by TriCore load or store instructions have a number of associated attributes such as address, data size etc. derived from the load or store instruction itself. In addition, bus transactions also have an IO privilege level status flag (User/Supervisor mode) derived from the PSW.IO bit field.

Unlike attributes derived from the instruction, the User/Supervisor mode status of TriCore initiated bus transactions is not staged correctly in the TriCore pipeline and is derived directly from the PSW. IO bit field.

This issue can only cause a problem in certain circumstances, specifically when a store transaction is outstanding (e.g. held in the CPU store buffer) and the PSW is modified to switch from Supervisor to User-0 or User-1 mode. In this case, the outstanding store transaction, executed in Supervisor mode, may be transferred to the bus in User mode (the bus systems do not discriminate between User-0 and User-1 modes). Due to the blocking nature of load transactions and the fact that User mode code cannot modify the PSW, neither of these other situations can cause a problem.

## **Example**

```

st.w [aX], dX ; Store to Supervisor mode protected SFR mtcr #PSW, dY ; Modify PSW.IO to switch to User mode ...

```

#### Workaround

Any MTCR instruction targeting the PSW, which may change the PSW.IO bit field, must be preceded by a DSYNC instruction, unless it can be guaranteed that no store transaction is outstanding.

```

st.w [aX], dX ; Store to Supervisor mode protected SFR

dsync

mtcr #PSW, dY ; Modify PSW.IO to switch to User mode

...

```

## <u>CPU\_TC.106</u> Incorrect PSW update for certain IP instructions dual-issued with MTCR PSW

In certain situations where an Integer Pipeline (IP) instruction which updates the PSW user status bits (e.g. PSW.V - Overflow) is followed immediately by an MTCR instruction targetting the PSW, with the instructions being dual-issued,

the update priority is incorrect. In this case, the PSW user status bits are updated with the value from the IP instruction rather than the later MTCR instruction. This situation only occurs in 2 cases:

- MUL/MADD/MSUB instruction followed by MTCR PSW

- RSTV instruction followed by MTCR PSW

## **Example**

```

rstv

mtcr #PSW, dY ; Modify PSW

```

#### Workaround

Insert one NOP instruction between the MUL/MADD/MSUB/RSTV instruction and the MTCR instruction updating the PSW.

```

rstv

nop

mtcr #PSW, dY ; Modify PSW

...

```

## <u>CPU\_TC.107</u> SYSCON.FCDSF may not be set after FCD Trap

Under certain conditions the SYSCON. FCDSF flag may not be set after an FCD trap is entered. This situation may occur when the CSA (Context Save Area) list is located in cacheable memory, or, dependent upon the state of the upper context shadow registers, when the CSA list is located in LDRAM.

The SYSCON.FCDSF flag may be used by other trap handlers, typically those for asynchronous traps, to determine if an FCD trap handler was in progress when the another trap was taken.

### Workaround

In the case where the CSA list is statically located in memory, asynchronous trap handlers may detect that an FCD trap was in progress by comparing the

current values of FCX and LCX, thus achieving similar functionality to the SYSCON.FCDSF flag.

In the case where the CSA list is dynamically managed, no reliable workaround is possible.

# <u>CPU\_TC.108</u> Incorrect Data Size for Circular Addressing mode instructions with wrap-around

In certain situations where a Load or Store instruction using circular addressing mode encounters the circular buffer wrap-around condition, the first access to the circular buffer may be performed using an incorrect data size, causing too many or too few data bytes to be transferred. The circular buffer wrap-around condition occurs when a load or store instruction using circular addressing mode addresses a data item which spans the boundary of a circular buffer, such that part of the data item is located at the top of the buffer, with the remainder at the base. The problem may occur in one of two cases:

#### Case 1

Where a **store** instruction using circular addressing mode encounters the circular buffer wrap-around condition, and is preceded in the LS pipeline by a multi-access load instruction, the first access of the store instruction using circular addressing mode may incorrectly use the transfer data size from the second part of the multi-access load instruction. A multi-access load instruction occurs in one of the following circumstances:

- Unaligned access to LDRAM or cacheable address which spans a 128-bit boundary.

- Unaligned access to a non-cacheable, non-LDRAM address.

- Circular addressing mode access which encounters the circular buffer wraparound condition.

Since half-word store instructions must be half-word aligned, and st.a instructions must be word aligned, they cannot trigger the circular buffer wrap-around condition. As such, this case only affects the following instructions using circular addressing mode: st.w, st.d, st.da.

## **Example**

```

LDA a8, 0xD000000E; Address of un-aligned load

LDA a12, 0xD0000820; Circular Buffer Base

LDA a13, 0x00180014; Circular Buffer Limit and Index

...

ld.w d6, [a8]; Un-aligned load, split 16+16

add d4, d3, d2; Optional IP instruction

st.d [a12/a13+c], d0/d1; Circular Buffer wrap, 32+32

...

```

In this example, the word load from address 0xD000000E is split into 2 half-word accesses, since it spans a 128-bit boundary in LDRAM. The double-word store encounters the circular buffer wrap condition and should be split into 2 word accesses, to the top and bottom of the circular buffer. However, due to the bug, the first access takes the transfer data size from the second part of the unaligned load and only 16-bits of data are written. Note that the presence of an optional IP instruction between the load and store transactions does not prevent the problem, since the load and store transactions are back-to-back in the LS pipeline.

#### Case 2

Case 2 is similar to case 1, and occurs where a **load** instruction using circular addressing mode encounters the circular buffer wrap-around condition, and is preceded in the LS pipeline by a multi-access load instruction. However, for case 2 to be a problem it is necessary that the first access of the load instruction encountering the circular buffer wrap-around condition (the access to the top of the circular buffer) also encounters a conflict condition with the contents of the CPU store buffer. Again, in this case the first access of the load instruction using circular addressing mode may incorrectly use the transfer data size from the second part of the multi-access load instruction. Since half-word load instructions must be half-word aligned, and Id.a instructions must be word aligned, they cannot trigger the circular buffer wrap-around condition. As such, this case only affects the following instructions using circular addressing mode: Id.w, Id.d, Id.da.

Note: In the current TriCore1 CPU implementation, load accesses are initiated from the DEC pipeline stage whilst store accesses are initiated from the following EXE pipeline stage. To avoid memory port contention problems when a load follows a store instruction, the CPU contains a single store buffer. In the case where a store instruction (in EXE) is immediately followed by a load instruction (in DEC), the store is directed to the CPU store buffer and the load operation overtakes the store. The store is then committed to memory from the store buffer on the next store instruction or non-memory access cycle. The store buffer is only used for store accesses to 'local' memories - LDRAM or DCache. Store instructions to bus-based memories are always executed immediately (in-order). A store buffer conflict is detected when a load instruction is encountered which targets an address for which at least part of the requested data is currently held in the CPU store buffer. In this store buffer conflict scenario, the load instruction is cancelled, the store committed to memory from the store buffer and then the load re-started. In systems with an enabled MMU and where either the store buffer or load instruction targets an address undergoing PTE-based translation, the conflict detection is just performed on address bits (9:0), since higher order bits may be modified by translation and a conflict cannot be ruled out. In other systems (no MMU, MMU disabled), conflict detection is performed on the complete address.

## Example

```

LDA a8, 0xD000000E; Address of un-aligned load

LDA a12, 0xD0000820; Circular Buffer Base

LDA a13, 0x00180014; Circular Buffer Limit and Index

...

st.h [a12]0x14, d7; Store causing conflict

ld.w d6, [a8]; Un-aligned load, split 16+16

add d4, d3, d2; Optional IP instruction

ld.d [a12/a13+c], d0/d1; Circular Buffer wrap, 32+32; conflict with st.h

```

In this example, the half-word store is to address 0xD0000834 and is immediately followed by a load instruction, so is directed to the store buffer. The

word load from address 0xD000000E is split into 2 half-word accesses, since it spans a 128-bit boundary in LDRAM. The double-word load encounters the circular buffer wrap condition and should be split into 2 word accesses, to the top and bottom of the circular buffer. In addition, the first circular buffer access conflicts with the store to address 0xD0000834. Due to the bug, after the store buffer is flushed, the first access takes the transfer data size from the second part of the un-aligned load and only 16-bits of data are read. Note that the presence of an optional IP instruction between the two load transactions does not prevent the problem, since the load transactions are back-to-back in the LS pipeline.

#### Workaround

Where it cannot be guaranteed that a word or double-word load or store instruction using circular addressing mode will not encounter one of the corner cases detailed above which may lead to incorrect behaviour, one NOP instruction should be inserted prior to the load or store instruction using circular addressing mode.

```

LDA a8, 0xD000000E; Address of un-aligned load

LDA a12, 0xD0000820; Circular Buffer Base

LDA a13, 0x00180014; Circular Buffer Limit and Index

...

ld.w d6, [a8] ; Un-aligned load, split 16+16

add d4, d3, d2 ; Optional IP instruction

nop ; Bug workaround

st.d [a12/a13+c], d0/d1; Circular Buffer wrap, 32+32

...

```

## <u>CPU\_TC.109</u> Circular Addressing Load can overtake conflicting Store in Store Buffer

In a specific set of circumstances, a load instruction using circular addressing mode may overtake a conflicting store held in the TriCore1 CPU store buffer. The problem occurs in the following situation:

- The CPU store buffer contains a byte store instruction, st.b, targeting the base address + 0x1 of a circular buffer.

- A word load instruction, ld.w, is executed using circular addressing mode, targetting the same circular buffer as the buffered byte store.

- This word load is only half-word aligned and encounters the circular buffer wrap-around condition such that the second, wrapped, access of the load instruction to the bottom of the circular buffer targets the same address as the byte store held in the store buffer.

Additionally, one of the following further conditions must also be present for the problem to occur:

- The circular buffer base address for the word load is double-word but not quad-word (128-bit) aligned i.e. the base address has bits (3:0) = 0x8 with the conflicting byte store having address bits (3:0) = 0x9, OR,

- The circular buffer base address for the word load is quad-word (128-bit) aligned and the circular buffer size is an odd number of words i.e. the base address has bits (3:0) = 0x0 with the conflicting byte store having address bits (3:0) = 0x1.

In these very specific circumstances the conflict between the load instruction and store buffer contents is not detected and the load instruction overtakes the store, returning the data value prior to the store operation.

Note: In the current TriCore1 CPU implementation, load accesses are initiated from the DEC pipeline stage whilst store accesses are initiated from the following EXE pipeline stage. To avoid memory port contention problems when a load follows a store instruction, the CPU contains a single store buffer. In the case where a store instruction (in EXE) is immediately followed by a load instruction (in DEC), the store is directed to the CPU store buffer and the load operation overtakes the store. The store is then committed to memory from the store buffer on the next store instruction or non-memory access cycle. The store buffer is only used for store accesses to 'local' memories - LDRAM or DCache. Store instructions to bus-based memories are always executed immediately (in-order). A store buffer conflict is detected when a load instruction is encountered which targets an address for which at least part of the requested data is currently held in the CPU store buffer. In this store buffer conflict scenario, the load instruction is cancelled, the store committed to memory from the store

buffer and then the load re-started. In systems with an enabled MMU and where either the store buffer or load instruction targets an address undergoing PTE-based translation, the conflict detection is just performed on address bits (9:0), since higher order bits may be modified by translation and a conflict cannot be ruled out. In other systems (no MMU, MMU disabled), conflict detection is performed on the complete address.

## **Example - Case 1**

```

LDA a12, 0xD0001008; Circular Buffer Base

LDA a13, 0x00180016; Circular Buffer Limit and Index

...

st.b [a12]0x1, d2; Store to byte offset 0x9

ld.w d6, [a12/a13+c]; Circular Buffer wrap, 16+16

...

```

In this example the circular buffer base address is double-word but not quadword aligned. The byte store to address 0xD0001009 is immediately followed by a load operation and is placed in the CPU store buffer. The word load instruction encounters the circular buffer wrap condition and is split into 2 half-word accesses, to the top (0xD0001016) and bottom (0xD0001008) of the circular buffer. The first load access completes correctly, but, due to the bug, the second access overtakes the store operation and returns the previous half-word from 0xD0001008.

## Example - Case 2

```

LDA a12, 0xD0001000; Circular Buffer Base

LDA a13, 0x00140012; Circular Buffer Limit and Index

...

st.b [a12]0x1, d2; Store to byte offset 0x1

ld.w d6, [a12/a13+c]; Circular Buffer wrap, 16+16

```

In this example the circular buffer base address is quad-word aligned but the buffer size is an odd number of words (0x14 = 5 words). The byte store to address 0xD0001001 is immediately followed by a load operation and is placed

in the CPU store buffer. The word load instruction encounters the circular buffer wrap condition and is split into 2 half-word accesses, to the top (0xD0001012) and bottom (0xD0001000) of the circular buffer. The first load access completes correctly, but, due to the bug, the second access overtakes the store operation and returns the previous half-word from 0xD0001000.

#### Workaround

For any circular buffer data structure, if byte store operations (st.b) are not used targeting the circular buffer, or if the circular buffer has a quad-word aligned base address and is an even number of words in depth, then this problem cannot occur. If these restrictions and the other conditions required to trigger the problem cannot be ruled out, then any load word instruction (ld.w) targeting the buffer using circular addressing mode, and which may encounter the circular buffer wrap condition, must be preceded by a single NOP instruction.

```

LDA a12, 0xD0001000; Circular Buffer Base

LDA a13, 0x00140012; Circular Buffer Limit and Index

...

st.b [a12]0x1, d2; Store to byte offset 0x1

nop; Workaround

ld.w d6, [a12/a13+c]; Circular Buffer wrap, 16+16

...

```

## <u>CPU\_TC.110</u> Register Banks may be out of sync after FCU Trap

In order to improve the performance of Upper Context Save and Restore operations (Call, Interrupt etc.) the current TriCore1 CPU implementation contains shadow registers for the upper context General Purpose Registers (GPRs), D8-D15 and A10-A15, forming a foreground and a background bank. In normal operation read and write accesses to the upper context registers target the same bank, with read and write accesses targetting different banks just during upper context save and restore operations.

However, in a certain corner case where an FCU trap is taken, read and write accesses to the register banks remain out of synchronisation in the FCU trap handler and cannot be easily re-synchronised. Since FCU traps are non-

recoverable system errors, with some system state already lost, maintaining correct behaviour is not critical. However, due to the bug, it is no longer straightforward to discriminate FCU traps from other context management (Class 3) traps. Since the read and write pointers to the register banks are incorrect in the bug situation, the update of D15 with the Trap Identification Number (TIN) will write to one bank whilst the read of D15 in the trap handler will read the other (incorrect) bank, returning an invalid TIN. For similar reasons, the upper context GPRs are unusable in an FCU trap handler, since register read and write operations may target different banks.

The problem occurs in the following situation:

- FCX (Free Context Pointer) points to an invalid location (Null End of CSA list, Invalid Segment Virtual or Peripheral segment).

- CALL / CALLI instruction is in the decode pipeline stage and would generate an FCU trap due to the invalid FCX pointer.

- Instruction in the Load-Store pipeline execute stage encounters a synchronous trap condition (VAF-D, VAP-D, MPR, MPW, MPP, MPN, ALN, MEM, DSE, SOVF, OVF), which would also be converted into an FCU trap.

#### Workaround

The LCX (Free Context List Limit) pointer should be initialised in order to trap impending context list overflow before the FCU condition is encountered. However, in order to maintain some system function in the case of an FCU trap, the following workaround is required, split into two parts.

Firstly, the Context Management (Class 3) trap handler must be modified to discriminate FCU traps that incorrectly appear to have a TIN pertaining to another Class 3 trap due to the bug. This is done by checking for the correct behaviour of the upper context registers and jumping to the FCU trap handler if the register file behaviour is found to be in error:

```

_class3_handler:

mov d12, #7

nop

nop

jne d12, #7, _fcu_handler

mov d12, #-8

nop

```

```

nop

jne d12, #-8, _fcu_handler

; Now read valid D15 to obtain TIN

```

Since the initial contents of the upper context registers are unknown, it is necessary to check one of the upper context registers twice, with different values, in case the initial contents match the first value to be checked.

Note: The NOP instructions in the above code are mandatory to ensure that reads from the GPRs target the register file directly, rather than the forwarding paths which always function correctly.

Secondly, within the FCU trap handler itself, only the global and lower context registers may be used, D0-D7 and A0-A9. Since the upper context information is already lost in an FCU trap condition, usage of the global and lower context registers without previously saving this information is acceptable.

## **CPU TC.111** Imprecise Return Address for FCU Trap

The FCU trap is taken when a context save operation is attempted but the free context list is found to be empty, or when an error is encountered during a context save or restore operation. In failing to complete the context operation, architectural state is lost, so the occurrence of an FCU trap is a non-recoverable system error.

Since FCU traps are non-recoverable system errors, having a precise return address is not important, but can be useful in establishing the cause of the FCU trap. The TriCore1 CPU does not generate a precise return address for an FCU trap if the cause of the FCU trap was one of the following trap types: FCD, DAE, DIE, CAE or NMI.

In each of these circumstances the return address may be invalid.

#### Workaround

None

## **CPU TC.113** Interrupt may be taken during Trap entry sequence

A problem exists whereby interrupts are not correctly disabled at the very beginning of a trap entry sequence, and under certain circumstances an interrupt may be taken at the start of a trap handler. The problem occurs when an interrupt request is received by the TriCore CPU within a window spanning a single clock cycle either side of a trap condition being detected, and where interrupts are enabled and the interrupt priority number is higher than the current CPU priority number (CCPN). In this case the trap entry sequence begins and the upper context registers are stored to the appropriate CSA. However, before the first instruction of the trap handler is executed the interrupt condition is detected and the interrupt handler entered at a time when interrupts should be disabled. This problem affects all trap types but does not affect interrupts - an interrupt cannot be taken during the entry sequence of another interrupt.

It should be noted that no state information is lost when this issue occurs. When the interrupt handler completes and the RFE instruction is executed, program execution restarts with the first instruction of the interrupted trap handler and the trap handler then continues as normal.

The main issue associated with this problem is that the handling of the interrupt will delay the start of the trap handler. For the majority of trap types associated with the program flow this is not a problem. However, where the interrupted trap type denotes a serious system problem, such as an NMI trap, the delay in servicing the trap may be of concern. In addition, if interrupts are re-enabled within the interrupt handler then the delay in returning to the trap handler will be further extended by the handling of any additional higher priority interrupt requests which may occur. However, once processing of the initial interrupt handler is complete and the RFE instruction executed to return to the trap handler, interrupts are correctly disabled immediately and the trap handler will continue, even if further interrupts are pending when the RFE instruction is executed.

Another point to note is that this issue can cause some assumptions made in system software to be invalid. For example, if a system does not allow interrupts or traps to re-enable interrupts - then it would have been safe to assume that whenever a trap or interrupt is entered, that the code that has been suspended (and hence the state information saved in the CSA) is for a user task and

typically non-privileged. Unfortunately, with this issue that premise no longer holds - the code interrupted and state saved in a CSA can be that of a privileged trap handler. Dealing with this changed circumstance is easy, provided it is considered whenever CSA's are examined or manipulated.

#### Workaround

As described previously, the main problem associated with this erratum is the delay that may be incurred before the servicing of certain critical trap types, such as NMI, if no additional action is taken. If this is an issue for a system, then in order to minimize the impact of this erratum it is necessary to adapt the interrupt handlers to check for the occurrence of this issue and react accordingly.

The occurrence of this issue may be checked for by one of two methods, dependent upon whether all trap classes or just a limited set are considered timing critical.

If it is required to check for the occurrence of this issue for all trap classes, then this may be performed by checking the value of the PCXI.PIE register bit within the interrupt handlers, before any further context operations (such as BISR) are performed. If PCXI.PIE is clear, such that no interrupt should have been taken, then this indicates the occurrence of this issue. Although when this method is used then it is preferred to check the value of PCXI.PIE before any further context operations are performed, it is possible to use this method after additional context operations have been performed. In this case it is necessary to traverse the CSA list to check the required PCXI.PIE value from the appropriate saved context.

If it is necessary within a system to check for the occurrence of this issue just for specific, timing critical, trap classes, then this may be performed by examination of the return address, held in the A11 register, within the interrupt handler and comparing this return address against the trap vector address(es). For example, if only the NMI trap is a system issue requiring immediate action, the following code may be added to the interrupt handler to determine if the interrupt was taken at the start of the NMI handler:

```

< Timing critical section of Interrupt Handler >

movh.a a12, #@his(NMITrapAddress); BTV OR 0xE0

```

```

lea a12, [a12]@los(NMITrapAddress) ; BTV OR 0xE0

eq.a d13, a12, a11 ; Compare with A11, result in d13

< Call / Branch to NMI handler based on d13 result >

```

Note that this code segment assumes that the  $\mathtt{BTV}$  CSFR is static during runtime. If this is not the case then it would be necessary to determine the trap offset address during runtime by reading the  $\mathtt{BTV}$  CSFR and ORing with the TCN offset of the trap of interest. If more than one trap class is considered timing critical within a system, it is possible to adapt the previous code to check the return address of the interrupt handler against a number (or range) of trap class entry addresses.

If the interrupted traps are considered recoverable, and are not time sensitive, the interrupt handler can simply complete and it's terminating RFE will correctly return execution to the first instruction of the trap handler - where it will now execute to completion without undesired interruption. If the interrupted traps are considered recoverable but are time sensitive and need to be executed immediately, then some method of deferring the interrupt processing is required. If the test of the situation (e.g. checking the PCXI.PIE bit is clear) is at the start of the Interrupt handler, then there are two simple methods to consider:

The first method would be to re-request the interrupt, by writing the appropriate Service Request Control Register with the SETR bit set to one, and then executing an RFE which will be taken back to the trap handler. The interrupt will now be pending again, but will not be taken until the trap handler executes its RFE to re-enable interrupts. This method is simple if the device (and hence it's SRC register address) generating the interrupt is known. If this is not easy to determine (statically or dynamically), the second method might be preferred.

The second method would be to jump to the trap handler, after setting the trap identification number (TIN) and the return address (which the trap handler will use) to be the next instruction in the interrupt handler. This relies on the fact that the CSA saved away by the preemption of the trap handler is equally valid as an execution context for the interrupt handler. The code for this method is as follows:

```

interruptN:

mfcr   d15, PCXI

jnz.t   d15, 23, interruptReal

```

```

; force CSA into memory

dsync

sh.h

d14, d15, #12

insert d15, d14, d15, #6, #16

mov.a a15, d15

; load trap value of d15 from CSA

ld.w d15, [a15]0x3C

mov.a a15, a11

movh.a all, #@his(interuptReal)

a11, [a11]@los(interruptReal)

; jump to trap handler, will return to interruptReal

jі

a15

; the remaining part of the interrupt handler

interruptReal:

```

Again it is preferred that this method be used immediately at the beginning of the interrupt handler, since this approach works straightforwardly provided there is no state in the Upper Context registers or on the interrupt stack that is required by the interrupt handler when it returned to. Although it is possible to adapt this approach to operate later during interrupt handling, additional steps need to be taken to ensure the correct state is maintained when returning to the interrupt handler.

## CPU\_TC.114 CAE Trap may be generated by UPDFL instruction

UPDFL is a User mode instruction implemented as part of the TriCore1 Floating-Point Unit (FPU), which allows individual bits of the PSW user status bits, PSW[31:24], to be set or cleared. Contrary to early revisions of the TriCore1.3.1 architecture manual, and in contrast to most other FPU instructions, the UPDFL instruction should not generate Co-Processor Asynchronous Error (CAE) traps. However, in certain circumstances the TriCore1.3.1 FPU will generate CAE traps for UPDFL instructions.

The TriCore1.3.1 FPU will generate a CAE trap upon execution of the UPDFL instruction in the following situation:

- After execution of the UPDFL instruction, one or more of the PSW [31:26] bits are set either the PSW bit(s) are set by UPDFL or were set prior to execution and not cleared by the UPDFL instruction.

- FPU traps are enabled for one of the asserted PSW[31:26] bits, via the corresponding FPU TRAP CON.FxE bit being set.

- The FPU\_TRAP\_CON.TST CSFR bit is clear no previous FPU trap has been generated without the subsequent clearing of FPU\_TRAP\_CON.TST.

#### Workaround

The UPDFL instruction is normally used in one of two situations:

- Clearing the FPU sticky flags held in PSW [30:26].

- Setting the FPU rounding mode bits in PSW[25:24].

In the first case, if all the PSW[31:26] bits are cleared by UPDFL, no CAE trap will be generated.

In the second case, UPDFL may still be used to set the FPU rounding mode, but in this case the remaining PSW bits, [31:26], must be cleared by UPDFL in order to avoid generation of an unexpected CAE trap.

In all other cases, where FPU traps are enabled, some other method of manipulating the PSW user status bits must be used in order to avoid extraneous CAE trap generation. For instance, if in Supervisor mode the PSW may be read using the MFCR instruction, the high order PSW bits modified and written back using the MTCR instruction.

# <u>CPU\_TC.115</u> Interrupt may be taken on exit from Halt mode with Interrupts disabled

A problem exists whereby an interrupt may be taken by the TriCore CPU upon exiting Halt mode, even if interrupts are disabled at that point.

The problem occurs when an interrupt request is received by the TriCore CPU, with the pending interrupt priority number (PIPN) higher than the current CPU priority number (CCPN), and interrupts are enabled. In this case, where only the CPU pipeline status is preventing the interrupt from being taken immediately, the interrupt is latched and taken as soon as the pipeline can accept an interrupt. This may cause unexpected behavior whilst debugging, where

interrupts are enabled before entry to Halt mode, or where interrupts are temporarily enabled during Halt mode. In this case an interrupt may be latched whilst the CPU is in Halt mode, and subsequently disabling interrupts during Halt mode, by setting  $ICR.IE = 0_B$ , will not prevent the interrupt from being serviced immediately upon exit from Halt mode.

It should be noted that no corruption of the program flow is associated with this issue and that it affects debugging only, primarily the debugger single-stepping functionality. The problem may or may not be visible whilst debugging, dependent upon the implementation of single-stepping by the debugger. If single-stepping is implemented by the debugger setting Break-Before-Make (BBM) breakpoints on all instructions except the next to be executed, then if this problem occurs the next instruction when single-stepping will be the first instruction of the interrupt handler. However, if single-stepping is implemented by setting a Break-After-Make (BAM) breakpoint on the next instruction to be executed, or a BBM breakpoint on the next but one instruction, the problem will not be visible. In this case, when single-stepping, the interrupt handler will be executed in its entirety before returning to the interrupted program flow and the breakpoint being taken after the next instruction to be single-stepped.

#### Workaround

As described previously, this problem affects debug only and in this case the taking of the interrupt immediately upon exit from Halt mode cannot be avoided if the conditions to trigger the problem occur. However, the debugger single-stepping functionality may be implemented in such a way that this problem does not directly affect the user, as follows:

Upon first hitting a breakpoint, the debugger should read and hold the current interrupt enable status from ICR.IE. Interrupts should then be disabled by setting ICR.IE =  $0_B$ .

If the next debugger action is to single-step, a BAM breakpoint should be placed on the next instruction to be executed and the CPU re-started. In this case a previously latched interrupt may be serviced, but will not result in a further breakpoint being flagged until the interrupt handler returns and the next instruction intended to be single-stepped is executed.

Subsequent single-step operations may be implemented using any appropriate method, since interrupts will be disabled before Halt mode is entered.

If the debugger action is to re-start normal execution, the interrupt enable status should be restored from the value read upon hitting the initial breakpoint and the CPU re-started.

### **DMA TC.013 DMA-LMB-Master Access to Reserved Address Location**

DMA-LMB-Master goes into an unintentional lock-up state when a Read or Write access is made to a reserved memory location with an unrecognised slave.

Subsequent Read/Write accesses from a DMA Channel, MLI, Cerberus or the DMA-FPI-Slave to all memory locations mapped to the DMA-LMB-Master  $(80000000_{\rm H}\ {\rm to}\ {\rm DFFFFFF}_{\rm H})$  will be halted until control of the DMA-LMB-Master is regained.

In the case of a lock-up DMA-LMB-Master Read access, the next LMB access and associated response will have the following effect:

- ERROR Response: The DMA-LMB-Master will treat this error response as its own. It will clear the lock-up state and return an error to the DMA access requester. Normal operation will then continue. Halted DMA access requests will resume. There is no corruption of the data flow.

- NSC (No Special Condition) Acknowledge: The DMA-LMB-Master will treat

this response as its own and again clear the lock-up state. The correct

response to an unrecognised slave is an ERROR. Therefore the DMA-LMBMaster has signalled an invalid response back to the DMA access requester

resulting in a corruption of the data flow.

- RETRY Response: The DMA-LMB-Master will treat the retry response as its

own and again clear the lock-up state. The access will be repeated to the

same reserved address location again resulting in a lock-up condition. The

sequence is broken by the first ERROR response or NSC acknowledge.

The effect of a DMA-LMB-Master Write accesses to an unrecognised slave is the same as above with one exception:

If the next access is a Read access from the EBU-LMB-Slave then the DMA-LMB-Master will clear the lock-up state and respond as above. The EBU read completes but the data read by the Originator (e.g. TriCore) will be the write data of the DMA-LMB-Master Write access.

The following should be noted:

- At all times the DMA-FPI-Master and DMA-FPI-Slave remain accessible.

- If the LMB-DMA-Master is in the lock-up state then accesses can still be made to the LMB bus by all other LMB-Masters (e.g. LFI-LMB-Master).

#### Hint

Do not perform a DMA channel, MLI, Cerberus or DMA-FPI-Slave access to a reserved address: all areas specified as reserved in the Memory Map Chapter, LMB Address Map Table must not be accessed by the DMA (ME, MLI, Cerberus).

#### Workaround

The LMB-Bus-Control-Unit can recognise a DMA-LMB-Master access to an unrecognised slave. It can be programmed to raise an interrupt and then generate a Class 3 Application Reset to clear the lock-up state.

## **DMI TC.014** Problems with Parity Handling in TriCore Data Memories

A small number of cases exist in which the handling of parity errors in the TriCore data memories (LDRAM, DCache and Data Cache Tag) does not function correctly, potentially leading to data corruption for accesses to these memories. This data corruption may occur whether the access to one of these memories is from the TriCore CPU, or, in the case of LDRAM, from another bus master access via the LMB.

#### Workaround

In systems where the Data Memory parity handling must be enabled, the following is required to guarantee correct behaviour:

Compatibility mode must be selected for the TriCore Data side memories by setting COMPAT.DIE = 1<sub>B</sub>. In this case parity errors are signalled to the SCU and returned to the CPU as an NMI trap, rather than as a DIE trap directly to the CPU.

**AND**

If the system has a data cache, the data cache must be used to cache readonly data only (such as Flash contents). Writes to cacheable locations must not be used with the Data Cache enabled.

Note that this does not concern the program side which works as expected.

## <u>DMI\_TC.015</u> LDRAM Access Limitations for 2KByte Data Cache Configurations

TriCore1.3.1 based devices are physically built with a certain size of Data Memory (DMEM) and a data tag memory to support a certain maximum size of Data Cache (DCache). Within these physical limitations, software may select the exact split between LDRAM and DCache where DMEM size = LDRAM size + DCache size. The software selection is performed according to the configuration of the DCache size in DMI\_CON.DC\_SZ\_CFG, with any DMEM not configured as DCache ordinarily available as LDRAM.

However, a problem exists where the DCache is configured to be 2KByte, DMI\_CON.DC\_SZ\_CFG =  $0001_B$ . In this case the expected amount of LDRAM is available for accesses from the CPU (DMEM size - 2KByte), but the address range checking is incorrect for accesses to LDRAM from the LMB and the available LDRAM size for LMB accesses is limited to (DMEM size - 4KByte).

## Example

A TC1767 device is physically built to support a maximum of 72KByte DMEM and 4KByte DCache. Where the DCache size is configured as 4KByte, available LDRAM is 68KByte, where the DCache size is configured as 0KByte, available LDRAM is 72KByte. However, when the DCache size is configured as 2KByte, 70KByte LDRAM is addressable by the CPU, but only the bottom 68KByte is addressable by LMB bus masters.

#### Workaround

In systems where a 2KByte DCache is configured, the top 2KByte of LDRAM is only available for usage by the CPU, and cannot contain data structures that may be required by other bus masters. For instance, this space could be used as part of the CSA list. However, note that since this memory is not addressable

by LMB masters in the 2KByte DCache configuration, this would affect debuggers. Hence it would only be possible to view this memory space in a debugger if it takes appropriate steps to make the memory region accessable (e.g. by temporarily setting the DCache size to 0KByte) to examine that address range.

## <u>DMI\_TC.016</u> CPU Deadlock possible when Cacheable access encounters Flash Double-Bit Error

A problem exists whereby the TriCore CPU may become deadlocked when attempting a mis-aligned load access to a cacheable address. The problem will be triggered in the following situation:

- The TriCore CPU executes a load instruction whose target address is not naturally aligned - a data word access which targets an address which is not word aligned, or a data / address double-word access which is not doubleword aligned.

- The mis-aligned load access targets a cacheable address, whether the device is configured with a data cache or not.

- The mis-aligned load access spans two halves of the same 128-bit cache line. For instance, a data word access with address offset 6<sub>H</sub>.

- The mis-aligned load access results in a cache miss, which will refill the 128-bit cache line / Data Line Buffer (DLB) via a Block Transfer 2 (BTR2) read transaction on the LMB, and this LMB read encounters a bus error condition in the second beat of the block transfer.

It should be noted that under normal operation, LMB block transfers will not result in a bus error condition being flagged on the second beat of a block transfer. However, such a condition may be encountered when accessing the on-chip Flash, if the second double-word of data accessed from the Flash (for the second half of the cache line) contains an uncorrectable double-bit error.

When this condition is triggered, the first part of the requested data is obtained from the valid first beat of the BTR2 transfer, and the second part is required from the errored second beat. In this case, no error is flagged to the TriCore CPU and the transaction is incorrectly re-started on the LMB. In the case of a Flash double-bit error, this transaction will be re-tried continuously on the LMB

by the DMI LMB master and the CPU become deadlocked. This situation would then only be recoverable by a Watchdog reset.

The problem exists within the DMI DLB, which is used as a single cache line when no data cache is configured, and as a streaming buffer when data cache is present. As such the problem affects all load accesses to cacheable locations, whether data cache is configured or not, since the DLB is used in both cases.

Note: This problem affects load accesses to the on-chip Flash only. Instruction fetches which encounter a similar condition (bus error on later beat of block transfer) behave as expected and will return a PSE trap upon any attempt to execute an instruction from a Flash location containing a double-bit error.

#### Workaround

As described previously, this problem should not be encountered during normal operation and will only be triggered in the case of a double-bit error being detected in an access to the on-chip Flash.

However, in order to remove the possibility of encountering this issue, all load accesses to cacheable addresses within the on-chip Flash should be made using natural alignment - word transfers should be word aligned, double-word transfers double-word aligned.

It is also possible to check for the occurrence of this problem by having some other master, such as the PCP, periodically poll the LBCU LEATT register to check for the occurrence of LMB error conditions, specifically if one is detected during a BTR2 read transfer from the DMI, as reported by LEATT.OPC and LEATT.TAG.

## <u>DMI\_TC.017</u> DMI line buffer is not invalidated by a write to OVC OCON.DCINVAL if cache off.

A problem exists whereby the DMI line buffer is not invalidated by a write to OVC\_OCON.DCINVAL when operating with the D-cache turned off. This means that the user cannot rely on a write to OVC\_OCON.DCINVAL to make sure that any stale data in the DMI line buffer is invalidated. This can be a

problem for users who want to use the OVC\_OCON.DCINVAL bit to ensure coherency between the DMI and background memory.

It should be noted that this problem is not encountered when the D-cache is turned on. When the D-cache is turned on, writing a one to OVC\_OCON.DCINVAL will correctly invalidate all clean cache entries and invalidate the DMI line buffer. The problem only concerns systems with no cache or systems where the cache is turned off.

## **Detailed description**

#### D-Cache turned on:

When D-cache is turned on, the DMI line buffer is only used as a performance enhancement mechanism with no logical existence to the user. It is therefore not operating as a micro-cache and the current issue does not apply. When the dcache is turned on, writing to OVC\_OCON.DCINVAL will always invalidate all clean lines in the dcache. No stale data will subsist in the DMI line buffer.

#### D-Cache turned off:

The problem occurs when the dcache is turned off. When the dcache is turned off (or non-existent) the DMI line buffer operates as a 16-byte cache. Writing a one to the OVC\_OCON.DCINVAL register should invalidate the data inside the DMI line buffer as long as the data is not dirty. This invalidation mechanism does not work on AUDO-Future devices. Writing to OVC\_OCON.DCINVAL will have no effect at all. Any cache line which was previously loaded into the DMI line buffer will not be invalidated (whether it was dirty or not).

#### Workaround

The workaround consists in executing a cachei.wi instruction with an operand register containing a random non-protected cacheable address. The DMI line buffer will respond to cachei.wi instructions regardless of the content of its operand, provided that the operand contains a cacheable address which is not protected. On execution of cachei.wi, the DMI line buffer will flush and invalidate itself. For example, executing the following two instructions should flush and invalidate the DMI line buffer in any circumstance. Note that the current workaround always invalidates the entry regardless of whether it was dirty or not.

```

movh.a a0, #0x8000;; Cachei operand is random non-protected cacheable address. cachei.wi [a0] ;; The DLB gets invalidated regardless of the value in a0.

```

If the user is not concerned in invalidating the DMI line buffer but simply guaranteeing its coherency with external memory then there is another simple workaround. This consists in issueing a read to a dummy cacheable address pointing outside the 16-byte block containing the next required data. Access to the next required data will then necessarily result in a refill and the resulting data will be coherent. This is what the following code does (a0 contains a dummy address and a1 contains the address for the user's required data).

```

movh.a a0, #0x8000;; Dummy address is 0x80000000.

ld.w d0, [a0] ;; a0 has to point to different 16-byte block than a1.

ld.w d0, [a1] ;; This load will be executed fresh from memory with a refill.

;; Read data will be coherent with rest of memory.

```

# EBU\_TC.020 BAA Delay Options Controlled by Wrong Register Field

The timing options for the BAA signal are specified as being controlled by the settings of the <code>BUSRCONX.EXTCLOCK</code> and <code>BUSRCONX.EBSE</code> register fields. In the implementation of the EBU, the logic controlling BAA timing was connected to the <code>BUSRCONX.ECSE</code> field instead of <code>BUSRCONX.EBSE</code>.

#### Workaround

Use the  ${\tt BUSRCONx.ECSE}$  field to control the desired timing option for the  $\overline{\mbox{BAA}}$  signal.

# **EBU\_TC.021** Incorrect delay calculation accessing Asynchronous memories

The EBU has the facility for the flash clock to run continuously by setting one of the BUSRCONx.BFCMSEL to  $0_{\rm B}$ . In this case, as all attached devices see the same clock, then all accesses requiring a flash clock will use the BUSRAPx.EXTCLOCK setting from the region which has BUSRCONx.BFCMSEL = $0_{\rm B}$  when determining the correct delays for the various control signals enabled by the ECSE and EBSE bits.

However, no distinction was made for asynchronous regions to enable them to use a separate method of delay calculation so, if a continuous flash clock is enabled, signal delays for asynchronous accesses will be calculated using the same EXTCLOCK value as that used for synchronous accesses instead of the EXTCLOCK value in the registers of the region being accessed.

## Workaround

If the continuous flash clock mode is in use, adjust the phase lengths for the asynchronous regions to compensate for the modified signal delays.

# **EBU\_TC.022** Write Data Delay Control for Asynchronous Memory Accesses

The EBU allows the timing of the write data driven onto the EBU\_AD(31:0) pins to be adjusted using the EBU\_BUSWCONx.ECSE and EBU\_BUSWAPx.EXTCLOCK register fields. This delay mechanism is not working as specified for asynchronous write accesses:

- The time at which write data is disabled cannot be delayed by half a clock cycle. Register settings where a half clock cycle delay would be expected will result in a full clock cycle of delay.

- The time at which write data is enabled is never delayed. The bus will always

be driven as if no delay was in effect. If the register settings require the data

to be delayed then invalid data will be driven for the delay period.

- The time at which valid write data is driven cannot be delayed by half a clock cycle. Register settings where a half clock cycle delay would be expected will result in no delay being applied.

This results in the timing detailed in the table below, where CP1 is the first clock cycle of the command phase, DHn is the last clock cycle of the Data Hold Phase and  $T_{CLK}$  is one period of the EBU clock:

Table 7 Write Data Signal Timing

| EXTCLOCK is set to                                  | Driven at:        | Priven at:                  |                             | Removed at:                      |  |

|-----------------------------------------------------|-------------------|-----------------------------|-----------------------------|----------------------------------|--|

|                                                     | Delay<br>Disabled | Delay<br>Enabled            | Delay<br>Disabled           | Delay<br>Enabled                 |  |

| 00 <sub>B</sub>                                     | Start of CP1      | Start of<br>CP1             | End of<br>DHn <sup>1)</sup> | End of DHn<br>+ T <sub>CLK</sub> |  |

| 01 <sub>B</sub> , 10 <sub>B</sub> , 11 <sub>B</sub> | Start of<br>CP1   | End of<br>CP1 <sup>2)</sup> | End of DHn                  | End of DHn<br>+ T <sub>CLK</sub> |  |

<sup>1)</sup> DHn indicates the final Data Hold Phase. If no Data Hold is programmed, this will be CPn, the final Command Phase.

## Workaround

Adjust the phase lengths for the asynchronous regions to compensate for the modified signal delays.

# <u>FADC\_TC.005</u> Equidistant multiple channel-timers

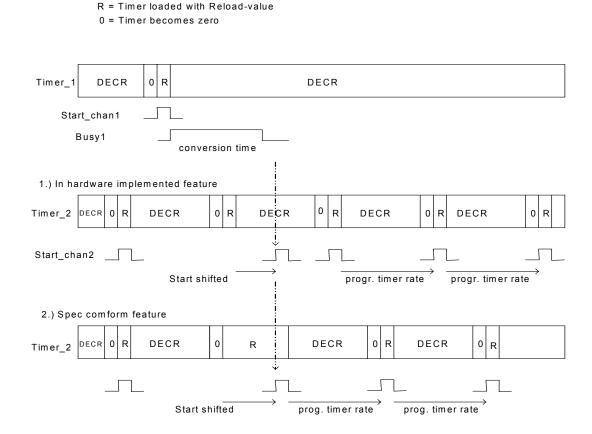

The description is an example for timer\_1 and timer\_2, but can also affect all other combinations of timers.

Timer\_1 and Timer\_2 are running with different reload-values. Both timers should start conversions with the requirement of equidistant timing.

# Problem description:

Timer\_1 becomes zero and starts a conversion. Timer\_2 becomes zero during this conversion is running and sets the conversion-request-bit of channel\_2. At the end of the conversion for channel\_1 this request initiates a start for channel\_2. But the Timer\_2 is reloaded only when setting the request-bit for channel\_2 and is decremented during the conversion of channel\_1.

<sup>2)</sup> Data bus will be enabled at the beginning of CP1

The correct behavior would be a reload when the requested conversion (of channel\_2) is started.

Therefore the start of conversion for channel\_2 is delayed by maximum one conversion-time. After this delay it will be continued with equidistant conversion-starts. Please refer to the following figure.

Note: the programmed timer rate is much longer than the conversion time, this means that the fault is much smaller than in the picture

Figure 1 Timing concerning equidistant multiple timers

#### Workaround

Use one timer base in combination with neighboring trigger and selection by software which result has to be taken into account.

## FIRM TC.010 Data Flash Erase Suspend Function

This problem affects devices with microcode version V11 (see FIRM\_TC.H000 for identification of the microcode version):

A sector DFx in the Data Flash may not be correctly erased when two successive erase operations are executed **without** any programming between the erase operations, as described in the following sequence  $(x, y = 0 \text{ or } 1, x \neq y)$ :

- 1. A Program Flash sector or a Data Flash sector (DFy or DFx) has been erased.