# SAA7134HL

## PCI audio and video broadcast decoder

Rev. 04 — 31 March 2006

**Product data sheet**

The SAA7134HL is a single chip solution to digitize and decode video and sound, and to capture both data streams through the PCI-bus.

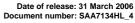

Special means are incorporated to maintain the synchronization of audio to video. The device offers versatile peripheral interfaces (GPIO), that support various extended applications, e.g. analog audio pass-through for loop back cable to the sound card, or capture of DTV and DVB transport streams, such as Vestigial Side Band (VSB), Orthogonal Frequency Division Multiplexing (OFDM) and Quadrature Amplitude Modulation (QAM) decoded digital television standards, see Figure 1.

Fig 1. Application diagram for capturing live TV video and audio streams in the PC, with optional extensions for enhanced audio feature processing or DTV and DVB capture

#### 1.1 Introduction

The PCI audio and video broadcast decoder SAA7134HL is a highly integrated, low cost and solid foundation for TV capture in the PC, for analog TV and digital video broadcast. The various multimedia data types are transported over the PCI-bus by bus-master-write, to optimally exploit the streaming capabilities of a modern host based system. Legacy requirements are also taken care of.

The SAA7134HL meets the requirements of *PC design guides 98/99 and 2001* and is PCI 2.2 and Advanced Configuration and Power Interface (ACPI) compliant.

The analog video is sampled by 9-bit ADCs, decoded by a multi-line adaptive comb filter and scaled horizontally, vertically and by field rate. Multiple video output formats (YUV and RGB) are available, including packed and planar, gamma-compensated or black-stretched.

Analog TV sound is digitized and stereo decoded (NICAM and dual FM standards). Audio is streamed digitally via the PCI-bus or routed as an analog signal via the loop back cable to the sound card.

The SAA7134HL provides a versatile peripheral interface to support system extensions, e.g. MPEG encoding for time shift viewing, or DSP applications for audio enhancements.

The channel decoder for digital video broadcast reception (ATSC or DVB) can re-use the integrated video ADCs.

The Transport Stream (TS) is collected by a tailored interface and pumped through the PCI-bus to the system memory in well-defined buffer structures. Various internal events, or peripheral status information, can be enabled as an interrupt on the PCI-bus.

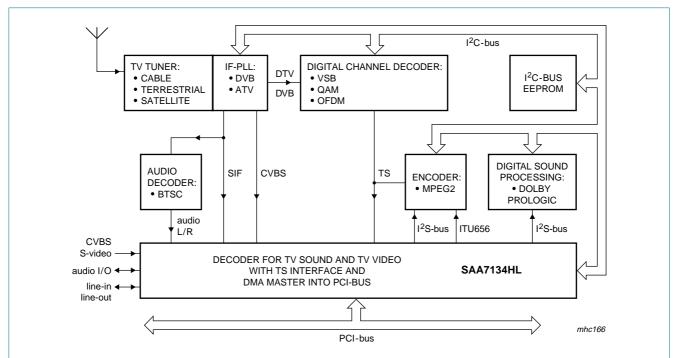

## 1.2 Overview of TV decoders with PCI bridge

A TV decoder family with PCI interfacing has been created to support worldwide TV broadcasting. The pin compatibility of these TV decoders offers the opportunity to support different TV broadcast standards with one PCB layout.

Table 1: TV decoder family with PCI interfacing

| TV parameter      | 1                                              | TV decoder type [1] |           |                   |                   |  |  |

|-------------------|------------------------------------------------|---------------------|-----------|-------------------|-------------------|--|--|

|                   |                                                | SAA7130HL           | SAA7133HL | SAA7134HL         | SAA7135HL         |  |  |

| PCI bridge        | version                                        | 2.2                 | 2.2       | 2.2               | 2.2               |  |  |

|                   | DMA channel                                    | 7                   | 7         | 7                 | 7                 |  |  |

| TV video decoding | PAL, NTSC and SECAM                            | X                   | X         | Х                 | X                 |  |  |

| Video scaling     | 2 dimension and 2 task scaler                  | X                   | X         | X                 | Х                 |  |  |

| Raw VBI           | 27 MHz sampling rate                           | Χ                   | Χ         | Χ                 | Χ                 |  |  |

| TV sound          | FM A2 and NICAM                                | -                   | -         | Χ                 | Χ                 |  |  |

| decoding          | BTSC (dbx-TV) plus<br>SAP; EIAJ                | -                   | X         | -                 | Х                 |  |  |

|                   | stereo sampling (I <sup>2</sup> S-bus and DMA) | -                   | 32 kHz    | 32 kHz,<br>48 kHz | 32 kHz,<br>48 kHz |  |  |

| Radio             | FM radio stereo                                | -                   | X         | -                 | X                 |  |  |

Table 1: TV decoder family with PCI interfacing...continued

## 1.3 Related documents

This document describes the functionality and characteristics of the SAA7134HL.

Other documents related to the SAA7134HL are:

- User manual SAA7130HL/34HL, describing the programmability

- Application note SAA7130HL/34HL, pointing out recommendations for system implementation

- Demonstration and reference boards, including description, schematics, etc.:

- Proteus-Pro: TV capture PCI card for analog TV (standards: B/G, I, D/K and L/L')

- Europe: hybrid DVB-T and analog TV capture PCI card for European broadcasting

- Data sheets of other devices referred to in this document, e.g:

- TDA9852: BTSC stereo decoder

- Tuners:

FI1216 for PAL B/G

FI1216MF for PAL B/G + SECAM

FI1246 for PAL I

FI1256 for PAL D/K

- TD1316: ATV+DVB-T tuner

- TDA10045: DVB channel receiver

- TDA9886: analog IF-PLL

- TDA9889: digital IF-PLL

<sup>[1]</sup> X =function available.

SAA6752HS: MPEG-2 video and MPEG-audio/AC-3 audio encoder with multiplexer

## 2. Features

## 2.1 PCI and DMA bus mastering

- PCI 2.2 compliant including full Advanced Configuration and Power Interface (ACPI)

- System vendor ID, etc. via EEPROM

- Hardware support for virtual addressing by MMU

- DMA bus master write for video, audio, VBI and TS

- Configurable PCI FIFOs, graceful overflow

- Packed and planar video formats, overlay clipping

## 2.2 TV video decoder and video scaling

- All-standards TV decoder: NTSC, PAL and SECAM

- Five analog video inputs: CVBS and S-video

- Video digitizing by two 9-bit ADCs at 27 MHz

- Sampling according ITU-R BT.601 with 720 pixels/line

- Adaptive comb filter for NTSC and PAL, also operating for non-standard signals

- Automatic TV standard detection

- Three level Macrovision copy protection detection according to Macrovision detect specification revision 1

- Control of brightness, contrast, saturation and hue

- Versatile filter bandwidth selection

- Horizontal and vertical downscaling or zoom

- Adaptive anti-alias filtering

- Capture of raw VBI samples

- Two alternating settings for active video scaling

- Output in YUV and RGB

- Gamma compensation, black stretching

#### 2.3 TV sound decoder and audio I/O

- TV stereo decoding for NICAM and dual FM

- Audio sampling locked to video field rate, no drift of audio stream against video stream

- On-chip stereo audio ADCs and DACs (2 x 16-bit)

- Sampling rate, e.g. 32 kHz, 44.1 kHz and 48 kHz

- Integrated analog audio pass-through for analog audio loop back cable to sound card

## 2.4 Peripheral interface

- I<sup>2</sup>C-bus master interface: 3.3 V and 5 V

- Digital video output: ITU and VIP formats

- TS input: serial or parallel

- General purpose I/O, e.g. for strapping and interrupt

Propagate reset and ACPI state D3-hot

## 2.5 General

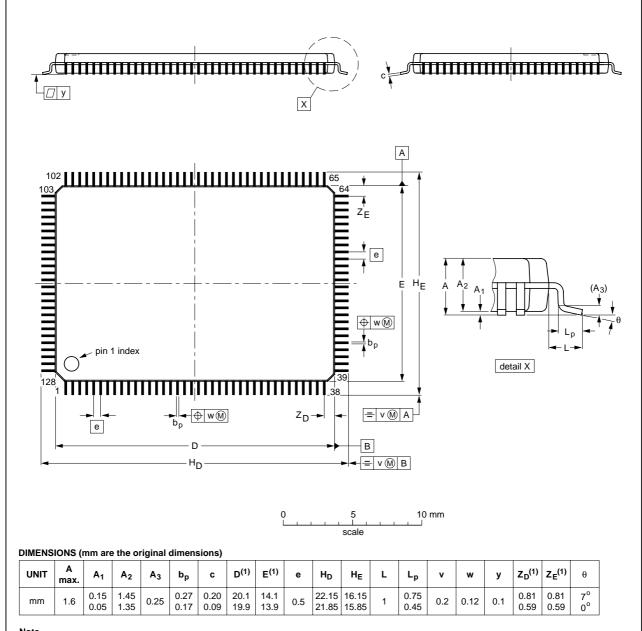

- Package: LQFP128

- Power supply: 3.3 V only

- Power consumption of typical application: 1.1 W

- Standby state (D3-hot): < 0.02 W

- All interface signals 5 V tolerant

- Reference designs available

- SDK for Windows (98, 2000 and XP) and Windows Driver Model (WDM)

# 3. Ordering information

**Table 2: Ordering information**

| Туре      | Package |                                                                                     |          |  |  |  |

|-----------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|

| number    | Name    | Description                                                                         | Version  |  |  |  |

| SAA7134HL | LQFP128 | plastic low profile quad flat package; 128 leads; body $14 \times 20 \times 1.4$ mm | SOT425-1 |  |  |  |

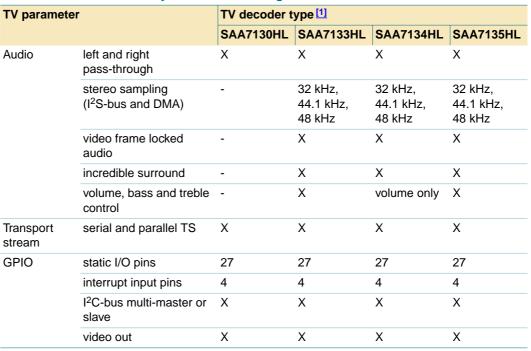

# **Block diagram**

Rev. 04

Product data sheet

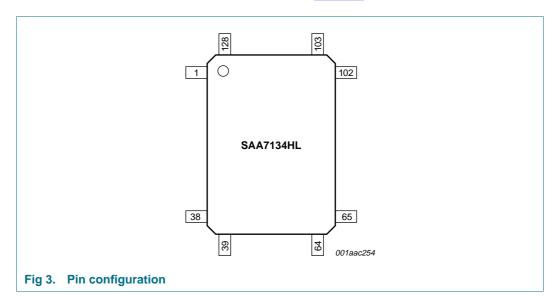

# 5. Pinning information

## 5.1 Pinning

The SAA7134HL is packaged in a rectangular Low profile Quad Flat Package (LQFP) with 128 pins, see Figure 3.

All the pins are shown sorted by number in Table 3.

Functional pin groupings are given in the following tables:

Power supply pins: <u>Table 4</u>

PCI interface pins: <u>Table 5</u>

Analog interface pins: <u>Table 6</u>

Joint Test Action Group (JTAG) test interface pins for boundary scan test: Table 7

I<sup>2</sup>C-bus multi-master interface: Table 8

General purpose interface (pins GPIO) and the main functions: Table 9

The characteristics of the pin types are detailed in Table 10.

Table 3: Pin allocation table

| Pin | Symbol    | Pin | Symbol    | Pin | Symbol    | Pin | Symbol            |

|-----|-----------|-----|-----------|-----|-----------|-----|-------------------|

| 1   | $V_{DDD}$ | 33  | C/BE[1]#  | 65  | $V_{DDD}$ | 97  | $V_{SSA}$         |

| 2   | GNT#      | 34  | AD[15]    | 66  | V_CLK     | 98  | RIGHT1            |

| 3   | REQ#      | 35  | AD[14]    | 67  | GPIO17    | 99  | $V_{REF0}$        |

| 4   | AD[31]    | 36  | AD[13]    | 68  | GPIO16    | 100 | RIGHT2            |

| 5   | AD[30]    | 37  | AD[12]    | 69  | GPIO15    | 101 | V <sub>REF1</sub> |

| 6   | AD[29]    | 38  | $V_{DDD}$ | 70  | GPIO14    | 102 | $V_{REF2}$        |

| 7   | AD[28]    | 39  | $V_{SSD}$ | 71  | GPIO13    | 103 | OUT_RIGHT         |

| 8   | AD[27]    | 40  | PCI_CLK   | 72  | GPIO12    | 104 | OUT_LEFT          |

| 9   | AD[26]    | 41  | AD[11]    | 73  | $V_{DDD}$ | 105 | PROP_RST_N        |

SAA7134HL\_4

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

| Pin | Symbol           | Pin | Symbol           | Pin | Symbol    | Pin | Symbol            |

|-----|------------------|-----|------------------|-----|-----------|-----|-------------------|

| 10  | AD[25]           | 42  | AD[10]           | 74  | $V_{SSD}$ | 106 | SIF               |

| 11  | AD[24]           | 43  | AD[09]           | 75  | GPIO11    | 107 | V <sub>REF3</sub> |

| 12  | C/BE[3]#         | 44  | AD[08]           | 76  | GPIO10    | 108 | V <sub>SSA</sub>  |

| 13  | IDSEL            | 45  | C/BE[0]#         | 77  | GPIO9     | 109 | CV2_C             |

| 14  | AD[23]           | 46  | AD[07]           | 78  | GPIO8     | 110 | $V_{DDA}$         |

| 15  | AD[22]           | 47  | AD[06]           | 79  | GPIO7     | 111 | V <sub>REF4</sub> |

| 16  | AD[21]           | 48  | AD[05]           | 80  | GPIO6     | 112 | DRCV_Y            |

| 17  | AD[20]           | 49  | AD[04]           | 81  | GPIO5     | 113 | V <sub>SSA</sub>  |

| 18  | AD[19]           | 50  | AD[03]           | 82  | GPIO4     | 114 | CV0_Y             |

| 19  | $V_{DDD}$        | 51  | AD[02]           | 83  | GPIO3     | 115 | $V_{DDA}$         |

| 20  | V <sub>SSD</sub> | 52  | AD[01]           | 84  | GPIO2     | 116 | CV1_Y             |

| 21  | AD[18]           | 53  | AD[00]           | 85  | GPIO1     | 117 | DRCV_C            |

| 22  | AD[17]           | 54  | $V_{DDD}$        | 86  | GPIO0     | 118 | CV3_C             |

| 23  | AD[16]           | 55  | V <sub>SSD</sub> | 87  | GPIO27    | 119 | V <sub>SSA</sub>  |

| 24  | C/BE[2]#         | 56  | GPIO23           | 88  | GPIO26    | 120 | CV4               |

| 25  | FRAME#           | 57  | GPIO22           | 89  | GPIO25    | 121 | TRST_N            |

| 26  | IRDY#            | 58  | GPIO21           | 90  | SCL       | 122 | TCK               |

| 27  | TRDY#            | 59  | GPIO20           | 91  | SDA       | 123 | TMS               |

| 28  | DEVSEL#          | 60  | GPIO19           | 92  | $V_{DDD}$ | 124 | TDO               |

| 29  | STOP#            | 61  | GPIO18           | 93  | $V_{SSD}$ | 125 | TDI               |

| 30  | PERR#            | 62  | XTALI            | 94  | LEFT2     | 126 | INT_A             |

| 31  | SERR#            | 63  | XTALO            | 95  | $V_{DDA}$ | 127 | PCI_RST#          |

| 32  | PAR              | 64  | $V_{SSD}$        | 96  | LEFT1     | 128 | V <sub>SSD</sub>  |

# 5.2 Pin description

Table 4: Power supply pins

| Symbol           | Pin                                     | Туре | Description                                                        |

|------------------|-----------------------------------------|------|--------------------------------------------------------------------|

| $V_{SSA}$        | 97, 108,<br>113<br>and 119              | AG   | analog ground for integrated analog signal processing              |

| V <sub>DDA</sub> | 95, 110<br>and 115                      | AS   | analog supply voltage for integrated analog signal processing      |

| V <sub>SSD</sub> | 20, 39,<br>55, 64,<br>74, 93<br>and 128 | VG   | digital ground for digital circuit, core and input/outputs         |

| V <sub>DDD</sub> | 1, 19, 38,<br>54, 65,<br>73<br>and 92   | VS   | digital supply voltage for digital circuit, core and input/outputs |

Table 5: PCI interface pins [1]

|                         | iterrace pir                                                                   |                  | B                                                                                                                                         |

|-------------------------|--------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | Pin                                                                            | Туре             | Description                                                                                                                               |

| PCI_CLK                 | 40                                                                             | PI               | PCI clock input: reference for all bus transactions, up to 33.33 MHz                                                                      |

| PCI_RST#                | 127                                                                            | PI               | PCI reset input: will 3-state all PCI pins (active LOW)                                                                                   |

| AD[31] to AD[00]        | 4 to 11,<br>14 to 18,<br>21 to 23,<br>34 to 37,<br>41 to 44<br>and<br>46 to 53 | PIO and<br>T/S   | multiplexed address and data input or output: bi-directional, 3-state                                                                     |

| C/BE[3]# to<br>C/BE[0]# | 12, 24,<br>33<br>and 45                                                        | PIO and<br>T/S   | command code input or output: indicates type of requested transaction and byte enable, for byte aligned transactions (active LOW)         |

| PAR                     | 32                                                                             | PIO and<br>T/S   | parity input or output: driven by the data source, even parity over all pins AD and C/BE#                                                 |

| FRAME#                  | 25                                                                             | PIO and<br>S/T/S | frame input or output: driven by the current bus master (owner), to indicate the beginning and duration of a bus transaction (active LOW) |

| TRDY#                   | 27                                                                             | PIO and<br>S/T/S | target ready input or output: driven by the addressed target, to indicate readiness for requested transaction (active LOW)                |

| IRDY#                   | 26                                                                             | PIO and<br>S/T/S | initiator ready input or output: driven by the initiator, to indicate readiness to continue transaction (active LOW)                      |

| STOP#                   | 29                                                                             | PIO and<br>S/T/S | stop input or output: target is requesting the master to stop the current transaction (active LOW)                                        |

| IDSEL                   | 13                                                                             | PI               | initialization device select input: this input is used to select<br>the SAA7134HL during configuration read and write<br>transactions     |

| DEVSEL#                 | 28                                                                             | PIO and<br>S/T/S | device select input or output: driven by the target device, to acknowledge address decoding (active LOW)                                  |

| REQ#                    | 3                                                                              | РО               | PCI request output: the SAA7134HL requests master access to PCI-bus (active LOW)                                                          |

| GNT#                    | 2                                                                              | PI               | PCI grant input: the SAA7134HL is granted to master access PCI-bus (active LOW)                                                           |

| INT_A                   | 126                                                                            | PO and<br>O/D    | interrupt A output: this pin is an open-drain interrupt output, conditions assigned by the interrupt register                             |

| PERR#                   | 30                                                                             | PIO and<br>S/T/S | parity error input or output: the receiving device detects data parity error (active LOW)                                                 |

| SERR#                   | 31                                                                             | PO and<br>O/D    | system error output: reports address parity error (active LOW)                                                                            |

|                         |                                                                                |                  |                                                                                                                                           |

<sup>[1]</sup> PCI-bus pins are located on the long side of the package to simplify PCI board layout requirements.

Table 6: Analog interface pins [1]

| Symbol | Pin | Туре | Description                                      |

|--------|-----|------|--------------------------------------------------|

| XTALI  | 62  | CI   | quartz oscillator input: 32.11 MHz or 24.576 MHz |

| XTALO  | 63  | CO   | quartz oscillator output                         |

| LEFT2  | 94  | Al   | analog audio stereo left 2 input or mono input   |

Table 6:

Analog interface pins [1]...continued

| Symbol            | Pin | Type | Description                                                                                                                                                                              |  |

|-------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>DDA</sub>  | 95  | AS   | analog supply voltage (3.3 V)                                                                                                                                                            |  |

| LEFT1             | 96  | Al   | analog audio stereo left 1 input or mono input; default analog pass-through to pin OUT_LEFT after reset                                                                                  |  |

| V <sub>SSA</sub>  | 97  | AG   | analog ground (for audio)                                                                                                                                                                |  |

| RIGHT1            | 98  | AI   | analog audio stereo right 1 input or mono input; default analog pass-through to pin OUT_RIGHT after reset                                                                                |  |

| V <sub>REF0</sub> | 99  | AR   | analog reference ground for audio Sigma Delta ADC; to be connected directly to analog ground (V <sub>SSA</sub> )                                                                         |  |

| RIGHT2            | 100 | Al   | analog audio stereo right 2 input or mono input                                                                                                                                          |  |

| V <sub>REF1</sub> | 101 | AR   | analog reference voltage for audio Sigma Delta ADC; to be connected directly to analog supply voltage ( $V_{DDA}$ ) and via a 220 nF capacitor to pin $V_{REF0}$                         |  |

| $V_{REF2}$        | 102 | AR   | analog reference voltage for audio Sigma Delta ADC; to be supported with two parallel capacitors of 47 $\mu F$ and 0.1 $\mu F$ to analog ground (V_SSA)                                  |  |

| OUT_RIGHT         | 103 | AO   | analog audio stereo right channel output; 1 V (RMS) line-out, feeding the audio loop back cable via a coupling capacitor of 2.2 μF                                                       |  |

| OUT_LEFT          | 104 | AO   | analog audio stereo left channel output; 1 V (RMS) line-out, feeding the audio loop back cable via a coupling capacitor of 2.2 $\mu F$                                                   |  |

| PROP_RST_N        | 105 | AO   | analog output for test and debug purposes (active LOW)                                                                                                                                   |  |

| SIF               | 106 | Al   | sound IF input from TV tuner (4.5 MHz to 9.2 MHz); coupling capacitor of 47 pF after the termination with 50 $\Omega$                                                                    |  |

| V <sub>REF3</sub> | 107 | AR   | analog reference voltage for audio FIR-DAC and SCART audio input buffer; to be supported with two parallel capacitors of 47 $\mu\text{F}$ and 0.1 $\mu\text{F}$ to analog ground (V_SSA) |  |

| V <sub>SSA</sub>  | 108 | AG   | analog ground                                                                                                                                                                            |  |

| CV2_C             | 109 | Al   | composite video input (mode 2) or C input (modes 6 and 8)                                                                                                                                |  |

| $V_{DDA}$         | 110 | AS   | analog power supply (3.3 V)                                                                                                                                                              |  |

| V <sub>REF4</sub> | 111 | AR   | analog reference voltage; to be supported with a capacitor of 220 nF to analog ground (V <sub>SSA</sub> )                                                                                |  |

| DRCV_Y            | 112 | AR   | differential reference connection (for CV0 and CV1); to be supported with a capacitor of 47 nF to analog ground $(V_{\mbox{\footnotesize SSA}})$                                         |  |

| $V_{SSA}$         | 113 | AG   | analog ground                                                                                                                                                                            |  |

| CV0_Y             | 114 | Al   | composite video input (mode 0) or Y input (modes 6 and 8)                                                                                                                                |  |

| $V_{DDA}$         | 115 | AS   | analog supply voltage (3.3 V)                                                                                                                                                            |  |

| CV1_Y             | 116 | Al   | composite video input (mode 1) or Y input (modes 7 and 9)                                                                                                                                |  |

| DRCV_C            | 117 | AR   | differential reference connection (for CV2, CV3 and CV4); to be supported with a capacitor of 47 nF to analog ground ( $V_{\rm SSA}$ )                                                   |  |

Table 6: Analog interface pins 11...continued

| Symbol    | Pin | Type | Description                                               |

|-----------|-----|------|-----------------------------------------------------------|

| CV3_C     | 118 | Al   | composite video input (mode 3) or C input (modes 7 and 9) |

| $V_{SSA}$ | 119 | AG   | analog ground                                             |

| CV4       | 120 | Al   | composite video input (mode 4)                            |

<sup>[1]</sup> The SAA7134HL offers an interface for analog video and audio signals. The related analog supply pins are included in this table.

Table 7: JTAG test interface pins

|        |     | -    |                                                                    |

|--------|-----|------|--------------------------------------------------------------------|

| Symbol | Pin | Type | Description                                                        |

| TRST_N | 121 | I    | test reset input: drive LOW for normal operating (active LOW)      |

| TCK    | 122 | I    | test clock input: drive LOW for normal operating                   |

| TMS    | 123 | I    | test mode select input: tie HIGH or let float for normal operating |

| TDO    | 124 | 0    | test serial data output: 3-state                                   |

| TDI    | 125 | I    | test serial data input: tie HIGH or let float for normal operating |

Table 8: I<sup>2</sup>C-bus multi-master interface

| Symbol     | Pin | Туре | Description                                                      |

|------------|-----|------|------------------------------------------------------------------|

| SCL        | 90  | IO2  | serial clock input (slave mode) or output (multi-master mode)    |

| SDA        | 91  | 102  | serial data input and output; always available                   |

| PROP_RST_N | 105 | GO   | propagate reset and D3-hot output; to peripheral board circuitry |

Table 9: GPIO pins and functions [1]

| Symbol | Pin | Туре | Function                                   |                                        |                     |             |  |  |  |  |

|--------|-----|------|--------------------------------------------|----------------------------------------|---------------------|-------------|--|--|--|--|

|        |     |      | Audio and video port outputs               | TS capture inputs                      | Raw DTV/DVB outputs | GPIO        |  |  |  |  |

| GPIO27 | 87  | GIO  | A_SDO (I <sup>2</sup> S-bus data)          | -                                      | -                   | R/W         |  |  |  |  |

| GPIO26 | 88  | GIO  | A_WS<br>(I <sup>2</sup> S-bus word select) | -                                      | -                   | R/W         |  |  |  |  |

| GPIO25 | 89  | GIO  | A_SCK (I <sup>2</sup> S-bus clock)         | -                                      | -                   | R/W         |  |  |  |  |

| V_CLK  | 66  | GO   | V_CLK (also gated)                         | -                                      | ADC_CLK (out)       | -           |  |  |  |  |

| GPIO23 | 56  | GIO  | HSYNC                                      | -                                      | ADC_C[0] (LSB)      | R/W,<br>INT |  |  |  |  |

| GPIO22 | 57  | GIO  | VSYNC                                      | TS_LOCK<br>(channel<br>decoder locked) | -                   | R/W,<br>INT |  |  |  |  |

| GPIO21 | 58  | GIO  | -                                          | TS_S_D<br>(bit-serial data)            | -                   | R/W         |  |  |  |  |

| GPIO20 | 59  | GIO  | -                                          | TS_CLK<br>(< 33 MHz)                   | -                   | R/W         |  |  |  |  |

| Symbol             | Pin                               | Type Function |                                                                    |                                        |                     |             |  |

|--------------------|-----------------------------------|---------------|--------------------------------------------------------------------|----------------------------------------|---------------------|-------------|--|

|                    |                                   |               | Audio and video port outputs                                       | TS capture inputs                      | Raw DTV/DVB outputs | GPIO        |  |

| GPIO19             | 60                                | GIO           | -                                                                  | TS_SOP<br>(packet start)               | -                   | R/W         |  |

| GPIO18             | 61                                | GIO           | VAUX2                                                              | -                                      | X_CLK_IN            | R/W,<br>INT |  |

| GPIO17             | 67                                | GIO           | VAUX1 (e.g. VACTIVE)                                               | -                                      | ADC_Y[0] (LSB)      | R/W         |  |

| GPIO16             | 68                                | GIO           | -                                                                  | TS_VAL (valid flag)                    | -                   | R/W,<br>INT |  |

| GPIO15 to<br>GPIO8 | 69 to<br>72<br>and<br>75 to<br>78 | GIO           | VP[7:0] for formats:<br>ITU-R BT.656, VMI,<br>VIP (1.1, 2.0), etc. | -                                      | ADC_Y[8:1]          | R/W         |  |

| GPIO7 to<br>GPIO0  | 79 to<br>86                       | GIO           | VP extension for 16-bit<br>formats: ZV, VIP-2,<br>DMSD, etc.       | TS_P_D[7:0]<br>(byte-parallel<br>data) | ADC_C[8:1]          | R/W         |  |

- [1] The SAA7134HL offers a peripheral interface with General Purpose Input/Output (GPIO) pins. Dedicated functions can be selected:

- a) Digital Video Port (VP): output only; in 8-bit and 16-bit formats, such as VMI, DMSD (ITU-R BT.601); zoom-video, with discrete sync signals; ITU-R BT.656; VIP (1.1 and 2.0), with sync encoded in SAV and EAV codes.

- b) Transport Stream (TS) capture input: from the peripheral DTV/DVB channel decoder; synchronized by Start Of Packet (SOP); in byte-parallel or bit-serial protocol.

- c) Digitized raw DTV/DVB samples stream output: from internal ADCs; to feed the peripheral DTV/DVB channel decoder.

- d) GPIO: as default (no other function selected); static (no clock); read and write from or to individually selectable pins; latching 'strap' information at system reset time.

- e) Peripheral interrupt (INT) input: enabled by interrupt enable register; routed to PCI interrupt (INT\_A).

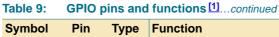

## 5.2.1 Pin type description

Table 10: Characteristics of pin types and remarks

| Pin type | Description                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------|

| AG       | analog ground                                                                                           |

| Al       | analog input; video, audio and sound                                                                    |

| AO       | analog output                                                                                           |

| AR       | analog reference support pin                                                                            |

| AS       | analog supply voltage (3.3 V)                                                                           |

| CI       | CMOS input; 3.3 V level (not 5 V tolerant)                                                              |

| СО       | CMOS output; 3.3 V level (not 5 V tolerant)                                                             |

| GI       | digital input (GPIO); 3.3 V level (5 V tolerant)                                                        |

| GIO      | digital input/output (GPIO); 3.3 V level (5 V tolerant)                                                 |

| GO       | digital output (GPIO); 3.3 V level (5 V tolerant)                                                       |

| I        | JTAG test input                                                                                         |

| IO2      | digital input and output of the I <sup>2</sup> C-bus interface; 3.3 V and 5 V compatible, auto-adapting |

Table 10: Characteristics of pin types and remarks...continued

level is LOW

## 6. Functional description

#### 6.1 Overview of internal functions

The SAA7134HL is able to capture TV signals over the PCI-bus in personal computers by a single chip; see Figure 4.

The SAA7134HL incorporates two 9-bit video ADCs and the entire decoding circuitry of any analog TV signal: NTSC, PAL and SECAM, including non-standard signals, such as playback from a VCR. The adaptive multi-line comb filter provides superb picture quality, component separation, sharpness and high bandwidth. The video stream can be cropped and scaled to the needs of the application. Scaling down as well as zooming up is supported in the horizontal and vertical direction, and an adaptive filter algorithm prevents aliasing artifacts. With the acquisition unit of the scaler two different 'tasks' can be defined, e.g. to capture video to the CPU for compression, and write video to the screen from the same video source but with different resolution, color format and frame rate.

The SAA7134HL contains TV sound stereo decoding from Sound IF (SIF), for NICAM standards and dual carrier FM systems, as used in European and Asian countries. Baseband stereo audio sampling is also implemented, e.g. for capturing from a camcorder or externally decoded BTSC. The audio sampling rate can be locked to the video frame rate to ensure synchronization (lip-sync) between the video and audio data flow, e.g. for storage, compression or time shift viewing applications.

The SAA7134HL incorporates analog audio pass-through and support for the analog audio loop back cable to the sound card function.

The decoded video streams are fed to the PCI-bus, and are also applied to a peripheral streaming interface, in ITU, VIP or VMI format. A possible application extension is on-board hardware MPEG compression, or other feature processing. The compressed data is fed back through the peripheral interface, in parallel or serial format, to be captured by the system memory through the PCI-bus. The Transport Stream (TS) from a DTV/DVB channel decoder can be captured through the peripheral interface in the same way.

Audio, video and transport streams are collected in a configurable FIFO with a total capacity of 1 kB. The DMA controller monitors the FIFO filling degree and master-writes the audio and video stream to the associated DMA channel. The virtual memory address space (from OS) is translated into physical (bus) addresses by the on-chip hardware Memory Management Unit (MMU).

The application of the SAA7134HL is supported by reference designs and a set of drivers for the Windows operating system (Windows driver model compliant).

## 6.2 Application examples

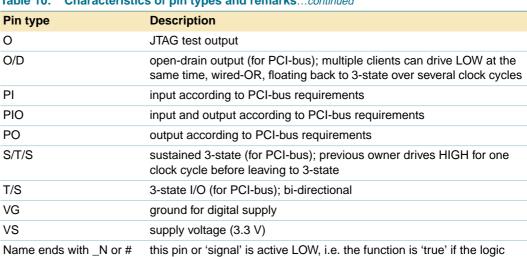

The SAA7134HL enables PC TV capture applications both on the PC motherboard and on PCI add-on TV capture cards. <u>Figure 5</u> and <u>Figure 6</u> illustrate some examples of add-on card applications.

<u>Figure 5</u> shows the basic application to capture video from analog TV sources. The proposed tuner types incorporate the RF tuning function and the IF downconversion. Usually the IF downconversion stage also includes a single channel and analog sound FM demodulator. The Philips tuner FI1216MK2 is dedicated to the 50 Hz system B/G standard as used in Europe. The FI1236MK2 is the comparable type for the 60 Hz system M standard for the USA. Both types are suited for terrestrial broadcast and for cable reception. The tuner provides composite video and baseband audio as mono or 'multiplexed' (mpx) in case of BTSC. These analog video and sound signals are fed to the appropriate input pins of the SAA7134HL.

Further analog video input signals, CVBS and/or Y-C, can be connected via the board back-panel, or the separate front connectors, e.g. from a camcorder. Accompanying stereo audio signals can also be fed to the SAA7134HL.

Video is digitized and decoded to YUV. TV sound is digitized and decoded to stereo audio, according to NICAM or dual FM standards. The digital streams are pumped via DMA into the PCI memory space.

The SAA7134HL incorporates means for legacy analog audio signal routing. The on-chip audio DACs convert the digital decoded stereo signal into analog audio. This analog audio input signal is fed via an analog audio loop back cable into the line-in of a legacy sound card. An external audio signal, that would have otherwise connected directly to the sound card, is now routed through the SAA7134HL. This analog pass-through is enabled as default by a system reset, i.e. without any driver involvement and before system setup.

During the power-up procedure, the SAA7134HL will investigate the on-board EEPROM to load the board specific system vendor ID and board version ID into the related places of the PCI configuration space. The board vendor can store other board specific data in the EEPROM that is accessible via the  $I^2C$ -bus.

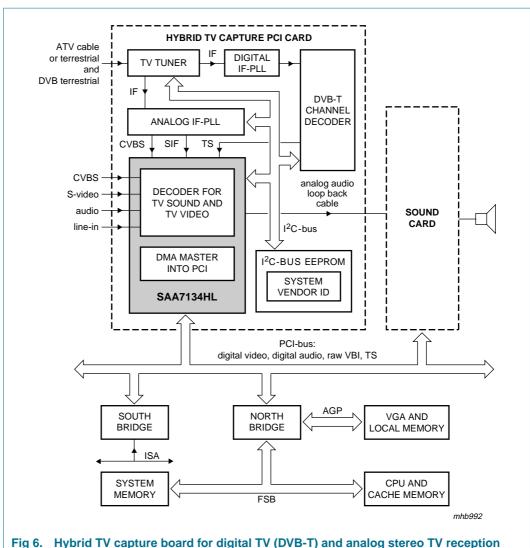

<u>Figure 6</u> shows an application extension with a hybrid TV tuner front-end and digital terrestrial channel decoding for DTV-T.

The single-conversion tuner TD1316 provides two dedicated IF signals for the analog IF-PLL (TDA9886) and the digital IF-PLL (TDA9889). The CVBS (video) and SIF (sound) output signals of the analog IF-PLL can be routed to one of the video inputs and the SIF input of the SAA7134HL for analog TV decoding. On the other hand, the 2nd IF signal of the digital IF-PLL is fed directly to the interface of the channel decoder (TDA10045), which decodes the signal into a digital DVB-T Transport Stream (TS).

The SAA7134HL captures this TS via the dedicated peripheral interface into the configurable internal FIFO for DMA into the PCI memory space.

The packet structure as decoded by the TDA10045 is maintained in a well-defined buffer structure in the system memory, and therefore can easily be sorted (de-multiplexed) by the CPU for proper MPEG decoding.

The Broadcast Driver Architecture (BDA) for Windows operating systems supports this type of hybrid TV capture application, sharing one capture board for analog and digital TV reception.

## 6.3 Software support

## 6.3.1 Device driver

A complex and powerful software packet is provided for all PCI chips from the SAA713x family. This packet includes plug-and-play driver and capture driver installations for all commonly used 32-bit Windows platforms.

All platform related drivers support the following:

- Video preview and capture interfaces

- Audio control and audio capture interfaces.

Table 11: Microsoft Operation System (MOS) support

|              | танто типетовите времянием вустем (то в) выручением                                                                                                        |  |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MOS          | Driver support                                                                                                                                             |  |  |  |  |  |  |  |

| Windows 98   | Device access is contained with a kernel-mode Windows Driver Model (WDM) driver. The capture driver interface is based on Microsoft DirectShow technology. |  |  |  |  |  |  |  |

| Windows 2000 | The driver is binary-compatible with the Windows 98 driver and validated for passing the Microsoft WHQL test for getting the Win2000 driver signature.     |  |  |  |  |  |  |  |

| Windows XP   | The driver is binary-compatible with the Windows 98 driver and validated for passing the Microsoft WHQL test for getting the WinXP driver signature.       |  |  |  |  |  |  |  |

## 6.3.2 Supporting WDM

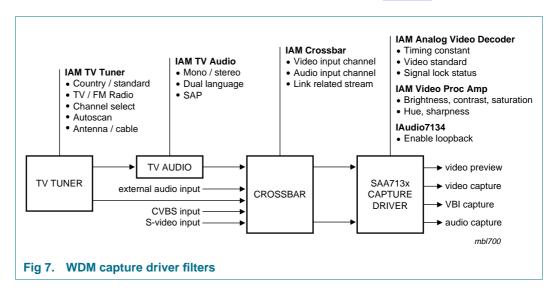

The Windows driver is implemented as an AV-streaming class-driver and provides a 'DirectShow' (DS) filter with output pins for video preview, video capture and VBI, together with a crossbar for input sources selection.

The TV tuner filter is a separate child driver and supports the control of all common Philips CAN and Silicon tuners. The typical filter structure is shown in Figure 7.

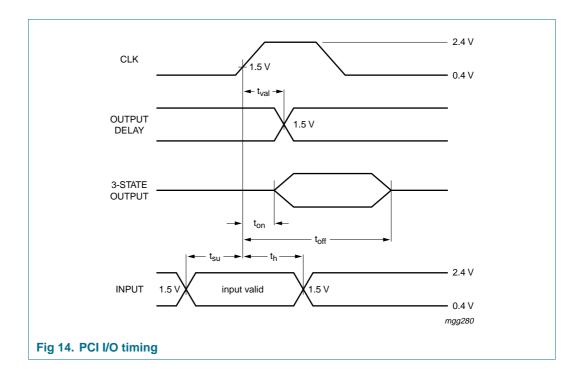

## 6.4 PCI interface

## 6.4.1 PCI configuration registers

The PCI interface of the SAA7134HL complies with the *PCI specification 2.2* and supports power management and Advanced Configuration and Power Interface (ACPI) as required by the *PC Design Guide 2001*.

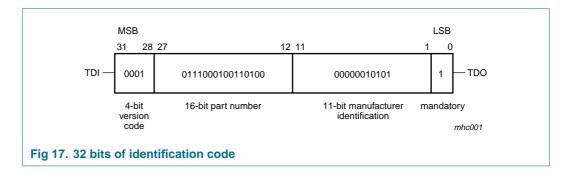

The PCI specification defines a structure of the PCI configuration space that is investigated during the boot-up of the system. The configuration registers (see <u>Table 12</u>) hold information essential for plug-and-play, to allow system enumeration and basic device setup without depending on the device driver, and support association of the proper software driver. Some of the configuration information is hard-wired in the device; some information is loaded during the system start-up.

| Function                      | Register address (hex) | Value [1]                                  | Remark        |

|-------------------------------|------------------------|--------------------------------------------|---------------|

| Device vendor ID              | 00 and 01              | 1131h                                      | for Philips   |

| Device ID                     | 02 and 03              | 7134h                                      | for SAA7134HL |

| Revision ID                   | 08                     | 00h                                        | or higher     |

| Class code                    | 09 to 0B               | 04 8000h                                   | multimedia    |

| Memory address space required | 10 to 13               | XXXX XXXX XXXX XXXX<br>XXXX XX00 0000 0000 | 1 kB          |

| System (board)<br>vendor ID   | 2C and 2D              | loaded from EEPROM                         |               |

| Sub-system (board version) ID | 2E and 2F              | loaded from EEPROM                         |               |

<sup>[1]</sup> X = don't care.

The device vendor ID is hard coded to 1131h, which is the code for Philips as registered with PCI-SIG.

The device ID is hard coded to 7134h.

During power-up, initiated by PCI reset, the SAA7134HL fetches additional system information via the I<sup>2</sup>C-bus from the on-board EEPROM, to load actual board type specific codes for the system vendor ID, sub-system ID (board version) and ACPI related parameters into the configuration registers.

## 6.4.2 ACPI and power states

The PCI specification 2.2 requires support of Advanced Configuration and Power Interface specification 1.0 (ACPI); more details are defined in the PCI Power Management Specification 1.0.

The power management capabilities and power states are reported in the extended configuration space. The main purpose of ACPI and PCI power management is to tailor the power consumption of the device to the actual needs.

The SAA7134HL supports all four ACPI device power states (see Table 13).

The pin PROP\_RST\_N of the peripheral interface is switched active LOW during the PCI reset procedure, and for the duration of the D3-hot state. Peripheral devices on board of the add-on card should use the level of this signal PROP\_RST\_N to switch themselves in any Power-save mode (e.g. disable device) and reset to default settings on the rising edge of signal PROP\_RST\_N.

| Power state | Description                                                                                                                                                                                                                                                                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0          | Normal operation: all functions accessible and programmable. The default setting after reset and before driver interaction (D0 un-initialized) switches most of the circuitry of the SAA7134HL into the Power-down mode, effectively such as D3-hot.                                                     |

| D1          | First step of reduced power consumption: no functional operation. Program registers are not accessible, but content is maintained. Most of the circuitry of the SAA7134HL is disabled with exception of the crystal and real-time clock oscillators, so that a quick recovery from D1 to D0 is possible. |

| D2          | Second step of reduced power consumption: no functional operation. Program registers are not accessible, but content is maintained. All functional circuitry of the SAA7134HL is disabled, including the crystal and clock oscillators.                                                                  |

| D3-hot      | Lowest power consumption: no functional operation. The content of the programming registers gets lost and is set to default values when returning to D0.                                                                                                                                                 |

## 6.4.3 DMA and configurable FIFO

The SAA7134HL supports seven DMA channels to master-write captured active video, audio, raw VBI and DTV/DVB Transport Streams (TS) into the PCI memory. Each DMA channel contains inherently the definition of two buffers, e.g. for odd and even fields in case of interlaced video, or two alternating buffers to capture continuous audio stream.

The DMA channels share in time and space one common FIFO pool of 256 Dwords (1024 bytes) total. It is freely configurable how much FIFO capacity can be associated with which DMA channel. Furthermore, a preferred minimum burst length can be programmed, i.e. the amount of data to be collected before the request for the PCI-bus is issued. This means that latency behavior per DMA channel can be tailored and optimized for a given application.

In the event that a FIFO of a certain channel overflows due to latency conflict on the bus, graceful overflow recovery is applied. The amount of data that gets lost because it could not be transmitted, is monitored (counted) and the PCI-bus address pointer is incremented accordingly. Thus new data will be written to the correct memory place, after the latency conflict is resolved.

## 6.4.4 Virtual and physical addressing

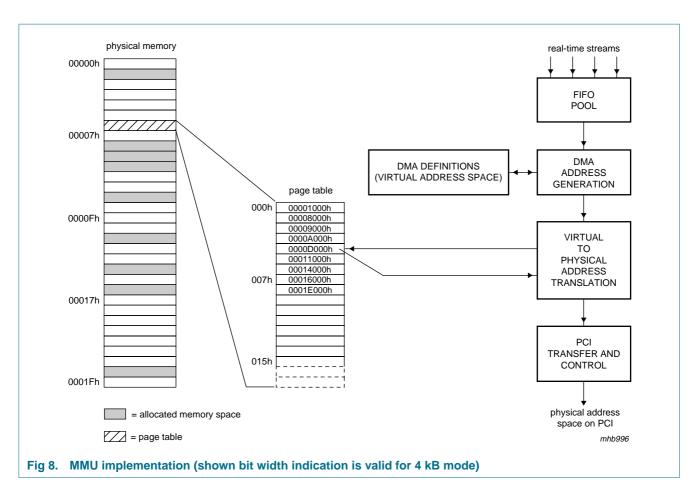

Most operating systems allocate memory to requesting applications for DMA as continuous ranges in virtual address space. The data flow over the PCI-bus points to physical addresses, usually not continuous and split in pages of 4 kB (Intel architecture, most UNIX systems, Power PC).

The association between the virtual (logic) address space and the fragmented physical address space is defined in page tables (system files); see Figure 8.

The SAA7134HL incorporates hardware support (MMU) to translate virtual to physical addresses on the fly, by investigating the related page table information. This hardware support reduces the demand for real-time software interaction and interrupt requests, and therefore saves system resources.

Product data sheet

## 6.4.5 Status and interrupts on PCI-bus

The SAA7134HL provides a set of status information about internal signal processing, video and audio standard detection, peripheral inputs and outputs (pins GPIO) and behavior on the PCI-bus. This status information can be conditionally enabled to raise an interrupt on the PCI-bus, e.g. completion of a certain DMA channel or buffer, or change in a detected TV standard, or the state of peripheral devices.

The cause of an issued interrupt is reported in a dedicated register, even if the original condition has changed before the system was able to investigate the interrupt.

## 6.5 Analog TV standards

Analog TV signals are described in three categories of standards:

- Basic TV systems: defining frame rate, number of lines per field, levels of synchronization signals, blanking, black and white, signal bandwidth and the RF modulation scheme

- Color transmission: defining color coding and modulation method

- Sound and stereo: defining coding for transmission

TV signals that are broadcast usually conform fairly accurately to the standards. Transmission over the air or through a cable can distort the signal with noise, echoes, crosstalk or other disturbances.

Video signals from local consumer equipment, e.g. VCR, camcorder, camera, game console, or even DVD player, often do not follow the standard specification very accurately.

Playback from video tape cannot be expected to maintain correct timing, especially not during feature mode (fast forward, etc.).

Table 14 to Table 16 list some characteristics of the various TV standards.

The SAA7134HL decodes all color TV standards and non-standard signals as generated by video tape recorders e.g. automatic video standard detection can be applied, with preference options for certain standards, or the decoder can be forced to a dedicated standard.

The SAA7134HL incorporates TV stereo decoding for NICAM and dual FM sound systems. BTSC and EIAJ are demodulated to monaural sound, but stereo decoding can be added externally. Baseband stereo audio can be fed into the device as analog signal, or in digital form in I<sup>2</sup>S-bus format.

Table 14: Overview of basic TV standards

| Main parameters        | Standard |          |         |         |         |         |         |     |  |

|------------------------|----------|----------|---------|---------|---------|---------|---------|-----|--|

|                        | M        | N        | В       | G, H    | I       | D/K     | L       |     |  |

| RF channel width       | 6        | 6        | 7       | 7       | 8       | 7       | 8       | MHz |  |

| Video bandwidth        | 4.2      | 4.2      | 5       | 5       | 5.5     | 6       | 6       | MHz |  |

| 1st sound carrier      | 4.5, FM  | 4.5, FM  | 5.5, FM | 5.5, FM | 6.0, FM | 6.5, FM | 6.5, AM | MHz |  |

| Field rate             | 59.94006 | 50       | 50      | 50      | 50      | 50      | 50      | Hz  |  |

| Lines per frame        | 525      | 625      | 625     | 625     | 625     | 625     | 625     | -   |  |

| Line frequency         | 15.734   | 15.625   | 15.625  | 15.625  | 15.625  | 15.625  | 15.625  | kHz |  |

| ITU clocks per<br>line | 1716     | 1728     | 1728    | 1728    | 1728    | 1728    | 1728    | -   |  |

| Sync, setup level      | -40, 7.5 | -40, 7.5 | -43, 0  | -43, 0  | -43, 0  | -43, 0  | -43, 0  | IRE |  |

| Gamma correction       | 2.2      | 2.2      | 2.8     | 2.8     | 2.8     | 2.8     | 2.8     | -   |  |

Table 14:

Overview of basic TV standards...continued

| Main parameters                    | Standard                 |           |                                 |                                  |                           |                             |                              |   |

|------------------------------------|--------------------------|-----------|---------------------------------|----------------------------------|---------------------------|-----------------------------|------------------------------|---|

|                                    | M                        | N         | В                               | G, H                             | I                         | D/K                         | L                            |   |

| Associated color TV standards      | NTSC, PAL                | PAL       | PAL                             | PAL                              | PAL                       | SECAM,<br>PAL               | SECAM                        | - |

| Associated stereo TV sound systems | BTSC,<br>EIAJ, A2        | BTSC      | dual FM,<br>A2                  | NICAM                            | NICAM                     | NICAM, A2                   | NICAM                        | - |

| Country examples                   | USA,<br>Japan,<br>Brazil | Argentina | part of<br>Europe,<br>Australia | Spain,<br>Malaysia,<br>Singapore | UK,<br>Northern<br>Europe | China,<br>Eastern<br>Europe | France,<br>Eastern<br>Europe | - |

Table 15: TV system color standards

| Main parameters              | NTSC M                         | PAL M  | PAL N                          | PAL<br>BGHID                           | SECAM LD                                       | GHK   | PAL 4.4<br>(60 Hz)                        | Unit |

|------------------------------|--------------------------------|--------|--------------------------------|----------------------------------------|------------------------------------------------|-------|-------------------------------------------|------|

| Field rate                   | 59.94                          | 59.94  | 50                             | 50                                     | 50                                             |       | ≈60                                       | Hz   |

| Lines per frame              | 525                            | 525    | 625                            | 625                                    | 625                                            |       | 525                                       |      |

| Chrominance subcarrier       | 3.580                          | 3.576  | 3.582                          | 4.434                                  | 4.406                                          | 4.250 | 4.434                                     | MHz  |

| f <sub>sc</sub> to H ratio   | 227.5                          | 227.25 | 229.25                         | 283.75                                 | 282                                            | 272   | n.a.                                      |      |

| f <sub>sc</sub> offset (PAL) | -                              | -      | 50                             | 50                                     | -                                              | -     | n.a.                                      | Hz   |

| Alternating phase            | no                             | yes    | yes                            | yes                                    | -                                              | -     | yes                                       |      |

| Country examples             | USA,<br>Japan,<br>Asia-Pacific | Brazil | Middle and<br>South<br>America | Europe,<br>Common-<br>wealth,<br>China | France, Eastern Europe,<br>Africa, Middle East |       | VCR<br>transcoding<br>NTSC-tape<br>to PAL |      |

Table 16: TV stereo sound standards

| Main parameters  | Analog systems |                         |                          |             |                | Digital co | Digital coding |     |

|------------------|----------------|-------------------------|--------------------------|-------------|----------------|------------|----------------|-----|

|                  | Mono           | BTSC                    | EIAJ                     | A2 (dual F  | FM)            | NICAM      |                |     |

| Stereo coding    | -              | internal carrier (      | (mpx)                    | 2-Carrier S | Systems (2CS   | S)         |                | '   |

| scheme           |                | AM                      | FM                       | 2nd FM ca   | ırrier         | DQPSK or   | n FM           |     |

| 2nd language     | -              | mono SAP on internal FM | as alternative to stereo | as alternat | tive to stereo | mono on 1  | st carrier     |     |

| Sound IF         |                |                         |                          | 1st         | 2nd            | 1st        | 2nd            |     |

| M, N             | 4.5 FM         | 4.5                     | 4.5                      | 4.5         | 4.724          | not used   | not used       | MHz |

| B, G, H          | 5.5 FM         | not used                | not used                 | 5.5         | 5.742          | 5.5        | 5.850          | MHz |

| I                | 6.0 FM         | not used                | not used                 | not used    | not used       | 6.0        | 6.552          | MHz |

| DK (1)           | 6.5 FM         | not used                | not used                 | 6.5         | 6.742          | 6.5        | 5.850          | MHz |

| DK (2)           | 6.5 FM         | -                       | -                        | -           | 6.258          | -          | -              | MHz |

| DK (3)           | 6.5 FM         | -                       | -                        | -           | 5.742          | -          | -              | MHz |

| L                | 6.5 AM         | not used                | not used                 | not used    | not used       | 6.5        | 5.850          | MHz |

| De-emphasis      | 75             | 75, dbx-TV              | 50                       | 50 or 75    | 50 or 75       | 50 or 75   | 50 or 75       | μs  |

| Audio bandwidth  | 15             | 15                      | 15                       | 15          | 15             | 15         | 15             | kHz |

| Country examples | world-<br>wide | USA, South<br>America   | Japan                    | part of Eu  | rope, Korea    | part of Eu | rope, China    |     |

## 6.6 Video processing

## 6.6.1 Analog video inputs

The SAA7134HL provides five analog video input pins:

- Composite video signals (CVBS), from tuner or external source

- · S-video signals (pairs of Y-C), e.g. from camcorder

- DTV/DVB 'low-IF' signal, from an appropriate DTV or combi-tuner

Analog anti-alias filters are integrated on chip and therefore, no external filters are required. The device also contains automatic clamp and gain control for the video input signals, to ensure optimum utilization of the ADC conversion range. The nominal video signal amplitude is 1 V (p-p) and the gain control can adapt deviating signal levels in the range of +3 dB to -6 dB. The video inputs are digitized by two ADCs of 9-bit resolution, with a sampling rate of nominal 27 MHz (the line-locked clock) for analog video signals.

## 6.6.2 Video synchronization and line-locked clock

The SAA7134HL recovers horizontal and vertical synchronization signals from the selected video input signal, even under extremely adverse conditions and signal distortions. Such distortions are 'noise', static or dynamic echoes from broadcast over air, crosstalk from neighboring channels or power lines (hum), cable reflections, time base errors from video tape play-back and non-standard signal levels from consumer type video equipment (e.g. cameras, DVD).

The heart of this TV synchronization system is the generation of the Line-Locked Clock (LLC) of nominal 27 MHz, as defined by *ITU-R BT.601*. The LLC ensures orthogonal sampling, and always provides a regular pattern of synchronization signals, that is a fixed and well defined number of clock pulses per line. This is important for further video processing devices connected to the peripheral video port (pins GPIO). It is very effective to run under the LLC of 27 MHz, especially for on-board hardware MPEG encoding devices, since MPEG is defined on this clock and sampling frequency.

## 6.6.3 Video decoding and automatic standard detection

The SAA7134HL incorporates color decoding for any analog TV signal. All color TV standards and flavors of NTSC, PAL, SECAM and non-standard signals (VCR) are automatically recognized and decoded into luminance and chrominance components, i.e.  $Y-C_B-C_R$ , also known as YUV.

The video decoder of the SAA7134HL incorporates an automatic standard detection, that does not only distinguish between 50 Hz and 60 Hz systems, but also determines the color standard of the video input signal. Various preferences ('look first') for automatic standard detection can be chosen, or a selected standard can be forced directly.

## 6.6.4 Adaptive comb filter

The SAA7134HL applies adaptive comb filter techniques to improve the separation of luminance and chrominance components in comparison to the separation by a chroma notch filter, as used in traditional TV color decoder technology. The comb filter compares the signals of neighboring lines, taking into account the phase shift of the chroma subcarrier from line to line. For NTSC the signal from three adjacent lines are investigated, and in the event of PAL the comb filter taps are spread over four lines.

Comb filtering achieves higher luminance bandwidth, resulting in sharper picture and detailed resolution. Comb filtering further minimizes color crosstalk artifacts, which would otherwise produce erroneous colors on detailed luminance structures.

The comb filter as implemented in the SAA7134HL is adaptive in two ways:

- Adaptive to transitions in the picture content

- Adaptive to non-standard signals (e.g. VCR)

The integrated digital delay lines are always exactly correct, due to the applied unique line-locked sampling scheme (LLC). Therefore the comb filter does not need to be switched off for non-standard signals and remains operating continuously.

#### 6.6.5 Macrovision detection

The SAA7134HL detects if the decoded video signal is copy protected by the Macrovision system. The detection logic distinguishes the three levels of the copy protection as defined in rev. 7.01, and are reported as status information. The decoded video stream is not effected directly, but application software and Operation System (OS) has to ensure that this video stream maintains tagged as 'copy protected', and such video signal would leave the system only with the reinforced copy protection. The multi-level Macrovision detection on the video capture side supports proper TV re-encoding on the output point, e.g. by Philips TV encoders SAA712x or SAA7102.

#### 6.6.6 Video scaling

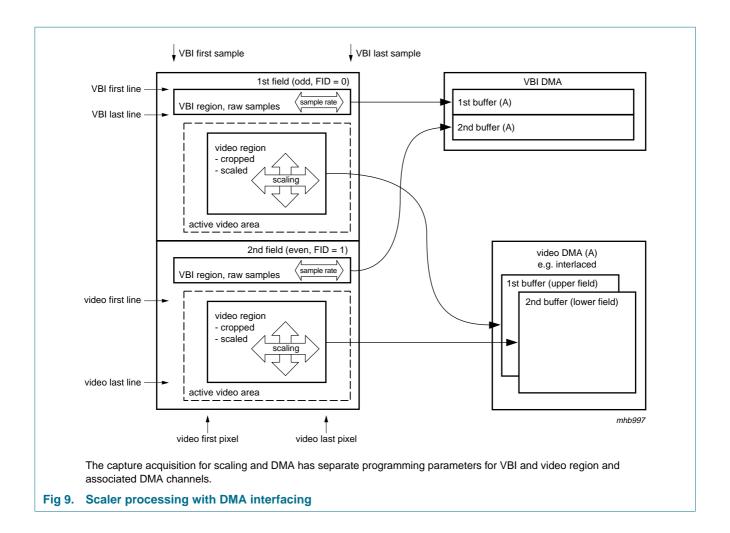

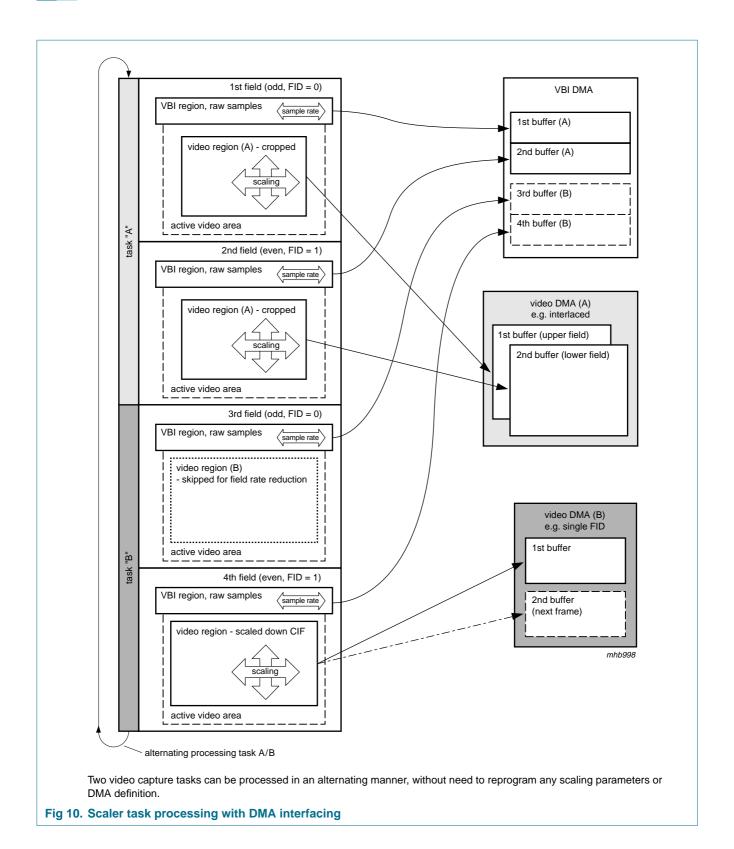

The SAA7134HL incorporates a filter and processing unit to downscale or upscale the video picture in the horizontal and vertical dimension, and in frame rate (see Figure 9 and Figure 10). The phase accuracy of the re-sampling process is  $^{1}/_{64}$  of the original sample distance. This is equivalent to a clock jitter of less than 1 ns. The filter depth of the anti-alias filter adapts to the scaling ratio, from 10 taps horizontally for scaling ratios close to 1 : 1, to up to 74 taps for an icon sized video picture.

Most video capture applications will typically require for downscaling. But some zooming is required for conversion of ITU sampling to SQuare Pixel (SQP), or to convert the 240 lines of an NTSC field to 288 lines to comply with ITU-T video phone formats.

The scaling acquisition definition also includes cropping, frame rate reduction, and defines the amount of pixels and lines to be transported through DMA over the PCI-bus.

Two programming pages are available to enable re-programming of the scaler in the 'shadow' of the running processing, without holding or disturbing the flow of the video stream. Alternatively, the two programming pages can be applied to support two video destinations or applications with different scaler settings, e.g. firstly to capture video to CPU for compression (storage, video phone), and secondly to preview the picture on the monitor screen. A separate scaling region is dedicated to capture raw VBI samples, with a specific sampling rate, and be written into its own DMA channel.

#### 6.6.7 VBI data

The Vertical Blanking Interval (VBI) is often utilized to transport data over analog video broadcast. Such data can closely relate to the actual video stream, or just be general data (e.g. news). Some examples for VBI data types are:

- Closed Caption (CC) for the hearing impaired (CC, on line 21 of first field)

- Intercast data in US coded in North-American Broadcast Text System (NABTS) format, in Europe in World Standard Teletext (WST), to transmit internet related services, optionally associated with actual video program content

- Teletext, transporting news services and broadcast related information, Electronic Program Guide (EPG), widely used in Europe (coded in WST format)

- EPG, broadcaster specific program and schedule information, sometimes with proprietary coding scheme (pay service), usually carried on NABTS, WST, Video Programming Service (VPS), or proprietary data coding format

- Video Time Codes (VTC) as inserted in camcorders e.g. use for video editing

- Copy Guard Management System (CGMS) codes, to indicate copy protected video material, sometimes combined with format information, Wide Screen Signalling (WSS)

This information is coded in the unused lines of the vertical blanking interval, between the vertical sync pulse and the active visible video picture. So-called full-field data transmission is also possible, utilizing all video lines for data coding.

The SAA7134HL supports capture of VBI data by the definition of a VBI region to be captured as raw VBI samples, that will be sliced and decoded by software on the host CPU. The raw sample stream is taken directly from the ADC and is not processed or filtered by the video decoder. The sampling rate of raw VBI can be adjusted to the needs of the data slicing software.

## 6.6.8 Signal levels and color space

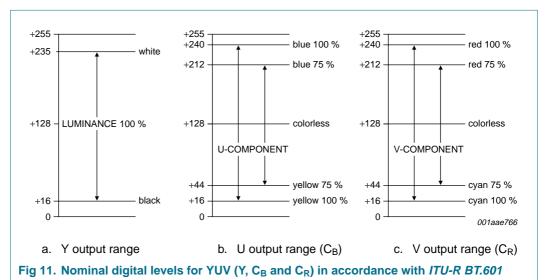

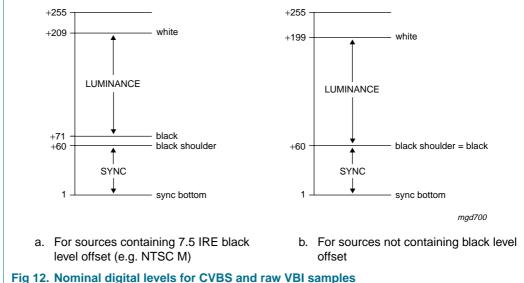

Analog TV video signals are decoded into its components luminance and color difference signals (YUV) or in its digital form Y-C<sub>B</sub>-C<sub>R</sub>. *ITU-R BT.601* defines 720 pixels along the line (corresponding to a sampling rate of 27 MHz divided by two), and a certain relationship from level to number range; see Figure 11.

The video components do not use the entire number range, but leave some margin for overshoots and intermediate values during processing. For the raw VBI samples there is no official specification how to code, but it is common practice to reserve the lower quarter of the number range for the sync, and to leave some room for overmodulation beyond the nominal white amplitude; see <u>Table 12</u>.

The automatic clamp and gain control at the video input, together with the automatic chroma gain control of the SAA7134HL, ensures that the video components stream at the output comply to the standard levels. Beyond that additional brightness, contrast, saturation and hue control can be applied to satisfy special needs of a given application. The raw VBI samples can be adjusted independent of the active video.

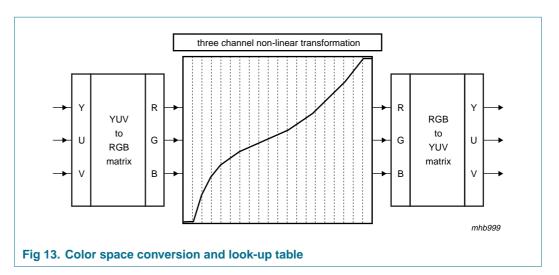

The SAA7134HL incorporates the YUV-to-RGB matrix (optional), the RGB-to-YUV matrix and a three channel look-up table in between; see <a href="Figure 13">Figure 13</a>. Under nominal settings, the RGB space will use the same number range as defined by the ITU and shown in <a href="Figure 11">Figure 11</a> for luminance, between 16 and 235. As graphic related applications are based

on full-scale RGB, i.e. 0 to 255, the range can be stretched by applying appropriate brightness, contrast and saturation values. The look-up table supports gamma correction (freely definable), and allows other non-linear signal transformation such as black stretching.

The analog TV signal applies a quite strong gamma pre-compensation (2.2 for NTSC and 2.8 for PAL). As computer monitors exhibit a gamma (around 2.5), the difference between gamma pre-compensation and actual screen gamma has to be corrected, to achieve best contrast and color impression.

The SAA7134HL offers a multitude of formats to write video streams over the PCI-bus: YUV and RGB color space, 15-bit, 16-bit, 24-bit and 32-bit representation, packed and planar formats. For legacy requirements a clipping procedure is implemented, that allows the definition of eight overlay rectangles. This process can alternatively be used to associate 'alpha' values to the video pixels.

.055

rig 12. Nominal digital levels for GVD3 and raw VDI Samples

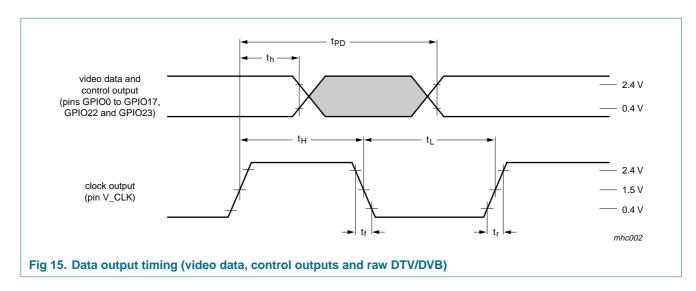

## 6.6.9 Video port, ITU and VIP codes

The decoded and/or scaled video stream can be captured via PCI-DMA to the system memory, and/or can be made available locally through the video side port (VP), using some of the GPIO pins. Two types of applications are intended:

- Streaming real-time video to a video side port at the VGA card, e.g. via ribbon cable over the top

- Feeding video stream to a local MPEG compression device on the same PCI board, e.g. for time shift viewing applications

The video port of the SAA7134HL supports the following 8 and 16-bit wide YUV video signalling standards (see <u>Table 9</u>):

- VMI: 8-bit wide data stream, clocked by LLC = 27 MHz, with discrete sync signals HSYNC, VSYNC and VACTIVE

- ITU-R BT.656, parallel: 8-bit wide data stream, clocked by LLC = 27 MHz, synchronization coded in SAV and EAV codes

- VIP 1.1 and 2.0: 8-bit or 16-bit wide data stream, clocked by LLC = 27 MHz, synchronization coded in SAV and EAV codes (with VIP extensions)

- Zoom Video (ZV): 16-bit wide pixel stream, clocked by LLC/2 = 13.5 MHz, with discrete sync signals HSYNC and VSYNC

- ITU-R BT.601 direct (DMSD): 16-bit wide pixel stream, clocked by LLC = 27 MHz, with discrete sync signals HSYNC, VSYNC/FID and CREF

- Raw DTV/DVB sample stream: 9-bit wide data, clocked with a copy of signal X\_CLK\_IN

The VIP standard can transport scaled video and discontinuous data stream by allowing the insertion of '00' as marker for empty clock cycles. For the other video port standards, a data valid flag or gated clock can be applied.

#### 6.7 TV sound

## 6.7.1 TV sound stereo decoding

TV sound is modulated on an internal sound subcarrier, on the upper end of the TV RF channel, at 4.5 MHz, 5.5 MHz, 6.0 MHz, or 6.5 MHz, depending on the TV system. The modulation is usually on FM and for system L on AM (see <u>Table 16</u>). There are basically three variants how stereo sound is encoded on analog TV transmission:

- An internal multiplexed carrier for the difference signal L R (BTSC uses AM and EIAJ uses FM); this is similar to FM radio stereo

- A second independent FM carrier in the RF channel (dual FM), that can carry the difference signal L – R, or a second language

- A (second) independent FM/QPSK carrier in the RF channel (NICAM), carrying a digital audio signal, stereo, or dual language mono

Some parameters of the used coding scheme are modulated on an inaudible pilot carrier.

The SAA7134HL incorporates TV sound decoding from the Sound Intermediate Frequency (SIF) signal. The analog SIF signal is taken from the tuner, digitized and digitally FM or AM demodulated. The pilot tone is investigated and the signal is properly stereo decoded. The SAA7134HL supports TV stereo decoding for all NICAM and dual FM sound systems on-chip. The digital FM demodulation maintains stable phase accuracy, resulting into improved channel separation, compared to traditional analog demodulation. BTSC and EIAJ are demodulated to monaural sound, but stereo decoding can be added externally.

The SAA7134HL incorporates baseband stereo audio ADCs, to capture sound signals associated with external video sources, e.g. camera, camcorder or VCR.

For concurrent capture of audio and video signals, it is important to maintain synchronization between the two streams. The spoken word and other sound should match the displayed picture within a video frame ( $\frac{1}{30}$  s 'lip-sync'). The SAA7134HL has special means to lock the audio sampling clock to the video frame frequency (FLC), so that a certain fix predefined number of audio samples are associated with each video field. This is especially important for video editing, compression and recording, e.g. time shift viewing. There is no drift between the audio and video streams, not even for longer recording times.

TV sound offers an audio bandwidth of less than 15 kHz, that is usually sampled and digitized with 32 kHz. NICAM as digital sound coding has inherently a 32 kHz sample rate, locked already on the source side to the video rate. The digital audio stream can be captured through dedicated DMA into the PCI memory space, or to the output in I<sup>2</sup>S-format to further peripheral digital sound processing, e.g. virtual surround sound, or converted to analog stereo via integrated audio DACs, to feed analog audio over the loop back cable to the sound card function.

## 6.7.2 Analog audio pass-through and loop back cable

Most operating systems are prepared to deal with audio input at only one single entry point, namely at the sound card function. Therefore the sound associated with video has to get routed through the sound card.

The SAA7134HL supports analog audio pass-through and the loop back cable on-chip. No external components are required. The audio signal, that was otherwise connected to the sound card line-in, e.g. analog sound from a CD-ROM drive, has to be connected to one of the inputs of the SAA7134HL. By default, after a system reset and without involvement of any driver, this audio signal is passed through to the analog audio output pins, that will feed the loop back cable to the sound card line-in connector. The AV capture driver has to open the default pass-through and switch in the TV sound signal by will.

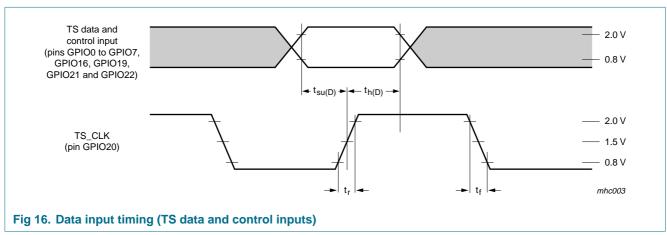

## 6.8 DTV/DVB channel decoding and TS capture

The SAA7134HL is optimally equipped to support the application extension to capture digital TV signals, e.g. for VSB (ATSC) or DVB (T/C/S). A hybrid TV tuner for analog and digital TV broadcast reception usually provides a DTV signal on low IF, i.e. downconverted into a frequency range from 0 MHz to 10 MHz. Such signals can be fed to one of the 5 video inputs of the SAA7134HL for digitizing. The digital raw DTV is output at the video port, and is sent to the peripheral channel decoder, e.g. TDA8961 for VSB-8 decoding. The channel decoder provides the sampling clock via the external clock input pin X\_CLK\_IN (up to 36 MHz input clock frequency), and adjusts the signal gain in the tuner or in the video input path in front of the ADC. Alternatively, the low IF DTV/DVB signal could be fed directly to the channel decoder, depending on the capability for digitizing the selected device.

The peripheral channel decoder circuitry decodes the digital transmission into bits and bytes, apply error correction etc. and outputs a packed Transport Stream (TS) accompanied by a clock and handshake signals. The SAA7134HL captures the TS in parallel or serial protocol, synchronized by Start Of Packet (SOP), and pumps it via the dedicated DMA into the PCI memory space. The DMA definition supports automatic toggling between two buffers.

## 6.9 Control of peripheral devices

#### 6.9.1 I<sup>2</sup>C-bus master

The SAA7134HL incorporates an I<sup>2</sup>C-bus master to setup and control peripheral devices such as tuner, DTV/DVB channel decoder, audio DSP co-processors, etc. The I<sup>2</sup>C-bus interface itself is controlled from the PCI-bus on a command level, reading and writing byte by byte. The actual I<sup>2</sup>C-bus status is reported (status register) and, as an option, can raise error interrupts on the PCI-bus.

At PCI reset time, the I<sup>2</sup>C-bus master receives board specific information from the on-board EEPROM to update the PCI configuration registers.

The  $I^2C$ -bus interface is multi-master capable and can assume slave operation too. This allows application of the device in the stand-alone mode, i.e. with the PCI-bus not connected. Under the slave mode, all internal programming registers can be reached via the  $I^2C$ -bus with exception of the PCI configuration space.

## 6.9.2 Propagate reset

The PCI system reset and ACPI power management state D3 is propagated to peripheral devices by the dedicated pin PROP\_RST\_N. This signal is switched to active LOW by reset and D3, and is only switched HIGH under control of the device driver 'by will'. The intention is that peripheral devices will use signal PROP\_RST\_N as Chip-Enable (CE). The peripheral devices should enter a low power consumption state if pin PROP\_RST\_N = LOW, and reset into default setting at the rising edge.

#### 6.9.3 **GPIO**