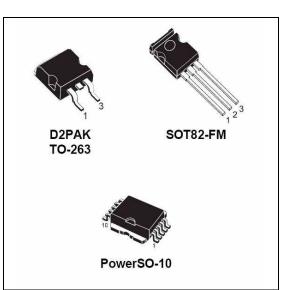

# VNB14N04 - VNK14N04FM VNV14N04

"OMNIFET" fully autoprotected Power MOSFET

### Features

| Туре       | V <sub>clamp</sub> | R <sub>DS(on)</sub> | l <sub>lim</sub> |

|------------|--------------------|---------------------|------------------|

| VNB14N04   | 42 V               | 0.07 Ω              | 14 A             |

| VNK14N04FM | 42 V               | 0.07 Ω              | 14 A             |

| VNV14N04   | 42 V               | 0.07 Ω              | 14 A             |

- Linear current limitation

- Thermal shutdown

- Short circuit protection

- Integrated clamp

- Low current drawn from input pin

- Diagnostic feedback through input pin

- ESD protection

- Direct access to the gate of the power MOSFET (analog driving)

- Compatible with standard power MOSFET

## Description

The VNB14N04, VNK14N04FM and VNV14N04 are monolithic devices made using STMicroeletronics VIPower M0 Technology, intended for replacement of standard power MOSFETS in DC to 50 kHz applications. Built-in thermal shutdown, linear current limitation and overvoltage clamp protect the chip in harsh environment.

Fault feedback can be detected by monitoring the voltage at the input pin.

Table 1. Device summary

| Part number | Order code                                          |

|-------------|-----------------------------------------------------|

| VNB14N04    | VNB14N04, VNB14N04-E,<br>VNB14N0413TR, VNB14N04TR-E |

| VNK14N04FM  | VNK14N04FM                                          |

| VNV14N04    | VNV14N04, VNV14N04-E                                |

## Contents

| 1 | Block diagram                    |

|---|----------------------------------|

| 2 | Electrical specification4        |

|   | 2.1 Absolute maximum rating 4    |

|   | 2.2 Thermal data                 |

|   | 2.3 Electrical characteristics 4 |

| 3 | Protection features7             |

| 4 | Package information              |

| 5 | Revision history                 |

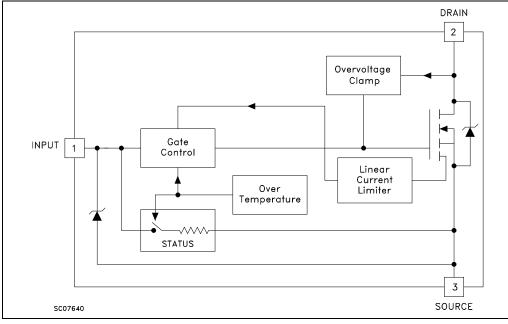

# 1 Block diagram

1. PowerSO-10 pin configuration : INPUT = 6,7,8,9,10; SOURCE = 1,2,4,5; DRAIN = TAB

# 2 Electrical specification

## 2.1 Absolute maximum rating

|        |                                                         | Valu                | ie       |      |

|--------|---------------------------------------------------------|---------------------|----------|------|

| Symbol | Parameter                                               | PowerSO-10<br>D2PAK | SOT-82FM | Unit |

| Vds    | Drain-source voltage (V <sub>in</sub> = 0)              | Internally of       | clamped  | V    |

| Vin    | Input voltage 18                                        |                     | V        |      |

| ld     | Drain current                                           | Internally limited  |          | А    |

| lr     | Reverse DC output current                               | -14                 |          | А    |

| Vesd   | Electrostatic discharge (C = 100 pF, R=1.5 K $\Omega$ ) | 2000                |          | V    |

| Ptot   | Total dissipation at $T_c = 25 $ °C                     | 50 9.5              |          | W    |

| Tj     | Operating junction temperature Internally limited       |                     | limited  | C    |

| Tc     | Case operating temperature Internally limited           |                     | C        |      |

| Tstg   | Storage temperature                                     | -55 to              | 150      | C    |

#### Table 2.Absolute maximum rating

## 2.2 Thermal data

#### Table 3. Thermal data

| Symbol    | Parameter                               | PowerSO-10 | SOT82-FM | D2PAK | Unit |

|-----------|-----------------------------------------|------------|----------|-------|------|

| Rthj-case | Thermal resistance junction-case max    | 2.5        | 13       | 2.5   | °C/W |

| Rthj-amb  | Thermal resistance junction-ambient max | 50         | 100      | 62.5  | C/W  |

## 2.3 Electrical characteristics

$T_{case}$  =25 °C unless otherwise specified.

| Table 4. | Electrical | characteristics |

|----------|------------|-----------------|

|          |            |                 |

| Symbol             | Parameter                            | Test conditions                             | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------------|---------------------------------------------|------|------|------|------|

| Off                |                                      |                                             |      |      |      |      |

| V <sub>CLAMP</sub> | Drain-source clamp voltage           | I <sub>D</sub> = 200 mA V <sub>in</sub> = 0 | 36   | 42   | 48   | V    |

| V <sub>CLTH</sub>  | Drain-source clamp threshold voltage | $I_D = 2 \text{ mA } V_{in} = 0$            | 35   |      |      | V    |

| V <sub>INCL</sub>  | Input-source reverse clamp voltage   | I <sub>in</sub> = -1 mA                     | -1   |      | -0.3 | V    |

57

| Symbol                                                                                              | Parameter                                                                    | Test conditions                                                                                                                        | Min.     | Тур.                     | Max.                     | Unit                 |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|--------------------------|----------------------|

| I <sub>DSS</sub>                                                                                    | Zero input voltage drain current (V <sub>in</sub> = 0)                       | $V_{DS} = 13 V V_{in} = 0$<br>$V_{DS} = 25 V V_{in} = 0$                                                                               |          |                          | 50<br>200                | μΑ<br>μΑ             |

| I <sub>ISS</sub>                                                                                    | Supply current from input pin                                                | V <sub>DS</sub> = 0 V V <sub>in</sub> = 10 V                                                                                           |          | 250                      | 500                      | μΑ                   |

| On <sup>(1)</sup>                                                                                   |                                                                              |                                                                                                                                        |          | •                        |                          |                      |

| V <sub>IN(th)</sub>                                                                                 | Input threshold voltage                                                      | $V_{DS} = V_{in} I_D + I_{in} = 1 \text{ mA}$                                                                                          | 0.8      |                          | 3                        | V                    |

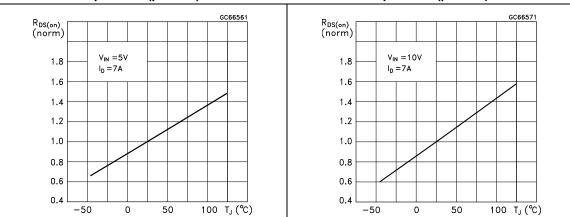

| Report                                                                                              |                                                                              | V <sub>in</sub> = 10 V I <sub>D</sub> = 7 A<br>V <sub>in</sub> = 5 V I <sub>D</sub> = 7 A                                              |          |                          | 0.7<br>0.1               | Ω<br>Ω               |

| Dynamic                                                                                             |                                                                              |                                                                                                                                        |          |                          |                          |                      |

| g <sub>fs</sub> <sup>(1)</sup>                                                                      | Forward transconductance                                                     | V <sub>DS</sub> = 13 V I <sub>D</sub> = 7 A                                                                                            | 8        | 10                       |                          | S                    |

| C <sub>oss</sub>                                                                                    | Output capacitance                                                           | V <sub>DS</sub> = 13 V f = 1 MHz V <sub>in</sub> = 0                                                                                   |          | 400                      | 500                      | pF                   |

| Switchir                                                                                            | ng <sup>(2)</sup>                                                            |                                                                                                                                        |          |                          |                          |                      |

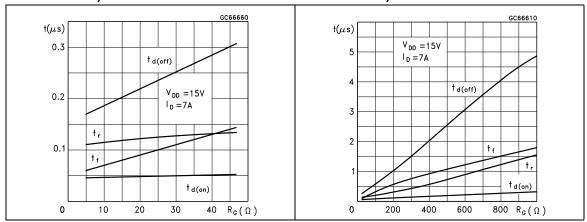

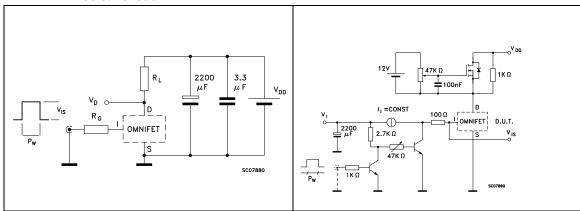

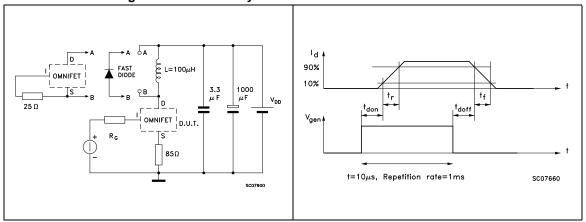

| t <sub>d(on)</sub><br>t <sub>r</sub><br>t <sub>d(off)</sub><br>t <sub>f</sub>                       | Turn-on delay time<br>Rise time<br>Turn-off delay time<br>Fall time          | $V_{DD} = 15 \text{ V I}_{d} = 7 \text{ A}$ $V_{gen} = 10 \text{ V R}_{gen} = 10 \Omega$ (see <i>Figure 26</i> )                       |          | 60<br>160<br>250<br>100  | 120<br>300<br>400<br>200 | ns<br>ns<br>ns<br>ns |

| t <sub>d(on)</sub><br>t <sub>r</sub><br>t <sub>d(off)</sub><br>t <sub>f</sub>                       | Turn-on delay time<br>Rise time<br>Turn-off delay time<br>Fall time          | $V_{DD} = 15 V I_d = 7 A$ $V_{gen} = 10 V R_{gen} = 1000 \Omega$ (see <i>Figure 26</i> )                                               |          | 300<br>1.5<br>5.5<br>1.8 | 500<br>2.2<br>7.5<br>2.5 | ns<br>µs<br>µs<br>µs |

| (di/dt) <sub>on</sub>                                                                               | Turn-on current slope                                                        | $V_{DD} = 15 \text{ V } I_D = 7 \text{ A}$ $V_{in} = 10 \text{ V } R_{gen} = 10 \Omega$                                                |          | 120                      |                          | A/µs                 |

| Qi                                                                                                  | Total input charge                                                           | V <sub>DD</sub> = 12 V I <sub>D</sub> = 7 A V <sub>in</sub> = 10 V                                                                     |          | 30                       |                          | nC                   |

| Source                                                                                              | drain diode                                                                  |                                                                                                                                        |          |                          |                          |                      |

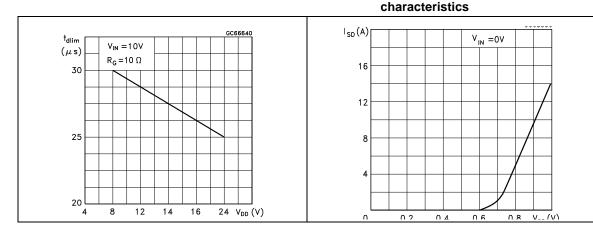

| $V_{SD}$ $^{(1)}$                                                                                   | Forward on voltage                                                           | I <sub>SD</sub> = 7 A V <sub>in</sub> = 0                                                                                              |          |                          | 1.6                      | V                    |

| t <sub>rr</sub> <sup>(2)</sup><br>Q <sub>rr</sub> <sup>(2)</sup><br>I <sub>RRM</sub> <sup>(2)</sup> | Reverse recovery time<br>Reverse recovery charge<br>Reverse recovery current | $I_{SD} = 7 \text{ A di/dt} = 100 \text{ A/µs}$<br>$V_{DD} = 30 \text{ V T}_j = 25 ^{\circ}C$<br>(see test circuit, <i>Figure 28</i> ) |          | 110<br>0.34<br>6.1       |                          | ns<br>μC<br>Α        |

| Protecti                                                                                            | on                                                                           |                                                                                                                                        |          |                          |                          |                      |

| l <sub>lim</sub>                                                                                    | Drain current limit                                                          | V <sub>in</sub> = 10 V V <sub>DS</sub> = 13 V<br>V <sub>in</sub> = 5 V V <sub>DS</sub> = 13 V                                          | 10<br>10 | 14<br>14                 | 20<br>20                 | A<br>A               |

| t <sub>dlim</sub> (2)                                                                               | Step response<br>Current limit                                               | $V_{in} = 10 V$<br>$V_{in} = 5 V$                                                                                                      |          | 30<br>80                 | 60<br>150                | μs<br>µs             |

| T <sub>jsh</sub> <sup>(2)</sup>                                                                     | Overtemperature shutdown                                                     |                                                                                                                                        | 150      |                          |                          | C                    |

| T <sub>jrs</sub> <sup>(2)</sup>                                                                     | Overtemperature reset                                                        |                                                                                                                                        | 135      |                          |                          | °C                   |

#### Table 4. Electrical characteristics (continued)

| Symbol         | Parameter                     | Test conditions                                                                                                           | Min. | Тур.     | Max. | Unit     |

|----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|----------|------|----------|

| $I_{gf}^{(2)}$ | Fault sink current            | $V_{in} = 10 V V_{DS} = 13 V$<br>$V_{in} = 5 V V_{DS} = 13 V$                                                             |      | 50<br>20 |      | mA<br>mA |

| $E_{as}^{(2)}$ | Single pulse avalanche energy | starting T <sub>j</sub> = 25°C V <sub>DD</sub> = 20 V<br>V <sub>in</sub> = 10 V R <sub>gen</sub> = 1 K $\Omega$ L = 10 mH | 0.65 |          |      | J        |

#### Table 4. Electrical characteristics (continued)

1. Pulsed: Pulse duration = 300  $\mu s,$  duty cycle 1.5 %

2. Parameters guaranteed by design/characterization

## **3** Protection features

During normal operation, the Input pin is electrically connected to the gate of the internal power MOSFET. The device then behaves like a standard power MOSFET and can be used as a switch from DC to 50 kHz. The only difference from the user's standpoint is that a small DC current (liss) flows into the Input pin in order to supply the internal circuitry.

The device integrates:

- Overvoltage clamp protection: internally set at 42 V, along with the rugged avalanche characteristics of the Power MOSFET stage give this device unrivalled ruggedness and energy handling capability. This feature is mainly important when driving inductive loads.

- Linear current limiter circuit: limits the drain current ld to llim whatever the Input pin voltage. When the current limiter is active, the device operates in the linear region, so power dissipation may exceed the capability of the heatsink. Both case and junction temperatures increase, and if this phase lasts long enough, junction temperature may reach the overtemperature threshold T<sub>jsh</sub>.

- Overtemperature and short circuit protection: these are based on sensing the chip temperature and are not dependent on the input voltage. The location of the sensing element on the chip in the power stage area ensures fast, accurate detection of the junction temperature. Overtemperature cutout occurs at minimum 150 °C. The device is automatically restarted when the chip temperature falls below 135 °C.

- Status feedback: in the case of an overtemperature fault condition, a Status Feedback is provided through the Input pin. The internal protection circuit disconnects the input from the gate and connects it instead to ground via an equivalent resistance of 100 Ω. The failure can be detected by monitoring the voltage at the Input pin, which will be close to ground potential.

Additional features of this device are ESD protection according to the Human Body model and the ability to be driven from a TTL Logic circuit (with a small increase in RDS(on)).

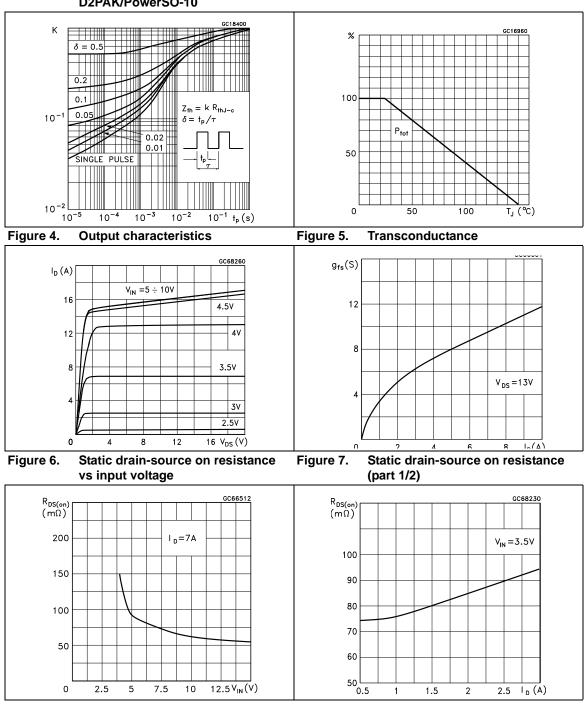

Figure 2. Thermal impedance for Figure 2. D2PAK/PowerSO-10

Figure 3. Derating curve

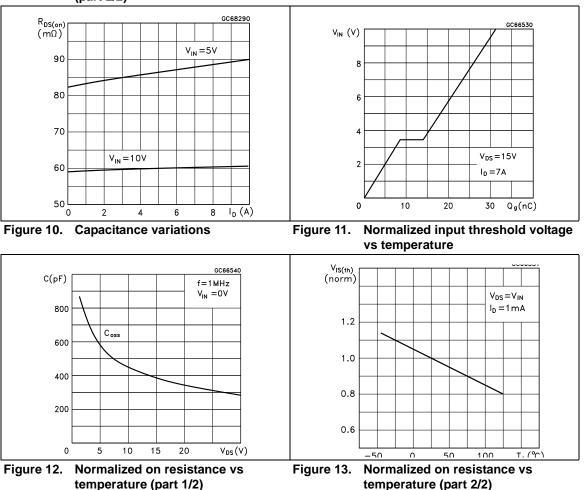

Input charge vs input voltage

Figure 8. Static drain-source on resistance (part 2/2)

Figure 9.

57

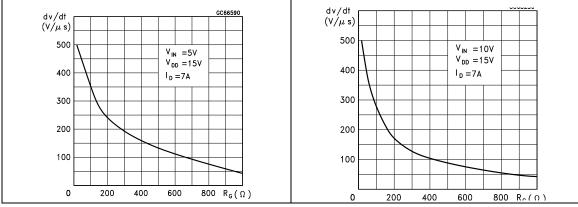

GC66580 di /dt (A/µ s) di /dt (A/µ s) GC68240  $V_{IN} = 5V$  $V_{IN} = 10V$  $V_{DD} = 15V$ 120  $V_{DD} = 15V$ 120  $I_D = 7A$  $I_{D} = 7A$ 100 100 80 80 60 60 40 40 20 20 0 R<sub>G</sub>(Ω) 200 400 600 800 0 200 400 600 800  $R_{G}(\Omega)$

Figure 14. Turn-on current slope(part 1/2)

Figure 15. Turn-on current slope (part 2/2)

Figure 16. Turn-off drain-source voltage slope Figure 17. Turn-off drain-source voltage slope (part 1/2) (part 2/2)

Figure 18. Switching time resistive load (part Figure 19. Switching time resistive load (part 1/3) 2/3)

GC66620 GC66630  $I_{lim}(A)$  $t(\mu s)$  $V_{DD} = 15V$  $I_{D} = 7A$  $R_{g} = 4.7\Omega$ 0.6  $V_{IN} = 10V$ 0.5  $V_{DD} = 1.3V$ 18 0.4 16 0.3 t, t d(off) 0.2 14 0.1 t f t d(on) 12 0 100 T」(℃) -50 0 50 4 5 6 7 8 9 10 V<sub>IN</sub>(V) Figure 23. Figure 22. Step response current limit Source drain diode forward

# Figure 20. Switching time resistive load (part Figure 21. Current limit vs junction 3/3) temperature

57

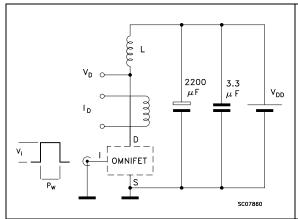

Figure 24. Unclamped inductive load test circuits

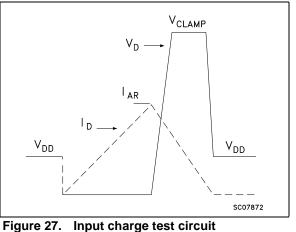

57

Figure 26. Switching times test circuits for resistive load

Figure 28. Test circuit for inductive load Figure 29. Waveforms switching and diode recovery times

Figure 25. Unclamped inductive waveforms

## 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>.

ECOPACK<sup>®</sup> is an ST trademark.

| DIM.     |      | mm   | 72 - 27 |       | inch | 95.   |

|----------|------|------|---------|-------|------|-------|

|          | MIN. | TYP. | MAX.    | MIN.  | TYP. | MAX.  |

| A        | 4.3  |      | 4.6     | 0.169 |      | 0.181 |

| A1       | 2.49 |      | 2.69    | 0.098 | с    | 0.106 |

| в        | 0.7  |      | 0.93    | 0.027 |      | 0.036 |

| B2       | 1.25 |      | 1.4     | 0.049 |      | 0.055 |

| С        | 0.45 |      | 0.6     | 0.017 |      | 0.023 |

| C2       | 1.21 |      | 1.36    | 0.047 |      | 0.053 |

| D        | 8.95 |      | 9.35    | 0.352 |      | 0.368 |

| E        | 10   |      | 10.28   | 0.393 |      | 0.404 |

| G        | 4.88 |      | 5.28    | 0.192 |      | 0.208 |

| L        | 15   |      | 15.85   | 0.590 |      | 0.624 |

| L2       | 1.27 |      | 1.4     | 0.050 |      | 0.055 |

| L3       | 1.4  |      | 1.75    | 0.055 |      | 0.068 |

|          |      |      |         | 650   |      | 1     |

| L2<br>L3 |      | B2   | A1      |       |      | D     |

Figure 30. TO-263 (D2PAK) mechanical data

13/17

| DIM.     | mm   |        |      |       | inch |       |

|----------|------|--------|------|-------|------|-------|

| (7,895A) | MIN. | TYP.   | MAX. | MIN.  | TYP. | MAX   |

| A        | 2.85 |        | 3.05 | 1.122 |      | 1.200 |

| A1       | 1.47 | 2      | 1.67 | 0.578 |      | 0.657 |

| b        | 0,40 |        | 0.60 | 0.157 |      | 0.236 |

| b1       | 1.4  | 6<br>6 | 1.6  | 0.551 |      | 0.630 |

| b2       | 1.3  |        | 1.5  | 0.511 |      | 0.590 |

| C        | 0.45 | 6<br>6 | 0.6  | 0.177 |      | 0.236 |

| D        | 10.5 |        | 10.9 | 4.133 |      | 4.291 |

| е        | 2.2  |        | 2.8  | 0.866 |      | 1.102 |

| E        | 7.45 |        | 7.75 | 2.933 |      | 3.051 |

| L        | 15.5 |        | 15.9 | 6.102 |      | 6.260 |

| L1       | 1.95 |        | 2.35 | 0.767 |      | 0.925 |

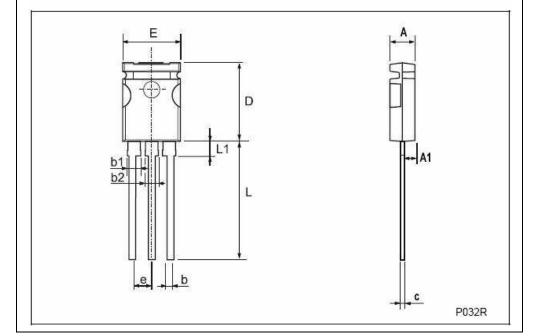

Figure 31. SOT82-FM mechanical data

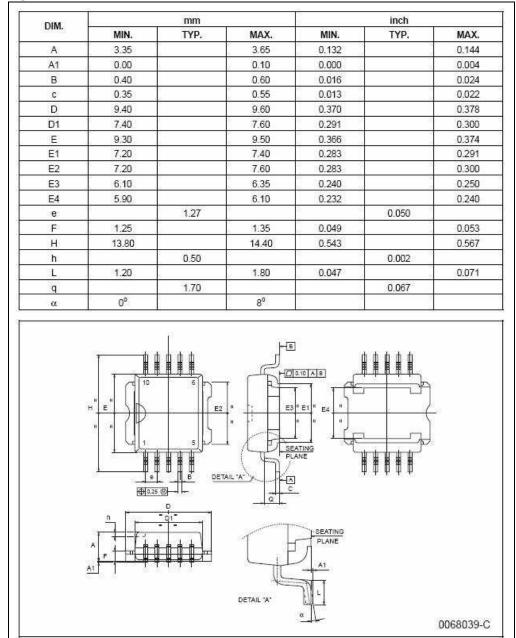

Figure 32. PowerSO-10 mechanical data

# 5 Revision history

| n history |

|-----------|

|           |

| Date        | Revision | Changes                                                                                                                              |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 20-Jan-1998 | 1        | Initial release.                                                                                                                     |

| 21-Jun-2004 | 5        | Update.                                                                                                                              |

| 08-Apr-2009 | 6        | Document reformatted.<br>Added <i>Table 1: Device summary on page 1.</i><br>Updated <i>Section 4: Package information on page 13</i> |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

17/17