# Octal, 12-/16-Bit, I<sup>2</sup>C, *dense*DACs with 5 ppm/°C On-Chip Reference

### **Data Sheet**

### FEATURES

Low power octal DACs AD5629R: 12 bits AD5669R: 16 bits 2.6 mm × 2.6 mm 16-ball WLCSP 4 mm × 4 mm 16-lead LFCSP and 16-lead TSSOP On-chip 1.25 V/2.5 V, 5 ppm/°C reference Power down to 400 nA at 5 V, 200 nA at 3 V 2.7 V to 5.5 V power supply Guaranteed monotonic by design Power-on reset to zero scale or midscale 3 power-down functions Hardware LDAC and CLR functions I<sup>2</sup>C-compatible serial interface supports standard (100 kHz) and fast (400 kHz) modes

### APPLICATIONS

Process control Data acquisition systems Portable battery-powered instruments Digital gain and offset adjustment Programmable voltage and current sources

### **GENERAL DESCRIPTION**

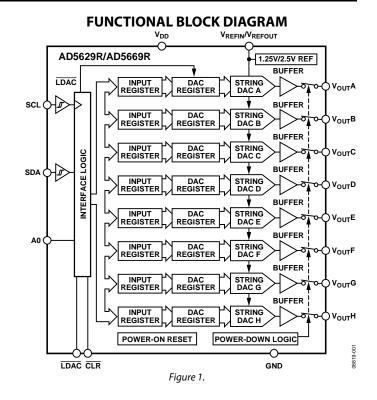

The AD5629R/AD5669R devices are low power, octal, 12-/16bit, buffered voltage-output DACs. All devices are guaranteed monotonic by design.

The AD5629R/AD5669R have an on-chip reference with an internal gain of 2. The AD5629R-1/AD5669R-1 have a 1.25 V, 5 ppm/°C reference, giving a full-scale output range of 2.5 V. The AD5629R-2/AD5629R-3 and the AD5669R-2/AD5669R-3 have a 2.5 V 5 ppm/°C reference, giving a full-scale output range of 5 V depending on the option selected. Devices with 1.25 V reference selected operate from a single 2.7 V to 5.5 V supply. Devices with 2.5 V reference is off at power-up, allowing the use of an external reference. The internal reference is enabled via a software write.

# AD5629R/AD5669R

The parts incorporate a power-on reset circuit to ensure that the DAC output powers up to 0 V (AD5629R-1/AD5629R-2, AD5669R-1/AD5669R-2) or midscale (AD5629R-3/AD5669R-3) and remains powered up at this level until a valid write takes place. The part contains a power-down feature that reduces the current consumption of the device to 400 nA at 5 V and provides software-selectable output loads while in power-down mode for any or all DAC channels.

### **PRODUCT HIGHLIGHTS**

- 1. Octal, 12-/16-bit DACs.

- 2. On-chip 1.25 V/2.5 V, 5 ppm/°C reference.

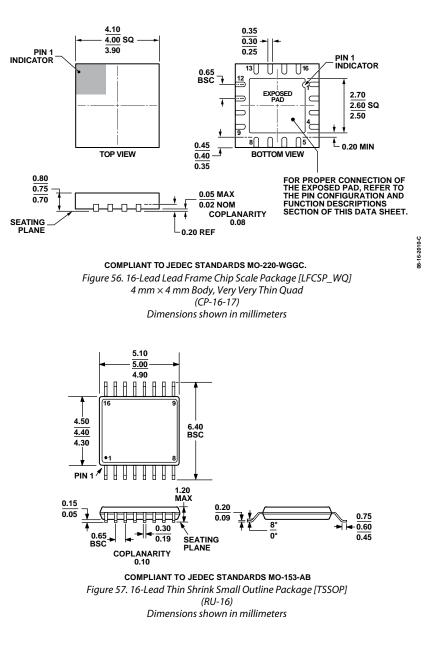

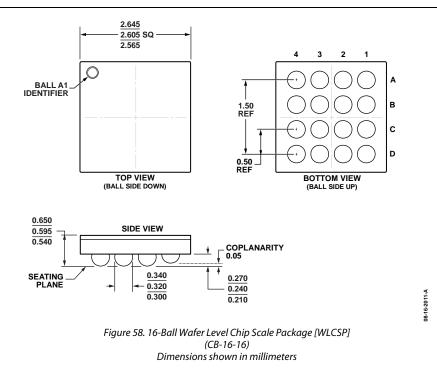

- 3. Available in 16-lead LFCSP and TSSOP, and 16-ball WLCSP.

- 4. Power-on reset to 0 V or midscale.

- 5. Power-down capability. When powered down, the DAC typically consumes 200 nA at 3 V and 400 nA at 5 V.

#### Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2010-2013 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **Data Sheet**

# TABLE OF CONTENTS

### **REVISION HISTORY**

#### 2/13—Rev. A to Rev. B

| Added 16-Ball WLCSP                     | Universal |

|-----------------------------------------|-----------|

| Changes to Features Section             | 1         |

| Added Figure 5, Renumbered Sequentially | 10        |

| Moved Table 6                           | 11        |

| Changes to Figure 25 and Figure 26      | 15        |

| Added Figure 58                         | 29        |

| Changes to Ordering Guide               |           |

|                                         |           |

#### 12/10—Rev. 0 to Rev. A

| Changes to Features, General Description, and Product          |

|----------------------------------------------------------------|

| Highlights Sections1                                           |

| Changes to AD5629R Relative Accuracy Parameter, Reference      |

| Output (1.25 V) Reference Input Range Parameter, and Reference |

| Output (2.5 V) Reference Input Range Parameter (Table 1) 3     |

|   | Resistor String                      | . 21 |

|---|--------------------------------------|------|

|   | Internal Reference                   | . 21 |

|   | Output Amplifier                     | . 22 |

|   | Serial Interface                     | . 22 |

|   | Write Operation                      | . 22 |

|   | Read Operation                       | . 22 |

|   | Input Shift Register                 | . 23 |

|   | Multiple Byte Operation              | . 23 |

|   | Internal Reference Register          | . 24 |

|   | Power-On Reset                       | . 24 |

|   | Power-Down Modes                     | . 25 |

|   | Clear Code Register                  | . 25 |

|   | LDAC Function                        | . 27 |

|   | Power Supply Bypassing and Grounding | . 27 |

| 0 | utline Dimensions                    | . 28 |

|   | Ordering Guide                       | . 30 |

|   |                                      |      |

| Changes to Relative Accuracy Parameter, Reference Tempco     |

|--------------------------------------------------------------|

| Parameter (Table 2)5                                         |

| Changes to Output Voltage Settling Time Parameter (Table 3)6 |

| Changes to Table 59                                          |

| Changes to CLR Pin Description (Table 6) 10                  |

| Added Figure 32 and Figure 33 15                             |

| Added Figure 46 17                                           |

| Changes to Internal Reference Section                        |

| Changes to Power-On Reset Section                            |

| Changes to Clear Code Register Section                       |

| Updated Outline Dimensions                                   |

| Changes to Ordering Guide                                    |

|                                                              |

10/10—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{DD}}$  = 4.5 V to 5.5 V,  $R_L$  = 2 k $\Omega$  to GND,  $C_L$  = 200 pF to GND,  $V_{\text{REFIN}}$  =  $V_{\text{DD}}$ . All specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

### Table 1.

|                                      |       | A Grade | <b>e</b> <sup>1</sup> |       | B Grade    | <b>e</b> <sup>1</sup> |        |                                                                              |

|--------------------------------------|-------|---------|-----------------------|-------|------------|-----------------------|--------|------------------------------------------------------------------------------|

| Parameter                            | Min   | Тур     | Max                   | Min   | Тур        | Max                   | Unit   | Test Conditions/Comments                                                     |

| STATIC PERFORMANCE <sup>2</sup>      |       |         |                       |       |            |                       |        |                                                                              |

| AD5629R                              |       |         |                       |       |            |                       |        |                                                                              |

| Resolution                           | 12    |         |                       | 12    |            |                       | Bits   |                                                                              |

| Relative Accuracy                    |       | ±0.5    | ±4                    |       | ±0.5       | ±1                    | LSB    | See Figure 6                                                                 |

| Differential Nonlinearity            |       |         | ±0.25                 |       |            | ±0.25                 | LSB    | Guaranteed monotonic by design<br>(see Figure 8)                             |

| AD5669R                              |       |         |                       |       |            |                       |        |                                                                              |

| Resolution                           | 16    |         |                       | 16    |            |                       | Bits   |                                                                              |

| Relative Accuracy                    |       | ±8      | ±32                   |       | ±8         | ±16                   | LSB    | See Figure 5                                                                 |

| Differential Nonlinearity            |       |         | ±1                    |       |            | ±1                    | LSB    | Guaranteed monotonic by design<br>(see Figure 7)                             |

| Zero-Code Error                      |       | 6       | 19                    |       | 6          | 19                    | mV     | All 0s loaded to DAC register (see Figure 18)                                |

| Zero-Code Error Drift                | 1     | ±2      |                       |       | ±2         |                       | μV/°C  |                                                                              |

| Full-Scale Error                     | 1     | -0.2    | -1                    |       | -0.2       | -1                    | % FSR  | All 1s loaded to DAC register (see Figure 19)                                |

| Gain Error                           | 1     |         | ±1                    |       |            | ±1                    | % FSR  |                                                                              |

| Gain Temperature Coefficient         |       | ±2.5    |                       |       | ±2.5       |                       | ppm    | Of FSR/°C                                                                    |

| Offset Error                         |       | ±6      | ±19                   |       | ±6         | ±19                   | mV     |                                                                              |

| DC Power Supply Rejection<br>Ratio   |       | -80     |                       |       | -80        | ,                     | dB     | $V_{DD} \pm 10\%$                                                            |

| DC Crosstalk<br>(External Reference) |       | 10      |                       |       | 10         |                       | μV     | Due to full-scale output change, $R_L = 2 k\Omega$ to GND or $V_{DD}$        |

|                                      |       | 5       |                       |       | 5          |                       | μV/mA  | Due to load current change                                                   |

|                                      |       | 10      |                       |       | 10         |                       | μV     | Due to powering down (per channel)                                           |

| DC Crosstalk<br>(Internal Reference) |       | 25      |                       |       | 25         |                       | μV     | Due to full-scale output change,<br>$R_L = 2 k\Omega$ to GND or $V_{DD}$     |

| · · · · ·                            |       | 10      |                       |       | 10         |                       | μV/mA  | Due to load current change                                                   |

| OUTPUT CHARACTERISTICS <sup>3</sup>  |       |         |                       |       |            |                       |        |                                                                              |

| Output Voltage Range                 | 0     |         | V <sub>DD</sub>       | 0     |            | V <sub>DD</sub>       | v      |                                                                              |

| Capacitive Load Stability            | Ũ     | 2       | • 00                  | Ũ     | 2          | •00                   | nF     | $R_L = \infty$                                                               |

| cupuelitive Louis Stability          |       | 10      |                       |       | 10         |                       | nF     | $R_L = 2 k\Omega$                                                            |

| DC Output Impedance                  |       | 0.5     |                       |       | 0.5        |                       | Ω      |                                                                              |

| Short-Circuit Current                |       | 30      |                       |       | 30         |                       | mA     | $V_{DD} = 5 V$                                                               |

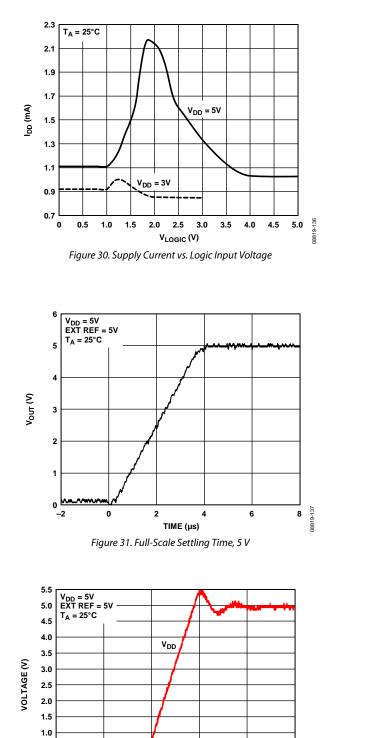

| Power-Up Time                        |       | 4       |                       |       | 4          |                       |        | Coming out of power-down mode, $V_{DD} = 5$ V                                |

| REFERENCE INPUTS                     |       | 4       |                       |       | 4          |                       | μs     | $\sim$                                                                       |

|                                      | 1     | 40      | 50                    |       | 10         | 50                    |        |                                                                              |

| Reference Current                    |       | 40      | 50<br>V               |       | 40         | 50<br>V               | μA     | $V_{\text{REFIN}} = V_{\text{DD}} = 5.5 \text{ V} \text{ (per DAC channel)}$ |

| Reference Input Range                | 0     | 11-     | $V_{\text{DD}}$       | 0     | 140        | $V_{\text{DD}}$       | V      |                                                                              |

| Reference Input Impedance            |       | 14.6    |                       |       | 14.6       |                       | kΩ     |                                                                              |

| REFERENCE OUTPUT (1.25 V)            |       |         |                       |       |            |                       |        | T 050C                                                                       |

| Output Voltage                       | 1.247 |         | 1.253                 | 1.247 |            | 1.253                 | μA     | $T_A = 25^{\circ}C$                                                          |

| Reference Input Range                |       | ±15     |                       |       | ±5         | ±15                   | ppm/°C | LFCSP, TSSOP                                                                 |

| Output Impedance                     |       | 7.5     |                       |       | ±15<br>7.5 |                       | kΩ     | WLCSP                                                                        |

| REFERENCE OUTPUT (2.5 V)             |       |         |                       |       |            |                       |        |                                                                              |

| Output Voltage                       | 2.495 |         | 2.505                 | 2.495 |            | 2.505                 | μA     | $T_A = 25^{\circ}C$                                                          |

| Reference Input Range                | 2.795 | ±15     | 2.505                 | 2.495 | ±5         | ±10                   | ppm/°C |                                                                              |

| Output Impedance                     | 1     |         |                       |       |            | 10                    |        |                                                                              |

| Output impedance                     |       | 7.5     |                       |       | 7.5        |                       | kΩ     | <u> </u>                                                                     |

|                                                     |     | A Grade | e <sup>1</sup> |     | B Grade | <b>e</b> <sup>1</sup> |      |                                                                         |

|-----------------------------------------------------|-----|---------|----------------|-----|---------|-----------------------|------|-------------------------------------------------------------------------|

| Parameter                                           | Min | Тур     | Max            | Min | Тур     | Max                   | Unit | Test Conditions/Comments                                                |

| LOGIC INPUTS <sup>3</sup>                           |     |         |                |     |         |                       |      |                                                                         |

| Input Current                                       |     |         | ±3             |     |         | ±3                    | μΑ   | All digital inputs                                                      |

| Input Low Voltage, V <sub>INL</sub>                 |     |         | 0.8            |     |         | 0.8                   | V    | $V_{DD} = 5 V$                                                          |

| Input High Voltage, V <sub>INH</sub>                | 2   |         |                | 2   |         |                       | V    | $V_{DD} = 5 V$                                                          |

| Pin Capacitance                                     |     | 3       |                |     | 3       |                       | pF   |                                                                         |

| POWER REQUIREMENTS                                  |     |         |                |     |         |                       |      |                                                                         |

| V <sub>DD</sub>                                     | 4.5 |         | 5.5            | 4.5 |         | 5.5                   | V    | All digital inputs at 0 or $V_{DD}$ , DAC active, excludes load current |

| I <sub>DD</sub> (Normal Mode) <sup>4</sup>          |     |         |                |     |         |                       |      | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                    |

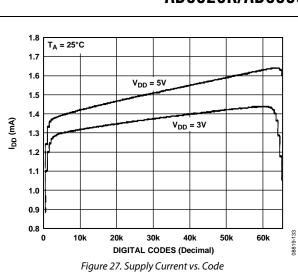

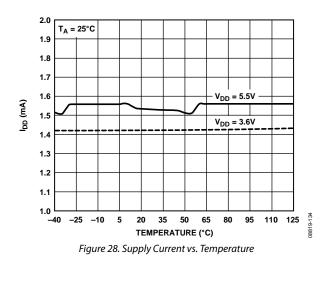

| $V_{DD} = 4.5 V$ to 5.5 V                           |     | 1.3     | 1.8            |     | 1.3     | 1.8                   | mA   | Internal reference off                                                  |

|                                                     |     | 2       | 2.5            |     | 2       | 2.5                   | mA   | Internal reference on                                                   |

| I <sub>DD</sub> (All Power-Down Modes) <sup>5</sup> |     |         |                |     |         |                       |      |                                                                         |

| $V_{DD} = 4.5 V$ to 5.5 V                           |     | 0.4     | 1              |     | 0.4     | 1                     | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                    |

<sup>1</sup> Temperature range is -40°C to +105°C, typical at 25°C. <sup>2</sup> Linearity calculated using a reduced code range of the AD5629R (Code 32 to Code 4064) and the AD5669R (Code 512 to 65,024). Output unloaded. <sup>3</sup> Guaranteed by design and characterization; not production tested. <sup>4</sup> Interface inactive. All DACs active. DAC outputs unloaded. <sup>5</sup> All eight DACs powered down.

# **Data Sheet**

$V_{\text{DD}} = 2.7 \text{ V to } 3.6 \text{ V}, R_{\text{L}} = 2 \text{ } k\Omega \text{ to GND}, C_{\text{L}} = 200 \text{ pF to GND}, V_{\text{REFIN}} = V_{\text{DD}}. \text{ All specifications } T_{\text{MIN}} \text{ to } T_{\text{MAX}} \text{, unless otherwise noted.}$

|                                      | A Grade <sup>1</sup> B Grade <sup>1</sup> |         | <b>e</b> <sup>1</sup> |       |         |                 |             |                                                                                             |

|--------------------------------------|-------------------------------------------|---------|-----------------------|-------|---------|-----------------|-------------|---------------------------------------------------------------------------------------------|

| Parameter                            | Min                                       | Тур     | Max                   | Min   | Тур     | Max             | Unit        | Conditions/Comments                                                                         |

| STATIC PERFORMANCE <sup>2</sup>      |                                           |         |                       |       |         |                 |             |                                                                                             |

| AD5629R                              |                                           |         |                       |       |         |                 |             |                                                                                             |

| Resolution                           | 12                                        |         |                       | 12    |         |                 | Bits        |                                                                                             |

| Relative Accuracy                    |                                           | ±0.5    | ±4                    |       | ±0.5    | ±1              | LSB         | See Figure 6                                                                                |

| Differential Nonlinearity            |                                           |         | ±0.25                 |       |         | ±0.25           | LSB         | Guaranteed monotonic by design (see Figure 8)                                               |

| AD5669R                              |                                           |         |                       |       |         |                 |             |                                                                                             |

| Resolution                           | 16                                        |         |                       | 16    |         |                 | Bits        |                                                                                             |

| Relative Accuracy                    |                                           | ±8      | ±32                   |       | ±8      | ±16             | LSB         | See Figure 5                                                                                |

| Differential Nonlinearity            |                                           |         | ±1                    |       |         | ±1              | LSB         | Guaranteed monotonic by design (see Figure 7)                                               |

| Zero-Code Error                      |                                           | 6       | 19                    |       | 6       | 19              | mV          | All 0s loaded to DAC register (see Figure 18)                                               |

| Zero-Code Error Drift                |                                           | ±2      |                       |       | ±2      |                 | μV/°C       |                                                                                             |

| Full-Scale Error                     |                                           | -0.2    | -1                    |       | -0.2    | -1              | % FSR       | All 1s loaded to DAC register (see Figure 19)                                               |

| Gain Error                           |                                           |         | ±1                    |       |         | ±1              | % FSR       |                                                                                             |

| Gain Temperature Coefficient         |                                           | ±2.5    |                       |       | ±2.5    |                 | ppm         | Of FSR/°C                                                                                   |

| Offset Error                         |                                           | ±6      | ±19                   |       | ±6      | ±19             | mV          |                                                                                             |

| DC Power Supply Rejection            |                                           | -80     |                       |       | -80     |                 | dB          | $V_{DD} \pm 10\%$                                                                           |

| Ratio                                |                                           |         |                       |       |         |                 |             |                                                                                             |

| DC Crosstalk<br>(External Reference) |                                           | 10      |                       |       | 10      |                 | μV          | Due to full-scale output change,<br>R <sub>L</sub> = 2 k $\Omega$ to GND or V <sub>DD</sub> |

| (External Reference)                 |                                           | 5       |                       |       | 5       |                 | μV/mA       | $R_L = 2 RD to GND of V_{DD}$<br>Due to load current change                                 |

|                                      |                                           | 5<br>10 |                       |       | 5<br>10 |                 | μv/mA<br>μV | Due to powering down (per channel)                                                          |

| DC Crosstalk                         |                                           | 25      |                       |       | 25      |                 |             | Due to full-scale output change,                                                            |

| (Internal Reference)                 |                                           | 25      |                       |       | 23      |                 | μV          | $R_L = 2 k\Omega$ to GND or $V_{DD}$                                                        |

| (                                    |                                           | 10      |                       |       | 10      |                 | μV/mA       | Due to load current change                                                                  |

| OUTPUT CHARACTERISTICS <sup>3</sup>  |                                           |         |                       |       |         |                 | <b>F</b> ,  |                                                                                             |

| Output Voltage Range                 | 0                                         |         | V <sub>DD</sub>       | 0     |         | V <sub>DD</sub> | v           |                                                                                             |

| Capacitive Load Stability            |                                           | 2       |                       |       | 2       |                 | nF          | $R_1 = \infty$                                                                              |

|                                      |                                           | 10      |                       |       | 10      |                 | nF          | $R_L = 2 k\Omega$                                                                           |

| DC Output Impedance                  |                                           | 0.5     |                       |       | 0.5     |                 | Ω           |                                                                                             |

| Short-Circuit Current                |                                           | 30      |                       |       | 30      |                 | mA          | $V_{DD} = 3 V$                                                                              |

| Power-Up Time                        |                                           | 4       |                       |       | 4       |                 | μs          | Coming out of power-down mode, $V_{DD} = 3 V$                                               |

| REFERENCE INPUTS                     |                                           |         |                       |       |         |                 |             |                                                                                             |

| Reference Current                    |                                           | 40      | 50                    |       | 40      | 50              | μA          | $V_{REFIN} = V_{DD} = 3.6 V$ (per DAC channel)                                              |

| Reference Input Range                | 0                                         |         | V <sub>DD</sub>       | 0     |         | V <sub>DD</sub> |             |                                                                                             |

| Reference Input Impedance            |                                           | 14.6    |                       |       | 14.6    |                 | kΩ          |                                                                                             |

| REFERENCE OUTPUT                     |                                           |         |                       |       |         |                 |             |                                                                                             |

| Output Voltage                       |                                           |         |                       |       |         |                 |             |                                                                                             |

| AD5629R/AD5669R                      | 1.247                                     |         | 1.253                 | 1.247 |         | 1.253           | v           | $T_A = 25^{\circ}C$                                                                         |

| Reference Tempco <sup>3</sup>        |                                           | ±15     |                       |       | ±5      | ±15             | ppm/°C      | LFCSP, TSSOP                                                                                |

|                                      |                                           |         |                       |       | ±15     | 2.0             | PP          | WLCSP                                                                                       |

| Reference Output Impedance           |                                           | 7.5     |                       |       | 7.5     |                 | kΩ          |                                                                                             |

| LOGIC INPUTS <sup>3</sup>            |                                           |         |                       |       |         |                 |             |                                                                                             |

| Input Current                        |                                           |         | ±3                    |       |         | ±3              | μA          | All digital inputs                                                                          |

| Input Low Voltage, VINL              |                                           |         | 0.8                   |       |         | 0.8             | V           | V <sub>DD</sub> = 3 V                                                                       |

| Input High Voltage, VINH             | 2                                         |         |                       | 2     |         |                 | V           | $V_{DD} = 3 V$                                                                              |

| Pin Capacitance                      |                                           | 3       |                       |       | 3       |                 | рF          |                                                                                             |

#### Table 2.

|                                                    |     | A Grade | e <sup>1</sup> |     | B Grad | <b>e</b> <sup>1</sup> |      |                                                                         |

|----------------------------------------------------|-----|---------|----------------|-----|--------|-----------------------|------|-------------------------------------------------------------------------|

| Parameter                                          | Min | Тур     | Мах            | Min | Тур    | Max                   | Unit | <b>Conditions/Comments</b>                                              |

| POWER REQUIREMENTS                                 |     |         |                |     |        |                       |      |                                                                         |

| V <sub>DD</sub>                                    | 2.7 |         | 3.6            | 2.7 |        | 3.6                   | V    | All digital inputs at 0 or $V_{DD}$ , DAC active, excludes load current |

| I <sub>DD</sub> (Normal Mode) <sup>4</sup>         |     |         |                |     |        |                       |      | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                    |

| $V_{DD} = 2.7 \text{ V} \text{ to } 3.6 \text{ V}$ |     | 1.0     | 1.5            |     | 1.0    | 1.5                   | mA   | Internal reference off                                                  |

|                                                    |     | 1.8     | 2.25           |     | 1.7    | 2.25                  | mA   | Internal reference on                                                   |

| IDD (All Power-Down Modes) <sup>5</sup>            |     |         |                |     |        |                       |      |                                                                         |

| $V_{DD} = 2.7 V$ to 3.6 V                          |     | 0.2     | 1              |     | 0.2    | 1                     | μΑ   | $V_{IH} = V_{DD}$ and $V_{IL} = GND$                                    |

<sup>1</sup> Temperature range is -40°C to +105°C, typical at 25°C.

<sup>2</sup> Linearity calculated using a reduced code range of the AD5629R (Code 32 to Code 4064) and the AD5669R (Code 512 to 65,024). Output unloaded.

<sup>3</sup> Guaranteed by design and characterization; not production tested.

<sup>4</sup> Interface inactive. All DACs active. DAC outputs unloaded.

<sup>5</sup> All eight DACs powered down.

#### **AC CHARACTERISTICS**

$V_{DD} = 2.7 V$  to 5.5 V,  $R_L = 2 k\Omega$  to GND,  $C_L = 200 pF$  to GND,  $V_{REFIN} = V_{DD}$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 3.                         |     |     |     |        |                                                                |

|----------------------------------|-----|-----|-----|--------|----------------------------------------------------------------|

| Parameter <sup>1, 2</sup>        | Min | Тур | Max | Unit   | Conditions/Comments <sup>3</sup>                               |

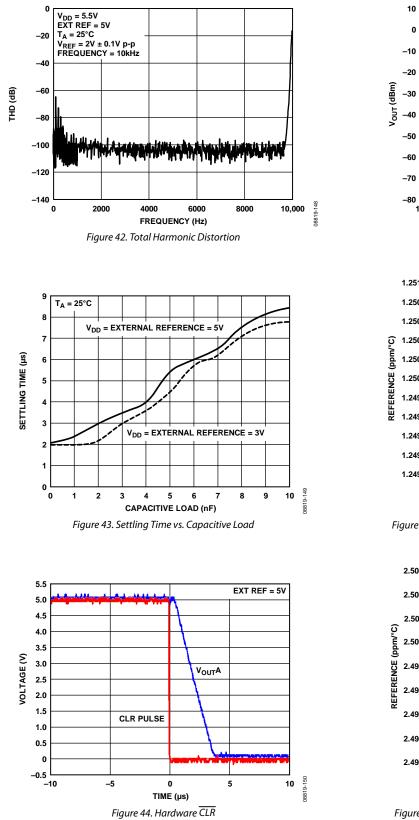

| Output Voltage Settling Time     |     | 2.5 | 7   | μs     | $\frac{1}{4}$ to $\frac{3}{4}$ scale settling to $\pm 2$ LSB   |

| Slew Rate                        |     | 1.2 |     | V/µs   |                                                                |

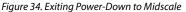

| Digital-to-Analog Glitch Impulse |     | 4   |     | nV-s   | 1 LSB change around major carry (see Figure 35)                |

|                                  |     | 19  |     | nV-s   | From Code 59904 to Code 59903                                  |

| Digital Feedthrough              |     | 0.1 |     | nV-s   |                                                                |

| Reference Feedthrough            |     | -90 |     | dB     | $V_{REFIN} = 2 V \pm 0.1 V p$ -p, frequency = 10 Hz to 20 MHz  |

| Digital Crosstalk                |     | 0.2 |     | nV-s   |                                                                |

| Analog Crosstalk                 |     | 0.4 |     | nV-s   |                                                                |

| DAC-to-DAC Crosstalk             |     | 0.8 |     | nV-s   |                                                                |

| Multiplying Bandwidth            |     | 320 |     | kHz    | $V_{\text{REFIN}} = 2 \text{ V} \pm 0.2 \text{ V} \text{ p-p}$ |

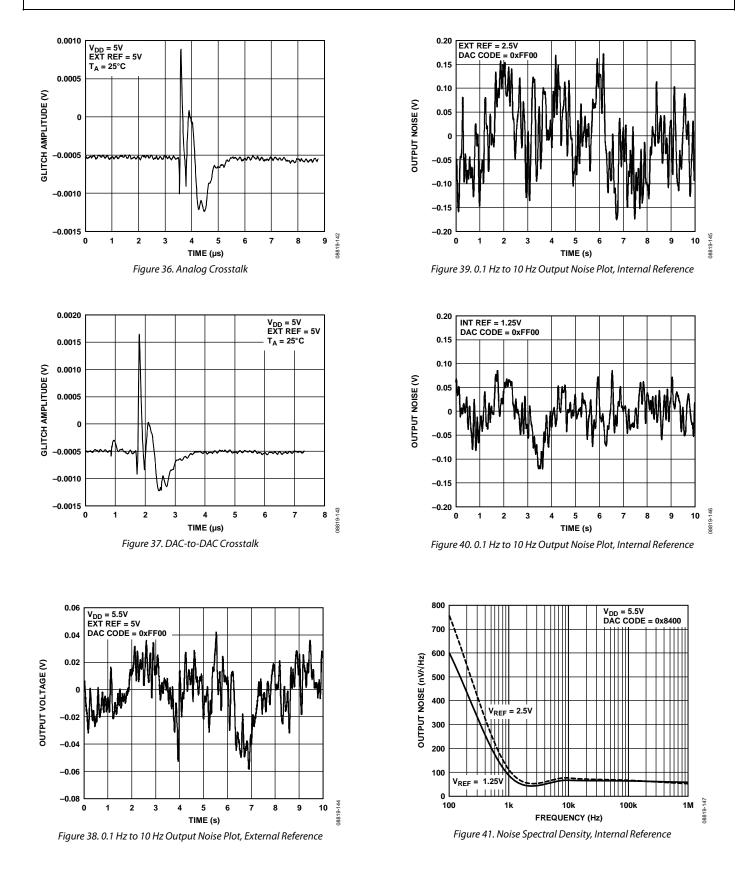

| Total Harmonic Distortion        |     | -80 |     | dB     | $V_{REFIN} = 2 V \pm 0.1 V p-p$ , frequency = 10 kHz           |

| Output Noise Spectral Density    |     | 120 |     | nV/√Hz | DAC code = 0x8400, 1 kHz                                       |

|                                  |     | 100 |     | nV/√Hz | DAC code = 0x8400, 10 kHz                                      |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> See the Terminology section.

<sup>3</sup> Temperature range is -40°C to +105°C, typical at 25°C.

### I<sup>2</sup>C TIMING CHARACTERISTICS

$V_{\text{DD}}$  = 2.7 V to 5.5 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ ,  $f_{\text{SCL}}$  = 400 kHz, unless otherwise noted.

| Parameter                     | Conditions    | Min | Max  | Unit | Description                                                                                                           |

|-------------------------------|---------------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------|

| f <sub>SCL</sub> <sup>1</sup> | Standard mode |     | 100  | kHz  | Serial clock frequency                                                                                                |

|                               | Fast mode     |     | 400  | kHz  |                                                                                                                       |

| t1                            | Standard mode | 4   |      | μs   | t <sub>нідн</sub> , SCL high time                                                                                     |

|                               | Fast mode     | 0.6 |      | μs   |                                                                                                                       |

| t <sub>2</sub>                | Standard mode | 4.7 |      | μs   | t <sub>LOW</sub> , SCL low time                                                                                       |

|                               | Fast mode     | 1.3 |      | μs   |                                                                                                                       |

| t <sub>3</sub>                | Standard mode | 250 |      | ns   | t <sub>SU;DAT</sub> , data setup time                                                                                 |

|                               | Fast mode     | 100 |      | ns   |                                                                                                                       |

| t4                            | Standard mode | 0   | 3.45 | μs   | t <sub>HD;DAT</sub> , data hold time                                                                                  |

|                               | Fast mode     | 0   | 0.9  | μs   |                                                                                                                       |

| t <sub>5</sub>                | Standard mode | 4.7 |      | μs   | t <sub>SU;STA</sub> , setup time for a repeated start condition                                                       |

|                               | Fast mode     | 0.6 |      | μs   |                                                                                                                       |

| t <sub>6</sub>                | Standard mode | 4   |      | μs   | t <sub>HD;STA</sub> , hold time (repeated) start condition                                                            |

|                               | Fast mode     | 0.6 |      | μs   |                                                                                                                       |

| t <sub>7</sub>                | Standard mode | 4.7 |      | μs   | $t_{\mbox{\scriptsize BUF}},$ bus-free time between a stop and a start condition                                      |

|                               | Fast mode     | 1.3 |      | μs   |                                                                                                                       |

| t <sub>8</sub>                | Standard mode | 4   |      | μs   | t <sub>su;sto</sub> , setup time for a stop condition                                                                 |

|                               | Fast mode     | 0.6 |      | μs   |                                                                                                                       |

| t9                            | Standard mode |     | 1000 | ns   | t <sub>RDA</sub> , rise time of SDA signal                                                                            |

|                               | Fast mode     |     | 300  | ns   |                                                                                                                       |

| t <sub>10</sub>               | Standard mode |     | 300  | ns   | t <sub>FDA</sub> , fall time of SDA signal                                                                            |

|                               | Fast mode     |     | 300  | ns   |                                                                                                                       |

| t <sub>11</sub>               | Standard mode |     | 1000 | ns   | t <sub>RCL</sub> , rise time of SCL signal                                                                            |

|                               | Fast mode     |     | 300  | ns   |                                                                                                                       |

| t <sub>11A</sub>              | Standard mode |     | 1000 | ns   | $t_{\mbox{\scriptsize RCL1}}$ , rise time of SCL signal after a repeated start condition and after an acknowledge bit |

|                               | Fast mode     |     | 300  | ns   |                                                                                                                       |

| t <sub>12</sub>               | Standard mode |     | 300  | ns   | t <sub>FCL</sub> , fall time of SCL signal                                                                            |

|                               | Fast mode     |     | 300  | ns   |                                                                                                                       |

| t <sub>13</sub>               | Standard mode | 10  |      | ns   | LDAC pulse width low                                                                                                  |

|                               | Fast mode     | 10  |      | ns   |                                                                                                                       |

| t <sub>14</sub>               | Standard mode | 300 |      | ns   | Falling edge of ninth SCL clock pulse of last byte of a valid write to the LDAC falling edge                          |

|                               | Fast mode     | 300 |      | ns   |                                                                                                                       |

| t15                           | Standard mode | 20  |      | ns   | CLR pulse width low                                                                                                   |

|                               | Fast mode     | 20  |      | ns   |                                                                                                                       |

| t <sub>SP</sub> <sup>2</sup>  | Fast mode     | 0   | 50   | ns   | Pulse width of spike suppressed                                                                                       |

<sup>1</sup> The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate but has a negative effect on the EMC behavior of the part.

<sup>2</sup> Input filtering on the SCL and SDA inputs suppresses noise spikes that are less than 50 ns for fast mode or less than 10 ns for high speed mode.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 5.

| Parameter                                  | Rating                            |

|--------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to GND                     | –0.3 V to +7 V                    |

| Digital Input Voltage to GND               | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Vout to GND                                | -0.3 V to V <sub>DD</sub> + 0.3 V |

| VREFIN/VREFOUT tO GND                      | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating Temperature Range                |                                   |

| Industrial                                 | –40°C to +105°C                   |

| Storage Temperature Range                  | –65°C to +150°C                   |

| Junction Temperature (T <sub>J MAX</sub> ) | +150°C                            |

| Power Dissipation                          | $(T_{J MAX} - T_A)/\Theta_{JA}$   |

| Thermal Impedance, $\theta_{JA}$           |                                   |

| 16-Lead TSSOP (4-Layer Board)              | 112.6°C/W                         |

| 16-Lead LFCSP (4-Layer Board)              | 30.4°C/W                          |

| Reflow Soldering Peak Temperature          |                                   |

| Pb Free                                    | 260°C                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

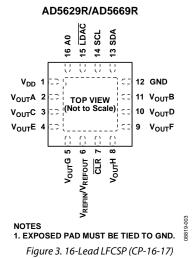

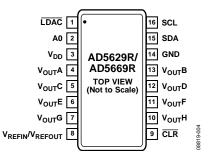

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. 16-Lead TSSOP (RU-16)

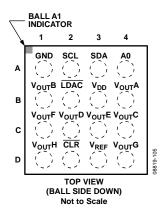

Figure 5. 16-Ball WLCSP

Table 6. Pin Function Descriptions

|       | Pin No. |       |                       |                                                                                                                                                                                                                                                                                                                                 |

|-------|---------|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP | TSSOP   | WLCSP | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                     |

| 15    | 1       | B2    | LDAC                  | Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to simultaneously update. Alternatively, this pin can be tied permanently low.                                                                                                             |

| 16    | 2       | A4    | A0                    | Address Input. Sets the least significant bit of the 7-bit slave address.                                                                                                                                                                                                                                                       |

| 1     | 3       | B3    | V <sub>DD</sub>       | Power Supply Input. These parts can be operated from 2.7 V to 5.5 V. Decouple the supply with a 10 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to GND.                                                                                                                                                           |

| 2     | 4       | B4    | VoutA                 | Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 3     | 5       | B1    | VoutC                 | Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 4     | 6       | C4    | VoutE                 | Analog Output Voltage from DAC E. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 5     | 7       | C2    | VoutG                 | Analog Output Voltage from DAC G. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 6     | 8       | D3    | VREFIN/VREFOUT        | The AD5629R/AD5669R have a common pin for reference input and reference output. When using the internal reference, this is the reference output pin. When using an external reference, this is the reference input pin. The default for this pin is as a reference input.                                                       |

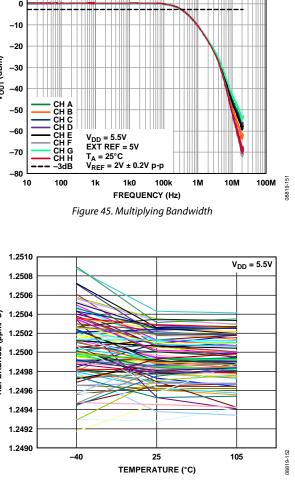

| 7     | 9       | D2    | CLR                   | Asynchronous Clear Input. The CLR input is falling edge sensitive. When CLR is low, all LDAC pulses are ignored. When CLR is activated, the input register and the DAC register are updated with the data contained in the CLR code register—zero scale, midscale, or full scale. The default setting clears the output to 0 V. |

| 8     | 10      | C3    | V <sub>OUT</sub> H    | Analog Output Voltage from DAC H. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 9     | 11      | C1    | VoutF                 | Analog Output Voltage from DAC F. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 10    | 12      | D4    | V <sub>OUT</sub> D    | Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 11    | 13      | D1    | VoutB                 | Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                              |

| 12    | 14      | A1    | GND                   | Ground Reference Point for All Circuitry on the Parts.                                                                                                                                                                                                                                                                          |

| 13    | 15      | A3    | SDA                   | Serial Data Input. This is used in conjunction with the SCL line to clock data into or out of the 32-bit input shift register. It is a bidirectional, open-drain data line that should be pulled to the supply with an external pull-up resistor.                                                                               |

| 14    | 16      | A4    | SCL                   | Serial Clock Line. This is used in conjunction with the SDA line to clock data into or out of the 32-bit input shift register.                                                                                                                                                                                                  |

| 17    | N/A     | N/A   | Exposed Pad<br>(EPAD) | The exposed pad must be tied to GND.                                                                                                                                                                                                                                                                                            |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Rev. B | Page 12 of 32

### **Data Sheet**

# AD5629R/AD5669R

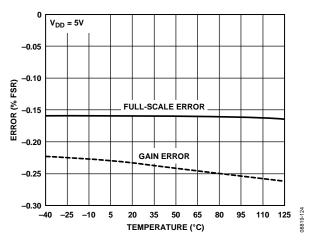

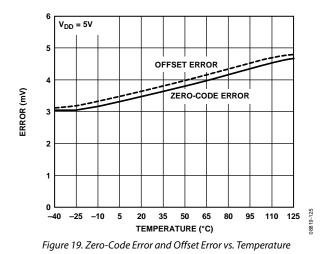

Figure 18. Gain Error and Full-Scale Error vs. Temperature

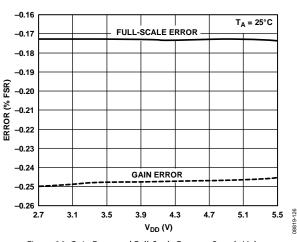

Figure 20. Gain Error and Full-Scale Error vs. Supply Voltage

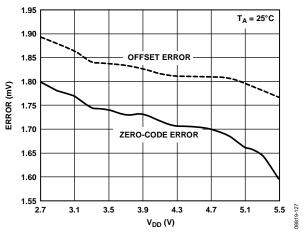

Figure 21. Zero-Code Error and Offset Error vs. Supply Voltage

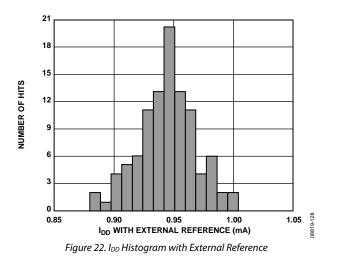

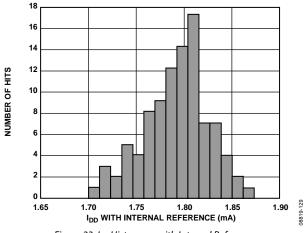

Figure 23. IDD Histogram with Internal Reference

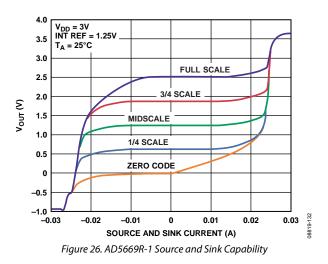

#### 0.4 T<sub>A</sub> = 25°C 0.3 0.2 ERROR VOLTAGE (V) 0.1 V<sub>DD</sub> = 3V, INT REF = 1.25V 0 -0.1 -0.2 -0.3 V<sub>DD</sub> = 5V, INT REF = 2.5V -0.4 -0.5 08819-130 -10 -8 -6 -4 -2 0 2 4 6 8 10 SOURCE/SINK CURRENT (mA) Figure 24. Headroom at Rails vs. Source and Sink

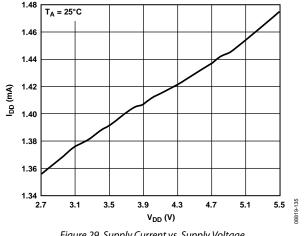

Figure 29. Supply Current vs. Supply Voltage

# AD5629R/AD5669R

VoutA

0.0006

0.0002

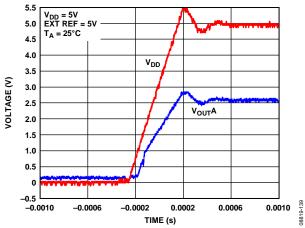

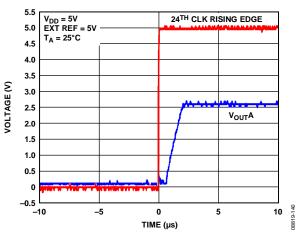

TIME (s) Figure 32. Power-On Reset to 0 V

Figure 33. Power-On Reset to Midscale

Rev. B | Page 16 of 32

08819-138

0.0010

-0.0006

-0.0002

0.5

0 -0.5

-0.0010

### **Data Sheet**

# AD5629R/AD5669R

Rev. B | Page 17 of 32

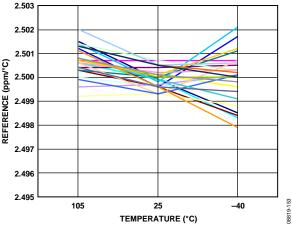

Figure 46. 1.25 V Reference Temperature Coefficient vs. Temperature

Figure 47. 2.5 V Reference Temperature Coefficient vs. Temperature

Rev. B | Page 18 of 32

### TERMINOLOGY

#### **Relative Accuracy**

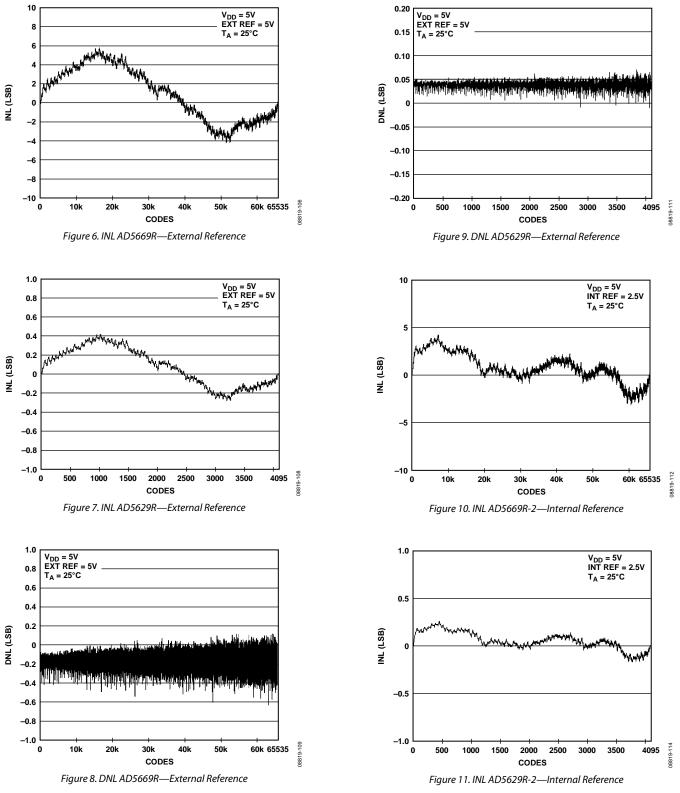

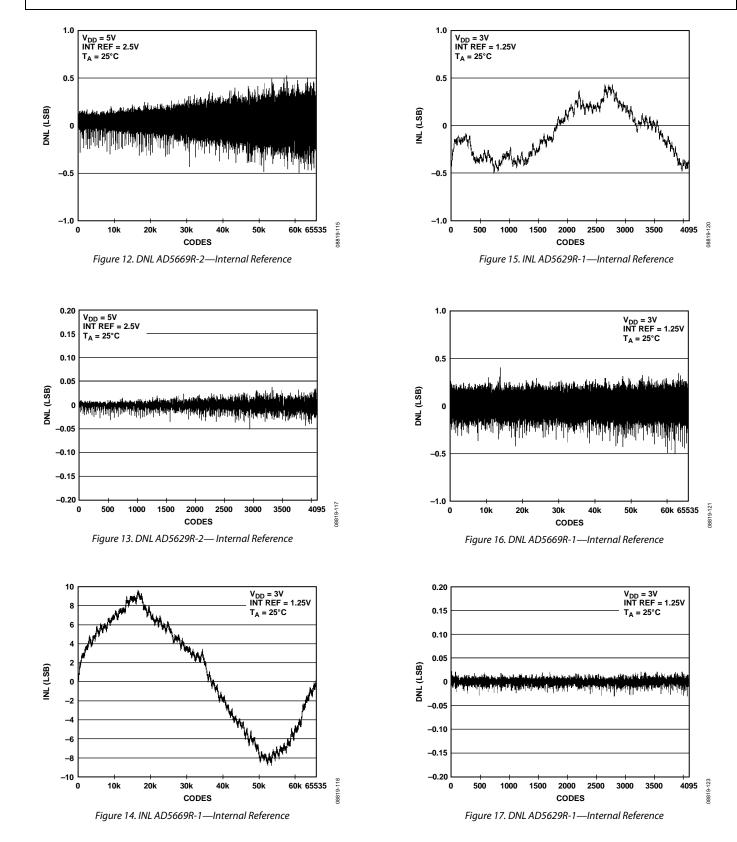

For the DAC, relative accuracy, or integral nonlinearity (INL), is a measure of the maximum deviation in LSBs from a straight line passing through the endpoints of the DAC transfer function. Figure 5, Figure 6, Figure 9, Figure 10, Figure 13, and Figure 14 show plots of typical INL vs. code.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. Figure 7, Figure 8, Figure 11, Figure 12, Figure 15, and Figure 16 show plots of typical DNL vs. code.

#### **Offset Error**

Offset error is a measure of the difference between the actual  $V_{OUT}$  and the ideal  $V_{OUT}$ , expressed in millivolts in the linear region of the transfer function. Offset error is measured on the AD5669R between Code 512 and Code 65024 loaded into the DAC register. It can be negative or positive and is expressed in millivolts.

#### Zero-Code Error

Zero-code error is a measure of the output error when zero code (0x0000) is loaded into the DAC register. Ideally, the output should be 0 V. The zero-code error is always positive because the output of the DAC cannot go below 0 V. It is due to a combination of the offset errors in the DAC and output amplifier. Zero-code error is expressed in millivolts. Figure 19 shows a plot of typical zero-code error vs. temperature.

#### **Gain Error**

Gain error is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal, expressed as a percentage of the full-scale range.

#### Zero-Code Error Drift

Zero-code error drift is a measure of the change in zero-code error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

#### **Gain Error Drift**

Gain error drift is a measure of the change in gain error with changes in temperature. It is expressed in (ppm of full-scale range)/°C.

#### **Full-Scale Error**

Full-scale error is a measure of the output error when full-scale code (0xFFFF) is loaded into the DAC register. Ideally, the output should be  $V_{REF} - 1$  LSB. Full-scale error is expressed as a percentage of the full-scale range. Figure 17 shows a plot of typical full-scale error vs. temperature.

#### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FFF to 0x8000). Figure 35 shows a typical digital-to-analog glitch impulse plot.

#### DC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{\text{OUT}}$  to a change in  $V_{\text{DD}}$  for full-scale output of the DAC.  $V_{\text{REF}}$  is held at 2 V, and  $V_{\text{DD}}$  is varied ±10%. It is measured in decibels.

#### DC Crosstalk

DC crosstalk is the dc change in the output level of one DAC in response to a change in the output of another DAC. It is measured with a full-scale output change on one DAC (or soft power-down and power-up) while monitoring another DAC kept at midscale. It is expressed in microvolts.

DC crosstalk due to load current change is a measure of the impact that a change in load current on one DAC has on another DAC kept at midscale. It is expressed in microvolts per milliamp.

#### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of a DAC from the digital input pins of the device, but is measured when the DAC is not being written to. It is specified in nV-s and measured with a full-scale change on the digital input pins, that is, from all 0s to all 1s or vice versa.

#### **Digital Crosstalk**

Digital crosstalk is the glitch impulse transferred to the output of one DAC at midscale in response to a full-scale code change (all 0s to all 1s or vice versa) in the input register of another DAC. It is measured in standalone mode and is expressed in nV-s.

#### Analog Crosstalk

Analog crosstalk is the glitch impulse transferred to the output of one DAC due to a change in the output of another DAC. It is measured by loading one of the input registers with a full-scale code change (all 0s to all 1s or vice versa) while keeping  $\overline{\text{LDAC}}$ high and then pulsing  $\overline{\text{LDAC}}$  low and monitoring the output of the DAC whose digital code has not changed. The area of the glitch is expressed in nV-s.

#### DAC-to-DAC Crosstalk

DAC-to-DAC crosstalk is the glitch impulse transferred to the output of one DAC due to a digital code change and subsequent output change of another DAC. This includes both digital and analog crosstalk. It is measured by loading one of the DACs with a full-scale code change (all 0s to all 1s or vice versa) with  $\overline{\text{LDAC}}$  low and monitoring the output of another DAC. The energy of the glitch is expressed in nV-s.

#### **Multiplying Bandwidth**

The amplifiers within the DAC have a finite bandwidth. The multiplying bandwidth is a measure of this. A sine wave on the reference (with full-scale code loaded to the DAC) appears on the output. The multiplying bandwidth is the frequency at which the output amplitude falls to 3 dB below the input.

#### **Total Harmonic Distortion (THD)**

Total harmonic distortion is the difference between an ideal sine wave and its attenuated version using the DAC. The sine wave is used as the reference for the DAC, and the THD is a measure of the harmonics present on the DAC output. It is measured in decibels.

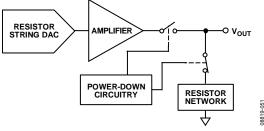

### THEORY OF OPERATION DIGITAL-TO-ANALOG CONVERTER (DAC) SECTION

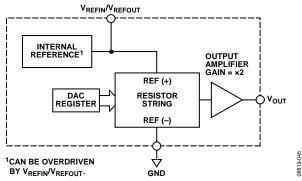

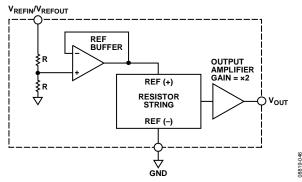

The AD5629R/AD5669R are fabricated on a CMOS process. The architecture consists of a string of DACs followed by an output buffer amplifier. Each part includes an internal 1.25 V/2.5 V, 5 ppm/°C reference with an internal gain of 2. Figure 48 and Figure 49 show block diagrams of the DAC architecture.

Figure 48. DAC Architecture for Internal Reference Configuration

Figure 49. DAC Architecture for External Reference Configuration

Because the input coding to the DAC is straight binary, the ideal output voltage when using an external reference is given by

$$V_{OUT} = V_{REFIN} \times \left(\frac{D}{2^N}\right)$$

The ideal output voltage when using the internal reference is given by

$$V_{OUT} = 2 \times V_{REFOUT} \times \left(\frac{D}{2^{N}}\right)$$

where:

D = decimal equivalent of the binary code that is loaded to the DAC register as follows: 0 to 4095 for AD5629R (12 bits).

0 to 65,535 for AD5669R (16 bits).

N = the DAC resolution.

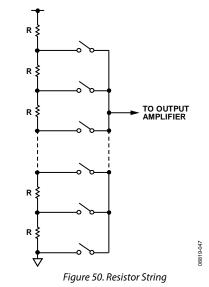

### **RESISTOR STRING**

The resistor string section is shown in Figure 50. It is simply a string of resistors, each of value R. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string to the amplifier. Because it is a string of resistors, it is guaranteed monotonic.

### **INTERNAL REFERENCE**

The AD5629R/AD5669R have an on-chip reference with an internal gain of 2. The AD5629R-1/AD5669R-1 have a 1.25 V, 5 ppm/°C reference, giving a full-scale output of 2.5 V or the AD5629R-2/AD5629R-3/AD5669R-2/AD5629R-3 have a 2.5 V, 5 ppm/°C reference, working between a supply from 4.5 V to 5.5 V giving a full-scale output of 5 V. The on-board reference is off at power-up, allowing the use of an external reference. The internal reference is enabled via a write to the control register (see Table 8).

The internal reference associated with each part is available at the  $V_{REFOUT}$  pin. A buffer is required if the reference output is used to drive external loads. When using the internal reference, it is recommended that a 100 nF capacitor be placed between the reference output and GND for reference stability.

Individual channel power-down is not supported while using the internal reference.

### **OUTPUT AMPLIFIER**

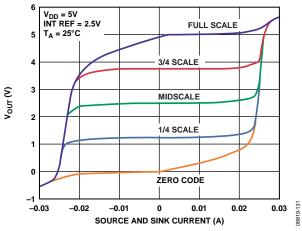

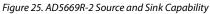

The output buffer amplifier can generate rail-to-rail voltages on its output, which gives an output range of 0 V to  $V_{DD}$ . The amplifier is capable of driving a load of 2 k $\Omega$  in parallel with 1000 pF to GND. The source and sink capabilities of the output amplifier can be seen in Figure 24 and Figure 25. The slew rate is 1.5 V/µs with a ¼ to ¾ scale settling time of 10 µs.

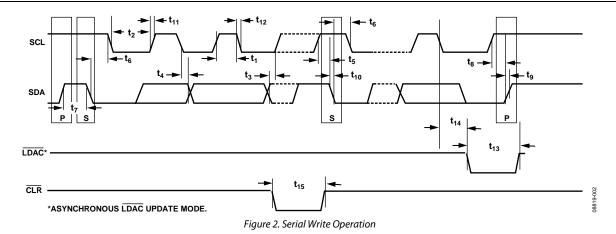

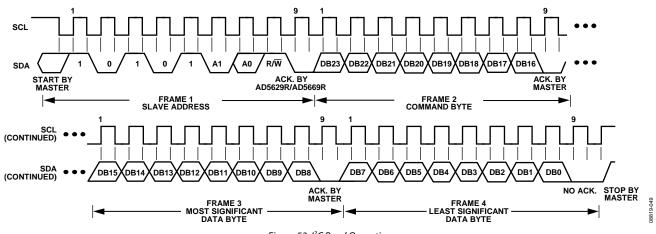

### SERIAL INTERFACE

The AD5629R/AD5669R have 2-wire I<sup>2</sup>C-compatible serial interfaces (refer to *The I<sup>2</sup>C-Bus Specification*, Version 2.1, January 2000, available from Philips Semiconductor). The AD5629R/AD5669R can be connected to an I<sup>2</sup>C bus as a slave device under the control of a master device. See Figure 2 for a timing diagram of a typical write sequence.

The AD5629R/AD5669R support standard (100 kHz) and fast (400 kHz) modes. High speed operation is only available on selected models. See the Ordering Guide for a full list of models. Support is not provided for 10-bit addressing and general call addressing.

The AD5629R/AD5669R each have a 7-bit slave address. The parts have a slave address whose five MSBs are 10101, and the two LSBs are set by the state of the A0 address pin, which determines the state of the A0 and A1 address bits.

The facility to make hardwired changes to the A0 pin allows the user to incorporate up to three of these devices on one bus, as outlined in Table 7.

### Table 7. ADDR Pin Settings

| A0 Pin Connection | A1 | A0 |

|-------------------|----|----|

| V <sub>DD</sub>   | 0  | 0  |

| NC                | 1  | 0  |

| GND               | 1  | 1  |

The 2-wire serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a start condition when a high-to-low transition on the SDA line occurs while SCL is high. The following byte is the address byte, which consists of the 7-bit slave address. The slave address corresponding to the transmitted address responds by pulling SDA low during the ninth clock pulse (this is termed the acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its shift register.

- 2. Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL.

- 3. When all data bits have been read or written, a stop condition is established. In write mode, the master pulls the SDA line high during the 10<sup>th</sup> clock pulse to establish a stop condition. In read mode, the master issues a no acknowledge for the ninth clock pulse (that is, the SDA line remains high). The master brings the SDA line low before the 10<sup>th</sup> clock pulse and then high during the 10<sup>th</sup> clock pulse to establish a stop condition.

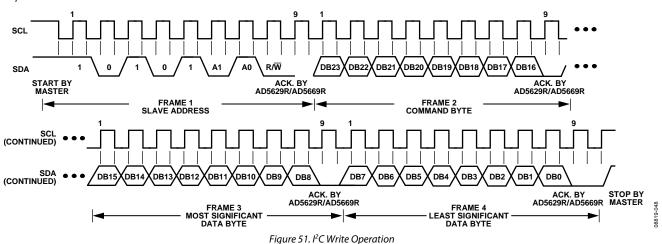

### WRITE OPERATION

When writing to the AD5629R/AD5669R, the user must begin with a start command followed by an address byte  $(R/\overline{W} = 0)$ , after which the DAC acknowledges that it is prepared to receive data by pulling SDA low. The AD5629R/AD5669R require two bytes of data for the DAC and a command byte that controls various DAC functions. Three bytes of data must, therefore, be written to the DAC, the command byte followed by the most significant data byte and the least significant data byte, as shown in Figure 51. After these data bytes are acknowledged by the AD5629R/AD5669R, a stop condition follows.

### **READ OPERATION**

When reading data back from the AD5629R/AD5669R, the user begins with a start command followed by an address byte  $(R/\overline{W} = 1)$ , after which the DAC acknowledges that it is prepared to transmit data by pulling SDA low. Two bytes of data are then read from the DAC, which are both acknowledged by the master as shown in Figure 52. A stop condition follows.

### **Data Sheet**

### AD5629R/AD5669R

#### Figure 52. I<sup>2</sup>C Read Operation

#### **Table 8. Command Definitions**

|    | Comr | nand |    |                                                                   |

|----|------|------|----|-------------------------------------------------------------------|

| С3 | C2   | C1   | C0 | Description                                                       |

| 0  | 0    | 0    | 0  | Write to Input Register n                                         |

| 0  | 0    | 0    | 1  | Update DAC Register n                                             |

| 0  | 0    | 1    | 0  | Write to In <u>put R</u> egister n; update all<br>(software LDAC) |

| 0  | 0    | 1    | 1  | Write to and update DAC Channel n                                 |

| 0  | 1    | 0    | 0  | Power down/power up DAC                                           |

| 0  | 1    | 0    | 1  | Load clear code register                                          |

| 0  | 1    | 1    | 0  | Load LDAC register                                                |

| 0  | 1    | 1    | 1  | Reset (power-on reset)                                            |

| 1  | 0    | 0    | 0  | Set up internal REF register                                      |

| 1  | 0    | 0    | 1  | Enable multiple byte mode                                         |

| 1  | 0    | 1    | 0  | Reserved                                                          |

| -  | -    | -    | -  | Reserved                                                          |

| 1  | 1    | 1    | 1  | Reserved                                                          |

#### **Table 9. Address Commands**

|    | Addr | ess (n) |    |                      |

|----|------|---------|----|----------------------|

| A3 | A2   | A1      | A0 | Selected DAC Channel |

| 0  | 0    | 0       | 0  | DAC A                |

| 0  | 0    | 0       | 1  | DAC B                |

| 0  | 0    | 1       | 0  | DAC C                |

| 0  | 0    | 1       | 1  | DAC D                |

| 0  | 1    | 0       | 0  | DAC E                |

| 0  | 1    | 0       | 1  | DAC F                |

| 0  | 1    | 1       | 0  | DAC G                |

| 0  | 1    | 1       | 1  | DAC H                |

| 1  | 1    | 1       | 1  | All DACs             |

#### **INPUT SHIFT REGISTER**

The input shift register is 24 bits wide. Data is loaded into the device as a 24-bit word under the control of a serial clock input, SCL. The input register contents for this operation is shown in Figure 53 and Figure 54. The eight MSBs make up the command byte. DB23 to DB20 are the command bits, C3, C2, C1, and C0, that control the mode of operation of the device (see Table 9 for details). The last four bits of the first byte are the address bits, A3, A2, A1, and A0, (see Table 9 for details). The rest of the bits are the 16-/12-bit data-word.

The AD5669R data-word comprises the 16-bit input code (see Figure 53) while the AD5629R data word is comprised of 12-bits followed by four don't cares (see Figure 54).

#### **MULTIPLE BYTE OPERATION**

Multiple byte operation is supported on the AD5629R/ AD5669R. Command 1001 is reserved for multiple byte operation (see Table 8) A 2-byte operation is useful for applications that require fast DAC updating and do not need to change the command byte. The S bit (DB22) in the command register can be set to 1 for the 2-byte mode of operation. For standard 3-byte and 4-byte operation, the S bit (DB22) in the command byte should be set to 0.

#### **INTERNAL REFERENCE REGISTER**

The internal reference is available on all versions. The on-board reference is off at power-up by default. The on-board reference can be turned off or on by a user-programmable internal REF register by setting Bit DB0 high or low (see Table 10). DB1 selects the internal reference value. Command 1000 is reserved for setting the internal REF register (see Table 8). Table 11 shows how the state of the bits in the input shift register corresponds to the mode of operation of the device.

#### **POWER-ON RESET**

The AD5629R/AD5669R contain a power-on reset circuit that controls the output voltage during power-up. The AD5629R/AD5669R DAC output powers up to 0 V and the AD5669R-3 DAC output powers up to midscale. The output remains powered up at this level until a valid write sequence is made to the DAC. This is useful in applications where it is important to know the state of the output of the DAC while it is in the process of powering up. There is also a software executable reset function that resets the DAC to the power-on reset code. Command 0111 is reserved for this reset function (see Table 8). Any events on LDAC or CLR during power-on reset are ignored.

| DB23 | DB22 | DB21 | DB20 | DB19   | DB18   | DB17  | DB16 | DB15 | DB14 | DB13 | DB12   | DB11   | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4    | DB3    | DB2 | DB1 | DB0 |

|------|------|------|------|--------|--------|-------|------|------|------|------|--------|--------|------|-----|-----|-----|-----|-----|--------|--------|-----|-----|-----|

| C3   | C2   | C1   | C0   | A3     | A2     | A1    | A0   | D15  | D14  | D13  | D12    | D11    | D10  | D9  | D8  | D7  | D6  | D5  | D4     | D3     | D2  | D1  | D0  |

|      | СОМ  | MAND |      | Ľ      | DAC AD | DRESS | 5    |      |      |      | DAC    | DATA   |      |     |     |     |     |     | DAC    | DATA   |     |     |     |

|      |      | C    | OMMA | ND BYT | E      |       |      |      |      | D    | ATA HI | GH BY1 | E    |     |     |     |     | D   | ATA LO | OW BY1 | Е   |     |     |

Figure 53. AD5669R Input Register Contents

| DB23 | DB22 | DB21 | DB20 | DB19   | DB18   | DB17  | DB16 | DB15 | DB14     | DB13 | DB12   | DB11   | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4    | DB3    | DB2 | DB1 | DB0 |

|------|------|------|------|--------|--------|-------|------|------|----------|------|--------|--------|------|-----|-----|-----|-----|-----|--------|--------|-----|-----|-----|

| C3   | C2   | C1   | C0   | A3     | A2     | A1    | A0   | D11  | D10      | D9   | D8     | D7     | D6   | D5  | D4  | D3  | D2  | D1  | D0     | х      | х   | х   | х   |

|      | СОМ  | MAND |      | Γ      | DAC AD | DRESS | •    |      | DAC DATA |      |        |        |      |     |     |     |     | DAC | DATA   |        |     |     |     |

|      |      | С    | омма | ND BYT | E      |       |      |      |          | D    | ATA HI | GH BY1 | Е    |     |     |     |     | D   | ATA LO | ом вут | Е   |     |     |

Figure 54. AD5629R Input Register Contents

### **POWER-DOWN MODES**

The AD5629R/AD5669R contain four separate modes of operation. Command 0100 is reserved for the power-down function (see Table 8). These modes are software-programmable by setting two bits, Bit DB9 and Bit DB8, in the control register.

Table 12 shows how the state of the bits corresponds to the mode of operation of the device. Any or all DACs (DAC H to DAC A) can be powered down to the selected mode by setting the corresponding eight bits (DB7 to DB0) to 1. See Table 13 for the contents of the input shift register during power-down/powerup operation.

When both bits are set to 0, the part works normally with its normal power consumption of 1.3 mA at 5 V. However, for the three power-down modes, the supply current falls to 0.4 µA at  $5 \text{ V} (0.2 \mu\text{A at } 3 \text{ V})$ . Not only does the supply current fall, but the output stage is also internally switched from the output of the amplifier to a resistor network of known values. This has the advantage that the output impedance of the part is known while the part is in power-down mode. There are three different options. The output is connected internally to GND through either a 1 k $\Omega$  or a 100 k $\Omega$  resistor, or it is left open-circuited (three-state). The output stage is illustrated in Figure 55.

Figure 55. Output Stage During Power-Down

#### Table 10. Internal Reference Register

| Internal REF Register (DB0) | Action                  |

|-----------------------------|-------------------------|

| 0                           | Reference off (default) |

| 1                           | Reference on            |

Table 11. 32-Bit Input Shift Register Contents for Reference Set-Up Command

MCR

| MSB  |          |              |      |       |                 |             |       |             | LSB                 |

|------|----------|--------------|------|-------|-----------------|-------------|-------|-------------|---------------------|

| DB23 | DB22     | DB21         | DB20 | DB19  | DB18            | DB17        | DB16  | DB15 to DB1 | DB0                 |

| 1    | 0        | 0            | 0    | Х     | Х               | Х           | Х     | Х           | 1/0                 |

| C    | ommand b | its (C3 to C | D)   | Addre | ess bits (A3 to | o A0)—don't | cares | Don't cares | Internal REF on/off |

AD5629R/AD5669R