## P-Channel Enhancement-Mode Vertical DMOS FETs

#### **Features**

- Free from secondary breakdown

- Low power drive requirement

- Ease of paralleling

- Low C<sub>ISS</sub> and fast switching speeds

- High input impedance and high gain

- Excellent thermal stability

- Integral source-to-drain diode

### **Applications**

- Motor controls

- Converters

- Amplifiers

- Switches

- Power supply circuits

- Drivers (relays, hammers, solenoids, lamps, memories, displays, bipolar transistors, etc.)

#### **General Description**

The Supertex VP0808 is an enhancement-mode (normallyoff) transistor that utilizes a vertical DMOS structure and Supertex's well-proven silicon-gate manufacturing process. This combination produces a device with the power handling capabilities of bipolar transistors, and the high input impedance and positive temperature coefficient inherent in MOS devices. Characteristic of all MOS structures, this device is free from thermal runaway and thermally-induced secondary breakdown.

Supertex's vertical DMOS FETs are ideally suited to a wide range of switching and amplifying applications where very low threshold voltage, high breakdown voltage, high input impedance, low input capacitance, and fast switching speeds are desired.

#### **Ordering Information**

| Device | Device TO-92 |     | R <sub>DS(ON)</sub><br>(max)<br>(Ω) | l <sub>D(ON)</sub><br>(min)<br>(A) |  |

|--------|--------------|-----|-------------------------------------|------------------------------------|--|

| VP0808 | VP0808L-G    | -80 | 5.0                                 | -1.1                               |  |

For packaged products, -G indicates package is RoHS compliant ('Green'). Consult factory for die / wafer form part numbers. Refer to Die Specification VF25 for layout and dimensions.

### **Absolute Maximum Ratings**

| Parameter                         | Value             |

|-----------------------------------|-------------------|

| Drain-to-source voltage           | BV <sub>DSS</sub> |

| Drain-to-gate voltage             | BV <sub>DGS</sub> |

| Gate-to-source voltage            | ±30V              |

| Operating and storage temperature | -55°C to +150°C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

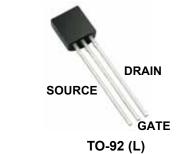

#### **Product Marking**

Package may or may not include the following marks: Si or 🎲

TO-92 (L)

## **Thermal Characteristics**

| Package | I <sub>D</sub><br>(continuous) <sup>†</sup><br>(mA) | I <sub>D</sub><br>(pulsed)<br>(A) | Power Dissipation<br>@T <sub>c</sub> = 25°C<br>(W) | <b>θ</b> <sub>jc</sub><br>(°C/W) | <b>θ</b> <sub>ja</sub><br>(°C/W) | I <sub>DR</sub> <sup>†</sup><br>(mA) | l <sub>DRM</sub><br>(mA) |

|---------|-----------------------------------------------------|-----------------------------------|----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------------|--------------------------|

| TO-92   | -280                                                | -3.0                              | 1.0                                                | 125                              | 170                              | -280                                 | -3.0                     |

Notes:

*†*  $I_{D}$  (continuous) is limited by max rated  $T_{i}$ .

#### Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise specified)

| Sym                 | Parameter                                  | Min  | Тур  | Max  | Units | Conditions                                                   |  |

|---------------------|--------------------------------------------|------|------|------|-------|--------------------------------------------------------------|--|

| BV <sub>DSS</sub>   | Drain-to-source breakdown voltage          | -80  | -    | -    | V     | V <sub>GS</sub> = 0V, Ι <sub>D</sub> = -10μΑ                 |  |

| V <sub>GS(th)</sub> | Gate threshold voltage                     | -1.0 | -    | -4.5 | V     | $V_{GS} = V_{DS}, I_{D} = -1.0 \text{mA}$                    |  |

| I <sub>GSS</sub>    | Gate body leakage current                  | -    | -    | -100 | nA    | $V_{GS} = \pm 20V, V_{DS} = 0V$                              |  |

|                     | Zero gate voltage drain current            |      | -    | -10  |       | $V_{GS}$ = 0V, $V_{DS}$ = Max Rating                         |  |

| I <sub>DSS</sub>    |                                            |      | -    | -500 | μA    | $V_{DS}$ = 0.8 Max Rating,<br>$V_{GS}$ = 0V, $T_{A}$ = 125°C |  |

| I <sub>D(ON)</sub>  | On-state drain current                     | -1.1 | -    | -    | А     | V <sub>GS</sub> = -10V, V <sub>DS</sub> = -15V               |  |

| R <sub>DS(ON)</sub> | Static drain-to-source on-state resistance | -    | -    | 5.0  | Ω     | V <sub>GS</sub> = -10V, I <sub>D</sub> = -1.0A               |  |

| G <sub>FS</sub>     | Forward transconductance                   | 200  | -    | -    | mmho  | V <sub>DS</sub> = -10V, I <sub>D</sub> = -500mA              |  |

| C <sub>ISS</sub>    | Input capacitance                          | -    | -    | 150  |       | $V_{GS} = 0V,$<br>$V_{DS} = -25V,$                           |  |

| C <sub>oss</sub>    | Common source output capacitance           | -    | -    | 60   | pF    |                                                              |  |

| C <sub>RSS</sub>    | Reverse transfer capacitance               | -    | -    | 25   |       | f = 1.0MHz                                                   |  |

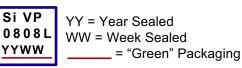

| t <sub>d(ON)</sub>  | Turn-on time                               | -    | -    | 15   |       | $V_{DD} = -25V,$                                             |  |

| t,                  | Rise time                                  | -    | -    | 40   | 20    |                                                              |  |

| t <sub>d(OFF)</sub> | Turn-off time                              |      | -    | 30   | ns    | $I_{D} = -500 \text{mA},$<br>$R_{GEN} = 25\Omega$            |  |

| t <sub>r</sub>      | Fall time                                  | -    | -    | 30   |       | GEN                                                          |  |

| V <sub>SD</sub>     | Diode forward voltage drop                 |      | -1.2 | -    | V     | V <sub>GS</sub> = 0V, I <sub>SD</sub> = -900mA               |  |

Notes:

1. All D.C. parameters 100% tested at 25°C unless otherwise stated. (Pulse test: 300µs pulse, 2% duty cycle.)

2. All A.C. parameters sample tested.

## **Switching Waveforms and Test Circuit**

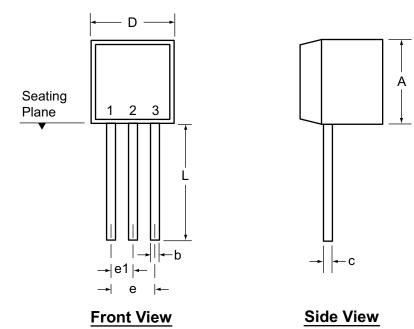

# 3-Lead TO-92 Package Outline (L)

Bottom View

| Symb                   | ol  | A    | b     | С     | D    | E    | E1   | е    | e1   | L     |

|------------------------|-----|------|-------|-------|------|------|------|------|------|-------|

|                        | MIN | .170 | .014† | .014† | .175 | .125 | .080 | .095 | .045 | .500  |

| Dimensions<br>(inches) | NOM | -    | -     | -     | -    | -    | -    | -    | -    | -     |

| (mones)                | MAX | .210 | .022† | .022† | .205 | .165 | .105 | .105 | .055 | .610* |

JEDEC Registration TO-92.

\* This dimension is not specified in the JEDEC drawing.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc.#: DSPD-3TO92N3, Version E041009.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2011 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.