# Si4702/03-C19

# BROADCAST FM RADIO TUNER FOR PORTABLE APPLICATIONS

### Features

- This data sheet applies to Si4702/03-C Firmware 19 and greater

- Worldwide FM band support (76–108 MHz)

- Digital low-IF receiver

- Frequency synthesizer with integrated VCO

- Seek tuning

- Automatic frequency control (AFC)

- Automatic gain control (AGC)

- Excellent overload immunity

- Signal strength measurement

- Programmable de-emphasis (50/75 µs)

### Applications

- Cellular handsets

- USB FM radioPDAs

- PDAS

Notebook PCs

- Adaptive noise suppression

- Volume control

- Line-level analog output

- 32.768 kHz reference clock

- 2-wire and 3-wire control interface

- 2.7 to 5.5 V supply voltage

- Integrated LDO regulator allows direct connection to battery

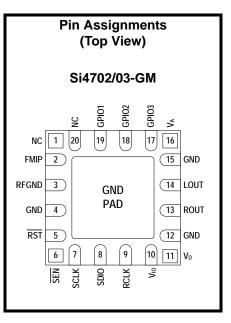

- 3 x 3 mm 20-pin QFN package

- Pb-free/RoHS compliant

- RDS/RBDS Processor (Si4703)

- Integrated crystal oscillator

- Portable navigation

- Consumer electronics

Portable radios

### Description

MP3 players

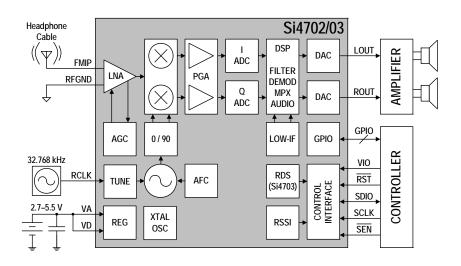

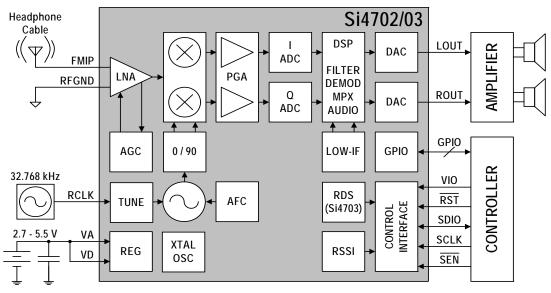

The Si4702/03 integrates the complete tuner function from antenna input to stereo audio output for FM broadcast radio reception.

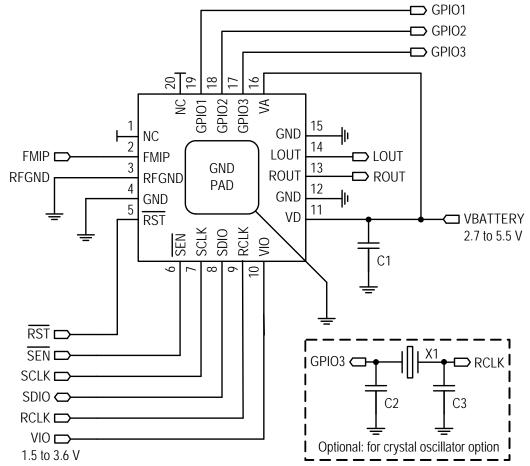

### **Functional Block Diagram**

U.S. and International Patents pending—Abbreviated U.S. Patent List:

7272375, 7127217, 7272373, 7272374, 7321324, 7339503, 7339504, 7355476, 7426376, 7436252, 7471940

# TABLE OF CONTENTS

# Section

## Page

| 1. Electrical Specifications         2. Typical Application Schematic         3. Bill of Materials | .14 |

|----------------------------------------------------------------------------------------------------|-----|

| 4. Functional Description                                                                          |     |

| 4.1. Overview                                                                                      | .15 |

| 4.2. FM Receiver                                                                                   |     |

| 4.3. General Purpose I/O Pins                                                                      | .16 |

| 4.4. RDS/RBDS Processor and Functionality                                                          | .16 |

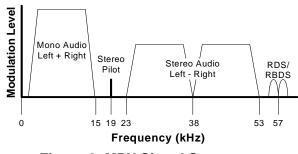

| 4.5. Stereo Audio Processing                                                                       |     |

| 4.6. Tuning                                                                                        |     |

| 4.7. Reference Clock                                                                               |     |

| 4.8. Control Interface                                                                             |     |

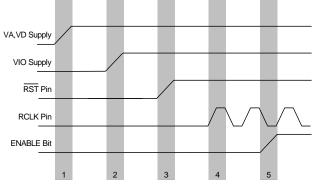

| 4.9. Reset, Powerup, and Powerdown                                                                 |     |

| 4.10. Audio Output Summation                                                                       |     |

| 4.11. Initialization Sequence                                                                      |     |

| 4.12. Programming Guide                                                                            |     |

| 5. Register Summary                                                                                |     |

| 6. Register Descriptions                                                                           |     |

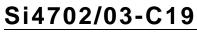

| 7. Pin Descriptions: Si4702/03-C19                                                                 |     |

| 8. Ordering Guide                                                                                  |     |

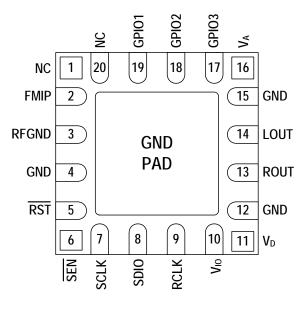

| 9. Package Markings (Top Marks)                                                                    |     |

| 9.1. Si4702 Top Mark                                                                               |     |

| 9.2. Si4703 Top Mark                                                                               |     |

| 9.3. Top Mark Explanation                                                                          |     |

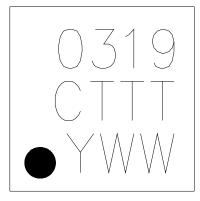

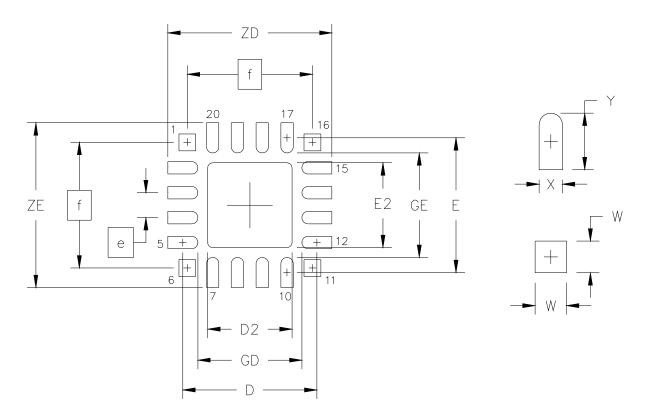

| 10. Package Outline: Si4702/03-C19                                                                 |     |

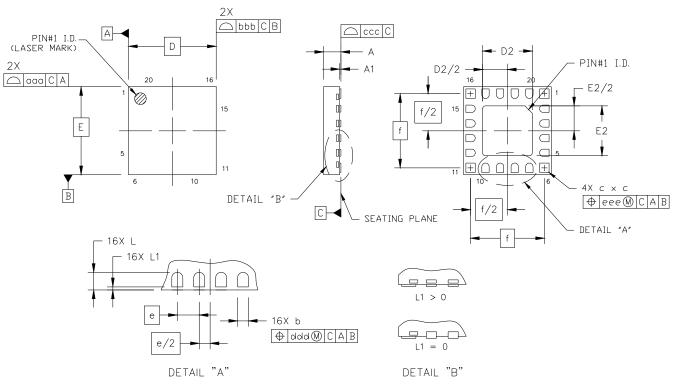

| 11. PCB Land Pattern: Si4702/03-C19                                                                |     |

| Additional Reference Resources                                                                     | -   |

| Document Change List                                                                               |     |

|                                                                                                    | .40 |

## **1. Electrical Specifications**

### Table 1. Recommended Operating Conditions

| Parameter                                                                                                                   | Symbol              | Test Condition | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| Digital Supply Voltage                                                                                                      | V <sub>D</sub>      |                | 2.7 | —   | 5.5 | V    |

| Analog Supply Voltage                                                                                                       | V <sub>A</sub>      |                | 2.7 |     | 5.5 | V    |

| Interface Supply Voltage                                                                                                    | V <sub>IO</sub>     |                | 1.5 |     | 3.6 | V    |

| Digital Power Supply Power-Up<br>Rise Time                                                                                  | V <sub>DRISE</sub>  |                | 10  |     | _   | μs   |

| Analog Power Supply Power-Up<br>Rise Time                                                                                   | V <sub>ARISE</sub>  |                | 10  | —   | —   | μs   |

| Interface Power Supply Power-Up<br>Rise Time                                                                                | V <sub>IORISE</sub> |                | 10  |     |     | μs   |

| Ambient Temperature                                                                                                         | T <sub>A</sub>      |                | -20 | 25  | 85  | °C   |

| <b>Note:</b> All minimum and maximum spec<br>Typical values apply at V <sub>D</sub> = V <sub>A</sub> =<br>otherwise stated. |                     |                |     |     |     |      |

## Table 2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                   | Symbol           | Value                           | Unit            |

|-----------------------------|------------------|---------------------------------|-----------------|

| Digital Supply Voltage      | VD               | -0.5 to 5.8                     | V               |

| Analog Supply Voltage       | V <sub>A</sub>   | -0.5 to 5.8                     | V               |

| Interface Supply Voltage    | V <sub>IO</sub>  | -0.5 to 3.9                     | V               |

| Input Current <sup>3</sup>  | I <sub>IN</sub>  | ±10                             | mA              |

| Input Voltage <sup>3</sup>  | V <sub>IN</sub>  | –0.3 to (V <sub>IO</sub> + 0.3) | V               |

| Operating Temperature       | T <sub>OP</sub>  | -40 to 95                       | °C              |

| Storage Temperature         | T <sub>STG</sub> | -55 to 150                      | °C              |

| RF Input Level <sup>4</sup> |                  | 0.4                             | V <sub>pK</sub> |

Notes:

4

1. Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

2. The Si4702/03-C19 device is a high-performance RF integrated circuit with an ESD rating of < 2 kV HBM. Handling and assembly of this device should only be done at ESD-protected workstations.

**3.** For input pins SCLK,  $\overline{SEN}$ , SDIO,  $\overline{RST}$ , RCLK, GPIO1, GPIO2, and GPIO3.

4. At RF input pins.

### Table 3. DC Characteristics<sup>1</sup>

(V\_D = V\_A = 2.7 to 3.6 V, V\_{IO} = 1.5 to 3.6 V, T\_A = -20 to 85 °C)

| Parameter                                            | Symbol            | Test Condition                                    | Min                   | Тур  | Max                   | Unit |

|------------------------------------------------------|-------------------|---------------------------------------------------|-----------------------|------|-----------------------|------|

| Analog Operating Supply Current <sup>2</sup>         | I <sub>A</sub>    | ENABLE = 1                                        | —                     | 10.8 | —                     | mA   |

| Digital Operating Supply Current <sup>2</sup>        | I <sub>D</sub>    | ENABLE = 1                                        | —                     | 3.3  | —                     | mA   |

| Interface Operating Supply<br>Current <sup>2</sup>   | I <sub>IO</sub>   | ENABLE = 1                                        | —                     | 0.3  |                       | mA   |

| Total Operating Supply<br>Current <sup>2,3,4,5</sup> | I <sub>OP</sub>   | ENABLE = 1<br>Low SNR signal                      | —                     | 15.3 | 16.8                  | mA   |

| Total Operating Supply<br>Current <sup>2,3,4</sup>   | I <sub>OP</sub>   | ENABLE = 1                                        | —                     | 14.4 | 15.9                  | mA   |

| Total Operating Supply<br>Current <sup>2,3,4,6</sup> | I <sub>OP</sub>   | ENABLE = 1<br>RDS = 1                             | —                     | 14.9 | 16.4                  | mA   |

| Total Operating Supply<br>Current <sup>2,3,4,6</sup> | I <sub>OP</sub>   | ENABLE = 1<br>RDS = 1,<br>Low SNR signal          | —                     | 15.8 | 16.8                  | mA   |

| Analog Powerdown Supply Current <sup>2,7</sup>       | I <sub>APD</sub>  | ENABLE = 0                                        | _                     | 3.5  | —                     | μA   |

| Digital Powerdown Supply Current <sup>2,7</sup>      | I <sub>DPD</sub>  | ENABLE = 0                                        | _                     | 2.5  | —                     | μA   |

| Interface Powerdown Supply<br>Current <sup>2,7</sup> | I <sub>IOPD</sub> | ENABLE = 0<br>SCLK, RCLK inactive                 | —                     | 2.5  |                       | μA   |

| Total Powerdown Supply Current <sup>2,7</sup>        | I <sub>PD</sub>   | ENABLE = 0                                        | —                     | 8.5  | 12.0                  | μA   |

| High Level Input Voltage <sup>8</sup>                | V <sub>IH</sub>   |                                                   | 0.7 x V <sub>IO</sub> |      | V <sub>IO</sub> + 0.3 | V    |

| Low Level Input Voltage <sup>8</sup>                 | V <sub>IL</sub>   |                                                   | -0.3                  |      | 0.3 x V <sub>IO</sub> | V    |

| High Level Input Current <sup>8</sup>                | I <sub>IH</sub>   | V <sub>IN</sub> = V <sub>IO</sub> = 3.6 V         | -10                   |      | 10                    | μA   |

| Low Level Input Current <sup>8</sup>                 | IIL               | V <sub>IN</sub> = 0 V,<br>V <sub>IO</sub> = 3.6 V | -10                   | _    | 10                    | μA   |

| High Level Output Voltage <sup>9</sup>               | V <sub>OH</sub>   | I <sub>OUT</sub> = 500 μA                         | 0.8 x V <sub>IO</sub> |      | —                     | V    |

| Low Level Output Voltage <sup>9</sup>                | V <sub>OL</sub>   | I <sub>OUT</sub> = -500 μA                        |                       |      | 0.2 x V <sub>IO</sub> | V    |

#### Notes:

1. All specifications for the Si4702 unless otherwise noted.

2. Refer to Register 02h, "Power Configuration" on page 24 for ENABLE bit description.

3. The LNA is automatically switched to higher current mode for optimum sensitivity in low SNR conditions.

4. Analog and digital supply currents are simultaneously adjusted based on SNR level.

5. Stereo and RDS functionality are disabled at low SNR levels.

6. RDS functionality only available for Si4703.

Refer to Section 4.9. "Reset, Powerup, and Powerdown" on page 19.

For input pins SCLK, SEN, SDIO, RST, RCLK, GPIO1, GPIO2, and GPIO3.

9. For output pins SDIO, GPIO1, GPIO2, and GPIO3.

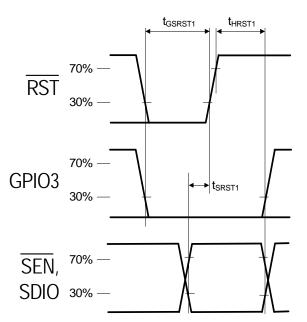

| Parameter                               | Symbol                | Test Condition | Min | Тур | Max | Unit |

|-----------------------------------------|-----------------------|----------------|-----|-----|-----|------|

| RST pulse width and GPIO3 Setup to RST↑ | t <sub>GSRST1</sub> 4 | GPIO3 = 0      | 100 |     |     | μs   |

| SEN and SDIO Setup to $\overline{RST}$  | t <sub>SRST1</sub>    |                | 30  | —   | —   | ns   |

| SEN, SDIO, and GPIO3 Hold from<br>RST↑  | t <sub>HRST1</sub>    |                | 30  |     |     | ns   |

### Table 4. Reset Timing Characteristics (Busmode Select Method 1)<sup>1,2,3</sup>

#### Notes:

1. When selecting 2-wire Mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

2. When selecting 3-wire Mode, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

3. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the 1st start condition.

4. If GPIO3 is driven low by the user, then minimum t<sub>GSRST1</sub> is only 30 ns. If <u>GPIO3</u> is hi-Z, then minimum t<sub>GSRST1</sub> is 100 µs, to provide time for an on-chip 1 M $\Omega$  pulldown device (active while  $\overrightarrow{RST}$  is low) to discharge the pin.

Figure 1. Reset Timing Parameters for Busmode Select Method 1 (GPIO3 = 0)

6

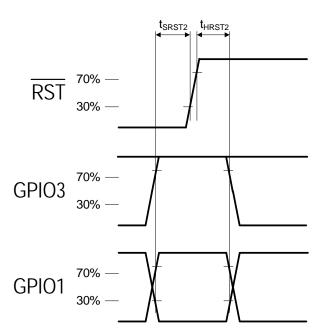

| Table 5. Reset Timing Characteristics (B | Busmode Select Method 2) <sup>1,2,3</sup> |

|------------------------------------------|-------------------------------------------|

|------------------------------------------|-------------------------------------------|

| Parameter                                 | Symbol             | Test Condition | Min | Тур | Max | Unit |

|-------------------------------------------|--------------------|----------------|-----|-----|-----|------|

| GPIO1 and GPIO3 Setup to $\overline{RST}$ | t <sub>SRST2</sub> | GPIO3 = 1      | 30  |     | _   | ns   |

| GPIO1 and GPIO3 Hold from RST↑            | t <sub>HRST2</sub> |                | 30  | _   | _   | ns   |

Notes:

1. When selecting 2-wire Mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

2. When selecting 3-wire Mode, the user must ensure that a rising edge of SCLK does not occur within 300 ns before the rising edge of RST.

3. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of RST, and stays high until after the 1st start condition.

Figure 2. Reset Timing Parameters for Busmode Select Method 2 (GPIO3 = 1)

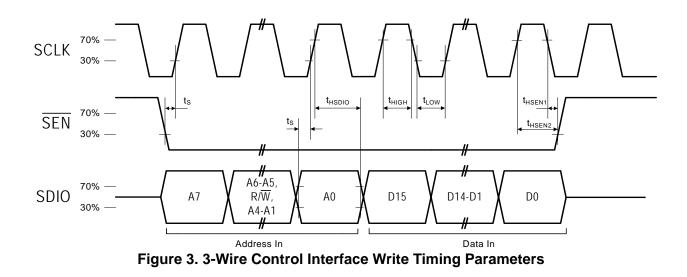

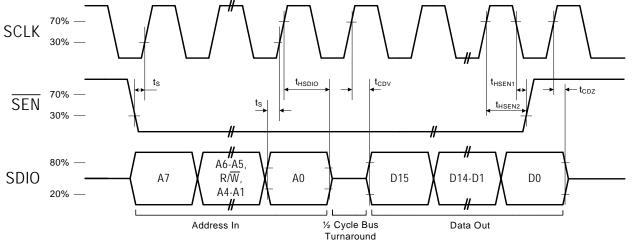

### **Table 6. 3-Wire Control Interface Characteristics**

$(V_D = V_A = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 \text{ °C})$

| Parameter                               | Symbol             | Test Condition               | Min        | Тур          | Max         | Unit       |

|-----------------------------------------|--------------------|------------------------------|------------|--------------|-------------|------------|

| SCLK Frequency                          | f <sub>CLK</sub>   |                              | 0          | —            | 2.5         | MHz        |

| SCLK High Time                          | t <sub>HIGH</sub>  |                              | 25         | —            | _           | ns         |

| SCLK Low Time                           | t <sub>LOW</sub>   |                              | 25         | —            | —           | ns         |

| SDIO Input, SEN to SCLK↑ Setup          | t <sub>S</sub>     |                              | 20         | —            | _           | ns         |

| SDIO Input to SCLK↑ Hold                | t <sub>HSDIO</sub> |                              | 10         | —            | —           | ns         |

| SEN Input to SCLK↓ Hold                 | t <sub>HSEN1</sub> |                              | 10         | —            | —           | ns         |

| SEN Input to SCLK↑ Hold                 | t <sub>HSEN2</sub> |                              | 10         | —            | _           | ns         |

| SCLK↑ to SDIO Output Valid              | t <sub>CDV</sub>   | Read                         | 2          | —            | 25          | ns         |

| SCLK <sup>↑</sup> to SDIO Output High Z | t <sub>CDZ</sub>   | Read                         | 2          | —            | 25          | ns         |

| Note: When selecting 3-wire Mode, the   | user must ens      | sure that a rising edge of S | CLK does r | not occur wi | thin 300 ns | before the |

rising edge of RST.

Figure 4. 3-Wire Control Interface Read Timing Parameters

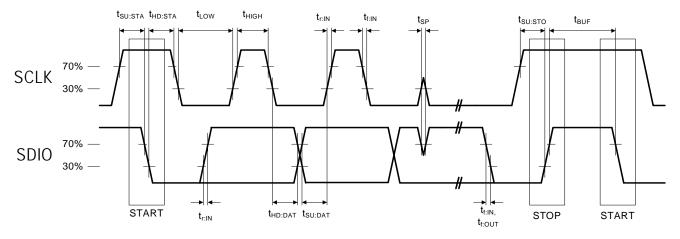

### Table 7. 2-Wire Control Interface Characteristics<sup>1,2,3</sup>

(V<sub>D</sub> = V<sub>A</sub> = 2.7 to 5.5 V, V<sub>IO</sub> = 1.5 to 3.6 V, T<sub>A</sub> = -20 to 85 °C)

| Parameter                                           | Symbol                                 | Test Condition | Min                     | Тур | Max | Unit |

|-----------------------------------------------------|----------------------------------------|----------------|-------------------------|-----|-----|------|

| SCLK Frequency                                      | f <sub>SCL</sub>                       |                | 0                       |     | 400 | kHz  |

| SCLK Low Time                                       | t <sub>LOW</sub>                       |                | 1.3                     |     | —   | μs   |

| SCLK High Time                                      | t <sub>HIGH</sub>                      |                | 0.6                     |     | —   | μs   |

| SCLK Input to SDIO↓ Setup<br>(START)                | t <sub>SU:STA</sub>                    |                | 0.6                     | —   | —   | μs   |

| SCLK Input to SDIO $\downarrow$ Hold (START)        | t <sub>HD:STA</sub>                    |                | 0.6                     |     | —   | μs   |

| SDIO Input to SCLK <sup>↑</sup> Setup               | t <sub>SU:DAT</sub>                    |                | 100                     |     | —   | ns   |

| SDIO Input to SCLK $\downarrow$ Hold <sup>4,5</sup> | t <sub>HD:DAT</sub>                    |                | 0                       |     | 900 | ns   |

| SCLK input to SDIO <sup>↑</sup> Setup (STOP)        | t <sub>SU:STO</sub>                    |                | 0.6                     |     | —   | μs   |

| STOP to START Time                                  | t <sub>BUF</sub>                       |                | 1.3                     |     | _   | μs   |

| SDIO Output Fall Time                               | t <sub>f:OUT</sub>                     |                | 20 + 0.1 C <sub>b</sub> |     | 250 | ns   |

| SDIO Input, SCLK Rise/Fall Time                     | t <sub>f:IN</sub><br>t <sub>r:IN</sub> |                | 20 + 0.1 C <sub>b</sub> | _   | 300 | ns   |

| SCLK, SDIO Capacitive Loading                       | Cb                                     |                | —                       |     | 50  | pF   |

| Input Filter Pulse Suppression                      | t <sub>SP</sub>                        |                | —                       | _   | 50  | ns   |

Notes:

1. When  $V_{IO} = 0$  V, SCLK and SDIO are low impedance.

2. When selecting 2-wire mode, the user must ensure that SCLK is high during the rising edge of  $\overline{RST}$ , and stays high until after the 1st start condition.

3. When selecting 2-wire mode, the user must ensure that a 2-wire start condition (falling edge of SDIO while SCLK is high) does not occur within 300 ns before the rising edge of RST.

As a 2-wire transmitter, the Si4702/03-C19 delays SDIO by a minimum of 300 ns from the V<sub>IH</sub> threshold of SCLK to comply with the 0 ns t<sub>HD:DAT</sub> specification.

The maximum t<sub>HD:DAT</sub> has only to be met when f<sub>SCL</sub> = 400 kHz. At frequencies below 400 KHz, t<sub>HD:DAT</sub> may be violated so long as all other timing parameters are met.

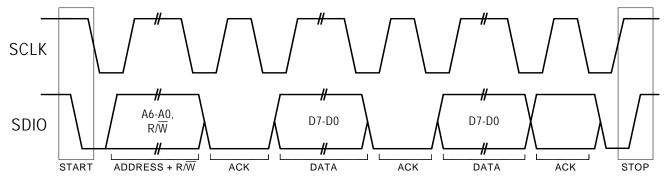

Figure 5. 2-Wire Control Interface Read and Write Timing Parameters

Figure 6. 2-Wire Control Interface Read and Write Timing Diagram

### Table 8. FM Receiver Characteristics<sup>1,2</sup>

$(V_D = V_A = 2.7 \text{ to } 5.5 \text{ V}, V_{IO} = 1.5 \text{ to } 3.6 \text{ V}, T_A = -20 \text{ to } 85 \text{ °C})$

| Symbol          | Test Condition                               | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Тур    | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Unit                                                    |

|-----------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| f <sub>RF</sub> |                                              | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _      | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MHz                                                     |

|                 | (S+N)/N = 26 dB                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.7    | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | μVEMF                                                   |

|                 | (S+N)/N = 26  dB                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | μVEMF                                                   |

|                 | $\Delta f = 2 \text{ kHz},$<br>RDS BLER < 5% | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | μVEMF                                                   |

|                 |                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | kΩ                                                      |

|                 |                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | pF                                                      |

|                 |                                              | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dBµVEMF                                                 |

|                 | m = 0.3                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | dB                                                      |

|                 | ±200 kHz                                     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dB                                                      |

|                 | ±400 kHz                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | dB                                                      |