# DESCRIPTION

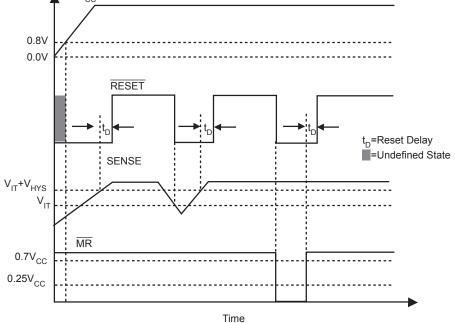

The MP6400 family is the microprocessor ( $\mu$ P) supervisory circuit which can monitor and provide reset function for system voltages from 0.4V. When either the SENSE voltage falls below its threshold (V<sub>IT</sub>) or the voltage of manual reset (MR) is pulled to a logic low, the RESET signal will be asserted. The reset voltage can be factory-set for standard voltage rails from 0.9V to 5V, while the MP6400DG(J)-01 reset voltage is adjustable with an external resistor divider. When SENSE voltage and MR exceed their thresholds, RESET is driven to a logic high after a user-programmable delay time.

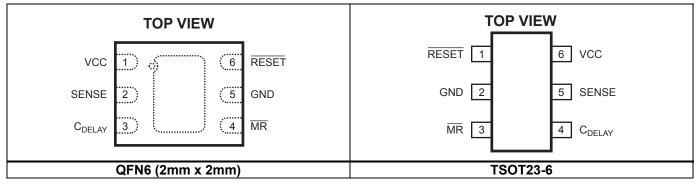

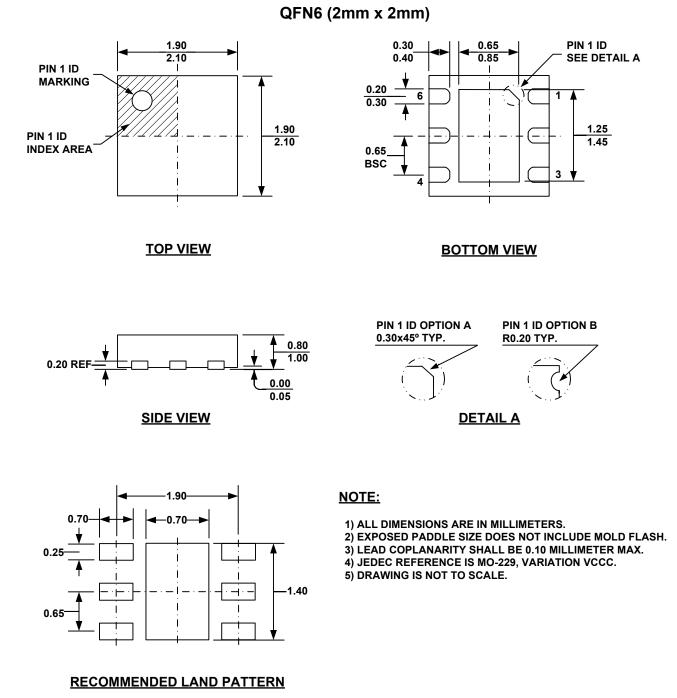

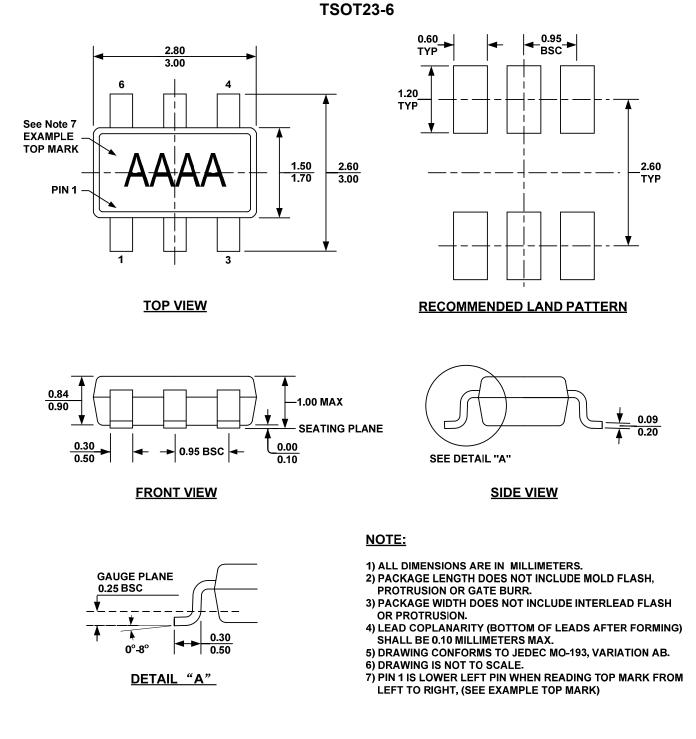

The MP6400 has a very low quiescent current of 1.6µA typically, which makes it ideal suitable for battery-powered applications. It provides a precision reference to achieve  $\pm 1\%$  threshold accuracy. The reset delay time can be selected by a capacitor which is connected between  $C_{DELAY}$  and GND, allowing the user to select any delay time from 2.1ms to 10s. 380ms delay time is selected by connecting the  $C_{DELAY}$  pin to  $V_{CC}$ , while 24ms delay time by leaving the  $C_{DELAY}$  pin float. MP6400 is available in TSOT23 and 2mm×2mm 6-pin QFN packages.

#### **FEATURES**

- Fixed Threshold Voltages for Standard Voltage Rails From 0.9V to 5V and Adjustable Voltage From 0.4V are Available

- Low Quiescent Current: 1.6uA typ

- Power-On Reset Generator with Adjustable Delay Time: 2.1ms to 10s

- High Threshold Accuracy: ±1% typ

- Manual Reset (MR) Input

- Open-Drain RESET Output

- Immune to Short Negative SENSE voltage

- Guaranteed Reset Valid to V<sub>CC</sub>=0.8V

- 6 Pin TSOT23 and 2mm×2mm QFN

## **APPLICATIONS**

- DSP or Micro controller Applications

- Laptop/Desktop Computers

- PDAs/Hand-Held Products

- Portable/Battery-Powered Products

- FPGA/ASIC Applications

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

#### **ORDERING INFORMATION**

| Part Number* | Package      | Free Air Temperature (T <sub>A</sub> ) |

|--------------|--------------|----------------------------------------|

| MP6400DG-XX  | QFN6 (2x2mm) |                                        |

| MP6400DJ-XX  | TSOT23-6     | –40°C to +85°C                         |

\*For Tape & Reel, add suffix -Z (e.g. MP6400DG-XX-Z);

For RoHS compliant packaging, add suffix –LF (e.g. MP6400DG–XX-LF–Z).

\*\*For Tape & Reel, add suffix –Z (e.g. MP6400DJ–XX-Z);

For RoHS compliant packaging, add suffix -LF(e.g. MP6400DJ-XX-LF-Z).

## PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>CC</sub> 0.3 to 6.5 V C <sub>DELAY</sub> Voltage V <sub>CDELAY</sub> 0.3V to V <sub>CC</sub> + 0.3V |

|---------------------------------------------------------------------------------------------------------------------------|

| SENSE Voltage V <sub>SENSE</sub>                                                                                          |

| All Other Pins–0.3V to +6.5V<br>RESET Current I <sub>RESET</sub>                                                          |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$                                                                 |

| QFN6 ( $2mmx2mm$ )                                                                                                        |

| TSOT23-60.57W                                                                                                             |

| Junction Temperature150°C                                                                                                 |

| Lead Temperature260°C                                                                                                     |

| Storage Temperature –65°C to +150°C                                                                                       |

# Recommended Operating Conditions <sup>(3)</sup>

| Thermal Resistance <sup>(4)</sup> | $\boldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}_{JC}$ |       |

|-----------------------------------|---------------------------|----------------------------|-------|

| QFN6 (2mmx2mm)                    | 50                        | 12                         | .°C/W |

| TSOT23-6                          | 220                       | 110.                       | .°C/W |

Notes:

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

<sup>1)</sup> Exceeding these ratings may damage the device.

<sup>2)</sup> The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

# **ELECTRICAL CHARACTERISTICS**

1.8V≤V<sub>CC</sub>≤6V, R<sub>3</sub> = 100kΩ, C<sub>3</sub> = 47pF, T<sub>A</sub>= -40°C to +85°C, Typical values are at T<sub>A</sub>=+25°C, unless otherwise noted.

| Parameters                                       | Symbol              | Condition                                                                                                                     | Min         | Тур  | Max          | Units             |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|------|--------------|-------------------|

| Input Supply Range                               | V <sub>CC</sub>     |                                                                                                                               | 1.8         |      | 6            | V                 |

| Supply Current                                   | I <sub>CC</sub>     | $V_{CC}$ = 3.3V, RESET not<br>asserted. MR, RESET,<br>$C_{DELAY}$ open                                                        |             | 1.6  | 3.5          | μA                |

| (current into V <sub>CC</sub> pin)               | ICC                 | $V_{CC} = 6V, \overline{RESET} \text{ not}$<br>asserted.MR, RESET,<br>$C_{DELAY}$ open                                        |             | 1.85 | 12           | μA                |

| Low-level Output Voltage                         | V <sub>OL</sub>     | $\begin{array}{l} 1.3 \text{V} \leq \text{V}_{\text{CC}} < 1.8 \text{V}, \\ \text{I}_{\text{OL}} = 0.4 \text{mA} \end{array}$ |             |      | 0.3          | V                 |

|                                                  | ŬĹ.                 | $1.8V \le V_{CC} \le 6V,$<br>$I_{OL} = 1.0mA$                                                                                 |             |      | 0.4          | V                 |

| Power-up Reset Voltage <sup>(5)</sup>            |                     | V <sub>OL</sub> (max) = 0.2V,<br>I <sub>RESET</sub> =15uA<br>T <sub>rise(Vcc)</sub> ≥15µs/V                                   |             |      | 0.8          | V                 |

| Negative-going Input Threshold<br>Accuracy       | V <sub>IT</sub>     | V <sub>SENSE</sub> falling slowly                                                                                             |             | ±1.0 | ±2.0         | %                 |

| Hysteresis on $V_{IT}$ Pin                       | $V_{\text{HYS}}$    |                                                                                                                               |             | 1.5  | 3.5          | V <sub>IT</sub> % |

| MR Internal Pull-up Resistance                   | $R_{\overline{MR}}$ |                                                                                                                               | 50          | 110  |              | kΩ                |

| Input Current at SENSE Pin                       | I <sub>SENSE</sub>  | MP6400DJ-01<br>V <sub>SENSE</sub> = V <sub>IT</sub>                                                                           | -25         |      | +25          | nA                |

|                                                  | ISENSE              | Fixed versions<br>V <sub>SENSE</sub> = 6V                                                                                     |             | 2.4  |              | μA                |

| RESET Leakage Current                            |                     | $V_{\overline{\text{RESET}}}$ = 6V, $\overline{\text{RESET}}$ not asserted                                                    |             |      | 300          | nA                |

| MR Logic Low Input                               | V <sub>IL</sub>     |                                                                                                                               |             |      | $0.25V_{CC}$ | V                 |

| MR Logic High Input                              | V <sub>IH</sub>     |                                                                                                                               | $0.7V_{CC}$ |      |              | V                 |

| SENSE Maximum Transient<br>Duration              | t <sub>w</sub>      | $V_{IH} = 1.05 V_{IT},$<br>$V_{IL} = 0.95 V_{IT}$                                                                             |             | 17.5 |              | μs                |

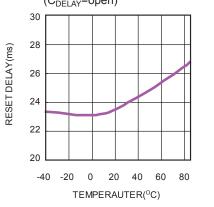

|                                                  |                     | C <sub>DELAY</sub> = Open                                                                                                     | 15          | 24   | 34           | ms                |

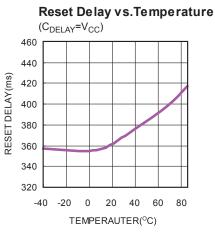

|                                                  | t <sub>d</sub>      | $C_{DELAY} = V_{CC}^{(6)}$                                                                                                    | 230         | 380  | 530          | ms                |

| RESET Delay Time                                 |                     | C <sub>DELAY</sub> = 150pF                                                                                                    | 1.3         | 2.1  | 3            | ms                |

|                                                  |                     | $C_{\text{DELAY}} = 10 \text{nF}^{(6)}$                                                                                       | 61          | 102  | 142          | ms                |

| MR to RESET Propagation Delay                    | t <sub>pHL1</sub>   | $V_{\text{IH}} = 0.7 V_{\text{CC}},$<br>$V_{\text{IL}} = 0.25 V_{\text{CC}}$                                                  |             | 160  |              | ns                |

| High to Low Level RESET Delay,<br>SENSE to RESET | $t_{\rm pHL2}$      |                                                                                                                               |             | 17.5 |              | μs                |

Note:

5) The lowest supply voltage ( $V_{CC}$ ) at which  $\overline{RESET}$  becomes active.

6) Guaranteed by design.

MP6400 Rev. 0.91 12/16/2009

| Product      | Package | Top Mark        | Nominal Supply Voltage | Threshold Voltage (VIT) |  |  |

|--------------|---------|-----------------|------------------------|-------------------------|--|--|

| MP6400DG-01  | QFN     | 5B              | Adjustable             | 0.4V                    |  |  |

| MP6400DJ-01  | TSOT23  | 4B              | Adjustable             | 0.4 v                   |  |  |

| MP6400DG-09  | QFN     | Contact Factory | 0.9V                   | 0.84V                   |  |  |

| MP6400DJ-09  | TSOT23  | " "             | 0.90                   | 0.04 v                  |  |  |

| MP6400DG-12  | QFN     | " "             | 1.2V                   | 1 12)/                  |  |  |

| MP6400DJ-12  | TSOT23  | " "             | 1.2 v                  | 1.12V                   |  |  |

| MP6400DG-125 | QFN     | " "             | 1.25V                  | 1.16V                   |  |  |

| MP6400DJ-125 | TSOT23  | " "             | 1.23 V                 | 1.16V                   |  |  |

| MP6400DG-15  | QFN     | " "             | 1 5)/                  | 1.40V                   |  |  |

| MP6400DJ-15  | TSOT23  | " "             | 1.5V                   | 1.40 V                  |  |  |

| MP6400DG-18  | QFN     | " "             | 1.8V                   | 1.67V                   |  |  |

| MP6400DJ-18  | TSOT23  | " "             | 1.8V                   | 1.07 V                  |  |  |

| MP6400DG-25  | QFN     | " "             | 2.5V                   | 2.33V                   |  |  |

| MP6400DJ-25  | TSOT23  | ** **           | 2.5V                   | 2.33V                   |  |  |

| MP6400DG-30  | QFN     | 9S              | 3.0V                   | 2.79V                   |  |  |

| MP6400DJ-30  | TSOT23  | 8S              | 5.0 v                  | 2.790                   |  |  |

| MP6400DG-33  | QFN     | 9R              | 2.2)/                  | 2.07\/                  |  |  |

| MP6400DJ-33  | TSOT23  | 3S              | 3.3V                   | 3.07V                   |  |  |

| MP6400DG-50  | QFN     | Contact Factory | E 0)/ 4 (E)/           |                         |  |  |

| MP6400DJ-50  | TSOT23  | " "             | 5.0V                   | 4.65V                   |  |  |

# ORDERING INFORMATION (7)

Note:

7) In "MP6400DG(J)- \_\_", the "\_\_" are placeholders for the monitored voltage levels of the devices. Desired monitored voltages are set by the suffix found in ordering information.

#### **PIN FUNCTIONS**

| QFN<br>Pin # | TSOT<br>Pin # | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|---------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6            | 1             | RESET              | $\overline{\text{RESET}}$ is an open drain signal which will be asserted when the SENSE voltage drops below a preset threshold or when the manual reset ( $\overline{\text{MR}}$ ) pin drops to a logic low. The $\overline{\text{RESET}}$ delay time is programmable from 2.1ms to 10s by using external capacitors. A pull-up resistor bigger than 10k should be connected this pin to supply line, and the $\overline{\text{RESET}}$ outputting a higher voltage than V <sub>CC</sub> is allowable. |

| 5            | 2             | GND                | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4            | 3             | MR                 | The manual reset ( $\overline{\text{MR}}$ ) can introduce another logic signal to control the $\overline{\text{RESET}}$ . It is internally connected to V <sub>CC</sub> through a 90k $\Omega$ resistor.                                                                                                                                                                                                                                                                                               |

| 3            | 4             | C <sub>DELAY</sub> | Programmable reset delay time pin. When $C_{\text{DELAY}}$ connected to $V_{\text{CC}}$ through a resistor between $50 k\Omega$ and $200 k\Omega$ , a 380ms delay time is selected. When $C_{\text{DELAY}}$ floated, the delay time is 24ms. A capacitor bigger than 150pF connected $C_{\text{DELAY}}$ to GND could be used to get the user's programmable time from 2.1ms to 10s.                                                                                                                    |

| 2            | 5             | SENSE              | SENSE pin is connected to the monitored system voltage. When the monitored voltage is below desired threshold, $\overline{\text{RESET}}$ is asserted.                                                                                                                                                                                                                                                                                                                                                  |

| 1            | 6             | V <sub>cc</sub>    | Supply voltage. A 0.1uF decoupling ceramic capacitor should be put close to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **DETAIL DESCRIPTION**

The MP6400 product family asserts a  $\overline{\text{RESET}}$  signal when either the SENSE pin voltage is lower than V<sub>IT</sub> or the manual reset ( $\overline{\text{MR}}$ ) is driven low. The MP6400 family can be monitored a fixed voltage from 0.9V to 5.0V, while the MP6400DG(J)-01 can monitor any voltage above 0.4V by adjusting the external resistor divider. After both the manual reset ( $\overline{\text{MR}}$ ) and SENSE voltages exceed their thresholds, the RESET

output remains asserted for a user's programmable delay time. Two fixed  $_{RESET}$  delay times are user-selectable: 380ms delay time by connecting the  $C_{DELAY}$  pin to  $V_{CC}$ , and 24ms delay time by leaving the  $C_{DELAY}$  pin float. Any delay time from 2.1ms to 10s could be gotten by connecting a capacitor between  $C_{DELAY}$  and GND. The wide monitor voltage and programmable reset delay time make MP6400 product family suitable for a broad array of applications.

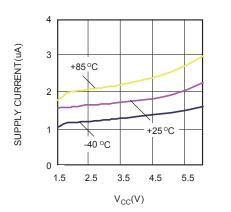

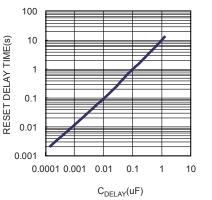

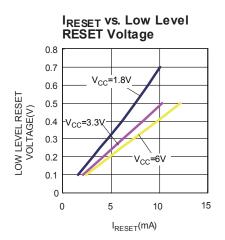

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC}$ =3.3V, R<sub>3</sub> = 100k $\Omega$ , C<sub>3</sub> = 47pF, T<sub>A</sub>= -40°C to +85°C, Typical values are at T<sub>A</sub>=+25°C, unless otherwise noted.

Reset Delay Time vs. CDELAY

Supply Current vs.  $V_{\mbox{CC}}$

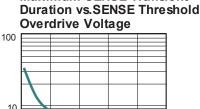

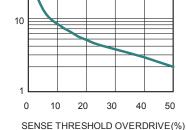

Maximum SENSE Transient

MAXIMUM SENSE TRANSIENT DURATION(us)

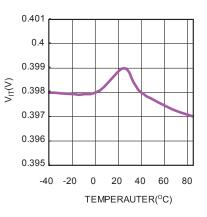

Reset Delay vs.Temperature (C<sub>DELAY</sub>=open)

VIT vs. Temperature

MP6400 Rev. 0.91 12/16/2009

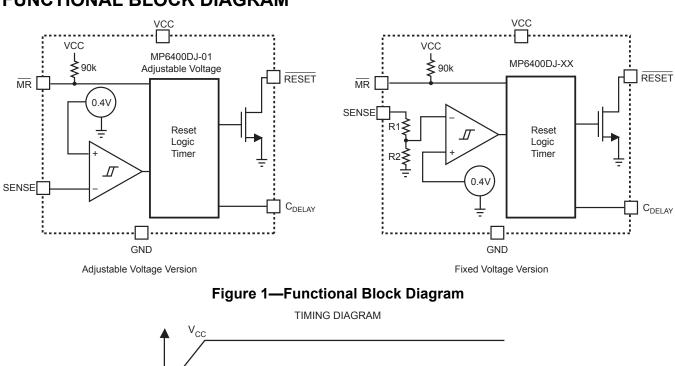

# FUNCTIONAL BLOCK DIAGRAM

| MR | SENSE > V <sub>IT</sub> | RESET |

|----|-------------------------|-------|

| L  | 0                       | L     |

| L  | 1                       | L     |

| Н  | 0                       | L     |

| Н  | 1                       | Н     |

####

MP6400 Rev. 0.91 12/16/2009

## **APPLICATION INFORMATION**

#### **Reset Output Function**

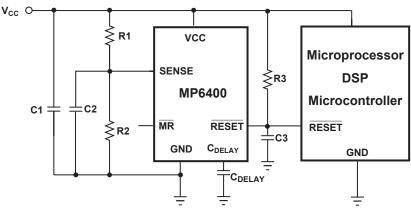

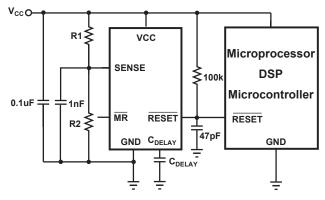

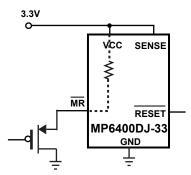

The MP6400  $\overline{\text{RESET}}$  output is typically connected to the  $\overline{\text{RESET}}$  input of a microprocessor, as shown in Figure 3. When  $\overline{\text{RESET}}$  is not asserted, a pull up resistor must be connected to hold this signal high. The voltage of reset signal is allowed to be higher than V<sub>CC</sub> (up to 6V) through a resistor pulling up from supply line. If the voltage is below 0.8V,  $\overline{\text{RESET}}$  output is undefined. This condition can be ignored generally because that most microprocessors do not function at this state. When both SENSE and MR are higher than their threshold voltage,  $\overline{\text{RESET}}$  output holds logic high. Once either of the two drops below their threshold,  $\overline{\text{RESET}}$  will be asserted.

Figure 3—Typical Application of MP6400 with Microprocessor

From the point that  $\overline{\text{MR}}$  is again logic high and SENSE is above  $V_{\text{IT}} + V_{\text{HYS}}$  (the threshold hysteresis),  $\overline{\text{RESET}}$  will be driven to a logic high after a reset delay time. The reset delay time is programmable by  $C_{\text{DELAY}}$  pin. Due to the finite impedance of  $\overline{\text{RESET}}$  pin, the pull up resistor should be bigger than  $10k\Omega$ .

#### Monitor a Voltage

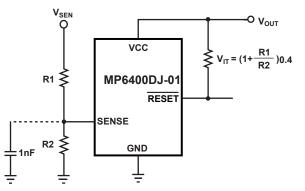

The SENSE input pin is connected to the monitored system voltage directly or through a resistor network (on MP6400DJ-01). When the voltage on the pin is below  $V_{IT}$ ,  $\overline{RESET}$  is asserted. A threshold hysteresis will prevent the chip from responding perturbation on SENSE pin. A 1nF to 10nF bypass capacitor should be put on this pin to increase its immunity to noise. A typical application of the MP6400DJ-01 is shown in Figure 4. Two external resistors form a voltage divider from monitored voltage to GND. Its tap

connects to the SENSE pin. The circuit can be used to monitor any voltage higher than 0.4V.

#### Figure 4—MP6400DJ-01 Monitoring a User-Defined Voltage

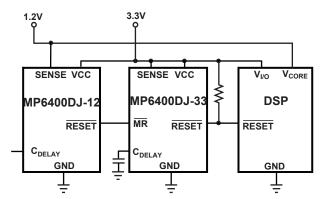

#### **Monitor Multiple System Voltages**

The manual reset ( $\overline{\text{MR}}$ ) can introduce another logic signal to control the  $\overline{\text{RESET}}$ . When  $\overline{\text{MR}}$  is a logic low (0.25V<sub>CC</sub>),  $\overline{\text{RESET}}$  will be asserted. After both SENSE and  $\overline{\text{MR}}$  are above their thresholds,  $\overline{\text{RESET}}$  will be driven to a logic high after a reset delay time. The  $\overline{\text{MR}}$  is internally connected to V<sub>CC</sub> through a 90k $\Omega$  resistor so this pin can float. See how multiple system voltages are monitored by  $\overline{\text{MR}}$  in Figure 5. If the signal on  $\overline{\text{MR}}$  isn't up to V<sub>CC</sub>, there will be an additional current through internal 90k $\Omega$  pull up resistor. A logic-level FET can be used to minimize the leakage, as shown in Figure 6.

Figure 5— MP6400 Family Monitoring Multiple System Voltages

MP6400 Rev. 0.91 12/16/2009

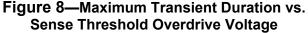

Figure 6—Minimizing  $I_{cc}$  When  $\overline{MR}$  Signal isn't over Vcc by External MOSFET

#### **Programmable Reset Delay Time**

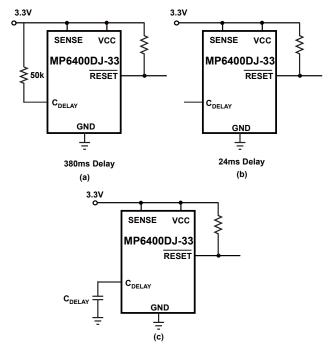

The reset delay time can be programmed by  $C_{DELAY}$  configure. When  $C_{DELAY}$  is connected to VCC through a resistor between 50k $\Omega$  and 200k $\Omega$ , the delay time is 380ms. When  $C_{DELAY}$  floated, the delay time is 24ms. In addition, a capacitor connected  $C_{DELAY}$  to GND could be used to get the user's programmable delay time from 2.1ms to 10s. The three configures can be found in Figure 7(a)(b)(c).

# Figure 7—Programmable Configurations to the Reset Delay Time

The external capacitor  $C_{DELAY}$  must be larger than 150pF. For a given delay time, the capacitor value can be calculated using the following equation:

$C_{\text{DELAY}}(nF) = [t_{D}(s) - 4.99 \times 10^{-4}(s)] \times 107$

The reset delay time is determined by the charge time of external capacitor. While SENSE is above  $V_{IT}$  and  $\overline{MR}$  is a logic high, the internal 140nA current source is enabled and starts to charge the capacitor to set the delay time. When the capacitor voltage rises to 1.13V, the RESET is deasserted. The capacitor will be discharged when the **RESET** is again asserted. Stray capacitance may cause errors of the delay time. A ceramic capacitor with low leakage is strongly recommended.

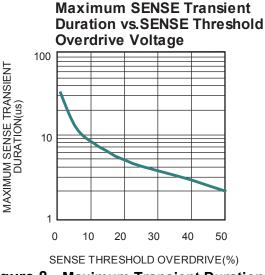

#### SENSE Voltage Transients Immunity

The MP6400 can be immune to SENSE pin short negative transient. The maximum immune duration is 17us while overdrive is 5%. A shorter negative transient can not assert the  $\overline{\text{RESET}}$  output. The effective duration is relative to the threshold overdrive, as shown in Figure 8.

# **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

| MP6400 Rev. 0.91 | www.MonolithicPower.com                                                         |

|------------------|---------------------------------------------------------------------------------|

| 12/16/2009       | MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited. |

|                  | © 2009 MPS. All Rights Reserved.                                                |