# 32-Channel Serial to Parallel Converter With Open Drain Outputs

#### **Features**

- Processed with HVCMOS<sup>®</sup> technology

- Output voltages to 225V using a ramped supply voltage

- SINK current minimum 100mA

- Shift register speed 8.0MHz

- Strobe and enable inputs

- CMOS compatible inputs

- Forward and reverse shifting options

- Hi-Rel processing available

#### **General Description**

The HV5222 is a low voltage serial to high voltage parallel converter with open drain outputs. This device has been designed for use as a driver for AC electroluminescent displays. They can also be used in any application requiring multiple output high voltage current sinking capabilities such as driving inkjet and electrostatic print heads, plasma panels, vacuum fluorescent, or large matrix LCD displays.

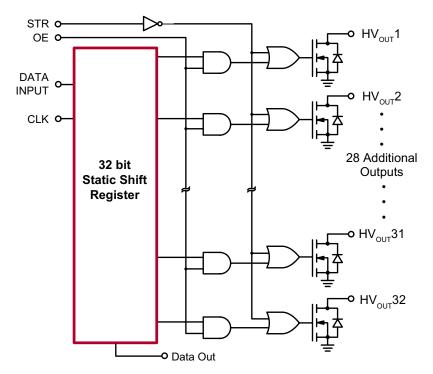

This device consists of a 32-bit shift register and control logic to perform the Output Enable and all-on functions. Data is shifted through the shift register on the high to low transition of the clock. The HV5222 shifts in the clockwise direction when viewed from the top of the package. A data output buffer is provided for cascading devices. This output reflects the current status of the last bit of the shift register. Operation of the shift register is not affected by the OE(Output Enable) or the STR (Strobe) inputs.

The HV5222 has been designed to be used in systems which either switch off the high voltage supply before changing the state of the high voltage outputs or which limit the current through each output.

#### **Functional Block Diagram**

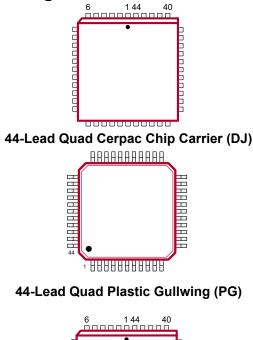

#### **Ordering Information**

|        |                                                                                                | Package Options                                                                               |                                                                                                 |   |

|--------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---|

| Device | 44-Lead Quad<br>Cerpac Chip Carrier<br>.650x.650in body<br>.190in height (max)<br>.050in pitch | 44-Lead Quad<br>Plastic Gullwing<br>10.00x10.00mm body<br>2.35mm height (max)<br>0.80mm pitch | 44-Lead Quad<br>Plastic Chip Carrier<br>.653x.653in body<br>.180in height (max)<br>.050in pitch | C |

| HV5222 | HV5222DJ*                                                                                      | HV5222PG-G                                                                                    | HV5222PJ-G                                                                                      | ] |

-G indicates package is RoHS compliant ('Green')

\* Hi-Rel processing available

## **Absolute Maximum Ratings**

| Parameter                                                             | Value                             |

|-----------------------------------------------------------------------|-----------------------------------|

| Supply voltage, V <sub>DD</sub>                                       | -0.5V to +15V                     |

| Supply voltage, V <sub>PP</sub>                                       | -0.5V to +250V                    |

| Logic input levels                                                    | -0.5V to V <sub>DD</sub> +0.5V    |

| Ground current <sup>1</sup>                                           | 1.5A                              |

| Continuous total power dissipation <sup>2</sup><br>Plastic<br>Ceramic | 1200W<br>1500W                    |

| Operating temperature range<br>Plastic<br>Ceramic                     | -40°C to +85°C<br>-55°C to +125°C |

| Storage temperature range                                             | -65°C to +150°C                   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### Notes:

- 1. Duty cycle is limited by the total power dissipated in the package.

- For operation above 25°C ambient derate linearly to maximum operating temperature at 20mW/°C for plastic and at 15mW/°C for ceramic.

# **Pin Configuration**

#### 44-Lead Quad Plastic Chip Carrier (PJ)

Packages may or may not include the following marks: Si or 🎲

#### **Recommended Operating Conditions**

| Sym               | Parameter                      |         | Min                  | Тур  | Max             | Units |

|-------------------|--------------------------------|---------|----------------------|------|-----------------|-------|

| V <sub>DD</sub>   | Logic voltage supply           |         | 10.8                 | 12   | 13.2            | V     |

| HV <sub>OUT</sub> | High voltage output            |         | -0.3                 | -    | 225             | V     |

| V <sub>IH</sub>   | High-level input voltage       |         | V <sub>DD</sub> -2.0 | -    | V <sub>DD</sub> | V     |

| V <sub>IL</sub>   | Low-level input voltage        |         | 0                    | -    | 2.0             | V     |

| f <sub>CLK</sub>  | Clock frequency                |         | -                    | -    | 8.0             | MHz   |

| т                 | Operating free air temperature | Plastic | -40                  | -    | +85             | 00    |

| T <sub>A</sub>    | Operating free-air temperature | -55     | -                    | +125 | °C              |       |

#### **Power-Up Sequence**

Power-up sequence should be the following:

- 1. Connect ground

- 2. Apply  $V_{DD}$ 3. Set all inputs to a known state

Power-down sequence should be the reverse of the above.

#### Electrical Characteristics (Over recommended operating conditions unless otherwise specified) **DC Characteristics**

| Sym                 | Parameter                                |                   | Min                   | Мах  | Units                    | Conditions                            |  |  |

|---------------------|------------------------------------------|-------------------|-----------------------|------|--------------------------|---------------------------------------|--|--|

| I <sub>DD</sub>     | V <sub>DD</sub> supply current           |                   | -                     | 15   | mA                       | $f_{CLK} = 8.0MHz, F_{DATA} = 4.0MHz$ |  |  |

| I <sub>DDQ</sub>    | Quiescent V <sub>DD</sub> supply curr    | rent              | -                     | 100  | μA                       | All $V_{IN} = 0V$                     |  |  |

| I <sub>O(OFF)</sub> | Off-state output current                 |                   | -                     | 10   | μA                       | All outputs high, all SWS parallel    |  |  |

| I <sub>IH</sub>     | High level logic input curre             | -                 | 1.0                   | μA   | V <sub>IH</sub> = 12V    |                                       |  |  |

| I <sub>IL</sub>     | Low level logic input curre              | ent               | -                     | -1.0 | μA                       | V <sub>IL</sub> = 0                   |  |  |

| V <sub>OH</sub>     | High level output data out               | :                 | V <sub>DD</sub> -1.0V | -    | V                        | Ι <sub>DOUT</sub> = -100μΑ            |  |  |

| M                   |                                          | HV <sub>OUT</sub> | -                     | 15   | V                        | I <sub>HVOUT</sub> = +100mA           |  |  |

| V <sub>OL</sub>     | V <sub>oL</sub> Low level output voltage | Data out          | -                     | 1.0  |                          | Ι <sub>DOUT</sub> = +100μΑ            |  |  |

| V <sub>oc</sub>     | $HV_{OUT}$ clamp voltage                 | -                 | -1.5                  | V    | I <sub>oL</sub> = -100mA |                                       |  |  |

#### AC Characteristics ( $V_{DD} = 12V, T_A = 25^{\circ}C$ )

| Sym              | Parameter                            | Min | Мах | Units | Conditions                      |

|------------------|--------------------------------------|-----|-----|-------|---------------------------------|

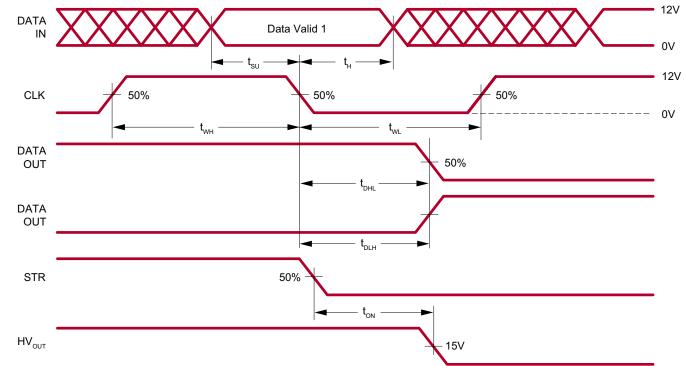

| f <sub>ськ</sub> | Clock frequency                      | -   | 8.0 | MHz   |                                 |

| t <sub>w</sub>   | Clock width, high or low             | 62  | -   | ns    |                                 |

| t <sub>s∪</sub>  | Data setup time before CLK falls     | 25  | -   | ns    |                                 |

| t <sub>H</sub>   | Data hold time after CLK falls       | 10  | -   | ns    |                                 |

| t <sub>on</sub>  | Turn-on time, $HV_{OUT}$ from strobe | -   | 500 | ns    | $R_{L}$ = 2.0K $\Omega$ to 200V |

| t <sub>DHL</sub> | Data output delay after H to L CLK   | -   | 100 | ns    | C <sub>L</sub> = 15pF           |

| t <sub>DLH</sub> | Data output delay after L to H CLK   | -   | 100 | ns    | C <sub>L</sub> = 15pF           |

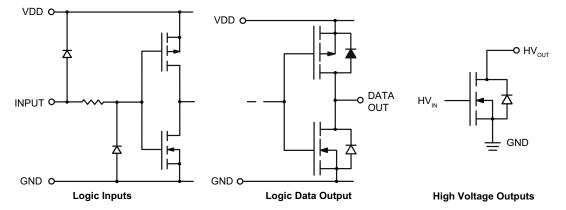

### Input and Output Equivalent Circuits

### **Switching Waveforms**

#### **Function Table**

|               |        | Inp          | uts |        | Outputs |     |           |        |      |  |  |

|---------------|--------|--------------|-----|--------|---------|-----|-----------|--------|------|--|--|

| Function      | Data   |              |     | Otrobo | Shift   | Reg | ΗV Οι     | utputs | Data |  |  |

|               | In     | CLK          | OE  | Strobe | 1       | 232 | 1         | 232    | Out  |  |  |

| All on        | X      | Х            | Х   | L      | •       | ••  | ON        | ONON   | •    |  |  |

| All off       | Х      | Х            | L   | Н      | •       | ••  | OFF       | OFFOFF | •    |  |  |

| Load S/R      | H OR L | $\downarrow$ | L   | Н      | H or L  | ••  | OFF       | OFFOFF | -    |  |  |

| Output Enable | Х      | H OR L       | Н   | Н      | H or L  | ••  | ON or OFF | ●●     | •    |  |  |

#### Notes:

$H = high \ level, \ L = low \ level, \ X = irrelevant, \ \downarrow = high-to-low \ transition$

• = dependent on previous stage's state before the last CLK: High-to-low transition

## 44-Lead PQFP Pin Assignment (PG)

| HV5222PG |                      |                                                                                                                                                       |  |  |  |  |  |  |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin      | Function             | Description                                                                                                                                           |  |  |  |  |  |  |

| 1        | HV <sub>out</sub> 22 |                                                                                                                                                       |  |  |  |  |  |  |

| 2        | HV <sub>out</sub> 21 |                                                                                                                                                       |  |  |  |  |  |  |

| 3        | HV <sub>out</sub> 20 |                                                                                                                                                       |  |  |  |  |  |  |

| 4        | HV <sub>out</sub> 19 |                                                                                                                                                       |  |  |  |  |  |  |

| 5        | HV <sub>out</sub> 18 |                                                                                                                                                       |  |  |  |  |  |  |

| 6        | HV <sub>out</sub> 17 |                                                                                                                                                       |  |  |  |  |  |  |

| 7        | HV <sub>out</sub> 16 |                                                                                                                                                       |  |  |  |  |  |  |

| 8        | HV <sub>out</sub> 15 |                                                                                                                                                       |  |  |  |  |  |  |

| 9        | HV <sub>out</sub> 14 |                                                                                                                                                       |  |  |  |  |  |  |

| 10       | HV <sub>out</sub> 13 |                                                                                                                                                       |  |  |  |  |  |  |

| 11       | HV <sub>out</sub> 12 |                                                                                                                                                       |  |  |  |  |  |  |

| 12       | HV <sub>out</sub> 11 | High voltage outputs.                                                                                                                                 |  |  |  |  |  |  |

| 13       | HV <sub>out</sub> 10 |                                                                                                                                                       |  |  |  |  |  |  |

| 14       | HV <sub>out</sub> 9  |                                                                                                                                                       |  |  |  |  |  |  |

| 15       | HV <sub>OUT</sub> 8  |                                                                                                                                                       |  |  |  |  |  |  |

| 16       | HV <sub>out</sub> 7  |                                                                                                                                                       |  |  |  |  |  |  |

| 17       | HV <sub>out</sub> 6  |                                                                                                                                                       |  |  |  |  |  |  |

| 18       | HV <sub>out</sub> 5  |                                                                                                                                                       |  |  |  |  |  |  |

| 19       | HV <sub>OUT</sub> 4  |                                                                                                                                                       |  |  |  |  |  |  |

| 20       | HV <sub>out</sub> 3  |                                                                                                                                                       |  |  |  |  |  |  |

| 21       | HV <sub>OUT</sub> 2  |                                                                                                                                                       |  |  |  |  |  |  |

| 22       | HV <sub>out</sub> 1  |                                                                                                                                                       |  |  |  |  |  |  |

| 23       | DATA OUT             | Serial data output<br>Data output for cascading to the data input of the next device.                                                                 |  |  |  |  |  |  |

| 24       |                      |                                                                                                                                                       |  |  |  |  |  |  |

| 25       | -                    |                                                                                                                                                       |  |  |  |  |  |  |

| 26       | N/C                  | No connect.                                                                                                                                           |  |  |  |  |  |  |

| 27       | -                    |                                                                                                                                                       |  |  |  |  |  |  |

|          |                      | Output enable input.                                                                                                                                  |  |  |  |  |  |  |

| 28       | OE                   | When OE is LOW, all HV outputs are forced into a LOW state, regardless of data in each channel. When OE is HIGH, all HV outputs reflect data latched. |  |  |  |  |  |  |

| 29       | CLK                  | Data shift register clock.<br>Input are shifted into the shift register on the positive edge of the clock.                                            |  |  |  |  |  |  |

| 30       | GND                  | Logic and high voltage ground.                                                                                                                        |  |  |  |  |  |  |

| 31       | VDD                  | Low voltage logic power rail.                                                                                                                         |  |  |  |  |  |  |

| 32       | STR                  | Strobe.                                                                                                                                               |  |  |  |  |  |  |

| 33       | DATA IN              | Serial data input                                                                                                                                     |  |  |  |  |  |  |

|          |                      | Data needs to be present before each rising edge of the clock.                                                                                        |  |  |  |  |  |  |

## 44-Lead PQFP Pin Assignment (PG) (cont.)

| HV5222PG |                      |                       |

|----------|----------------------|-----------------------|

| Pin      | Function             | Description           |

| 34       | N/C                  | No connect            |

| 35       | HV <sub>OUT</sub> 32 |                       |

| 36       | HV <sub>OUT</sub> 31 |                       |

| 37       | HV <sub>OUT</sub> 30 |                       |

| 38       | HV <sub>OUT</sub> 29 |                       |

| 39       | HV <sub>OUT</sub> 28 | High voltage outputs. |

| 40       | HV <sub>OUT</sub> 27 |                       |

| 41       | HV <sub>OUT</sub> 26 |                       |

| 42       | HV <sub>OUT</sub> 25 |                       |

| 43       | HV <sub>OUT</sub> 24 |                       |

| 44       | HV <sub>OUT</sub> 23 |                       |

# 44-Lead PLCC Pin Assignment (DJ/PJ)

| HV5222PJ |                      |                                                                                       |

|----------|----------------------|---------------------------------------------------------------------------------------|

| Pin      | Function             | Description                                                                           |

| 1        | HV <sub>OUT</sub> 17 |                                                                                       |

| 2        | HV <sub>out</sub> 16 |                                                                                       |

| 3        | HV <sub>out</sub> 15 |                                                                                       |

| 4        | HV <sub>out</sub> 14 |                                                                                       |

| 5        | HV <sub>out</sub> 13 |                                                                                       |

| 6        | HV <sub>out</sub> 12 |                                                                                       |

| 7        | HV <sub>out</sub> 11 |                                                                                       |

| 8        | HV <sub>out</sub> 10 |                                                                                       |

| 9        | HV <sub>out</sub> 9  | High voltage outputs.                                                                 |

| 10       | HV <sub>out</sub> 8  |                                                                                       |

| 11       | HV <sub>out</sub> 7  |                                                                                       |

| 12       | HV <sub>out</sub> 6  |                                                                                       |

| 13       | HV <sub>out</sub> 5  |                                                                                       |

| 14       | HV <sub>out</sub> 4  |                                                                                       |

| 15       | HV <sub>out</sub> 3  |                                                                                       |

| 16       | HV <sub>out</sub> 2  |                                                                                       |

| 17       | HV <sub>out</sub> 1  |                                                                                       |

| 18       | DATA OUT             | Serial data output<br>Data output for cascading to the data input of the next device. |

# 44-Lead PLCC Pin Assignment (PJ) (cont.)

| HV5222PJ |                      |                                                                                                                                                                               |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin      | Function             | Description                                                                                                                                                                   |

| 19       |                      |                                                                                                                                                                               |

| 20       |                      |                                                                                                                                                                               |

| 21       | N/C                  | No connect.                                                                                                                                                                   |

| 22       | ]                    |                                                                                                                                                                               |

| 23       | OE                   | Output enable input.<br>When OE is LOW, all HV outputs are forced into a LOW state, regardless of data in each channel. When OE is HIGH, all HV outputs reflect data latched. |

| 24       | CLK                  | Data shift register clock.<br>Input are shifted into the shift register on the positive edge of the clock.                                                                    |

| 25       | GND                  | Logic and high voltage ground.                                                                                                                                                |

| 26       | VDD                  | Low voltage logic power rail.                                                                                                                                                 |

| 27       | STR                  | Strobe.                                                                                                                                                                       |

| 28       | DATA IN              | Serial data input<br>Data needs to be present before each rising edge of the clock.                                                                                           |

| 29       | N/C                  | No connect                                                                                                                                                                    |

| 30       | HV <sub>OUT</sub> 32 |                                                                                                                                                                               |

| 31       | HV <sub>OUT</sub> 31 |                                                                                                                                                                               |

| 32       | HV <sub>OUT</sub> 30 |                                                                                                                                                                               |

| 33       | HV <sub>out</sub> 29 |                                                                                                                                                                               |

| 34       | HV <sub>OUT</sub> 28 |                                                                                                                                                                               |

| 35       | HV <sub>OUT</sub> 27 |                                                                                                                                                                               |

| 36       | HV <sub>OUT</sub> 26 |                                                                                                                                                                               |

| 37       | HV <sub>OUT</sub> 25 | High voltage outputs.                                                                                                                                                         |

| 38       | HV <sub>OUT</sub> 24 |                                                                                                                                                                               |

| 39       | HV <sub>OUT</sub> 23 |                                                                                                                                                                               |

| 40       | HV <sub>out</sub> 22 |                                                                                                                                                                               |

| 41       | HV <sub>out</sub> 21 |                                                                                                                                                                               |

| 42       | HV <sub>out</sub> 20 |                                                                                                                                                                               |

| 43       | HV <sub>out</sub> 19 |                                                                                                                                                                               |

| 44       | HV <sub>out</sub> 18 |                                                                                                                                                                               |

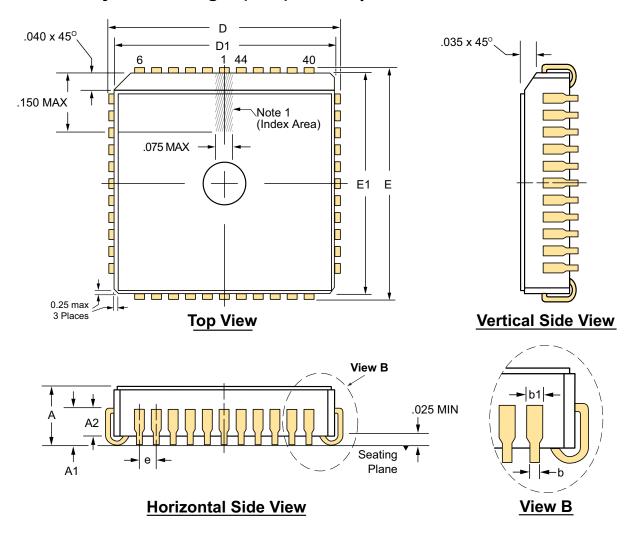

# 44-Lead Quad Cerpac Package Outline (DJ) .650x.650in body, .190in height (max), .050in pitch

Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symb                  | ol  | Α    | A1   | A2          | b    | b1   | D    | D1   | E    | E1   | е           |

|-----------------------|-----|------|------|-------------|------|------|------|------|------|------|-------------|

| <b>D</b>              | MIN | .155 | .090 |             | .017 | .026 | .685 | .630 | .685 | .630 | 050         |

| Dimension<br>(inches) | NOM | .172 | .100 | .060<br>REF | .019 | .029 | .690 | .650 | .690 | .650 | .050<br>BSC |

| (incres)              | MAX | .190 | .120 |             | .021 | .032 | .695 | .665 | .695 | .665 | DOO         |

JEDEC Registration MO-087, Variation AB, Issue B, August, 1991.

Drawings not to scale.

Supertex Doc. #: DSPD-44CERPACDJ, Version D090808.

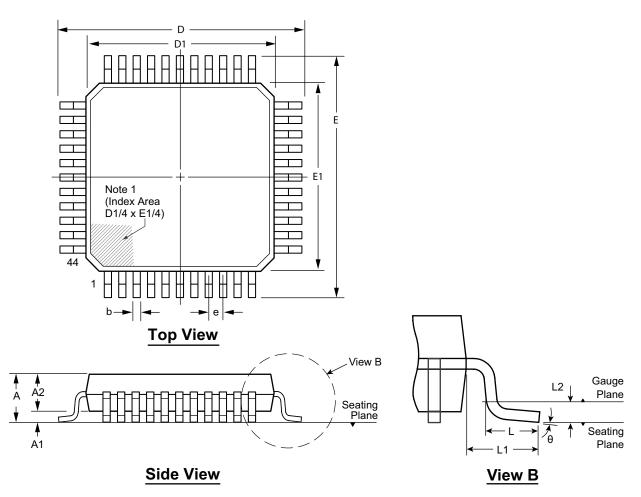

## 44-Lead PQFP Package Outline (PG) 10.00x10.00mm body, 2.35mm height (max), 0.80mm pitch

Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | ol  | Α     | A1   | A2   | b    | D      | D1     | Е      | E1     | е           | L    | L1          | L2          | θ                |

|-------------------|-----|-------|------|------|------|--------|--------|--------|--------|-------------|------|-------------|-------------|------------------|

|                   | MIN | 1.95* | 0.00 | 1.95 | 0.30 | 13.65* | 9.80*  | 13.65* | 9.80*  |             | 0.73 |             |             | <b>0</b> 0       |

| Dimension<br>(mm) | NOM | -     | -    | 2.00 | -    | 13.90  | 10.00  | 13.90  | 10.00  | 0.80<br>BSC | 0.88 | 1.95<br>REF | 0.25<br>BSC | 3.5 <sup>0</sup> |

| ()                | MAX | 2.35  | 0.25 | 2.10 | 0.45 | 14.15* | 10.20* | 14.15* | 10.20* |             | 1.03 |             |             | <b>7</b> °       |

JEDEC Registration MO-112, Variation AA-2, Issue B, Sep.1995.

\* This dimension is not specified in the JEDEC drawing.

Drawings not to scale.

Supertex Doc. #: DSPD-44PQFPPG, Version C041309.

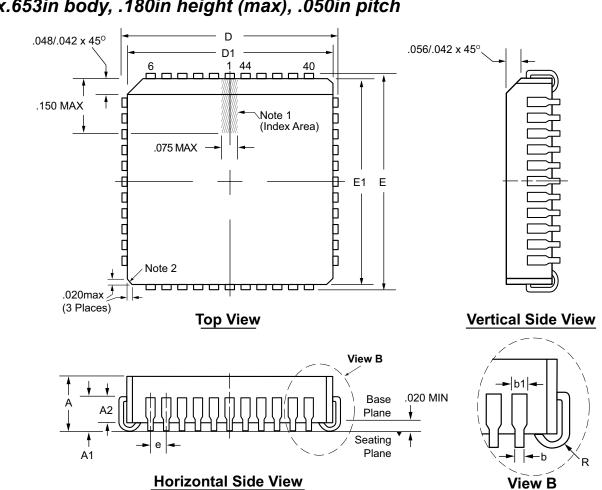

## 44-Lead PLCC Package Outline (PJ) .653x.653in body, .180in height (max), .050in pitch

Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Actual shape of this feature may vary.

| Symbol                |     | Α    | A1   | A2   | b    | b1    | D    | D1   | Е    | E1   | е           | R    |

|-----------------------|-----|------|------|------|------|-------|------|------|------|------|-------------|------|

| Dimension<br>(inches) | MIN | .165 | .090 | .062 | .013 | .026  | .685 | .650 | .685 | .650 | .050<br>BSC | .025 |

|                       | NOM | .172 | .105 | -    | -    | -     | .690 | .653 | .690 | .653 |             | .035 |

|                       | MAX | .180 | .120 | .083 | .021 | .036† | .695 | .656 | .695 | .656 |             | .045 |

JEDEC Registration MS-018, Variation AC, Issue A, June, 1993.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc. #: DSPD-44PLCCPJ, Version F031111.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.</u> supertex.com/packaging.html.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2011 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

Tel: 408-222-8888

www.supertex.com