# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

# **Features**

- Sensor IC based on HALIOS<sup>®</sup> technology

- Up to 4 sending channels, 1 compensation channel an 1 differential receiver input for various HALIOS<sup>®</sup> applications

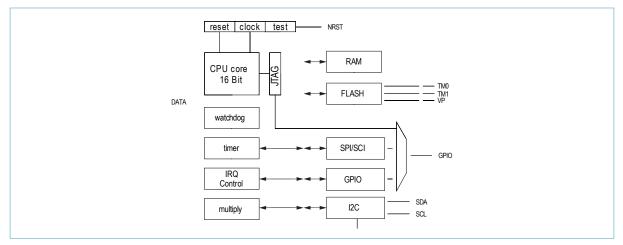

- ▶ 16 bit micro controller 'EL16' with debug interface

- Up to 1.5K x 18 (3KByte) SRAM including 2 bit parity per 16 bit word and byte write support

- Up to 30K x 22 (60KByte) FLASH including

6 bit CRC checksum per 16 bit word

- ► SPI and I<sup>2</sup>C communication interface

- SCI interface incl. LIN support

- Watchdog, 32 bit timer, up to 8 GPIOs

- Multiply unit

- AEC-Q100 automotive qualification

- Supply voltage range 2.25V to 2.75V

# **Ordering Information**

| Product ID | Temp. Range    | Package |

|------------|----------------|---------|

| E909.06    | -40°C to +85°C | QFN32L5 |

# **Applications**

- Optical or capacitive input devices

- Proximity and gesture detection

- Compact HMI interfaces for one-dimensional up to three-dimensional input

# **General Description**

The IC is based on an optical bridge technology which provides a non-mechanical detection of movements.

The system detects the optical reflections of an object in front of the sensor by using a function principle called HALIOS<sup>®</sup> (High Ambient Light Independent Optical System) which is very effective in the suppression of ambient light and also has self calibration capability to eliminate disturbances caused by housing reflections and scratches.

In the same manner capacitive systems can be addressed by using the integrated charge amplifier.

# 1 Pinout

# 1.1 Pin description

| No | Name      | Type 1) | Pull | ESD         | Description                           |

|----|-----------|---------|------|-------------|---------------------------------------|

| 1  | GPIO_7    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 7     |

| 2  | GPIO_6    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 6     |

| 3  | GPIO_5    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 5     |

| 4  | GPIO_4    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 4     |

| 5  | GPIO_3    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 3     |

| 6  | GPIO_2    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 2     |

| 7  | GPIO_1    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 1     |

| 8  | GPIO_0    | D_IO    | Down | +/- 2KV HBM | D IO PD Sr - General Purpose IO 0     |

| 9  | LED1      | A_O     | -    | +/- 2KV HBM | A O - LED Driver output               |

| 10 | VSSLED1,2 | S       | -    | +/- 2KV HBM | A G - Ground LED1,2                   |

| 11 | LED2      | A_O     | -    | +/- 2KV HBM | A O - LED Driver output               |

| 12 | LED3      | A_O     | -    | +/- 2KV HBM | A O - LED Driver output               |

| 13 | VSSLED3,4 | S       | -    | +/- 2KV HBM | A G - Ground LED3,4                   |

| 14 | LED4      | A_O     | -    | +/- 2KV HBM | A O - LED Driver output               |

| 15 | VSSLEDC   | S       | -    | +/- 2KV HBM | A G - Ground LEDC                     |

| 16 | LEDC      | A_O     | -    | +/- 2KV HBM | A O - LED Driver output               |

| 17 | I2C_SDA   | D_IO    | -    | +/- 2KV HBM | D IO - I2C SDA (Data)                 |

| 18 | I2C_SCL   | D_IO    | -    | +/- 2KV HBM | D IO - I2C SCL (CLK)                  |

| 19 | VDDC      | S       | -    | +/- 2KV HBM | D S - Core Supply 2.5V                |

| 20 | VSS       | S       | -    | +/- 2KV HBM | D G - Ground                          |

| 21 | VDDIO     | S       | -    | +/- 2KV HBM | D S - IO Supply 3.3V                  |

| 22 | AMP_KA    | A_O     | -    | +/- 2KV HBM | A O - Output 1. stage amplifier at KA |

| 23 | AVDD      | S       | -    | +/- 2KV HBM | A S - Analog Supply 2.5V              |

| 24 | KA        | A_I     | -    | +/- 2KV HBM | A I - Kathode                         |

| 25 | AN        | A_I     | -    | +/- 2KV HBM | A I - Anode                           |

| 26 | AVSS      | S       | -    | +/- 2KV HBM | A G - Analog Ground                   |

| 27 | AMP_AN    | A_O     | -    | +/- 2KV HBM | A O - Output 1. stage amplifier at AN |

| 28 | NRST      | D_I     | Up   | +/- 2KV HBM | D I PU St - Reset                     |

| 29 | TMODE     | D_I     | Down | +/- 2KV HBM | D I PD - Testmode                     |

| 30 | TM1       | A_IO    | -    | +/- 2KV HBM | A IO - Analog Testbus                 |

| 31 | TM0       | A_IO    | -    | +/- 2KV HBM | A IO - Analog Testbus                 |

| 32 | VPP       | HV_S    | -    | +/- 2KV HBM | A HV - FLASH program voltage          |

1) D = Digital, A = Analog, S = Supply, I = Input, O = Output, HV = High Voltage

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

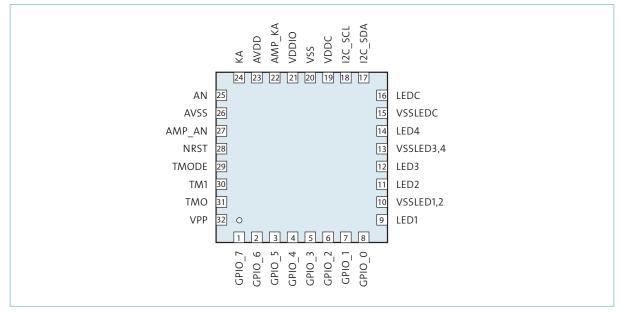

# 1.2 Package Pinout

Package: QFN32L5

Package is according JEDEC MO-220-K, version VHHD-4.

Figure 1: Package Pinout

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# HALIOS<sup>®</sup> MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

# **2** Operating Conditions

# 2.1 Absolute Maximum Ratings

Continuous operation of the device above these ratings is not allowed and may destroy the device. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

| No. | Description                                              | Condition                                           | Symbol                            | Min. | Max.                    | Unit |

|-----|----------------------------------------------------------|-----------------------------------------------------|-----------------------------------|------|-------------------------|------|

| 1   | Supply voltage: digital core, analog part                | Referenced<br>to V <sub>ss</sub> / A <sub>vss</sub> | $V_{_{ m DDC}}$ / $A_{_{ m VDD}}$ | -0.3 | 2.8                     | V    |

| 2   | IO supply voltage/digital pins<br>(see "type"/chapter )  | Referenced<br>to V <sub>ss</sub>                    | V <sub>ddio</sub>                 | -0.3 | 3.7                     | V    |

| 3   | Input voltage analog pins<br>(see "type"/chapter )       | Referenced<br>to A <sub>vss</sub>                   | V <sub>INA</sub>                  | -0.3 | A <sub>VDD</sub> + 0.3  | V    |

| 4   | Input voltage digital pins/GPIO<br>(see "type"/chapter ) | Referenced<br>to V <sub>ss</sub>                    | V <sub>IND</sub>                  | -0.3 | V <sub>DDIO</sub> + 0.3 | V    |

| 5   | Ground offset                                            | $V_{ss}$ to $A_{vss}$ to $V_{ssled}$                | Ground<br>offset                  | -0.3 | 0.3                     | V    |

| 6   | Junction Temperature                                     |                                                     | T <sub>j</sub>                    | -40  | +125                    | °C   |

| 7   | Storage Temperature                                      |                                                     | Т <sub>stg</sub>                  | -50  | 150                     | °C   |

# 2.2 Recommended Operating Conditions

The following conditions apply unless otherwise stated. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

| No. | Description                                             | Condition                                           | Symbol                            | Min. | Тур. | Max. | Unit |

|-----|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------|------|------|------|------|

| 1   | Supply voltage: analog part,<br>digital core            | Referenced to<br>V <sub>ss</sub> / A <sub>vss</sub> | $V_{_{ m DDC}}$ / $A_{_{ m VDD}}$ | 2.25 | 2.5  | 2.75 | V    |

| 2   | IO supply voltage/digital pins<br>(see "type"/chapter ) | Referenced<br>to V <sub>ss</sub>                    | V <sub>DDIO</sub>                 | 3.0  | 3.3  | 3.6  | V    |

| 3   | Filter capacitor analog part                            | Connected to $A_{VDD}$                              | C <sub>AVDD</sub>                 |      | 10   |      | μF   |

| 4   | Filter capacitor digital part                           | Connected to<br>V <sub>DDC</sub>                    | C <sub>VDDC</sub>                 |      | 100  |      | nF   |

| 5   | Ambient operating tempera-<br>ture range                |                                                     | T <sub>opt</sub>                  | -40  | 25   | 85   | °C   |

All voltages are referred to V<sub>ss</sub>, and currents are positive when flowing into the node unless otherwise specified.

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# E909.06

# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

# **3 Detailed Electrical Specification**

The following conditions apply unless otherwise stated. All potentials refer to GROUND (GND) unless otherwise specified. Currents flowing into the circuit pins have positive values.

# 3.1 Supply Voltages

| No. | Description                                      | Condition                                                                       | Symbol                                    | Min. | Тур. | Max. | Unit       |

|-----|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------|------|------|------|------------|

| 1   | Digital operating current, run mode              | FSYS = 8 MHz,<br>system state:<br>run                                           | I <sub>vddc</sub>                         |      | 5.8  | 12   | mA         |

| 2   | Digital operating current, standby mode          | System state:<br>standby                                                        | <br>STANDBY                               |      | 1.8  | 5    | mA         |

| 3   | Digital operating current, off mode              | System state:<br>off                                                            | I <sub>off</sub>                          |      |      | 35   | μΑ         |

| 4   | Analog operating current                         | MCR[13:12]<br>="11"<br>PCR[14:13]<br>="11"                                      | I <sub>AVDD</sub>                         |      | 3.5  | 5    | mA         |

| 5   | Analog operating current                         | Analog on = 0                                                                   | AVDD OFF                                  |      |      | 15   | μΑ         |

| 6   | Over all current consumption in application mode | Active mode <sup>1)</sup>                                                       | I <sub>ACTIVE</sub>                       |      | 2.0  | 2.25 | mA         |

| 7   | Over all current consumption in application mode | Idle mode<br>(I <sub>IDLE</sub> = I <sub>OFF</sub> +<br>I <sub>AVDD OFF</sub> ) | I <sub>IDLE</sub>                         |      | 16   | 50   | μΑ         |

| 8   | State change from STANDBY to RUN mode            | -                                                                               | T <sub>standb</sub> .<br><sub>Y2RUN</sub> |      |      | 3    | 1/<br>FSYS |

| 9   | State change from OFF to<br>RUN mode             |                                                                                 | T <sub>off2run</sub>                      |      |      | 5    | 1/<br>FSYS |

1) In application mode the current consumption is calculated from the duty cycle of the digital operating current and the analog operating current.

MCR - Measurement Configuration Register PCR - Preamplifier Configuration Register

# 3.2 Reset Generation

| No. | Description                                                                   | Condition                               | Symbol               | Min. | Тур.           | Max. | Unit       |

|-----|-------------------------------------------------------------------------------|-----------------------------------------|----------------------|------|----------------|------|------------|

| 1   | Power on reset level                                                          | Reference is<br>V <sub>DDC</sub>        | V <sub>por</sub>     |      |                | 2.25 | V          |

| 2   | Brown out high-to-low<br>threshold level                                      | Reference is<br>V <sub>DDC</sub>        | V <sub>bohl</sub>    | 1.8  |                |      | V          |

| 3   | Brown out reset hysteresis                                                    |                                         | V <sub>BOHYST</sub>  | 100  | 200            | 300  | mV         |

| 4   | Minimum supply voltage for power on reset and brown out circuit <sup>1)</sup> |                                         | VDDmin               |      | 0.9            |      | V          |

| 5   | NRST-pin threshold level                                                      |                                         | NRST                 |      | 0.5            |      | VD-<br>DIO |

| 6   | Pull up current NRST-pin                                                      | $V_{NRST} = V_{DDIO}$                   | I<br>NRSTPU          |      | 35             |      | μΑ         |

| 7   | Min. pulse width for a valid<br>reset at pin NRST<br>(debouncing)             | V <sub>DDC</sub> > V <sub>DDC min</sub> | T <sub>debnrst</sub> | 1.0  |                | -    | μs         |

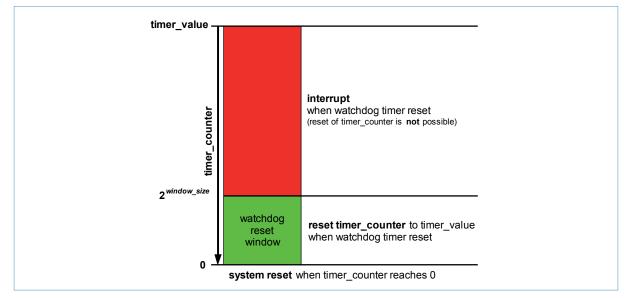

| 8   | Delay Watchdog start =><br>reset <sup>1)</sup>                                |                                         | T <sub>wdog</sub>    |      | timer<br>value |      | 1/<br>FSYS |

1) Will not be tested in production test

# **3.3 Internal Clock Generation**

# 3.3.1 Reference Clocks

| No. | Description            | Condition                                          | Symbol | Min.  | Тур.  | Max.  | Unit |

|-----|------------------------|----------------------------------------------------|--------|-------|-------|-------|------|

| 1   | Wakeup clock frequency | Within rec-<br>ommended<br>operating<br>conditions | FWK    | 115.2 | 128.0 | 140.8 | kHz  |

| 2   | Master clock           | Within rec-<br>ommended<br>operating<br>conditions | FSYS   | 7.2   | 8.0   | 8.8   | MHz  |

# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

# 3.4 Module Description

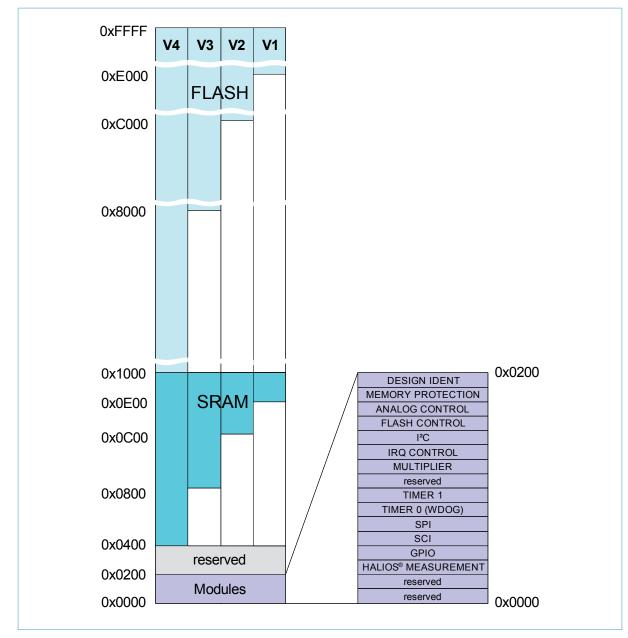

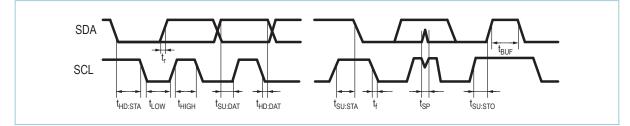

# 3.4.1 I<sup>2</sup>C Interface

| No. | Description                                                                                                       | Condition                 | Symbol               | Min.                         | Тур. | Max.                    | Unit |

|-----|-------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------|------------------------------|------|-------------------------|------|

| 1   | SDA/SCL: Input voltage low                                                                                        |                           | V                    | -0.3                         |      | 0.3 x V <sub>DDIO</sub> | V    |

| 2   | SDA/SCL: Input voltage high                                                                                       |                           | V <sub>IH</sub>      | $0.7 \times V_{\text{ddio}}$ |      | V <sub>DDIO</sub> + 0.3 | V    |

| 3   | SDA/SCL: Hysteresis of Sch-<br>mitt trigger inputs <sup>1)</sup>                                                  | V <sub>DDIO</sub> > 2.0 V | $V_{hys}$            | $0.05 \times V_{DDIO}$       |      | -                       | V    |

| 4   | SDA/SCL: Output voltage low<br>(open drain)                                                                       | I = 3 mA, V<br>> 2.0 V    | V <sub>ol</sub>      |                              |      | 0.4                     | V    |

| 5   | SDA/SCL: Input current                                                                                            | $0 < V_{IN} < V_{DDIO}$   | l <sub>i</sub>       | -10                          |      | 10                      | μΑ   |

| 6   | SDA/SCL: capacitance <sup>1)</sup>                                                                                |                           | C <sub>i</sub>       | -                            |      | 10                      | рF   |

| 7   | SCL clock frequency                                                                                               |                           | $f_{SCL}$            | 0                            |      | 400                     | kHz  |

| 8   | Hold time (repeated) START condition <sup>1)</sup>                                                                |                           | t <sub>hd.:sta</sub> | 600                          |      | -                       | ns   |

| 9   | LOW period of SCL clock                                                                                           |                           | t <sub>LOW</sub>     | 1300                         |      | -                       | ns   |

| 10  | HIGH period of SCL clock                                                                                          |                           | t <sub>ніgн</sub>    | 600                          |      | -                       | ns   |

| 11  | Set-up time for repeated start condition $^{1)}$                                                                  |                           | t <sub>su.:sta</sub> | 600                          |      | -                       | ns   |

| 12  | Data hold time 1)                                                                                                 |                           | t <sub>hd.dat</sub>  | 0                            |      | 900                     | ns   |

| 13  | Data set-up time 1)                                                                                               |                           | t <sub>su:dat</sub>  | 100                          |      | -                       | ns   |

| 14  | Rise time of SDA and SCL sig-<br>nals with a bus capacitance<br>(Cb) from 10 pF to 400 pF <sup>1)</sup>           |                           | t,                   | 20 + 0.1 x C <sub>b</sub>    |      | 300                     | ns   |

| 15  | Fall time of SDA and SCL sig-<br>nals with a bus capacitance<br>(Cb) from 10 pF to 400 pF <sup>1)</sup>           |                           | t <sub>f</sub>       | 20 + 0.1 x C <sub>b</sub>    |      | 300                     | ns   |

| 16  | SDA/SCL: Output fall time<br>from VIH to VIL with a bus<br>capacitance (Cb) from 10 pF<br>to 400 pF <sup>1)</sup> |                           | t <sub>of</sub>      | 20 + 0.1 x C <sub>b</sub>    |      | 250                     | ns   |

| 17  | Set-up time for STOP condi-<br>tion <sup>1)</sup>                                                                 |                           | t <sub>su:sto</sub>  | 600                          |      | -                       | ns   |

| 18  | Bus free time between STOP and START 1)                                                                           |                           | t <sub>BUF</sub>     | 1300                         |      | -                       | ns   |

| 19  | Pulse with of spikes which<br>must be suppressed by the<br>IC-internal input filter                               |                           | t <sub>sp</sub>      | 0                            |      | 50                      | ns   |

1) Will not be tested in production test

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

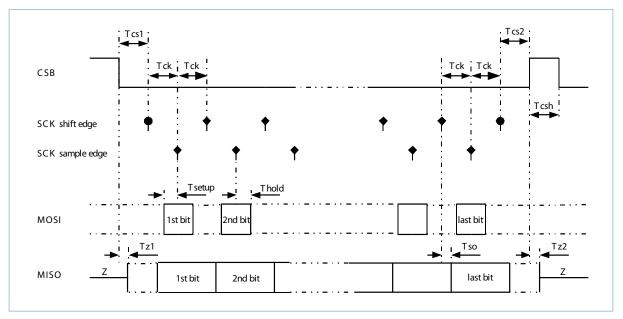

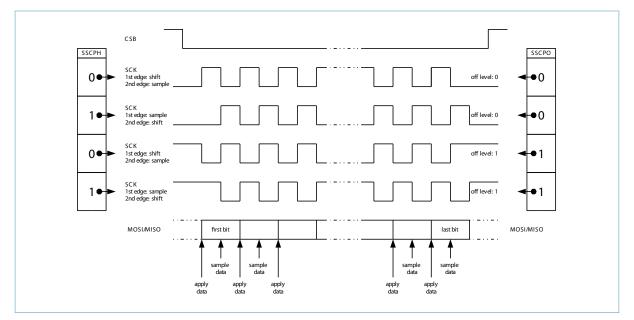

### 3.4.2 SPI Module

| No. | Description                               | Condition            | Symbol | Min. | Тур. | Max. | Unit       |

|-----|-------------------------------------------|----------------------|--------|------|------|------|------------|

| 1   | SCK pulse low width / pulse<br>high width | transfer             | Tck    | 4    |      |      | 1/<br>FSYS |

| 2   | First SCK after falling CSB               | start of<br>transfer | Tcs1   | 2    |      |      | 1/<br>FSYS |

| 3   | Last SCK before rising CSB                | end of<br>transfer   | Tcs2   | 2    |      |      | 1/<br>FSYS |

| 4   | Setup time                                |                      | Tsetup | 1    |      |      | 1/<br>FSYS |

| 5   | Hold time                                 |                      | Thold  | 1    |      |      | 1/<br>FSYS |

| 6   | Data out after shift                      |                      | Tso    |      |      | 3    | 1/<br>FSYS |

| 7   | CSB high time                             |                      | Tcsh   | 2    |      |      | 1/<br>FSYS |

| 8   | Data out change from Z to<br>driven data  | start of<br>transfer | Tz1    |      |      | 1    | 1/<br>FSYS |

| 9   | Data out change from driven<br>data to Z  | end of<br>transfer   | Tz2    |      |      | 1    | 1/<br>FSYS |

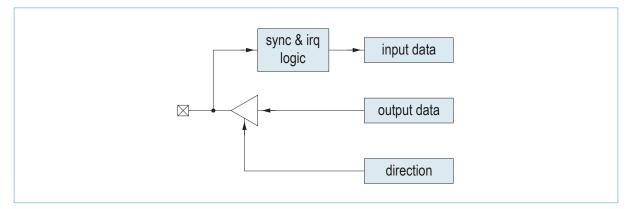

# 3.4.3 GPIO Module

| No. | Description                               | Condition                                  | Symbol              | Min.  | Тур. | Max. | Unit |

|-----|-------------------------------------------|--------------------------------------------|---------------------|-------|------|------|------|

| 1   | Threshold point                           |                                            | GPIO <sub>TH</sub>  | 1.2   | 1.32 | 1.46 | V    |

| 2   | Pull down resistor                        | $V_{IN} > 0.75 \cdot V_{DDIO}$             | R <sub>gpiopd</sub> | 54    |      | 130  | kΩ   |

| 3   | Output Voltage Low                        | GPIOIOL=4 mA;<br>V <sub>DDIO</sub> =3.3 V  | GPIOVOL             |       |      | 0.4  | V    |

| 4   | Output Voltage High                       | GPIOIOH=-4 mA;<br>V <sub>DDIO</sub> =3.3 V | GPIOVOH             | 2.4   |      |      | V    |

| 5   | Low Level Output Current                  | GPIOVOL=0.4V                               | GPIOIOL             | 6     |      | 12   | mA   |

| 6   | High Level Output Current                 | GPIOVOH=2.4V                               | GPIOIOH             | -25.6 |      | -7.8 | mA   |

| 7   | Tri-State Input/Output<br>Leakage Current | Vout=V <sub>DDIO</sub> or 0 V              | GPIOILC             | -1    |      | 1    | μΑ   |

# 3.4.4 HALIOS<sup>®</sup> Interface

# 3.4.4.1 Current Generation for LED Modulators

| No. | Description                         | Condition | Symbol           | Min. | Тур. | Max. | Unit |

|-----|-------------------------------------|-----------|------------------|------|------|------|------|

| 1   | DAC resolution                      |           | Ν                |      | 10   |      | bit  |

| 2   | Integral non linearity (INL)        |           | E <sub>i</sub>   |      | 2    |      | LSB  |

| 3   | Differential non linearity<br>(DNL) |           | E <sub>d</sub>   |      | 2    |      | LSB  |

| 4   | DAC output voltage at full scale    |           | V <sub>MAX</sub> |      | 1.22 |      | V    |

### 3.4.4.2 LED Driver 1 - 4

| No. | Description                                             | Condition   | Symbol               | Min. | Тур. | Max.                          | Unit |

|-----|---------------------------------------------------------|-------------|----------------------|------|------|-------------------------------|------|

| 1   | Regulated proportion of LED<br>current @ DAC = 0        | DAC = 0     | I <sub>R_MINS</sub>  |      |      | 5 % if I <sub>R_MAXS</sub> 1) | mA   |

| 2   | Max. regulated proportion of LED current (RANGE)        | RANGE = 31, | I <sub>R_MAXS</sub>  |      | 10.0 |                               | mA   |

| 3   | Stepsize for regulated cur-<br>rent-range configuration | DAC = 1023  | I <sub>r_steps</sub> |      | 290  |                               | μΑ   |

| 4   | Resolution current-range configuration                  |             | N <sub>RS</sub>      |      | 5    |                               | bit  |

| 5   | Max. fixed proportion of LED current (OFFSET)           |             | I <sub>o_maxs</sub>  |      | 10.0 |                               | mA   |

| 6   | Stepsize for fixed offset-cur-<br>rent configuration    | OFFSET = 31 | ISTEPS               |      | 290  |                               | μΑ   |

| 7   | Resolution offset-current configuration                 |             | N <sub>os</sub>      |      | 5    |                               | bit  |

| 8   | DC-bias current                                         |             | I <sub>bias s</sub>  |      | 225  |                               | μΑ   |

1)  $I_{R MAXS}$  is the maximum current selected with parameter RANGE

### 3.4.4.3 LED Driver C

| No. | Description                                             | Condition                 | Symbol                | Min. | Тур.  | Max.                                        | Unit |

|-----|---------------------------------------------------------|---------------------------|-----------------------|------|-------|---------------------------------------------|------|

| 1   | Regulated proportion of LED<br>current @ DAC = 0        | DAC = 0                   | I <sub>R_MINC</sub>   |      |       | 5 % of<br>I <sub>R_MAXS</sub> <sup>1)</sup> | mA   |

| 2   | Max. regulated proportion of LED current (RANGE)        | RANGE = 31,<br>DAC = 1023 | I <sub>R_MAXC</sub>   |      | 4.0   |                                             | mA   |

| 3   | Stepsize for regulated cur-<br>rent-range configuration |                           | I <sub>R_STEPC</sub>  |      | 125.0 |                                             | μΑ   |

| 4   | Resolution current-range configuration                  |                           | N <sub>RC</sub>       |      | 5     |                                             | bit  |

| 5   | Max. fixed proportion of LED current (OFFSET)           | OFFSET = 127              | I <sub>o_maxc</sub>   |      | 5.0   |                                             | mA   |

| 6   | Stepsize for fixed offset-cur-<br>rent configuration    |                           | I <sub>O_STEPC</sub>  |      | 40.0  |                                             | μΑ   |

| 7   | Resolution offset-current configuration                 |                           | N <sub>oc</sub>       |      | 7     |                                             | bit  |

| 8   | Minimal value for DC-bias current                       |                           | I <sub>bia_co</sub>   |      | 100   |                                             | μΑ   |

| 9   | Stepsize for DC-bias current                            |                           | I DCO_STEPC           |      | 2.5   |                                             | mA   |

| 10  | Max. DC-bias current<br>(DC_OFFSET)                     | DC_OFFSET<br>= 15         | I <sub>DCO_MAXC</sub> |      | 37.6  |                                             | mA   |

1)  $I_{R\_MAXS}$  is the maximum current selected with parameter RANGE

# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

## 3.4.4.4 Receiver

| No. | Description                                                                         | Condition                | Symbol             | Min. | Тур. | Max. | Unit |

|-----|-------------------------------------------------------------------------------------|--------------------------|--------------------|------|------|------|------|

| 1   | Feedback resistor of 1. stage<br>amplifier at input KA and AN;<br>bit 0, bit 1 = 1  |                          | R <sub>f</sub>     |      | 50   |      | kΩ   |

| 2   | Feedback capacitor of 1.<br>stage amplifier at input KA<br>and AN; bit 2, bit 3 = 1 |                          | C <sub>f</sub>     |      | 3.6  |      | рF   |

| 3   | DC photo-current Gyrator<br>mode; bit 9, bit 10 = 1                                 |                          | IDC_photo          |      |      |      | μΑ   |

| 4   | Voltage at amplifier input KA                                                       |                          | V <sub>KA</sub>    |      | 1.9  |      | V    |

| 5   | Voltage at amplifier input AN                                                       |                          | V <sub>AN</sub>    |      | 1.3  |      | V    |

| 6   | Corner frequency highpass<br>filter                                                 |                          | f <sub>G</sub>     |      | 10   |      | kHz  |

| 7   | Gain amplifier 2. stage                                                             |                          | G <sub>0</sub>     |      | 6    |      | dB   |

| 8   | Gain amplifier 3. stage                                                             | PCR[8:7]="01"            | G3                 |      | 12   |      | dB   |

| 9   | Gain amplifier 3. stage                                                             | PCR[8:7]="00"<br>or "11" | G3                 |      | 24   |      | dB   |

| 10  | Gain amplifier 3. stage                                                             | PCR[8:7]="10"            | G3                 |      | 36   |      | dB   |

| 11  | Total gain sym. input                                                               | PCR[8:7]="01"            | G <sub>TOT</sub>   |      | 118  |      | dBΩ  |

| 12  | Total gain sym. input                                                               | PCR[8:7]="00"<br>or "11" | G <sub>TOT</sub>   |      | 130  |      | dBΩ  |

| 13  | Total gain sym. input                                                               | PCR[8:7]="10"            | G <sub>TOT</sub>   |      | 142  |      | dBΩ  |

| 14  | Total gain nonsym. input                                                            | PCR[8:7]="01"            | G <sub>TOT</sub>   |      | 112  |      | dBΩ  |

| 15  | Total gain nonsym. input                                                            | PCR[8:7]="00"<br>or "11" | G <sub>TOT</sub>   |      | 124  |      | dBΩ  |

| 16  | Total gain nonsym. input                                                            | PCR[8:7]="10"            | G <sub>TOT</sub>   |      | 136  |      | dBΩ  |

| 17  | Center frequency                                                                    |                          | f <sub>c</sub>     |      | 125  |      | kHz  |

| 18  | Resolution demodulator output                                                       |                          | N <sub>demod</sub> |      | 1    |      | bit  |

| 19  | Capacitance of photo diode at input KA                                              |                          | C <sub>DIODE</sub> |      |      | 70   | pF   |

| 20  | Internal reference voltage                                                          |                          | V <sub>REF</sub>   |      | 1.22 |      | V    |

| 21  | Internal reference current                                                          |                          | I <sub>BIAS</sub>  |      | 10   |      | μΑ   |

PCR - Preamplifier Configuration Register

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# **4** Functional Description

### 4.1 Introduction

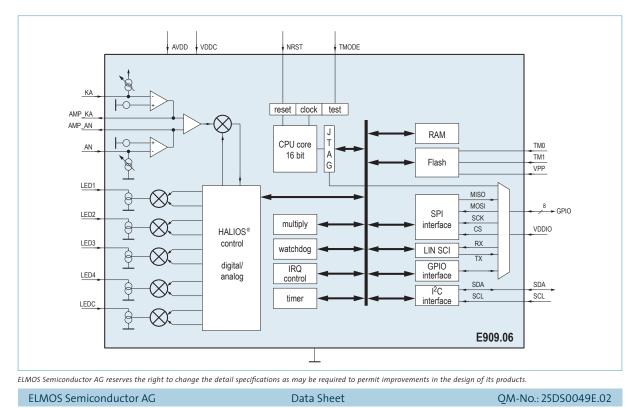

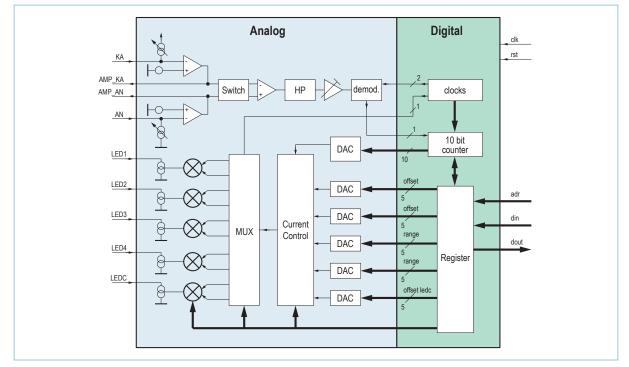

The general architecture of the 3D-optical input device is shown in the system block diagram.

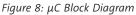

The CPU is connected to the memory (FLASH and SRAM) and the peripheral modules via the internal system bus. The system bus provides a 16 bit address space and allows 8 and 16 bit data transfers.

The memory contains the program code and the data. Memory and registers are mapped to the global memory map and can be accessed through all memory related operation provided by the CPUs instruction set. The memory of the IC consists a FLASH cell up to 30Kx22 (60KByte) including 6 additional bits per word used as CRC for error detection and error correction and a SRAM cell up to 1.5Kx18 (3KByte) including 2 bit parity per word.

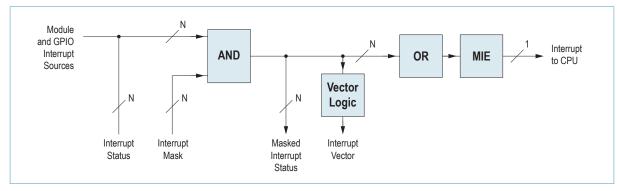

The Interrupt Controller collects requests from all interrupt sources and provides an interrupt signal to the CPU. Interrupt sources can be masked within the interrupt controller. Interrupts are generated by the modules and hold until they are cleared within the module. See module description for clearing procedures.

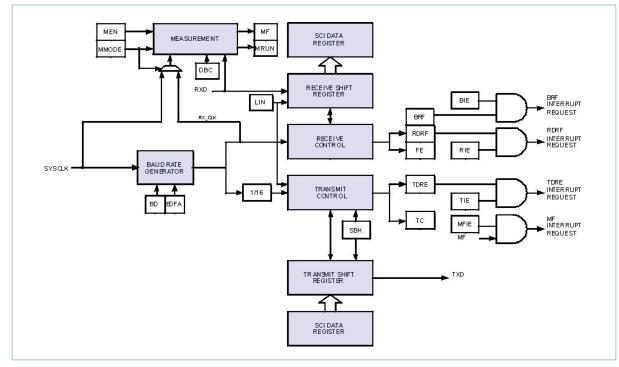

The SPI can be configured either as a master or a slave. Transfer length is eight bit and can be extended by a multiple of eight bit. Data FIFOs are provided for transmit and receive tasks.

The SCI provides the standard NRZ (Non Return to Zero) mark/space data format where each frame contains one start bit, eight data bits and one stop bit. Several features are implemented for special LIN support.

The timer module contains a 32 bit timer module as well as a watchdog timer. Additionally a second timer module operating on wake up clock is implemented that remains active even in off mode, so it can be used for a periodical wake up from off mode for applications that require a low current consumption.

8 IO port pins can either be configured as general purpose IO's or can be configured as ports for the SPI or SCI module. Additionally two ports are reserved for the I<sup>2</sup>C slave interface.

The clock and reset generator module provides the system clock and the global reset signal. A power-on-reset, brown out detect and a power watch are implemented. As external reset source a reset input will be considered. The system clock is generated by an on-chip oscillators. A more detailed diagram of the clock/reset generation block (CRG) is shown in the following sections.

# 4.2 Supply Voltages

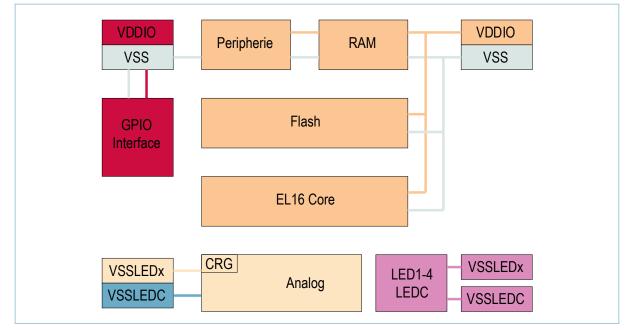

# 4.2.1 Block Diagram

Figure 2: Block Diagram Supply Voltages

# 4.2.2 Functional Description

The devices has three separated power domains and needs two different levels of power supplies. The core power domain is supplied by VDDC and the analog power domain by AVDD. Both needs the same voltage level. The third supply domain is supplied by VDDIO and powers GPIOs. See also 2.2 Recommended Operating Conditions.

# 4.2.3 Power Up Sequence Considerations

During power-up the power-on-reset configures all pads as inputs consequently disabling the output drivers. The IO supply is watched after power up if the core supply is in the specified range and causes a reset if it leaves the allowed region. The core supply is watched via a brown out circuit.

The pads will remain input pads as long as the software does not reconfigure them.

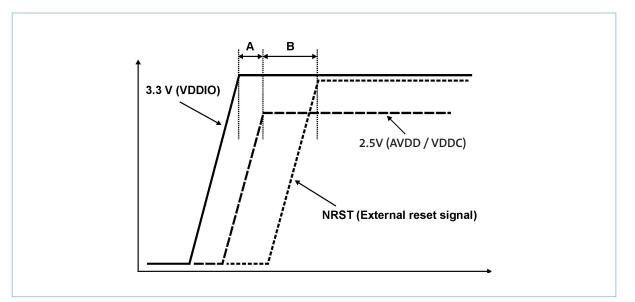

According the following diagram it must be guaranteed that ADVV / DVVC is not switched on before VDDIO. NRST can be switched on if the VDDIO and AVDD/DVVC are stabilized on its potential.

### A >= 0ms B > 5ms (recommended)

To avoid floating gates,  $A < 100 \mu s$  is recommended.

| ELMOS Semiconductor AG   |

|--------------------------|

| LLMOS SEITILOITUULLOI AU |

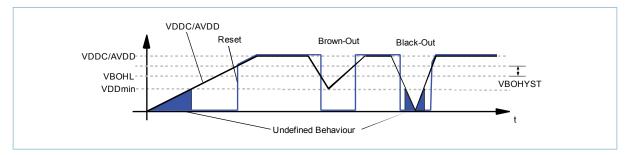

Figure 3: Brown-Out timing diagram

### 4.2.4 Power Down Sequence Considerations

During power down the chip will enter the reset state as soon as the core or IO supply leaves the specified region bringing all pads into input configuration again.

### 4.3 Brown Out Detection

### 4.3.1 Timing Diagram

Figure 4: Brown-Out timing diagram

# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

### 4.3.2 Functional Description

The brown out detection of the chip will cause a reset whenever the core or IO power supply falls below the specified region. An over-voltage protection is not implemented. The circuit will not be operational when the core supply is below VDDmin. In these cases the power-on-reset will take care of proper reset generation.

### 4.4 Reset Generation

# 4.4.1 Reset Generation (RESGEN)

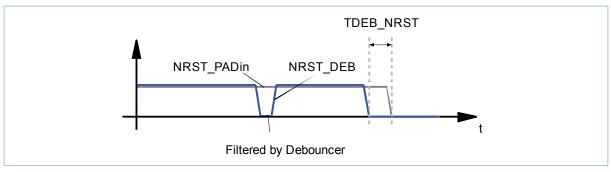

The IC is equipped with a reset input pin which can be used to reset the chip. Any low pulse longer than TDEBNRST on the external reset line will be sensed and causes an IC reset.

The IC contains different dynamic and static reset sources. The static sources trigger the master reset as long as the cause for the reset persists. The dynamic sources trigger the reset for a defined minimum reset time. After that time has expired the system reset is released. In case the dynamic source is still signaling a reset the reset is re-triggered.

### Static reset sources:

- A power up sequence of the core voltage (power on reset)

- Brown out of the core voltage

### Dynamic reset sources:

- Uncorrectable FLASH CRC error

- SRAM parity error

- CPU register parity error

- Watchdog timeout

- Uncorrectable trim register ECC error

Figure 5: Timing of the external reset signal

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

E909.06

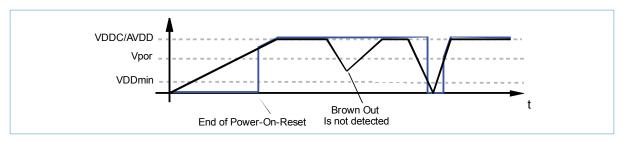

### 4.4.2 Power-On-Reset

## 4.4.2.1 Timing Diagram

Figure 6: Power-On-Reset timing digram

# 4.4.2.2 Functional Description

The power on reset is designed to cause a reset during the power on cycle of the chip. The reset will be deactivated when the supply crosses  $V_{_{POR}}$ .

After the power up sequence the power on reset block will only cause a new reset if the power supply voltage drops below VDDmin and the rise and fall times of the supply are below the specified values.

| failsafe feature                               | asserts interrupt | asserts reset |

|------------------------------------------------|-------------------|---------------|

| FLASH CRC (bit error corrected)                | Х                 |               |

| FLASH CRC (uncorrectable bit error)            |                   | Х             |

| Empty (erased) FLASH word read detection       |                   | Х             |

| FLASH write detection                          | Х                 |               |

| RAM byte parity                                |                   | Х             |

| Uninitialized RAM word / byte read detection   |                   | Х             |

| CPU register parity                            |                   | Х             |

| CPU undefined opcode detection                 | Х                 |               |

| CPU misaligned word access detection           | X                 |               |

| Opcode execution memory protection             | Х                 |               |

| Stack overflow detection                       | Х                 |               |

| Invalid module register access detection       | Х                 |               |

| Watchdog time-out                              |                   | Х             |

| Watchdog window protection                     | Х                 |               |

| Brownout detection (supply voltage monitoring) |                   | Х             |

| System clock monitoring                        |                   | Х             |

# 4.5 System Failsafe Features

### 4.6 HALIOS<sup>®</sup> Interface

### 4.6.1 HALIOS<sup>®</sup> Block Diagram

Figure 7: HALIOS® Block Diagram

### 4.6.2 HALIOS<sup>®</sup> Features

In order to be able to realize optical as well as capacitive sensors the input amplifier can be changed in its characteristic between transimpedance amplifier and charge amplifier. This is achieved by changing the feedback impedance. To have a good immunity to noise the receiving path consists of a symmetrical differential input.

The HALIOS<sup>®</sup> IC contains a configurable current driver interface. In the case of an optical sensor it is possible to drive up to four sending LEDs and one compensation LED. If a capacitive sensor should be realized, the current is converted into a voltage by connecting pullup resistances at the outputs LEDx. The HALIOS<sup>®</sup> measurement loop is closed by a 10 bit DAC which regulates the output current for the sending/compensation LED. The DAC is controlled by a counter that sets the DAC dependent on the received signal amplitudes up or down.

To follow fast signal changes the counter can be increased or decreased by 1, 2, 4 or 8 steps, this is called the step size that is set due to the number of up/down-counts in the same direction. To start a new measurement the interface is configured with the counter-value and the step size (generally the values from the last measurement), the LED configuration and the current configuration for the LED driver. The measurement regulates the DAC and performs 25 counter steps to follow the actual reflection conditions of the sensor. After one measurement the interface returns the counter-value, the mean-value (it is calculated from the last 16 counter-steps during one measurement) and the stepsize from the last integrator cycle.

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

| ELMOS Semiconductor AG | Data Sheet | QM-No.: 25DS0049E.02 |

|------------------------|------------|----------------------|

|------------------------|------------|----------------------|

# 16/71

Ε

# E909.06

### HALIOS<sup>®</sup> MULTI PURPOSE SENSOR FOR AUTOMOTIVE PRODUCTION DATA - NOV 16, 2011

After the automated measurement cycle is finished an interrupt appears if the interrupt is enabled. The interrupt is used to wake the system from standby mode.

The HALIOS<sup>®</sup> clock is adjustable in 5 frequencies (FSYS=8 MHz):

- 167 kHz

- 125 kHz (default)

- 100 kHz

- 83 kHz

- 71 kHz

# 4.6.3 HALIOS® Module Registers

| Register Name                            | Address | Description |

|------------------------------------------|---------|-------------|

| Start Value Counter                      | 0x00    |             |

| Measurement Configuration                | 0x02    |             |

| Measurement Configuration HALIOS® Clock  | 0x04    |             |

| Current Configuration Phase A            | 0x06    |             |

| Current Configuration Phase B            | 0x08    |             |

| Current Configuration Compensator Offset | 0x0A    |             |

| Measurement Result: Counter Value        | 0x0C    |             |

| Measurement Result: Mean Value           | 0x0E    |             |

| Interrupt                                | 0x10    |             |

| Preamplifier Configuration               | 0x12    |             |

| Send Frequency Select                    | 0x14    |             |

### Register Start Value Counter (0x00)

|                 | MSB                                                                                                                                                            |     |     |     |     |     |     |     |     |     |     |     |     |     |     | LSB |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Content         | 15:<br>12                                                                                                                                                      | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Reset value     |                                                                                                                                                                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Internal access |                                                                                                                                                                | R/W |

| External access |                                                                                                                                                                | R/W |

| Bit Description | 15:12 : STZ: Startup step size for one step of the integrator (range: "0001", "0100", "0100" or<br>"1000")<br>10 : 0 - normal settling time of optical gyrator |     |     |     |     |     |     |     |     |     |     |     |     |     | or  |     |

Table 1: Start Value Counter

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

# HALIOS® MULTI PURPOSE SENSOR FOR AUTOMOTIVE

PRODUCTION DATA - NOV 16, 2011

|                 | MSB                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                       |                                                                                                                                                               |                                                                                                                         |                                                                                                                                    |                                                                                                          |                                                                                                                                        |                                                      |        |     | LSB |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------|-----|-----|

| Content         | 15                                                                                                                                                                                                                      | 14                                                                                                                                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                                                                                                                                                                     | 8                                                                                                                                                             | 7                                                                                                                       | 6                                                                                                                                  | 5                                                                                                        | 4                                                                                                                                      | 3                                                    | 2      | 1   | 0   |

| Reset value     | 0                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                     | 0                                                                                                                                                             | 0                                                                                                                       | 0                                                                                                                                  | 0                                                                                                        | 0                                                                                                                                      | 0                                                    | 0      | 0   | 0   |

| Internal access | R/W                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                    | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W                                                                                                                                                                                                   | R/W                                                                                                                                                           | R/W                                                                                                                     | R/W                                                                                                                                | R/W                                                                                                      | R/W                                                                                                                                    | R/W                                                  | R/W    | R/W | R/W |