#### DC MOTOR 6 X HALF BRIDGE WITH SENSORLESS POSITIONING ADVANCE PRODUCT INFORMATION - MAY 05, 2011

E910.72

#### Features

- Operating supply voltage range 6V to 19V

- Tolerates automotive transients

- Standby current typ. 4μA

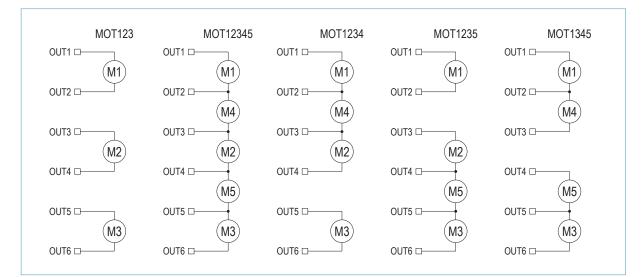

- 6 half bridges to drive 3, 4, or 5 DC motors

- $R_{DS,ON}$  of one half bridge typ. 1.25 $\Omega$

- Adjustable parameters to drive a high number of different motor types

- Output current max. 540mA per half bridge

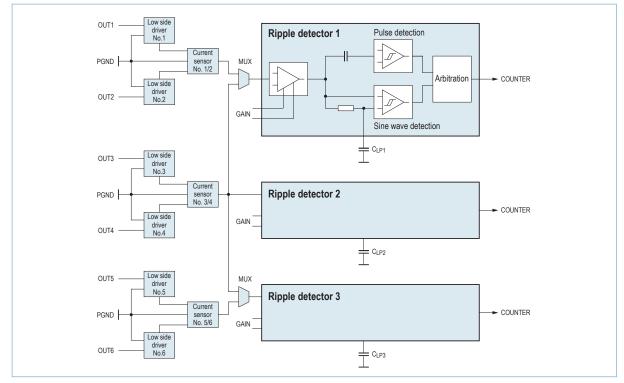

- Three independent pulse detectors and counters

- Excellent positioning performance

- Minimum external components required

- SPI for communication with μC (5V or 3.3V)

- Diagnostic data via SPI (short circuit, open loop, overtemperature, over and undervoltage)

- AEC-Q100 qualified

## **Applications**

- Automotive HVAC systems

- DC motor servo systems

## **General Description**

The E910.72 allows independent positioning of up to 5 DC motors. Pulse detection circuits convert the commutation current of the motors into countable digital signals especially for positioning of HVAC flap actuators.

Via an SPI a  $\mu$ C sends motor address, direction, and pulse count command to the device. The corresponding motor will then be driven to the desired position, and the actual number of counts is sent back to the  $\mu$ C.

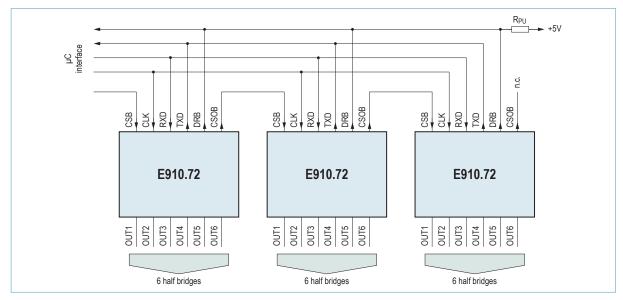

Diagnostic data such as overcurrent, overtemperature and motor stall is also transmitted via the SPI. An open drain low side output indicates when a required motor position is reached or diagnostic data is available. ICs can be connected in a daisy chain.

## **Ordering Information**

| Product ID | Temp. Range    | Package |

|------------|----------------|---------|

| E910.72    | -40°C to +85°C | QFN32L5 |

This document contains information on a new product. ELMOS Semiconductor AG reserves the right to change specifications and information herein without notice.

#### DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT ADVANCE PRODUCT INFORMATION - MAY 05, 2011

## 1 Pinout

# 1.1 Pin Description

| Pin | Name     | Type 1) | Description                                                                                                                                                  |

|-----|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CSOB     | D_O     | Chip Select Out Bar output / Daisy Chain output, active low                                                                                                  |

| 2   | DRB      | D_O     | Data Ready Bar flag output, open drain, active low                                                                                                           |

| 3   | TPIN     | D_IO    | Digital test input pin, to be connected to ground<br>Scan enable signal<br>In testmode the effective counts of the ripple detectors are visible at this pin. |

| 4   | TMODE    | D_I     | Test enable, to be connected to ground<br>Input to enter test mode, when high                                                                                |

| 5   | VDD      | S       | External 5V supply input                                                                                                                                     |

| 6   | VSS      | S       | Ground connection for analog part                                                                                                                            |

| 7   | VDDD3    | S       | Supply input for digital part<br>External 3.3V buffer capacitor or decoupling network to be connected                                                        |

| 8   | VDDA3    | S       | Internally regulated 3.3V supply output, supply input for analog part<br>External 3.3V buffer capacitor to be connected                                      |

| 9   | TANA     | AD_IO   | Test in/out analog, must not be connected<br>It should be connected to external high-input-impedance buffer during testing.                                  |

| 10  | CLP1     | A_IO    | Low pass filter capacitor for ripple detection 1                                                                                                             |

| 11  | CLP2     | A_IO    | Low pass filter capacitor for ripple detection 2                                                                                                             |

| 12  | CLP3     | A_IO    | Low pass filter capacitor for ripple detection 3                                                                                                             |

| 13  | CCP_HV   | HV_S    | External charge pump capacitor                                                                                                                               |

| 14  | N.C./GND |         | No internal connection, to be connected to ground                                                                                                            |

| 15  | VBAT_HV  | HV_S    | External battery voltage supply input for half bridge OUT1_HV                                                                                                |

| 16  | OUT1_HV  | HV_A_O  | Half bridge output OUT1_HV                                                                                                                                   |

| 17  | PGND     | S       | Power ground connection for half bridges OUT1_HV and OUT2_HV                                                                                                 |

| 18  | OUT2_HV  | HV_A_O  | Half bridge output OUT2_HV                                                                                                                                   |

| 19  | VBAT_HV  | HV_S    | External battery voltage supply input for half bridges OUT2_HV and OUT3_HV                                                                                   |

| 20  | OUT3_HV  | HV_A_O  | Half bridge output OUT3_HV                                                                                                                                   |

| 21  | PGND     | S       | Power ground connection for half bridges OUT3_HV and OUT4_HV                                                                                                 |

| 22  | OUT4_HV  | HV_A_O  | Half bridge output OUT4_HV                                                                                                                                   |

| 23  | VBAT_HV  | HV_S    | External battery voltage supply input for half bridges OUT4_HV and OUT5_HV                                                                                   |

| 24  | OUT5_HV  | HV_A_O  | Half bridge output OUT5_HV                                                                                                                                   |

| 25  | PGND     | S       | Power ground connection for half bridges OUT5_HV and OUT6_HV                                                                                                 |

| 26  | OUT6_HV  | HV_A_O  | Half bridge output OUT6_HV                                                                                                                                   |

| 27  | VBAT_HV  | HV_S    | External battery voltage supply input for half bridge OUT6_HV                                                                                                |

| 28  | N.C./GND |         | No internal connection, to be connected to ground                                                                                                            |

| 29  | CLK      | D_I     | Clock input of SPI                                                                                                                                           |

| 30  | CSB      | D_I     | Chip Select Bar input, active low                                                                                                                            |

| 31  | RXD      | D_I     | Receive data input of SPI                                                                                                                                    |

| 32  | TXD      | D_O     | Transmit data output of SPI                                                                                                                                  |

1) A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage

ELMOS Semiconductor AG

Data Sheet

#### DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT ADVANCE PRODUCT INFORMATION - MAY 05, 2011

MATION - MAT 05, 20

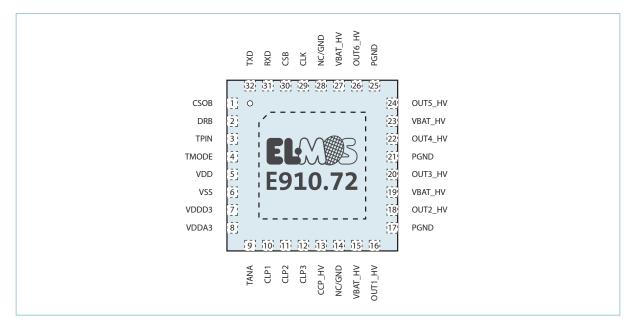

## **1.2 Pin Configuration**

Figure 1: Package pinout. Top view

#### Note:

- It is mandatory to solder the exposed pad of the package to the PCB. Otherwise the thermal performance of the package will significantly be reduced as well as the mechanical integrity of the connections between package and PCB.

- Please refer to chapter "Maximum Ratings" for further information about thermal performance of a QFN package.

#### DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT ADVANCE PRODUCT INFORMATION - MAY 05, 2011

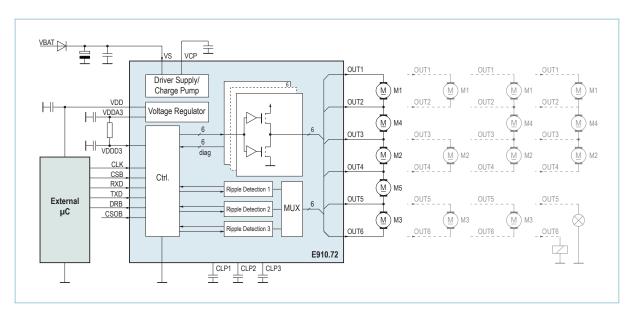

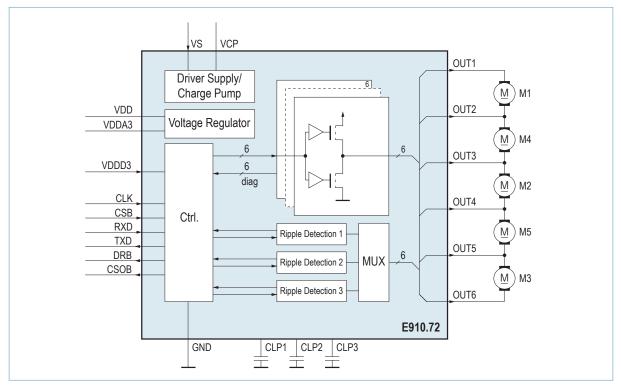

## 2 Block Diagram

Figure 2: Block diagram

| Pos. | Symbol            | Function                                                                                                                                                                          | Typ. value                             |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1    | C <sub>DD</sub>   | Bypass capacitor for 5.0V                                                                                                                                                         | 100nF (20%)                            |

| 2    | CLP1              | Capacitance for low pass filter in ripple counter 1                                                                                                                               | 47nF (20%)                             |

| 3    | C <sub>LP2</sub>  | Capacitance for low pass filter in ripple counter 2                                                                                                                               | 47nF (20%)                             |

| 4    | C <sub>LP3</sub>  | Capacitance for low pass filter in ripple counter 3                                                                                                                               | 47nF (20%)                             |

| 5    | C <sub>CCP</sub>  | Storage capacitor for charge pump                                                                                                                                                 | 47nF (20%)                             |

| 6    | C <sub>B1</sub>   | Bypass capacitor for battery supply                                                                                                                                               | 100nF (20%)                            |

| 7    | C <sub>B2</sub>   | Buffer capacitor for battery supply                                                                                                                                               | 220μF (20%)<br>or<br>470μF (20%)       |

| 8    | D <sub>1</sub>    | Diode for reverse voltage protection, It is recommended<br>to use a separate schottky diode for each E910.72 chip to<br>achieve a small voltage drop. Please also refer to 5.3.2. |                                        |

| 9    | R <sub>PU</sub>   | Pull up resistor for open drain pin DRB                                                                                                                                           | 10kΩ (20%)<br>Min. 2.2kΩ<br>Max. 100kΩ |

| 10   | C <sub>DDA3</sub> | Buffer capacitance for analog supply                                                                                                                                              | 100nF (20%)                            |

| 11   | C <sub>DDD3</sub> | Buffer capacitance for digital supply                                                                                                                                             | 100nF (20%)                            |

| 12   | R <sub>F</sub>    | Filter resistance between digital and analog supply                                                                                                                               | 1Ω (10%)                               |

#### 2.1 Recommended External Components

#### DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT ADVANCE PRODUCT INFORMATION - MAY 05, 2011

## **3 Operating Conditions**

### 3.1 Absolute Maximum Ratings

Operating the device at or beyond these limits may cause permanent damage.

All voltages are referred to ground (0V).

Currents flowing into the circuit have positive values.

| No. | Symbol                    | Condition                                           | Min. | Max.                             | Unit | Description                                                       |

|-----|---------------------------|-----------------------------------------------------|------|----------------------------------|------|-------------------------------------------------------------------|

| 1   | V <sub>bat_hv, abs</sub>  |                                                     | -0.3 | 28                               | V    | Battery supply voltage                                            |

| 2   | V_BAT_HV, ABS             | t500ms                                              | -0.3 | 40                               | V    | Battery supply voltage                                            |

| 3   | V <sub>dd, abs</sub>      |                                                     | -0.3 | 5.5                              | V    | 5V supply voltage                                                 |

| 4   | V <sub>ddd3, abs</sub>    |                                                     | -0.3 | 3.6                              | V    | 3.3V digital supply voltage                                       |

| 5   | V <sub>dda3, abs</sub>    |                                                     | -0.3 | 3.6                              | V    | 3.3V analog supply voltage                                        |

| 6   | DDA3, ABS                 |                                                     | -20  | 20                               | mA   | 3.3V analog supply output current                                 |

| 7   | $V_{HB,ABS}$              |                                                     | -0.3 | V <sub>BAT_HV</sub> +0.3         | V    | Output voltage of half bridges<br>OUT1_HVOUT6_HV                  |

| 8   | I <sub>hb, Abs</sub>      | Output<br>drivers in<br>tristate<br>mode<br>t<100µs | -100 | 100                              | mA   | Output current of half bridges<br>OUT1_HV OUT6_HV                 |

| 9   | V <sub>lvout, abs</sub>   |                                                     | -0.3 | V <sub>DD</sub> +0.3             | V    | Output voltage of low voltage outputs<br>TXD, CSOB, DRB           |

| 10  | I <sub>lvout, abs</sub>   |                                                     | -5   | 5                                | mA   | Output current of low voltage outputs<br>TXD, CSOB, DRB           |

| 11  | $V_{_{\text{LVIN, ABS}}}$ |                                                     | -0.3 | V <sub>DD</sub> +0.3             | V    | Input voltage of low voltage inputs RXD,<br>CSB, CLK, TMODE, TPIN |

| 12  | <br>LVIN, ABS             |                                                     | -10  | 10                               | mA   | Input current of low voltage inputs RXD,<br>CSB, CLK, TMODE, TPIN |

| 13  | V <sub>tana, abs</sub>    |                                                     | -0.3 | V <sub>DDA3</sub> +0.3           | V    | Voltage on test mode pin TANA                                     |

| 14  | V <sub>clp, Abs</sub>     |                                                     | -0.3 | V <sub>DDA3</sub> +0.3           | V    | Voltage on low pass filter pins CLP1CLP3                          |

| 15  | V <sub>CCP_HV, ABS</sub>  |                                                     | -0.3 | V <sub>BAT_HV</sub> +10<br>or 40 | V    | Voltage on charge pump pin CCP_HV                                 |

| 16  | P <sub>diss, abs</sub>    | T <sub>AMB</sub> ≤+85°C                             |      | 1000                             | mW   | Power dissipation                                                 |

| 17  | R <sub>tjc, abs</sub>     | QFN32L5                                             |      | 5                                | K/W  | Thermal resistance junction to case                               |

| 18  | R <sub>tjal, abs</sub>    | QFN32L5                                             |      | 80                               | K/W  | Thermal resistance junction to ambient, low conductivity          |

| 19  | R <sub>tjah, abs</sub>    | QFN32L5                                             |      | 32                               | K/W  | Thermal resistance junction to ambient, high conductivity         |

| 20  | T <sub>j, abs</sub>       |                                                     | -40  | 150                              | °C   | Junction temperature                                              |

| 21  | T <sub>stg, abs</sub>     |                                                     | -40  | 150                              | °C   | Storage temperature                                               |

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

#### **3.2 Recommended Operating Conditions**

Parameters are guaranteed within the range of recommended operating conditions unless otherwise specified. All voltages are referred to ground (0V).

Currents flowing into the circuit have positive values.

The first electrical potential connected to the IC must be GND. (If not specified specify timing sequence of electrical contacts.)

| No. | Symbol              | Condition | Min. | Тур. | Max. | Unit | Description                        |

|-----|---------------------|-----------|------|------|------|------|------------------------------------|

| 1   | V <sub>BAT_HV</sub> |           | 6    | 12   | 19   | V    | Battery supply voltage             |

| 2   | V <sub>DD</sub>     |           | 4.5  | 5.0  | 5.5  | V    | 5V supply voltage                  |

| 3   | Т <sub>амв</sub>    |           | -40  | 25   | 85   | °C   | Ambient operating tempera-<br>ture |

## **4 Detailed Electrical Specification**

#### 4.1 Supply Section

| No.  | Symbol                            | Condition                                                                  | Min. | Тур. | Max. | Unit | Description                                           |  |  |  |  |

|------|-----------------------------------|----------------------------------------------------------------------------|------|------|------|------|-------------------------------------------------------|--|--|--|--|

| Batt | Battery Supply DC Characteristics |                                                                            |      |      |      |      |                                                       |  |  |  |  |

| 1    | I<br>ВАТ                          | All outputs unloaded                                                       |      | 0.42 | 3    | mA   | Operating supply current                              |  |  |  |  |

| 2    | I <sub>bat,stby</sub>             | V <sub>DD</sub> =5.0V<br>Software standby<br>initiated by SPI com-<br>mand |      | 4.0  | 20   | uA   | Standby current <sup>1)</sup>                         |  |  |  |  |

| 3    | I <sub>BAT,PWROFF</sub>           | $V_{DD}$ =0.0V                                                             |      | 4.0  | 20   | uA   | Power-off current <sup>1)</sup>                       |  |  |  |  |

| 4    | V <sub>BAT,LOW</sub>              |                                                                            | 4.1  | 4.6  | 5.1  | V    | Undervoltage detection threshold                      |  |  |  |  |

| 5    | V <sub>bat,l,hys</sub>            |                                                                            |      | 150  |      | mV   | Undervoltage detection hysteresis                     |  |  |  |  |

| 6    | V <sub>bat,high</sub>             |                                                                            | 19   | 21.5 | 24   | V    | Overvoltage detection threshold                       |  |  |  |  |

| 7    | V <sub>bat,h,hys</sub>            |                                                                            |      | 400  |      | mV   | Overvoltage detection<br>hysteresis                   |  |  |  |  |

| Batt | Battery Supply AC Characteristics |                                                                            |      |      |      |      |                                                       |  |  |  |  |

| 1    | T <sub>debvb,ov,off</sub>         |                                                                            | 7    | 10   | 18   | ms   | Overvoltage shut-off de-<br>bounce time               |  |  |  |  |

| 2    | T <sub>debvb,ov,on</sub>          |                                                                            | 7    | 10   | 18   | ms   | Turn-on debounce time af-<br>ter overvoltage shut-off |  |  |  |  |

| 3    | T <sub>debvb,ov,off</sub>         |                                                                            | 7    | 10   | 18   | ms   | Undervoltage shut-off de-<br>bounce time              |  |  |  |  |

1) Standby and power-off current are specified for a maximum junction temperature of +85°C, assuming that the IC's power dissipation is negligible in these operating modes, so that  $T_j=T_{_{AMB^*}}$ .

ELMOS Semiconductor AG

E910.72

E910.72

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| No.   | Symbol                   | Condition                                                                | Min.                                | Тур.                       | Max.                            | Unit | Description                                 |  |  |  |  |

|-------|--------------------------|--------------------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------------|------|---------------------------------------------|--|--|--|--|

| Digi  | tal/Analog               | Supply                                                                   |                                     | <b>`</b>                   |                                 |      |                                             |  |  |  |  |

| 1     | I <sub>DD</sub>          |                                                                          |                                     | 2                          | 6                               | mA   | Operating supply current at $V_{DD}$        |  |  |  |  |

| 2     | <b> </b><br>DD,STBY      | V <sub>DD</sub> =5V<br>Software standby<br>initiated by SPI com-<br>mand |                                     | 200                        |                                 | μΑ   | Standby current at $V_{_{DD}}^{1}$          |  |  |  |  |

| 3     | V <sub>DD,LOW</sub>      |                                                                          | 2.3                                 | 2.6                        | 2.9                             | V    | Undervoltage reset                          |  |  |  |  |

| 4     | V <sub>dda3</sub>        | I <sub>DDA3</sub> =-10mA                                                 | 3                                   | 3.3                        | 3.6                             | V    | VDDA3 regulator output<br>voltage           |  |  |  |  |

| Ove   | Overtemperature Shut-Off |                                                                          |                                     |                            |                                 |      |                                             |  |  |  |  |

| 1     | Τ <sub>so</sub>          | Referred to junction temperature                                         | 150                                 |                            |                                 | °C   | Overtemperature shut-off threshold          |  |  |  |  |

| 2     | Τ <sub>ΗΥS</sub>         |                                                                          |                                     | 20                         |                                 | °C   | Overtemperature turn-on<br>hysteresis       |  |  |  |  |

| Seria | al Periphera             | al Interface, SPI DC                                                     | Characte                            | eristics                   |                                 |      |                                             |  |  |  |  |

| 1     | V <sub>IL</sub>          |                                                                          | 0.0                                 |                            | 1.5                             | V    | Input low voltage<br>Pins CLK, CSB, RXD     |  |  |  |  |

| 2     | V <sub>IH</sub>          |                                                                          | V <sub>DD</sub> -1                  |                            | VDD                             | V    | Input high voltage<br>Pins CLK, CSB, RXD    |  |  |  |  |

| 3     | R <sub>PD</sub>          | Tested at $V_{IN} = V_{DD}$                                              |                                     | 125                        |                                 | kΩ   | Pulldown resistance<br>Pins CLK, RXD        |  |  |  |  |

| 4     | R <sub>PU</sub>          | Tested at V <sub>IN</sub> =0.0V                                          |                                     | 125                        |                                 | kΩ   | Pullup resistance<br>Pin CSB                |  |  |  |  |

| 5     | V <sub>out,l</sub>       | I <sub>ou⊤</sub> =0.5mA<br>V <sub>DD</sub> =4.5V                         |                                     | 0.3                        | 0.5                             | V    | Low output voltage<br>Pins TXD, CSOB        |  |  |  |  |

| 6     | V <sub>out,h</sub>       | I <sub>out</sub> =-0.5mA<br>V <sub>DD</sub> =4.5V                        | V <sub>DD</sub><br>(t.b.d.)-<br>0.6 | V <sub>DD</sub> -0.4       |                                 | V    | High output voltage<br>Pins TXD, CSOB       |  |  |  |  |

| 7     | V <sub>out,l</sub>       | I <sub>оит</sub> =0.5mA<br>V <sub>DD</sub> =4.5V                         |                                     | 0.3                        | 0.5                             | V    | Low output voltage<br>Pin DRB (open drain)  |  |  |  |  |

| 8     | I <sub>leak</sub>        | DRB not active                                                           | -2                                  | 0.0                        | +2                              | μΑ   | Leakage current<br>Pin DRB (open drain)     |  |  |  |  |

| Seria | al Periphera             | al Interface, SPI AC                                                     | Characte                            | eristics                   |                                 |      |                                             |  |  |  |  |

| 1     | t <sub>spi,clkper</sub>  |                                                                          | 0.5                                 |                            | 1000                            | μs   | Clock period<br>Pin CLK                     |  |  |  |  |

| 2     | t <sub>sl</sub>          |                                                                          |                                     |                            | no limit                        | -    | Slope time<br>Pin CLK                       |  |  |  |  |

| 3     | t <sub>spi,CLKH</sub>    |                                                                          | 100                                 | t <sub>spi,clkper</sub> /2 | t <sub>spi,clkper</sub><br>-100 | ns   | High time<br>Pin CLK                        |  |  |  |  |

| 4     | t <sub>sl</sub>          |                                                                          |                                     |                            | no limit                        | -    | Slope time<br>Pins CSB, RXD                 |  |  |  |  |

| 5     | t <sub>sl,R</sub>        | 10%-90%<br>Cլ=10pF                                                       |                                     | 15                         | 30                              | ns   | Output rising slope time<br>Pins TXD, CSOB  |  |  |  |  |

| 6     | t <sub>sl,F</sub>        | 10%-90%<br>C <sub>L</sub> =10pF                                          |                                     | 15                         | 30                              | ns   | Output falling slope time<br>Pins TXD, CSOB |  |  |  |  |

| 7     | t <sub>sl,R,DRB</sub>    | 10%-90%<br>C <sub>L</sub> =10pF<br>R <sub>PU</sub> =10kΩ                 |                                     | 250                        |                                 | ns   | Output rising slope time<br>Pin DRB         |  |  |  |  |

# DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| No.  | Symbol                | Condition                                                   | Min.              | Тур.                       | Max.                        | Unit | Description                                                               |

|------|-----------------------|-------------------------------------------------------------|-------------------|----------------------------|-----------------------------|------|---------------------------------------------------------------------------|

| 8    | t <sub>sl,f,DRB</sub> | 10%-90%<br>C <sub>L</sub> =10pF<br>R <sub>PU</sub> =10kΩ    |                   | 15                         | 30                          | ns   | Output falling slope time<br>Pin DRB                                      |

| 9    | t <sub>spi,su</sub>   |                                                             | 100               | t <sub>spi,clkper</sub> /2 |                             | ns   | Setup time RXD before ris-<br>ing CLK                                     |

| 10   | t <sub>spi,ho</sub>   |                                                             | 100               | t <sub>spi,clkper</sub> /2 |                             | ns   | Hold time RXD after rising<br>CLK                                         |

| 11   | t <sub>spi,csb</sub>  |                                                             | 100               | t <sub>spi,clkper</sub> /2 |                             | ns   | Time before and after clock cycles, when CSB must be active               |

| 12   | t <sub>spi,txdd</sub> |                                                             |                   |                            | 50                          | ns   | Output delay of TXD after<br>CLK and CSB                                  |

| 13   | t <sub>rdy</sub>      |                                                             | 5                 | 10                         | 30                          | ms   | Ready time when leaving<br>standby mode for activating<br>the charge pump |

| Mot  | or Driver H           | alf Bridges DC Char                                         | acteristi         | cs                         |                             |      |                                                                           |

| 1    | V <sub>IN,REV</sub>   |                                                             | -0.3              |                            | V <sub>BAT_HV</sub><br>+0.3 | V    | Input voltage                                                             |

| 2    | R <sub>on,12</sub>    | V <sub>BAT_HV</sub> =12V<br> I <sub>outx</sub> =220mA       |                   | 1.25                       | 2.5                         | Ω    | On resistance                                                             |

| 3    | I <sub>LEAK,0</sub>   | V <sub>OUTx_HV</sub> =0V                                    | -5                | 0                          | 5                           | μΑ   | Leakage current in tristate mode                                          |

| 4    | I <sub>leak,18</sub>  | V <sub>BAT_HV</sub> =18V<br>V <sub>OUTx HV</sub> =18V       |                   | 100                        |                             | μΑ   | Input current in tristate mode                                            |

| 5    | I <sub>lim,H</sub>    | V <sub>BAT_HV</sub> =12V                                    | -1200<br>(t.b.d.) | -800<br>(t.b.d.)           | -550                        | mA   | High side current limitation                                              |

| 6    | I <sub>lim,l</sub>    | V <sub>BAT_HV</sub> =12V                                    | 550               | 800<br>(t.b.d.)            | 1200<br>(t.b.d.)            | mA   | Low side current limitation                                               |

| Mot  | or Driver Ha          | alf Bridges AC Char                                         | acteristi         | CS                         |                             |      |                                                                           |

| 1    | d <sub>von/dt</sub>   | 20%-80% V $_{\rm BAT}$ R $_{\rm LOAD}$ =50 $\Omega$ to PGND | 0.25              | 0.6                        | 1.1                         | V/µs | Turn on slew rate                                                         |

| 2    | d <sub>voff/dt</sub>  | 20%-80% V $_{\rm BAT}$ R $_{\rm LOAD}$ =50 $\Omega$ to PGND | -1.1              | -0.6                       | -0.25                       | V/µs | Turn off slew rate                                                        |

| 3    | t <sub>so,oc1</sub>   |                                                             |                   | 500                        |                             | μs   | Overcurrent shut-off debounce time                                        |

| Posi | tioning By <i>l</i>   | Means Of Ripple De                                          | etection          | DC Charac                  | teristics                   |      |                                                                           |

| 1    | I <sub>MOT</sub>      | Gain=11 <sub>b</sub><br>NonLin=01 <sub>b</sub>              | -15               |                            | 200                         | mA   | Motor current input range                                                 |

| 2    | I <sub>MOT</sub>      | Gain=10 <sub>b</sub><br>NonLin=10                           | -23               |                            | 320                         | mA   | Motor current input range                                                 |

| 3    | I <sub>мот</sub>      | Gain=01 <sub>b</sub><br>NonLin=11 <sub>b</sub>              | -37               |                            | 540                         | mA   | Motor current input range                                                 |

| 4    | I <sub>MOT</sub>      | Gain=11 <sub>b</sub><br>NonLin=11 <sub>b</sub>              | -15               |                            | 540                         | mA   | Motor current input range                                                 |

| 5    | I <sub>MOT</sub>      | Gain=10 <sub>b</sub><br>NonLin=11 <sub>b</sub>              | -23               |                            | 540                         | mA   | Motor current input range                                                 |

| 6    | I <sub>MOT,GT7P</sub> | Gain=11 <sub>b</sub><br>NonLin=01 <sub>b</sub>              | 2                 | 10                         | 30                          | mA   | Open load detection<br>threshold                                          |

## DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| No.  | Symbol              | Condition                                                                                                                                                                                                                                                                                                        | Min.      | Тур.       | Max.      | Unit   | Description                                                     |

|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----------|--------|-----------------------------------------------------------------|

| Amp  | olitude Thre        | shold For Pulses To                                                                                                                                                                                                                                                                                              | Be Dete   | cted By Pu | Ise Dete  | ector  | ·                                                               |

| 1    | I <sub>dr,neg</sub> | $\begin{array}{c} \text{Gain=11}_{\text{b}} \\ \text{NonLin=01}_{\text{b}} \\ \text{PulseTh=011}_{\text{b}} \\ \text{PulseT=010}_{\text{b}} \\ \\ \text{I}_{\text{MOT,DC}} = 10\text{mA} \\ \text{Max. } t_{\text{FALL}} = 20 \mu\text{s} \\ \text{Min. } t_{\text{PULSEWIDTH}} = 150 \mu\text{s} \end{array}$   |           |            | 1.8       | mA     | Threshold of negative cur-<br>rent drop amplitude <sup>1)</sup> |

| 2    | I <sub>DR,NEG</sub> | $\begin{array}{c} \text{Gain=10}_{\text{b}} \\ \text{NonLin=10}_{\text{b}} \\ \text{PulseTh=011}_{\text{b}} \\ \text{PulseT=010}_{\text{b}} \\ \\ \text{I}_{\text{MOT,DC}} = 16\text{mA} \\ \text{Max. } t_{\text{FALI}} = 20 \mu \text{s} \\ \text{Min. } t_{\text{PULSEWIDTH}} = 150 \mu \text{s} \end{array}$ |           |            | 2.8       | mA     | Threshold of negative cur-<br>rent drop amplitude <sup>1)</sup> |

| 3    | I <sub>dr,neg</sub> | Gain=01 <sub>b</sub><br>NonLin=11 <sub>b</sub><br>PulseTh=011 <sub>b</sub><br>PulseT=010 <sub>b</sub><br>$I_{MOT,DC}=27mA$<br>Max. $t_{FALL}=20\mu s$<br>Min. $t_{PULSEWIDTH}=150\mu s$                                                                                                                          |           |            | 4.3       | mA     | Threshold of negative cur-<br>rent drop amplitude <sup>1)</sup> |

| 4    | t <sub>PL</sub>     | PulseT=010 <sub>b</sub>                                                                                                                                                                                                                                                                                          |           | 100        |           | μs     | Pulse width threshold for pulses to be detected <sup>1)</sup>   |

| Min. | Peak-Peak           | -Value Threshold O                                                                                                                                                                                                                                                                                               | f Sine Wa | ave Signal | s To Be D | etecte | ed By Sine Wave Detector                                        |

| 1    | I <sub>sin,pp</sub> | Gain=11 <sub>b</sub><br>NonLin=01 <sub>b</sub><br>I <sub>MOT,DC</sub> =10mA<br>f <sub>SIN</sub> =70Hz                                                                                                                                                                                                            |           |            | 1.7       | mA     | Threshold of sinusoidal peak-peak current <sup>2)</sup>         |

| 2    | <br>SIN,PP          | Gain=10 <sub>b</sub><br>NonLin=10 <sub>b</sub><br>I <sub>MOT,DC</sub> =16mA<br>f <sub>SIN</sub> =70Hz                                                                                                                                                                                                            |           |            | 2.4       | mA     | Threshold of sinusoidal peak-peak current <sup>2)</sup>         |

| 3    | <br>sin,pp          | Gain=01 <sub>b</sub><br>NonLin=11 <sub>b</sub><br>I <sub>MOT,DC</sub> =27mA<br>f <sub>SIN</sub> =70Hz                                                                                                                                                                                                            |           |            | 4         | mA     | Threshold of sinusoidal peak-peak current 2)                    |

1) Pulse current variations above the maximum values are mandatory for a safe operation. The listed maximum values are detector threshold values of the respective conditions. Otherwise a functionality of the pulse detector could not be guaranteed by ELMOS.

2) Sinusoidal peak-peak current variations above the maximum values are mandatory for a safe operation. The listed maximum values are detector threshold values of the respective conditions. Otherwise a functionality of the sine detector could not be guaranteed by ELMOS.

| No.                  | Symbol                | Condition                          | Min. | Тур. | Max. | Unit | Description                        |  |  |

|----------------------|-----------------------|------------------------------------|------|------|------|------|------------------------------------|--|--|

| Motor control timing |                       |                                    |      |      |      |      |                                    |  |  |

| 1                    | t <sub>off,ar</sub>   | Switch drivers to<br>tristate mode | 70   | 100  | 160  | ms   | Turn off delay after last<br>pulse |  |  |

| 2                    | t <sub>br,stall</sub> | Both low side tran-<br>sistors on  | 140  | 200  | 320  | ma   | Break delay after motor stall      |  |  |

## **5** Functional Description

#### 5.1 Supply Section

The device is powered by two supply voltages, VBAT\_HV and VDD. VBAT\_HV is the battery voltage behind a reverse protection diode, and VDD is the digital 5.0V supply, also needed for several analog functions. Both voltages are monitored internally.

From the 5.0V VDD supply input, a 3.3V supply voltage is generated by an internal linear voltage regulator. The pin VDDA3 represents the output of the regulator and at the same the supply for the analog part of the IC. An external buffer capacitor CVDDA3 shall be connected to VDDA3. The pin VDDD3 represents the supply for the digital part of the IC and shall be connected to VDDA3 by an external decoupling network, consisting of a resistor RF and a second buffer capacitor CVDDD3.

For all outputs in motor control mode, in case of an overvoltage or undervoltage on VBAT\_HV, all outputs are switched into brake mode (low side drivers on). Ripple detection is still performed as long as VDD is present. All outputs, which are driving other loads than motors, are only switched off in case of overvoltage.

When VDD drops below the low voltage threshold all outputs are switched to tristate (high impedance) mode to avoid destruction in case of a short circuit. The internal charge pump will be turned off, and the device draws only standby current IBAT,STBY from the VBAT\_HV supply.

When VDD is present, a standby mode for both VBAT\_HV and VDD can be activated via an SPI telegram (see chapter 5.2.17).

VBAT\_HV and VDD may be turned on and off in any sequence.

#### 5.2 Serial Peripheral Interface, SPI

#### 5.2.1 Power-On Command Sequence Of The IC

After power-on, the IC starts in standby mode. The first commands sent to the E910.72 have to define the configuration register and read and acknowledge the diagnostic error data. Otherwise the E910.72 stays in "Hardware-Error" mode, i.e., signal DRB is pulled down. The idea is, that if the configuration registers become corrupt or reset (during normal operation), it will be indicated by low DRB due to "Hardware-Error" mode.

The activation can be done in the following scheme:

1.Send "Wake up and read status" command to leave the standby mode of the IC.

2.Wait the ready time t<sub>RDY</sub> after leaving the standby to allow the charge pump to power up. During this time all commands are ignored. The IC enters the error mode "Command overflow", if commands other than "NOP" commands are sent to the IC during this time.

3.Write the two configuration registers with proper values. !!!

4.Read out hardware error ("Configuration register error").

5. Acknowledge the hardware error, i.e. acknowledge that the configuration registers were not okay. The DRB signal now goes high.

6.The IC is now properly activated and can receive further commands.

Please refer chapter 5.2.21 for example commands.

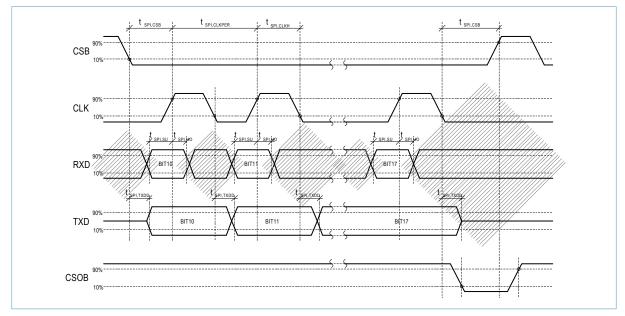

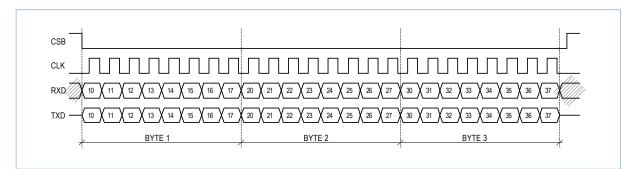

Data from and to the  $\mu$ C is transferred by means of an SPI. Received data is translated into switching commands for all half bridge outputs, and into positioning information, in case of motor control. A single data telegram from the  $\mu$ C may consist of 1 byte or 3 bytes. 1 byte information is used to turn an individual output on or off, 3 bytes information is necessary to move a motor into a defined direction with a given number of commutation ripples. To stop a motor which is still moving takes a 1 byte command as well.

As shown in Fig. 3, to start a data transmission the input signal CSB (Chip Select Bar) first has to be pulled low. Synchronised by a clock signal on CLK data is transferred into a shift register in the IC. The first bit of the data stream defines whether a 1 byte or a 3 byte information will be sent. After the appropriate number of bits has been received the shift register is stopped, and the output CSOB (Chip Select Out Bar) is pulled low, which can be seen at last falling edge of clock CLK. This signal can be used to activate the next IC in a daisy chain cascaded configuration. Again the first bit of the following data stream defines whether a 1 byte or a 3 byte information will be sent to the next IC.

Status data, position information of a motor that has been moved as well as hardware error information like overcurrent or overtemperature are available on output pin TXD. At the rising edge of clock CLK the data and TXD and RXD are valid and can be sampled. The bit transmission of TXD and RXD occurs simultaneously. The telegram length is defined by the leading bit no. 10 transferred to RXD and may be 1 byte or 3 bytes. The first byte carries diagnostic information while the second and third byte, in case of position mode, consist of motor address, direction and actual number of ripple pulses to be counted during motor movement. In case of an hardware error they contain overcurrent, overtemperature, voltage error or other diagnostic information.

Be aware, that the maximum possible request for motor position is 2047 (211-1). But in this case an overflow in the results appears, due to additional pulses in the brake phase of the motor. Therefore the maximum recommended request for motor position is 2037, supposing not more than 10 pulses in the brake mode.

Also be aware, that the minimum possible request for a motor position is 1. The value 0 for a motor drive command is not allowed.

| ELMOS Semiconductor AG | Data Sheet | QM-No.: 25DS0057E.00 |

|------------------------|------------|----------------------|

|                        |            |                      |

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT

Figure 3: SPI timing for 1-byte transfer, transmission starts with CSB

**Note:** On the rising edge of CLK, driven by  $\mu$ C, the transfer data RXD and TXD are valid and can be sampled.

To read data from the IC without changing any output state the  $\mu$ C can send a telegram with the address 000b. The available data, with a length defined by the leading bit of the  $\mu$ C's telegram, will be output on pin TXD.

The output DRB "Data Ready Bar" indicates that data is available. It may be diagnostic information and/or position information of a motor after it has been stopped.

Figure 4: SPI timing for 1-byte transfer, transmission starts with CSB

Transmission in both directions starts with bit 10 and ends with bit 37.

| FIMOS   | Semicon | ductor AG |

|---------|---------|-----------|

| LLINIOJ | Junicon | uuctor AG |

E910.72

## DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| Bit No.                                                                    | Bit Name        | Description                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte No. 1 Of RXD Data In Case Of Direct Half Bridge Control <sup>1)</sup> |                 |                                                                                                                                                                                                                                       |

| 10                                                                         | Selection       | 0 <sub>b</sub> : Direct control of half bridges<br>Length of telegram is 1 byte                                                                                                                                                       |

| 11                                                                         | SwitchStop      | $0_b$ : Output goes low<br>$1_b$ : Output goes high                                                                                                                                                                                   |

| 12                                                                         | ErrPos          | $0_b$ : Position data of motor will be read in case of a 3 byte telegram $1_b$ : Hardware error will be read in case of a 3 byte telegram<br>In case of a 1 byte telegram, the content of this bit does not care                      |

| 13                                                                         | Acknowledge     | $1_{b}$ : Reset either of error or position information, depending on bit 12                                                                                                                                                          |

| 14                                                                         | Address[2]      | MSB of half bridge address                                                                                                                                                                                                            |

| 15                                                                         | Address[1]      | Second bit of half bridge address                                                                                                                                                                                                     |

| 16                                                                         | Address[0]      | LSB of half bridge address                                                                                                                                                                                                            |

| 17                                                                         | Parity          | Odd parity of first byte<br>Content 00000000 <sub>b</sub> or 11111111 <sub>b</sub> leads to parity error                                                                                                                              |

| Byte No. 1                                                                 | 1 Of RXD Data I | n Case Of Direct Half Motor Control <sup>2)</sup>                                                                                                                                                                                     |

| 10                                                                         | Selection       | 1 <sub>b</sub> : Motor control<br>Length of telegram is 3 bytes if bit 11 is 0 <sub>b</sub><br>Length of telegram is 1 byte if bit 11 is 1 <sub>b</sub>                                                                               |

| 11                                                                         | SwitchStop      | $1_{\mathbf{b}}$ : Motor with the following address will be stopped, length of telegram is $1$ byte                                                                                                                                   |

| 12                                                                         | ErrPos          | 0 <sub>b</sub> : Position data of motor will be read in case of a 3 byte telegram<br>1 <sub>b</sub> : Hardware error will be read in case of a 3 byte telegram<br>In case of a 1 byte telegram, the content of this bit does not care |

| 13                                                                         | Acknowledge     | $1_{b}$ : Reset either of error or position information, depending on bit 12                                                                                                                                                          |

| 14                                                                         | Address[2]      | MSB of address of motor to be controlled. This address is independent of the motor adress to be read out in 5.2.12                                                                                                                    |

| 15                                                                         | Address[1]      | Second bit of address of motor to be controlled. This address is independent of the motor adress to be read out in 5.2.12                                                                                                             |

| 16                                                                         | Address[0]      | LSB of address of motor to be controlled. This address is independent of the motor adress to be read out in 5.2.12                                                                                                                    |

| 17                                                                         | Parity          | Odd parity of first byte<br>Content 00000000 <sub>b</sub> or 11111111 <sub>b</sub> leads to parity error                                                                                                                              |

## 5.2.2 Data Received From $\mu$ C, Input RXD

1) Telegram ends after bit 17

2) Telegram ends after bit 17, if bit 11 is  $1_{b}$

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| Bit No.   | Bit Name         | Description                                                                                                                              |

|-----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Bytes No: | s. 2 And 3 Of RX | D Data In Case Of Motor Control <sup>3)</sup>                                                                                            |

| 20        | Direction        | $0_b$ : Half bridge with the lower number is switched to high level $1_b$ : Half bridge with the higher number is switched to high level |

| 21        | Position[10]     | MSB of position command (2 <sup>10</sup> )                                                                                               |

| 22        | Position[9]      | 2 <sup>nd</sup> bit of position command (2 <sup>9</sup> )                                                                                |

| 23        | Position[8]      | 3 <sup>rd</sup> bit of position command (2 <sup>8</sup> )                                                                                |

| 24        | Position[7]      | 4 <sup>th</sup> bit of position command (2 <sup>7</sup> )                                                                                |

| 25        | Position[6]      | 5 <sup>th</sup> bit of position command (2 <sup>6</sup> )                                                                                |

| 26        | Position[5]      | 6 <sup>th</sup> bit of position command (2 <sup>5</sup> )                                                                                |

| 27        | Parity           | Odd parity of second byte<br>Content 0000000b or 1111111b leads to parity error                                                          |

| 30        | Position[4]      | 7 <sup>th</sup> bit of position command (2 <sup>4</sup> )                                                                                |

| 31        | Position[3]      | 8 <sup>th</sup> bit of position command (2 <sup>3</sup> )                                                                                |

| 32        | Position[2]      | 9 <sup>th</sup> bit of position command (2 <sup>2</sup> )                                                                                |

| 33        | Position[1]      | 10 <sup>th</sup> bit of position command (2 <sup>1</sup> )                                                                               |

| 34        | Position[0]      | LSB of position command (2°)                                                                                                             |

| 35        | reserved         |                                                                                                                                          |

| 36        | reserved         |                                                                                                                                          |

| 37        | Parity           | Odd parity of third byte<br>Content 00000000 <sub>b</sub> or 1111111 <sub>b</sub> leads to parity error                                  |

| 3 Bytes C | onfiguration Re  | gister No. 1 <sup>4)</sup>                                                                                                               |

| 10        | Selection        |                                                                                                                                          |

| 11        | SwitchStop       | 0 <sub>b</sub>                                                                                                                           |

| 12        | Write/Read       | $0_b$ : Configuration register is read by external $\mu$ C<br>$1_b$ : Configuration register is read and overwritten by external $\mu$ C |

| 13        | Acknowledge      |                                                                                                                                          |

| 14        | Address[2]       | 1 <sub>b</sub> , MSB of address of configuration register no.1 (110 <sub>b</sub> )                                                       |

| 15        | Address[1]       | $1_{b'}$ second bit of address of configuration register no.1 (110 <sub>b</sub> )                                                        |

| 16        | Address[0]       | 0 <sub>b</sub> , LSB of address of configuration register no.1 (110 <sub>b</sub> )                                                       |

| 17        | Parity           | Odd parity of first byte<br>Content 00000000 <sub>b</sub> or 11111111 <sub>b</sub> leads to parity error                                 |

| 20        | GainNorm[1]      | MSB of gain of selected ripple counter(s) in normal mode                                                                                 |

| 21        | GainNorm[0]      | LSB of gain of selected ripple counter(s) in normal mode                                                                                 |

| 22        | GainBreak[1]     | MSB of gain of selected ripple counter(s) in break mode                                                                                  |

| 23        | GainBreak[0]     | LSB of gain of selected ripple counter(s) in break mode                                                                                  |

| 24        | PulsThNorm[2]    | MSB of pulse detector threshold of selected ripple counter(s) in normal mode                                                             |

| 25        | PulsThNorm[1]    | Second bit of pulse detector threshold of selected ripple counter(s) in normal mode                                                      |

| 26        | PulsThNorm[0]    | LSB of pulse detector threshold of selected ripple counter(s) in normal mode                                                             |

| 27        | Parity           | Odd parity of second byte<br>Content 00000000 <sub>b</sub> or 11111111 <sub>b</sub> leads to parity error                                |

| 30        | PulsThBreak[2]   | MSB of pulse detector threshold of selected ripple counter(s) in break mode                                                              |

3) Telegram ends after bit 37

4) Telegram ends after bit 37

ELMOS Semiconductor AG

# DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| Bit No.   | Bit Name        | Description                                                                                                                                                                                                                                                                                                             |

|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31        | PulsThBreak[1]  | Second bit of pulse detector threshold of selected ripple counter(s) in break mode                                                                                                                                                                                                                                      |

| 32        | PulsThBreak[0]  | LSB of pulse detector threshold of selected ripple counter(s) in break mode                                                                                                                                                                                                                                             |

| 33        | reserved        |                                                                                                                                                                                                                                                                                                                         |

| 34        | reserved        |                                                                                                                                                                                                                                                                                                                         |

| 35        | MotorSel[1]     | MSB of motor controller select bits<br>$00_b$ : Configuration data valid for all motor control registers<br>$01_b$ : Configuration data valid for motor control register no.1<br>$10_b$ : Configuration data valid for motor control register no.2<br>$11_b$ : Configuration data valid for motor control register no.3 |

| 36        | MotorSel[0]     | LSB of motor controller select bits                                                                                                                                                                                                                                                                                     |

| 37        | Parity          | Odd parity of third byte<br>Content 00000000 <sub>b</sub> or 11111111 <sub>b</sub> leads to parity error                                                                                                                                                                                                                |

| 3 Bytes C | onfiguration Re | gister No. 2 ⁵)                                                                                                                                                                                                                                                                                                         |

| 10        | Selection       | 1 <sub>b</sub>                                                                                                                                                                                                                                                                                                          |

| 11        | SwitchStop      | 0 <sub>b</sub>                                                                                                                                                                                                                                                                                                          |

| 12        | Write/Read      | $0_b$ : Configuration register is read by external $\mu$ C<br>$1_b$ : Configuration register is read and overwritten by external $\mu$ C                                                                                                                                                                                |

| 13        | Acknowledge     |                                                                                                                                                                                                                                                                                                                         |

| 14        | Address[2]      | 1 <sub>b</sub> , MSB of address of configuration register no.2 (111 <sub>b</sub> )                                                                                                                                                                                                                                      |

| 15        | Address[1]      | $1_{b}$ , second bit of address of configuration register no.2 (111 $_{b}$ )                                                                                                                                                                                                                                            |

| 16        | Address[0]      | 1 <sub>b</sub> , LSB of address of configuration register no.2 (111 <sub>b</sub> )                                                                                                                                                                                                                                      |

| 17        | Parity          | Odd parity of first byte<br>Content 00000000 <sub>b</sub> or 1111111 <sub>b</sub> leads to parity error                                                                                                                                                                                                                 |

| 20        | NonLinNorm[1]   | MSB of nonlinear shape function of selected ripple counter(s) in normal mode                                                                                                                                                                                                                                            |

| 21        | NonLinNorm[0]   | LSB of nonlinear shape function of selected ripple counter(s) in normal mode                                                                                                                                                                                                                                            |

| 22        | NonLinBreak[1]  | MSB of nonlinear shape function of selected ripple counter(s) in break mode                                                                                                                                                                                                                                             |

| 23        | NonLinBreak[0]  | LSB of nonlinear shape function of selected ripple counter(s) in break mode                                                                                                                                                                                                                                             |

| 24        | PulsTNorm[2]    | MSB of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in normal mode                                                                                                                                                                                                                 |

| 25        | PulsTNorm[1]    | Second bit of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in normal mode                                                                                                                                                                                                          |

| 26        | PulsTNorm[0]    | LSB of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in normal mode                                                                                                                                                                                                                 |

| 27        | Parity          | Odd parity of second byte<br>Content 00000000 <sub>b</sub> or 1111111 <sub>b</sub> leads to parity error                                                                                                                                                                                                                |

| 30        | PulsTBreak[2]   | MSB of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in break mode                                                                                                                                                                                                                  |

| 31        | PulsTBreak[1]   | Second bit of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in break mode                                                                                                                                                                                                           |

| 32        | PulsTBreak[0]   | LSB of minimum pulse width to be detected as regular pulse of selected ripple counter(s) in break mode                                                                                                                                                                                                                  |

| 33        | reserved        |                                                                                                                                                                                                                                                                                                                         |

| 34        | reserved        |                                                                                                                                                                                                                                                                                                                         |

5) Telegram ends after bit 37

ELMOS Semiconductor AG

# DC MOTOR 6 X HALF BRIDGE WITH RIPPLE COUNT

ADVANCE PRODUCT INFORMATION - MAY 05, 2011

| Bit No. | Bit Name    | Description                                                                                                                                                                                                                                                                                                             |  |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 35      | MotorSel[1] | MSB of motor controller select bits<br>$00_b$ : Configuration data valid for all motor control registers<br>$01_b$ : Configuration data valid for motor control register no.1<br>$10_b$ : Configuration data valid for motor control register no.2<br>$11_b$ : Configuration data valid for motor control register no.3 |  |

| 36      | MotorSel[0] | LSB of motor controller select bits                                                                                                                                                                                                                                                                                     |  |

| 37      | Parity      | Odd parity of third byte<br>Content 00000000 <sub>b</sub> or 1111111 <sub>b</sub> leads to parity error                                                                                                                                                                                                                 |  |

| Address Bits     | SwitchStop Bit | Selection Bit = 0 <sub>b</sub> (Direct Half Bridge<br>Control) | Selection Bit = 1 <sub>b</sub> (Motor Control) |

|------------------|----------------|----------------------------------------------------------------|------------------------------------------------|

| Address Co       | rrelation 6)   |                                                                |                                                |

| 001 <sub>b</sub> | 0,             | OUT1_HV = Low                                                  | Motor 1 (OUT1_HV - OUT2_HV)                    |

| 001 <sub>b</sub> | 1,             | OUT1_HV = High                                                 | Stop motor 1                                   |

| 010,             | 0,             | OUT2_HV = Low                                                  | Motor 2 (OUT3_HV - OUT4_HV)                    |

| 010,             | 1,             | OUT2_HV = High                                                 | Stop motor 2                                   |

| 011,             | 0,             | OUT3_HV = Low                                                  | Motor 3 (OUT5_HV - OUT6_HV)                    |

| 011              | 1 <sub>b</sub> | OUT3_HV = High                                                 | Stop motor 3                                   |

| 100 <sub>b</sub> | 0,             | OUT4_HV = Low                                                  | Motor 4 (OUT2_HV - OUT3_HV)                    |

| 100 <sub>b</sub> | 1,             | OUT4_HV = High                                                 | Stop motor 4                                   |

| 101 <sub>b</sub> | 0,             | OUT5_HV = Low                                                  | Motor 5 (OUT4_HV - OUT5_HV)                    |

| 101 <sub>b</sub> | 1 <sub>b</sub> | OUT5_HV = High                                                 | Stop motor 5                                   |

| 110 <sub>b</sub> | 0,             | OUT6_HV = Low                                                  | Configuration register no.1                    |

| 110 <sub>b</sub> | 1,             | OUT6_HV = High                                                 | Invalid address, no reaction                   |

| 111 <sub>b</sub> | 0,             | Standby mode                                                   | Configuration register no.2                    |

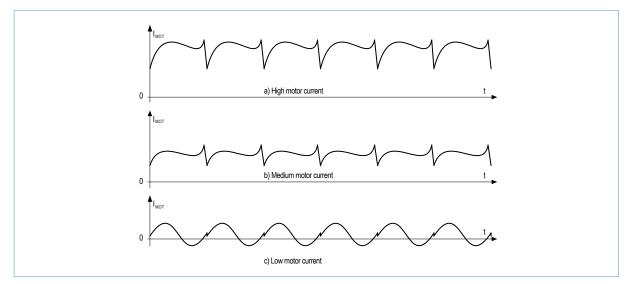

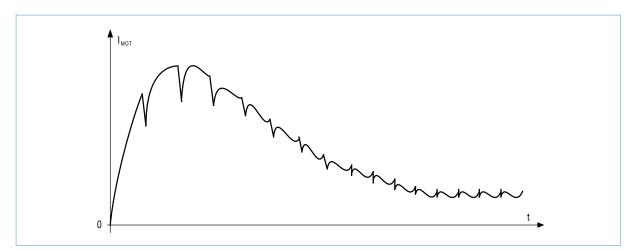

| 111 <sub>b</sub> | 1,             | Software reset                                                 | Software reset                                 |