## Supertex inc.

## Six-Channel LED Driver with Integrated Fault Protection

### **Features**

- Drives six strings of LEDs, up to 30mA each

- Phased PWM dimming

- Pin-programmable dimming frequency or synchronizable to an external signal

- PWM dimming to very low duty cycles

- ±1.5% typical current and 0.5% duty cycle matching

- Optional crystal oscillator for precision dimming frequency

- Outputs rated to 56V

- Robust protection against under voltage, over voltage, open/shorted strings, over current, and over temperature. Good strings remain lit.

- Programmable boost converter frequency

- 10µA maximum input current in shutdown state

- Resistor-programmable full-scale LED current

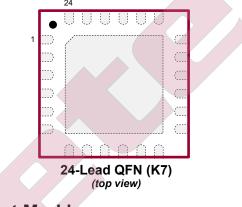

- 24-Lead 4×4 QFN package

### **Applications**

- Multi-string solid-state lighting applications

- Portable LED backlighting applications

### **General Description**

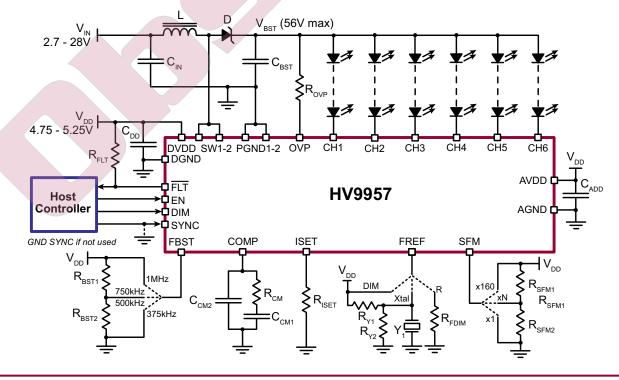

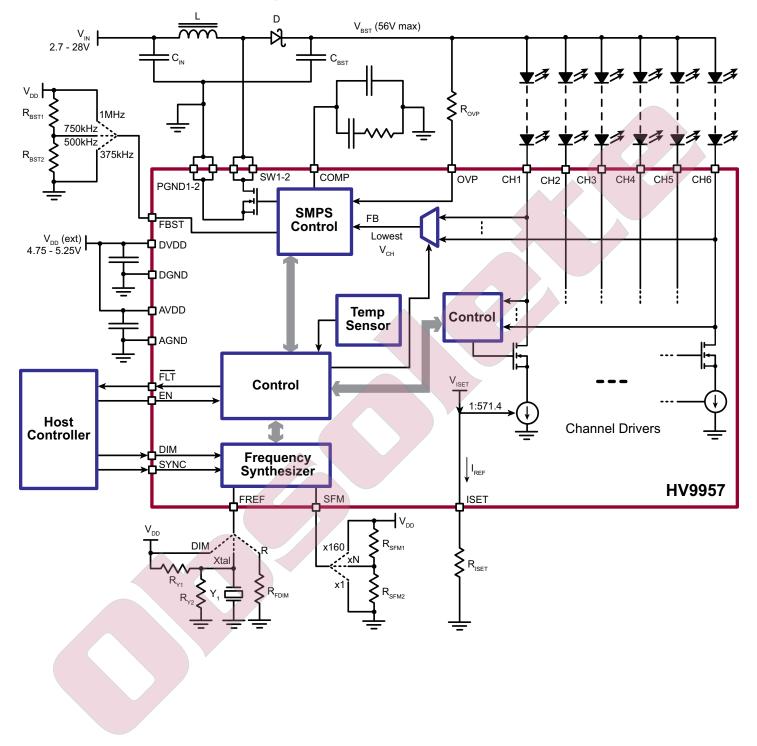

The HV9957 LED driver combines a switch-mode boost converter and six low-dropout linear current regulators to provide the advantages of high efficiency with precise current control. It may be configured for many applications, and is especially suited for one to three cell lithium-ion powered devices. An internal boost controller with an integrated switch eliminates the need for an external MOSFET.

Phased PWM dimming eliminates audible noise, reduces transient load on the boost converter, and minimizes supply current ripple. PWM dimming may be synchronized to an external signal such as the display refresh rate or, internally generated by a resistor or crystal oscillator.

Fault protection is provided against open/shorted LEDs, over voltage, under voltage, over current, and over temperature conditions. When a string fails, either shorted or open, the affected channel is removed from feedback and the rest continue operating normally.

## Typical Application Circuit

### **Ordering Information**

| Device | 24-Lead QFN<br>4.00x4.00mm body<br>0.80mm height (max)<br>0.50mm pitch |

|--------|------------------------------------------------------------------------|

| HV9957 | HV9957K7-G                                                             |

-G indicates package is RoHS compliant ('Green')

### **Absolute Maximum Ratings**

| Parameter                                  | Value                            |

|--------------------------------------------|----------------------------------|

| $AV_{DD}, DV_{DD}$                         | -0.3 to 6.5V                     |

| CH1-6 , SW1-2                              | 60V                              |

| FREF, DIM, SFM<br>SYNC, EN, FBSx, OVP, FLT | -0.3V to (V <sub>DD</sub> +0.3V) |

| I <sub>FLT</sub>                           | 10mA                             |

| V <sub>ISET</sub>                          | -0.3V to $V_{\text{DD}}$         |

| Storage temperature                        | -65°C to +150°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

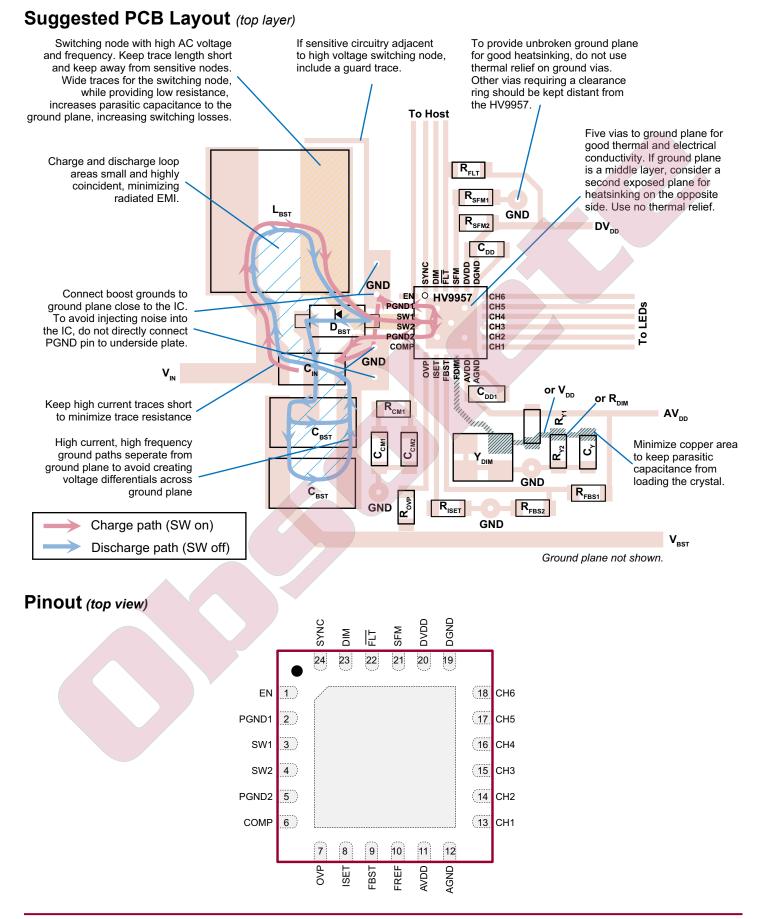

### Pin Configuration

### **Product Marking**

|      | Y = Last Digit of Year Sealed |  |  |  |  |

|------|-------------------------------|--|--|--|--|

| H957 | W = Code for Week Sealed      |  |  |  |  |

| YWLL | L = Lot Number                |  |  |  |  |

|      | = "Green" Packaging           |  |  |  |  |

Package may or may not include the following marks: Si or () 24-Lead QFN (K7)

## **Recommended Operating Conditions**

| Symbol            | Parameter                                   |                  | Min  | Тур      | Max  | Unit | Conditions                  |

|-------------------|---------------------------------------------|------------------|------|----------|------|------|-----------------------------|

| V <sub>DD</sub>   | IC supply voltage                           |                  | 4.75 | 5.00     | 5.50 | V    |                             |

| 6                 |                                             | DVDD             | 4.7  | -        | -    |      | One ceramic or an aluminum/ |

| C <sub>DD</sub>   | V <sub>DD</sub> capacitor                   | AV <sub>DD</sub> | 4.7  | -        | -    | μF   | tantalum +100nF ceramic     |

| V <sub>BST</sub>  | Boost converter output volta                | age              | -    | -        | 56   | V    | V <sub>IN</sub> ≥ 12V       |

| TJ                | Operating junction temperat                 | ture*            | -40  | -        | 125  | °C   |                             |

| І <sub>сн</sub>   | LED current                                 | -                | -    | 30       | mA   |      |                             |

| f <sub>DIM</sub>  | PWM dimming frequency (all operating modes) | 3.5              | -    | 24       | kHz  |      |                             |

| R <sub>osc</sub>  | Precision oscillator resistor               |                  | 125  | -        | 250  | kΩ   |                             |

| f <sub>xtal</sub> | Crystal frequency                           |                  | -    | 24.576   | -    | MHz  |                             |

| f <sub>sync</sub> | SYNC frequency                              | 60               | -    | 480      | Hz   |      |                             |

| I <sub>sw</sub>   | Boost converter switch curre                | -                | -    | 2.2      | A    |      |                             |

| C <sub>COMP</sub> | Loop compensation network                   |                  |      | Type 2   |      | -    |                             |

| BCOM              | Boost converter operating n                 | node             | С    | CM or DC | М    | -    |                             |

Note:

\* Junction temperature internally linked.

## Electrical Characteristics (over recommended operating conditions at 25°C unless otherwise specified)

| Sym                    | Parameter                                                                                          | Min             | Тур               | Max                  | Unit   | Conditions                                                                                                                                                                                                                                                                 |

|------------------------|----------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply                 |                                                                                                    |                 |                   |                      |        |                                                                                                                                                                                                                                                                            |

| I <sub>DD</sub>        | $V_{DD}$ active current (AV_{DD} + DV_{DD})                                                        | -               | 7.0               | 10                   | mA     | f <sub>BST</sub> = 1.0MHz                                                                                                                                                                                                                                                  |

| I <sub>DDQ</sub>       | $V_{DD}$ standby current (AV <sub>DD</sub> + DV <sub>DD</sub> )                                    | -               | 1.0               | 10                   | μA     | EN = 0                                                                                                                                                                                                                                                                     |

| I <sub>lkg</sub>       | OFF state leakage current, sum of SW1 - 2, OVP, and CH1 - 6 pins                                   | -               | -                 | 10                   | μA     | EN pin = 0, 12V applied to SWx<br>and CHx, 5.0V applied to VDD<br>pins                                                                                                                                                                                                     |

| Boost Co               | onverter                                                                                           |                 |                   |                      |        |                                                                                                                                                                                                                                                                            |

|                        |                                                                                                    | 338             | 375               | 412                  | kHz    | FBST = 0 - 0.05 × V <sub>DD</sub>                                                                                                                                                                                                                                          |

| c                      |                                                                                                    | 450             | 500               | 550                  | kHz    | FBST = 0.28 - 0.38 × V <sub>DD</sub>                                                                                                                                                                                                                                       |

| f <sub>ΒST</sub>       | Switching frequency                                                                                | 675             | 750               | 825                  | kHz    | FBST = 0.62 - 0.72 × V <sub>DD</sub>                                                                                                                                                                                                                                       |

|                        |                                                                                                    | 0.90            | 1.00              | 1.10                 | MHz    | FBST = 0.95 - 1.00 × V <sub>DD</sub>                                                                                                                                                                                                                                       |

| R <sub>sw</sub>        | Switch ON-resistance                                                                               | -               | 120               | 150                  | mΩ     | I <sub>sw</sub> = 1.0A                                                                                                                                                                                                                                                     |

| I <sub>SAT</sub>       | Switch saturation current                                                                          | 3.0             | -                 |                      | A      | V <sub>sw</sub> > 350mV                                                                                                                                                                                                                                                    |

| t <sub>RISE</sub>      | Switch current rise time                                                                           | -               | _                 | 5.0                  | ns     | I <sub>sw</sub> = 1.0A, 10% - 90%                                                                                                                                                                                                                                          |

| t <sub>FALL</sub>      | Switch current fall time                                                                           | -               | -                 | 5.0                  | ns     | I <sub>sw</sub> = 1.0A, 90% - 10%                                                                                                                                                                                                                                          |

| t <sub>BLNK</sub>      | Blanking interval                                                                                  | -               | 7.0               | -                    | ns     |                                                                                                                                                                                                                                                                            |

| t <sub>ss</sub>        | Soft start interval                                                                                | -               | 6.4               | -                    | ms     |                                                                                                                                                                                                                                                                            |

|                        | vers (CH1-CH6)                                                                                     |                 |                   |                      | 1      |                                                                                                                                                                                                                                                                            |

| V                      | Voltage at ISET pin                                                                                | -               | 700               | -                    | mV     |                                                                                                                                                                                                                                                                            |

| I <sub>сн</sub>        | Full scale output current (average of all channels)                                                | 19.6<br>        | 20.0<br>-<br>30.0 | 20.4<br>20.4<br>30.6 | mA     | $ \begin{array}{l} {\sf R}_{\rm ISET} = 20.0 {\sf k} \Omega,  {\sf V}_{\rm CH} = 900 {\sf mV} \\ {\sf R}_{\rm ISET} = 20.0 {\sf k} \Omega,  {\sf V}_{\rm CH} = 0 - 900 {\sf mV} \\ {\sf R}_{\rm SET} = 13.3 {\sf k} \Omega,  {\sf V}_{\rm CH} = 900 {\sf mV} \end{array} $ |

| I <sub>CH(OFF)</sub>   | Output current when disabled                                                                       | 2 -             | -                 | 10                   | μA     | EN = 0                                                                                                                                                                                                                                                                     |

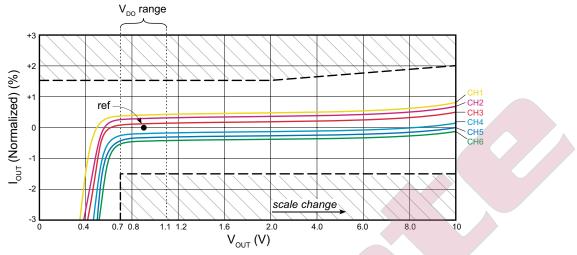

| ΔI <sub>CH</sub>       | Current matching (deviation from<br>average of all 6 channels)<br>See Output Characteristics graph | -1.5<br>-1.5    | -                 | +1.5<br>+1.5→2.0     | %<br>% | I <sub>OUT</sub> = 20mA, D <sub>DIM</sub> = 100%<br>V <sub>CH</sub> = 0.7 - 2.0V<br>V <sub>CH</sub> = 2.0 - 10V                                                                                                                                                            |

| $V_{DO}$               | Regulated dropout voltage headroom (lowest active channel)                                         | 700             | 900               | 1100                 | mV     | I <sub>OUT</sub> = 30mA                                                                                                                                                                                                                                                    |

| PWM LE                 | D Drive (CH1 - CH6)                                                                                |                 |                   |                      |        |                                                                                                                                                                                                                                                                            |

|                        |                                                                                                    | -               | -                 | 0                    |        | D <sub>IN</sub> = 0%, f <sub>DIM</sub> = 8kHz                                                                                                                                                                                                                              |

|                        | Duty cycle absolute accuracy                                                                       | 1.90            | 2.00              | 2.10                 | 0/     | D <sub>IN</sub> = 2%, f <sub>DIM</sub> = 8kHz                                                                                                                                                                                                                              |

| D <sub>DIM</sub>       | Average of all 6 channels                                                                          | 48.5            | 50.0              | 51.5                 | %      | D <sub>IN</sub> = 50%, f <sub>DIM</sub> = 8kHz                                                                                                                                                                                                                             |

|                        |                                                                                                    | 100             | -                 | -                    |        | D <sub>IN</sub> = 100%, f <sub>DIM</sub> = 8kHz                                                                                                                                                                                                                            |

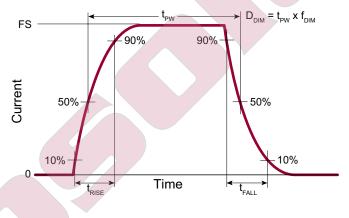

| $\Delta t_{_{PW}}$     | Pulse width matching<br>Deviation from avg of all 6 chs<br>Refer to Output Pulse graph             | -0.5            | -                 | +0.5                 | %      | $D_{IN} = 2 - 100\%$ , $f_{DIM} = 8kHz$ ,<br>measured at 50% full-scale                                                                                                                                                                                                    |

| t <sub>sync(MIN)</sub> | Minimum sync pulse width                                                                           | 300             | -                 | -                    | ns     |                                                                                                                                                                                                                                                                            |

| f <sub>INT</sub>       | Internally generated dimming frequency                                                             | 9.552<br>-10ppm | 9.600<br>9.600    | 9.648<br>+10ppm      | kHz    | $R_{FDIM}$ = 200kΩ, SFM = V <sub>DD</sub> , no xtal, SFM = V <sub>DD</sub> , 24.576MHz xta                                                                                                                                                                                 |

| <b>Electrical Characteristics</b> | (over recommended operating conditions at 25°C unless otherwise specified) |

|-----------------------------------|----------------------------------------------------------------------------|

|                                   | (over recommended operating conditions at 20 0 amedo otherwise operating)  |

| Sym                    | Parameter                                                   | Min      | Тур     | Мах  | Unit                      | Conditions                              |

|------------------------|-------------------------------------------------------------|----------|---------|------|---------------------------|-----------------------------------------|

| f <sub>SYNC(MIN)</sub> | Minimum SYNC frequency                                      | -        | 48      | 55   | Hz                        |                                         |

| f <sub>SYNC(MAX)</sub> | Maximum SYNC frequency                                      | 540      | 600     | -    | Hz                        |                                         |

| t <sub>RISE</sub>      | Output current rise time                                    | -        | 35      | -    | ns                        | I <sub>CH</sub> = 20mA, 10 - 90%        |

| t <sub>FALL</sub>      | Output current fall time                                    | -        | 160     | -    | ns                        | I <sub>CH</sub> = 20mA, 90 - 10%        |

|                        | n Circuits                                                  |          |         |      |                           |                                         |

| UVLO                   | V <sub>DD</sub> UVLO trip point, OFF                        | 4.00     | 4.20    | 4.40 | V                         |                                         |

| UVLO <sub>HYS</sub>    | V <sub>DD</sub> UVLO hysteresis                             | -        | 300     | -    | mV                        |                                         |

| V <sub>OCP</sub>       | Switch over current protection                              | -        | 350     | -    | mV                        | SW ON                                   |

| t <sub>ocp</sub>       | I <sub>OCP</sub> switch shut-OFF response time              | -        | -       | 50   | ns                        | I <sub>sw</sub> < 200mA                 |

| I <sub>ovp</sub>       | OVP bias current                                            | 1.12     | 1.14    | 1.16 | ×I <sub>SET</sub>         | V <sub>OVP</sub> < 1.7V                 |

| I <sub>OVPH</sub>      | OVP hysteresis current                                      | -6%      | -5%     | -4%  | ×I <sub>OVP</sub>         | V <sub>OVP</sub> > 2.3V                 |

| V <sub>OVP</sub>       | OVP threshold voltage                                       | 1.7      | 2.0     | 2.3  | V                         | -                                       |

| $V_{ACH}$              | ACH threshold voltage                                       | 1.15     | 1.25    | 1.35 | V                         |                                         |

| T <sub>ACT1</sub>      | Over temperature protection activation temperature, stage 1 | 125      | 135     | 145  | °C                        | Rising                                  |

| T <sub>RST1</sub>      | Over temperature protection reset temperature, stage 1      | -        | -20     | -    | °C                        | Falling                                 |

| T <sub>ACT2</sub>      | Over temperature protection activation temperature, stage 2 | 10       | 15      | 20   | °C +<br>T <sub>ACT2</sub> | Rising                                  |

| T <sub>RST2</sub>      | Over temperature protection reset temperature, stage 2      | -        | -30     | -    | °C +<br>T <sub>ACT2</sub> | Falling                                 |

| T                      | Over temperature protection re-activation interval          |          | 800     | -    | ms                        |                                         |

| EN                     | Enable low pulse width to reset fault                       | 0.1      | -       | 10   | μs                        |                                         |

| $EN_{OFF}$             | Enable low pulse width to disable                           | 50       | -       | -    | μs                        |                                         |

| Control Ir             | nputs/Outputs (SYNC, DIM, FLT, SF                           | M, FREF, | FBST, E | EN)  |                           |                                         |

| I <sub>SFM</sub>       | SFM input current                                           | -5.0     | -       | +5.0 | μA                        | V <sub>SFM</sub> = 0 - 5.0V             |

| V                      | Logic low input voltage                                     | -        | -       | 0.8  | V                         |                                         |

| VIH                    | Logic high input voltage                                    | 2.1      | -       | -    | V                         |                                         |

| V <sub>ol</sub>        | Logic low output voltage                                    | -        | -       | 0.4  | V                         | I <sub>LOAD</sub> = 4.0mA               |

| I <sub>L</sub>         | Logic low input current                                     | -        | -       | 5.0  | μA                        | $V_{IN}$ = grounded, open,              |

| I <sub>H</sub>         | Logic high input current                                    | -        | -       | 5.0  | μA                        | or 4.75 - 5.25V                         |

|                        | Guaranteed by design - not production tested                | .)       |         |      |                           |                                         |

|                        | Thermal resistance junction to                              |          |         |      |                           | Soldered to PCB with 5.0cm <sup>2</sup> |

| $	heta_{j-a}$  | Thermal resistance, junction to ambient            | - | 34  | - | °C/W | Soldered to PCB with 5.0cm <sup>2</sup><br>exposed copper area using 5<br>thermal vias |

|----------------|----------------------------------------------------|---|-----|---|------|----------------------------------------------------------------------------------------|

| $\theta_{j-p}$ | Thermal resistance, junction to<br>underside plate | - | 3.6 | - | °C/W |                                                                                        |

## Output Characteristics (I<sub>CH</sub> = 20mA nominal)

Example curves shown for illustrative purposes only. Normalization reference is the average current of all 6 channels at 900mV. Limits apply to each channel individually.

#### Output Pulse (PWM Dimming)

#### Abbreviations:

| OVP | Over-Voltage Protection     | <u>PW</u> M | Pulse Width Modulation    | CCM  | Continuous Conduction Mode     |

|-----|-----------------------------|-------------|---------------------------|------|--------------------------------|

| OCP | Over-Current Protection     | FLT         | Fault bit or pin          | DCM  | Discontinuous Conduction       |

| OLP | Open LED Protection         | PHD         | Phased Dimming            |      | Mode                           |

| SLP | Shorted LED Protection      | SFM         | Sync Frequency Multiplier | VBST | Boost converter output voltage |

| OTP | Over-Temperature Protection | RSA         | Redistribute start angles |      |                                |

|     |                             |             | (phased dimming)          |      |                                |

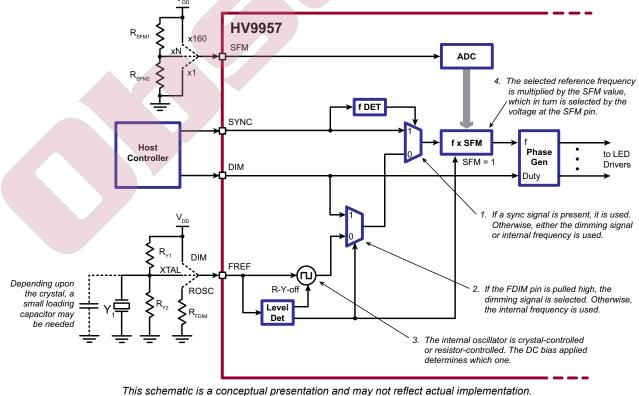

### Simplified Internal Block Diagram

### **Application Information**

#### Operation

The HV9957 combines a switch-mode boost converter and six low-dropout linear current regulators to provide the advantages of high efficiency and precise current control.

#### Supplies

Two independent supplies may be used to power the back-light controller circuit: one to supply the HV9957 ( $V_{DD}$ ) and another to supply the boost converter ( $V_{IN}$ ). The supply for the boost converter may range from 2.7 to 28V depending on the load. The HV9957 supply ( $V_{DD}$ ) is 5.0V nominal.

The boost converter need not be supplied from the same source as for the HV9957. The low ON-resistance internal boost converter switch combined with CCM operation allows boost converter supply voltages as low as 2.7V for singlecell lithium-ion batteries. At lower boost supply voltages, output power decreases due to the increased switch current.

The HV9957 has two power states - shutdown and active. To keep standby currents low, internal circuits are powered down when shut down.

The active state is when the HV9957 is driving the LED strings. When transitioning from shutdown to active, a soft-start circuit ramps input current over a 6.4ms interval.

#### HV9957 States

| EN pin            | State       |

|-------------------|-------------|

| 0 for >50µs       | Shutdown    |

| $0 \rightarrow 1$ | Soft-start  |

| 1                 | Active      |

| 1-0-1 for <10µs   | Reset fault |

#### Under-voltage Lock Out (UVLO)

The boost converter and output drivers will not be enabled until  $V_{DD}$  reaches its UVLO thresholds. When  $V_{DD}$  falls by the UVLO hysteresis voltage from the turn-ON threshold, the boost converter and output drivers are disabled.

#### **Boost Converter**

The boost converter provides the high voltage needed to drive the LED strings. It gets its feedback from the active output channels, maintaining a minimum voltage of 900mV across the linear current regulators (CH1 - 6). Therefore, the boost converters' output voltage ( $V_{BST}$ ) will be 900mV ( $V_{DO}$ )

plus the maximum LED string voltage drop ( $V_{\text{STR(MAX)}}$ ).

$$V_{\scriptscriptstyle BST} = V_{\scriptscriptstyle DO} + V_{\scriptscriptstyle STR(MAX)}$$

It is recommended that the boost ratio (V $_{\rm BST}$  / V $_{\rm OUT}$ ) be limited to 9 or less.

Due to boost switch limitations, load capability decreases with lower supply voltages. As with any switching converter, input power is relatively constant for a given load. Since  $P_{IN} = V_{IN} \cdot I_{IN}$ , input current increases as input voltage decreases. The following graph depicts the load capability for various supply voltages and LEDs/string.

#### Load Capability

|   | Batt<br>Cells | LED /<br>str | V <sub>out</sub><br>(V) | V <sub>IN</sub><br>(V) | Max<br>P <sub>LOAD</sub><br>(W) | Max<br>I <sub>LED</sub><br>(mA) | Avg<br>I <sub>IN</sub><br>(A) |

|---|---------------|--------------|-------------------------|------------------------|---------------------------------|---------------------------------|-------------------------------|

|   |               |              |                         | 2.7                    | 3.4                             | 25                              | 1.4                           |

|   | 1             | 7            | 22.4                    | 3.8                    | 4.0                             | 30                              | 1.0                           |

|   |               |              |                         | 4.2                    | 4.0                             | 30                              | 1.1                           |

|   |               |              | 7                       | 5.4                    | 6.9                             | 30                              | 1.4                           |

|   | 2             | 12           | 38.4                    | 7.6                    | 6.9                             | 30                              | 1.0                           |

|   |               |              |                         | 8.4                    | 6.9                             | 30                              | 0.9                           |

| _ |               |              |                         | 8.1                    | 9.8                             | 30                              | 1.3                           |

|   | 3             | 17           | 54.4                    | 11.4                   | 9.8                             | 30                              | 1.0                           |

|   |               |              |                         | 12.6                   | 9.8                             | 30                              | 0.9                           |

Based on mathematical modeling and assumed characteristics of external components. The actual circuit may yield different results.

$I_{\rm IN}$  is based on assumed 90% efficiency and CCM. Ripple should be factored in, depending on the inductor value and boost frequency

$V_{OUT}$  is based on 3.2V LEDs.

The boost converter frequency is pin-programmable in four steps by applying the appropriate voltage to the FBST pin.

| FBST               | Internal<br>Osc | XTAL<br>Osc |

|--------------------|-----------------|-------------|

| 0V                 | 375kHz          | ÷64         |

| 1/3V <sub>DD</sub> | 500kHz          | ÷48         |

| 2/3V <sub>DD</sub> | 500kHz          | ÷32         |

| V <sub>DD</sub>    | 1.0MHz          | ÷24         |

Slope compensation is employed internally, therefore continuous conduction mode (CCM) can be used.

An RC network on the COMP pin establishes boost converter loop stability.

#### **Over Current Protection (OCP)**

The boost converter internal switch is protected against over current. Switch voltage is monitored when the switch is ON, and if it reaches the  $V_{\text{OCP}}$  threshold, the OCP circuit immediately turns OFF the switch. OCP occurs on a cycle-by-cycle basis, resetting every boost converter cycle.

When OCP is active, peak current is limited and the boost converter may not support the load. The LEDs will dim, often unequally since the strings have different voltage drops. Some strings may extinguish entirely.

OCP latches the  $\overline{FLT}$  pin. It is reset by toggling EN.

#### Soft Start

Inrush current limiting during boost converter turn-ON is provided by a soft-start circuit which gradually ramps-up the boost converter duty cycle over a 6.4ms interval.

#### Output Channels (CH1–6)

Each channel has a linear current regulator which maintains a constant current thru the connected LED string. Full-scale current is established by the value of the external  $R_{set}$  resistor. In addition, the linear regulators may be turned ON and OFF under PWM control to provide a duty cycle average dimming control.

Efficiency is maximized by maintaining a low voltage across the outputs. The channel with the highest LED string voltage drop, and thus the lowest channel voltage, becomes the feedback point for regulating the boost converter output voltage. Once a channel has been identified as faulty due to OLP or SLP, it will not be used as a feedback point for boost converter regulation.

#### Full-scale LED Current (ISET)

Output current  $(I_{CH})$  is set by the value of the resistor connected to the ISET pin  $(R_{ISET})$ .

$$I_{CH} = \frac{400V}{R_{ISET}}$$

#### Enable

The EN pin serves two functions: it enables and disables the HV9957, or resets fault circuitry. When held high for at

least 50ns the HV9957 is enabled. When toggled low for 10 $\mu$ s, the fault circuits are reset, except for OTP, which is self-resetting.

When held low for more than  $50\mu$ s, the HV9957 is disabled. To achieve very low standby current consumption, enable controls the power provided to internal circuits. For this reason, there is a delay after EN = 1 until the driver reaches full operation.

#### **PWM Dimming**

In PWM dimming, an external PWM signal applied to the DIM input controls the ON/OFF duty cycle of the outputs (CH1 - 6). A logic 1 enables the outputs, while a logic 0 disables the outputs. The LED drive frequency need not be the frequency of the signal applied to the DIM input. See the section on LED drive frequency on Page 14.

In PWM dimming, the average LED current is the duty cycle average of the full-scale current.

$$I_{CH} = I_{FS} \cdot D_{PWM}$$

where:  $I_{CH}$  = average output current  $I_{FS}$  = full scale current  $D_{PWM}$  = duty cycle

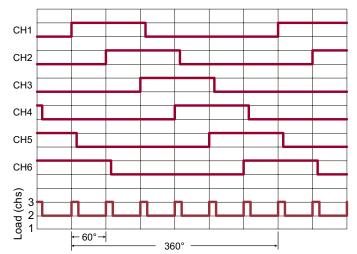

#### Phased PWM Dimming

With conventional PWM dimming, all the channels turn ON and OFF at the same time. Phased PWM dimming offsets the beginning of the ON time for each channel, distributing the start angles equally across 360°.

Phased dimming reduces the transient load on the boost converter, minimizing supply current ripple. This in turn, reduces conducted EMI on the supply rail and minimizes possible interference to adjacent circuitry. It also effectively sextuples the PWM dimming frequency, allowing a low PWM dimming frequency for dynamic range, while extending the audible effects beyond the range of human hearing.

With non-phased dimming, the dynamic load would have an amplitude of 6 channels and a frequency equal to the PWM dimming frequency. With phased PWM dimming, the transient load will be one channel amplitude at most, and at a frequency six times the dimming frequency.

When one or more channels is disabled by a fault condition, the phase angles of the remaining good strings are redistributed equally across  $360^{\circ}$ . For example, with all six channels active, the start phase angles are integer multiples of  $360^{\circ} \div 6 = 60^{\circ}$ . If one string fails, the remaining five strings have start phase angles that are integer multiples of  $360^{\circ} \div 5 = 72^{\circ}$ .

Phased dimming is active whether sync is used or not.

#### **Protection Circuits**

Robust protection is provided for various fault conditions, including boost switch over current, supply under voltage, output over voltage, temperature, shorted LED strings, and open or partially open LED strings. When OTP1 is activated, the HV9957 first attempts to alleviate the fault condition by disabling the shorted or open string. The string identified as open and/or shorted is disconnected while keeping the other strings lit.

If the fault condition persists and results in excessive die temperature, all the channels and the boost converter are disabled until die temperature falls below the reset threshold, at which point the driver is re-enabled. If the fault condition persists, the cycle is repeated.

#### **Over Voltage Protection (OVP)**

Over voltage protection prevents VBST from rising to destructive levels in the event that any LED strings become opened. VBST is sensed by converting the voltage to current via  $R_{OVP}$ . The OVP pin is biased at a constant voltage.

$$V_{OVP} = R_{OVP} \cdot 8/7 \cdot I_{SET} + 2V$$

rising

= 0.95 \cdot R\_{OVP} \cdot 8/7 \cdot I\_{SET} + 2V falling

where  $V_{OVP}$  is the OVP threshold voltage.

OVP is usually activated by an open or a partially open (Zener-protected) LED string as the boost converter seeks to regulate the voltage at output with the open LED.

The OVP pin goes into a high resistance state during shutdown to minimize supply current.

# Shorted LED Protection (SLP) Temperature Triggered

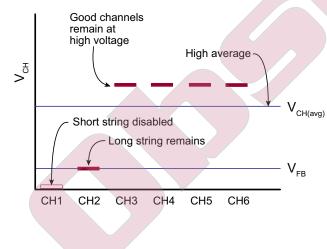

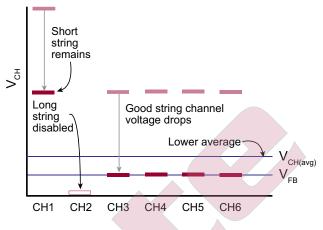

Protection against shorted LED strings is provided. Any string identified as shorted is removed from the boost converter feedback loop and disconnected. The remaining good strings continue to operate normally.

The FLT pin is asserted low. The fault circuit is reset by toggling EN or cycling power.

#### **Open LED Protection (OLP)**

With an open LED string,  $V_{BST}$  rises as it attempts to achieve 900mV at the channel with the open string. Eventually OVP or SLP activates, at which time those outputs having zero volts are marked as open and are removed from boost converter feedback. The current regulators on the open strings continue to operate and will regulate LED current should the string reconnect, but the channel will not be reconnected to the boost converter feedback. To restore feedback, the EN pin toggled or power cycled OFF and ON. Refer to the Fault Summary table.

The driver continues running with the remaining good strings.

The  $\overline{FLT}$  pin is asserted low. The fault condition is reset by toggling EN or cycling power.

#### **Over-temperature Protection (OTP)**

OTP is in two stages. OTP1 seeks to reduce die temperature by disconnecting the faulty string. If temperature continues to rise, OTP2 is triggered as a fail safe mechanism, shutting down the driver.

OTP is self-resetting once temperature falls below the reset threshold.

#### SLP and OLP Behavior

The process of identifying and disabling the channel having faulty string is two steps: 1) detecting a fault, and 2) determining if the fault is a shorted, partially open (Zener-protected), or fully open LED.

First consider the case with a partially open LED. The faulty channel will be at the 900mV feedback point, while the remaining channels will be relatively higher. Using a conventional approach for SLP, where those channels with an absolute voltage (REF to GND) above a set threshold, the five good strings will be misidentified as shorted and disabled.

Another problem exists with a conventional SLP; it can block activation of OLP. Open strings cause boost voltage to rise in an attempt to achieve 900mV on the faulty channel. The channel with the open string remains at ground, eventually causing VBST to rise until OVP trips. This is the trigger for the OLP circuit, which then identifiers and disables channels at 0V. The problem with this approach arises with the good strings: as VBST rises towards OVP, the good strings apply a high voltage to the channel outputs. This can cause SLP to trip before OVP trips, causing good strings to be misinterpreted as shorted and disabled while the open string remains. To reduce the chances of this occurring, the SLP threshold can be set higher, but this may render SLP useless.

The purpose of SLP is to prevent excessive dissipation in the channel output drivers and the resultant rise in die temperature. If die temperature remains reasonable, the shorted LED string can continue to operate, albeit at reduced brightness. Note that little power is wasted in the shorted LED.

For these two reasons the primary mechanism for disabling faulty strings is triggered when die temperature becomes excessive rather than at an arbitrary voltage level. The exceptions are the SLP and OVP limits, which should be high as a fail safe mechanism rather than as the normal trigger for the faulty string protection circuit. Once die temperature reaches the OTP1 threshold, a single string is identified as faulty and disabled. This should reduce internal power dissipation two ways. First, it eliminates the power dissipation in the channel driver with the faulty string. Second, the disconnected string reduces the load on the boost converter, which in turn allows the boost switch to run cooler.

When the die temperature falls below the hysteresis temperature, OTP re-arms after 800ms. If the die temperature has not fallen by the hysteresis temperature, OTP1 is retriggered. In addition, to prevent the successive disabling of channels following an OLP event, the protection circuit is not re-armed until at least one channel's voltage has fallen below the ACH (All Channels High) threshold. When OTP1 resets and ACH goes low, the protection circuit is re-armed to trigger on another fault, but the previously identified faulty string remains disabled under the assumption that faulty strings do not spontaneously repair themselves. Toggling EN or cycling power resets the faulty strings.

If the disabling of strings does not prevent die temperature

from rising, the second-stage OTP activates, shutting down the boost converter. OTP2 self-resets when die temperature falls by the hysteresis temperature, re-enabling the boost converter but not reconnecting faulty strings.

If a string is fully open, the protection circuit cannot wait for the temperature to rise to OTP1 level - in the meantime output voltage would rise to destructive levels. Once OVP is activated, the channel with the open string is identified and disconnected. If more than one string is open, OVP will retrigger and the second open string is disconnected. The cycle repeats as long as there is an open string on an active channel.

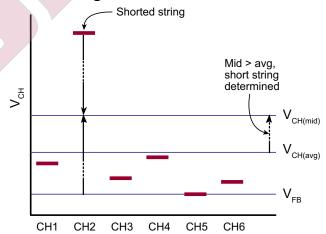

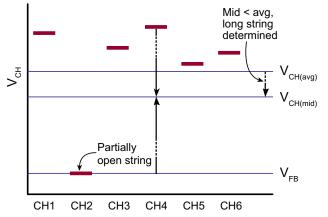

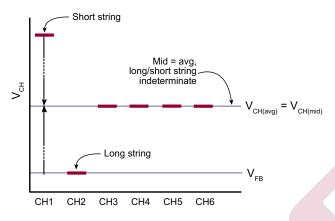

Once OTP1 is triggered, a fault condition has been established and the next step is to determine if a short or long string is the cause. An 'outlier' approach is used. Outliers being those channels with a voltage significantly different from the others. The midpoint between the highest and lowest active channels is compared to the average of the active channels to determine whether the faulty string is long or short. The following examples demonstrate the technique.

#### **Shorted String**

In the previous two examples, only a single faulty string has been considered. A problem arises if one string is long and another short such that the midpoint is at the average. Either the short or long string can be disabled. It is preferable to disable the long string, so a bias is applied to the midpoint favoring the long string. Long strings result in higher driver dissipation, as the following diagrams graphically explain.

In addition to lower driver dissipation, if the long string is caused by an open LED with a protection Zener conducting, power is wasted in the Zener. On the other hand, a shorted LED wastes no (or little) power.

#### Long & Short String

#### **Short String Favored**

#### Long String Favored

#### Under-voltage Lock Out (UVLO)

The boost converter and output drivers will not be enabled until  $V_{DD}$  reaches 4.2V nominal. When  $V_{DD}$  falls by 300mV from the 4.2V turn-ON threshold, the boost converter and output drivers are disabled.

#### Fault pin (FLT pin)

The FLT output pin signals a fault condition; SLP, OLP, OCP, or OTP. It is active low and open drain, requiring an external pull-up. It may be wire-or'd with other devices.

The FLT output may be used to generate an interrupt to the host controller.

Toggling EN resets both the SLP/OLP circuits and the  $\overline{\text{FLT}}$  pin.

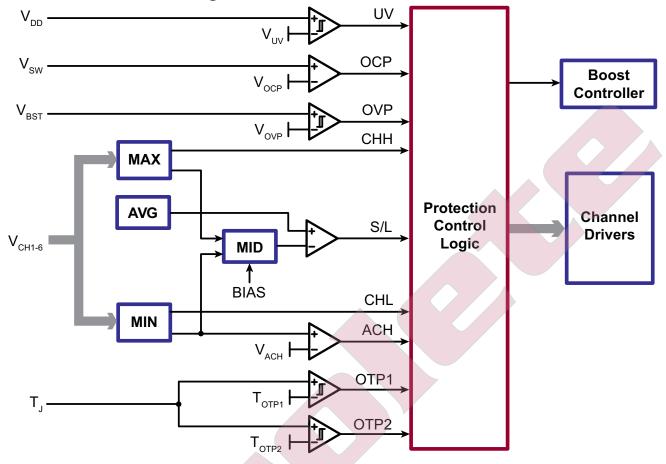

### Fault Protection Block Diagram

#### **Inputs**

**V**<sub>DD</sub> is supply voltage.

V<sub>sw</sub> is the ON-state boost switch voltage..

$V_{\text{BST}}$  is the boost converter output voltage.

$V_{CH1-6}$  are the voltages at the channel outputs.

T, is the die temperature.

#### **References**

$V_{uv}$  is the  $V_{DD}$  under voltage threshold.  $V_{OCP}$  is the boost switch over current protection threshold.

V<sub>ovP</sub> is the boost converter over voltage threshold.

**BIAS** is the offset applied to the midpoint.

$V_{ACH}$  is the All Channels High threshold ( $V_{ACH} > V_{FB}$ ).  $T_{OTP1}$  is the over temperature stage 1 protection threshold. ( $T_{OTP1} < T_{OTP2}$ )  $T_{orp}$  is the over temperature stage 2 protection threshold.

#### **Functions**

MAX selects the maximum voltage of all active channels. Outputs the voltage and channel.

**MIN** selects the minimum voltage of all active channels. Outputs the voltage and channel.

MID finds the midpoint between the highest and lowest active channel voltages.

AVG determines the average voltage of all active channels.

#### Inputs to Logic Block

UV indicates when the supply voltage is too low.

**OCP** indicates when the boost switch current is excessive.

**OVP** indicates when the boost output voltage exceeds the threshold established by  $R_{ove}$ .

CHH identifies the channel with the highest voltage.

CHL identifies the channel with the lowest voltage.

**SLP** indicates when a shorted string applies excessive voltage to the channel output.

S/L indicates whether the farthest outlying channel is a short string or a long string (0=short, 1=long).

**ACH** is all channels high - when all channels are above the regulated feedback voltage.

OTP1 indicates when die temperature has become excessive.

OTP2 indicates when die temperature has become critical.

### Fault Protection Logic Table

| UV | ОСР | OVP | S/L | ACH | OTP1 | OTP2 | CHL &<br>CHH | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|-----|-----|-----|-----|------|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Х   | Х   | Х   | Х   | Х    | Х    | х            | Shuts down the IC when supply voltage is too low.                                                                                                                                                                                                                                                                                                                                                                                       |

| 0  | 1   | 0   | х   | х   | х    | 0    | х            | Turns OFF boost converter switch when instantaneous current becomes excessive. Operates cycle-by-cycle. The active channels remain ON, but with a lower $V_{BST'}$ some strings may not be lit.                                                                                                                                                                                                                                         |

| 0  | 0   | 1   | x   | x   | x    | 0    | x            | Shuts down boost converter when output voltage exceeds threshold set by $R_{oVP}$ . The channel outputs are checked for an open string and are disconnected from feedback all at once. The channels remain on to discharge $C_{oUT}$ .<br>The boost converter is re-enabled when $V_{BST}$ falls below the lower OVP threshold and the voltage at least one channel falls below the $V_{ACH}$ threshold                                 |

| x  | х   | х   | 1   | 0   | 1    | 0    | ×            | Short/Long string. The S/L signal is used to determine if the channel to be disabled has a long string or a short string, with a bias towards a long string.                                                                                                                                                                                                                                                                            |

| x  | х   | х   | х   | х   | Х    | х    | СН           | Identifies the channel with the lowest (CHL) and high-<br>est (CHH) voltages. In conjunction with S/L, identifies the<br>channel to be disabled.                                                                                                                                                                                                                                                                                        |

| 0  | 0   | 0   | 0   | 1   | 0    | 0    | x            | All channels High. Indicates when all active channels have<br>a voltage above the regulated feedback voltage, which oc-<br>curs when a channel with an open or long string is disabled.<br>ACH disables the faulty string protection circuit and turns<br>OFF the boost converter until one channel falls below $V_{ACH}$ .<br>The active channels remain ON when the boost converter<br>is disabled to assure $C_{OUT}$ is discharged. |

| 0  | 0   | 0   | 0   | 0   | 1    | 0    | х            | Excessive die temperature triggers the faulty string protec-<br>tion circuit, disconnecting a string. If die temperature falls<br>below the hysteresis threshold, OTP1 is re-armed for any<br>subsequent faulty strings. If die temperature rises, OTP2<br>triggers.                                                                                                                                                                    |

| x  | x   | x   | x   | x   | х    | 1    | х            | Critical die temperature immediately shuts down the boost<br>converter. Self-resets when die temperature falls by the<br>hysteresis threshold. The boost converter is re-enabled but<br>faulty strings remain disconnected.                                                                                                                                                                                                             |

### **LED Drive Frequency**

The LED drive frequency may be derived from four sources: the SYNC input, the DIM input, an internal resistor-programmable precision oscillator, or a crystal-controlled internal oscillator. If a SYNC signal is present, it is used. If the SYNC signal is not present or <48Hz, the LED drive frequency is established by either the internal oscillator or the DIM signal. If the pin controlling the internal oscillator is pulled to VDD, the DIM input is used. If a resistor to ground is on this pin, the internal oscillator is used. If a crystal is connected to FREF and it is biased between  $0.6V_{DD}$  and  $0.8V_{DD}$ , a crystal oscillator is used.

An internal frequency synthesizer can be used to multiply the selected reference frequency. The Sync Frequency Multiplier (SFM) is set to one of ten possible values by applying a voltage to the SFM pin. The voltage is referenced to VDD, so a resistive voltage divider can be used to set the sync frequency multiplier. If the SFM pin is grounded, the reference frequency (SYNC, DIM, or internal) determines LED drive frequency on a 1:1 basis.

To handle higher DIM frequencies, an additional scaling factor (SCL) of 1/9 is applied for SFM values greater than 1.

#### LED Drive Frequency

| FRE               | F pin                                                                                    | SFM                                                                                                                       | f                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Attach Bias       |                                                                                          | pin                                                                                                                       | f <sub>сн</sub>                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| R <sub>FDIM</sub> | 0V                                                                                       | -                                                                                                                         | SFM × f <sub>SYNC</sub>                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Xtal              | 0.7•V <sub>DD</sub>                                                                      | -                                                                                                                         | SFM × $f_{SYNC}$                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Xtal              | V <sub>DD</sub>                                                                          | -                                                                                                                         | SFM × f <sub>SYNC</sub>                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| none              | $V_{_{DD}}$                                                                              | -                                                                                                                         | Illegal                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| $R_{FDIM}$        | 0V                                                                                       | -                                                                                                                         | SFM × f <sub>osc</sub>                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Xtal              | 0.7•V <sub>DD</sub>                                                                      | -                                                                                                                         | SFM × f <sub>xTAL</sub> / 409,600                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| none              | V <sub>DD</sub>                                                                          | 0V                                                                                                                        | SFM × f <sub>DIM</sub>                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| none              | V <sub>DD</sub>                                                                          | >0V                                                                                                                       | SFM × f <sub>DIM</sub> × 1/9                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                   | Attach<br>R <sub>FDIM</sub><br>Xtal<br>Xtal<br>none<br>R <sub>FDIM</sub><br>Xtal<br>none | $R_{FDIM}$ $0V$ Xtal $0.7 \cdot V_{DD}$ Xtal $V_{DD}$ none $V_{DD}$ $R_{FDIM}$ $0V$ Xtal $0.7 \cdot V_{DD}$ none $V_{DD}$ | AttachBiaspin $R_{FDIM}$ $0V$ -Xtal $0.7 \cdot V_{DD}$ -Xtal $V_{DD}$ -None $V_{DD}$ - $R_{FDIM}$ $0V$ -Xtal $0.7 \cdot V_{DD}$ -Xtal $0.7 \cdot V_{DD}$ -None $V_{DD}$ 0V |  |  |  |  |  |  |  |  |  |

#### **Boost Frequency**

| FRE               | F pin               | f <sub>BOOST</sub> (for given V <sub>FBST</sub> ) |                        |                        |                        |  |  |  |  |  |

|-------------------|---------------------|---------------------------------------------------|------------------------|------------------------|------------------------|--|--|--|--|--|

| Attach Bias       |                     | 0V                                                | 1/3 V <sub>DD</sub>    | 2/3 V <sub>DD</sub>    | $V_{_{DD}}$            |  |  |  |  |  |

| R <sub>FDIM</sub> | 0V                  | 375kHz                                            | 500kHz                 | 750kHz                 | 1.0MHz                 |  |  |  |  |  |

| Xtal              | 0.7•V <sub>DD</sub> | f <sub>xtal</sub> / 64                            | f <sub>xtal</sub> / 48 | f <sub>xtal</sub> / 32 | f <sub>xtal</sub> / 24 |  |  |  |  |  |

| Xtal              | V <sub>DD</sub>     | 375kHz                                            | 500kHz                 | 750kHz                 | 1.0MHz                 |  |  |  |  |  |

| none              | V <sub>DD</sub>     | 375kHz                                            | 500kHz                 | 750kHz                 | 1.0MHz                 |  |  |  |  |  |

Supertex inc. • 1235 Bordeaux Drive, Sunnyvale, CA 94089 • Tel: 408-222-8888 • www.supertex.com

### Frequency Synthesizer

|        | V <sub>SFM</sub><br>V <sub>DD</sub> | SFM |        | SYNC   | Input  |        | R-     | Programm | ed     | XTAL          |                | DIM     |

|--------|-------------------------------------|-----|--------|--------|--------|--------|--------|----------|--------|---------------|----------------|---------|

| #      |                                     |     | 60Hz   | 120Hz  | 180Hz  | 240Hz  | 250kΩ  | 200kΩ    | 125kΩ  | 24.576<br>MHz | Har of<br>60Hz | 540Hz   |

| 0      | 0.0                                 | 1   | 60     | 120    | 180    | 240    | 48.00  | 60.000   | 72.00  | 60            | 1.000          | 540     |

| 1      | 0.091                               | 17  | 1,020  | 2,040  | 3,060  | 4,080  | 816    | 1,020    | 1,224  | 1,020         | 17.000         | 9,180   |

| 2      | 0.182                               | 23  | 1,380  | 2,760  | 4,140  | 5,520  | 1,104  | 1,380    | 1,656  | 1,380         | 23.000         | 12,420  |

| 3      | 0.273                               | 32  | 1,920  | 3,840  | 5,760  | 7,680  | 1,536  | 1,920    | 2,304  | 1,920         | 32.000         | 17,280  |

| 4      | 0.364                               | 45  | 2,700  | 5,400  | 8,100  | 10,800 | 2,160  | 2,700    | 3,240  | 2,700         | 45.000         | 24,300  |

| 5      | 0.455                               | 62  | 3,720  | 7,440  | 11,160 | 14,880 | 2,976  | 3,720    | 4,464  | 3,720         | 62.000         | 33,480  |

| 6      | 0.545                               | 85  | 5,100  | 10,200 | 15,300 | 20,400 | 4,080  | 5,100    | 6,120  | 5,100         | 85.000         | 45,900  |

| 7      | 0.636                               | 117 | 7,020  | 14,040 | 21,060 | 28,080 | 5,616  | 7,020    | 8,424  | 7,020         | 117.000        | 63,180  |

| 8      | 1.000                               | 160 | 9,600  | 19,200 | 28,800 | 38,400 | 7,680  | 9,600    | 11,520 | 9,600         | 160.000        | 86,400  |

| 9      | 0.727                               | 221 | 13,260 | 26,520 | 39,780 | 53,040 | 10,608 | 13,260   | 15,912 | 13,260        | 221.000        | 119,340 |

| 10     | 0.818                               | 307 | 18,420 | 36,840 | 55,260 | 73,680 | 14,736 | 18,420   | 22,104 | 18,420        | 307.000        | 165,780 |

| 11     | 0.909                               | 410 | 24,600 | 49,200 | 73,800 | 98,400 | 19,680 | 24,600   | 29,520 | 24,600        | 410.000        | 221,400 |

| Nataai |                                     |     |        |        |        |        |        |          | -      |               |                |         |

### **LED Drive Frequencies for Given Source Frequencies**

Notes:

1. SFM values chosen for 9600Hz, R<sub>osc</sub> frequency range and overlap, and xtal harmonics of 60Hz.

2. Row #8 is out of sequence so that 9600Hz may be obtained without resistors (SFM pin =  $V_{pp}$ ).

3. Hatched cells indicate illegal conditions. The PWM duty cycle may be erroneous but no damage to either the HV9957 nor LEDs will be incurred.

### **Pin Description**

| Pin # | Pin<br>Name     | Description                                                                                                                                                                                                                                                                                                          |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | EN              | Enable input. When held low, shuts down the driver. When briefly toggled low, resets fault protection.                                                                                                                                                                                                               |

| 2     | PGND1           | Boost converter ground. The internal boost converter switch is connected to these pins.                                                                                                                                                                                                                              |

| 3     | SW1             | Peacet convertor internal quitab                                                                                                                                                                                                                                                                                     |

| 4     | SW2             | Boost converter internal switch.                                                                                                                                                                                                                                                                                     |

| 5     | PGND2           | Boost converter ground. The internal boost converter switch is connected to these pins.                                                                                                                                                                                                                              |

| 6     | COMP            | Boost converter loop compensation. An RC network connected between this pin and ground establishes loop stability.                                                                                                                                                                                                   |

| 7     | OVP             | Over voltage protection monitor. Biased at a constant current. A resistor from this pin to $V_{\rm BST}$ sets the OVP threshold.                                                                                                                                                                                     |

| 8     | ISET            | Output current set. A resistor from this pin to ground establishes full-scale output current.                                                                                                                                                                                                                        |

| 9     | FBST            | Sets boost converter frequency.                                                                                                                                                                                                                                                                                      |

| 10    | FREF            | Determines PWM dimming frequency when a SYNC signal is not present. When VDD applied, the frequency of the DIM signal is used. When a resistor to ground is connected, an internal R-C oscillator is used. When biased at $0.5 - 0.9 \times V_{DD}$ and a crystal connected, an internal crystal oscillator is used. |

| 11    | AVDD            | Supply for internal analog circuits. Bypass with a 1.0µF capacitor to ground.                                                                                                                                                                                                                                        |

| 12    | AGND            | Analog ground.                                                                                                                                                                                                                                                                                                       |

| 13    | CH1             |                                                                                                                                                                                                                                                                                                                      |

| 14    | CH2             |                                                                                                                                                                                                                                                                                                                      |

| 15    | CH3             | Our set sink outsuits fan driving that I ED stringe                                                                                                                                                                                                                                                                  |

| 16    | CH4             | Current sink outputs for driving the LED strings.                                                                                                                                                                                                                                                                    |

| 17    | CH5             |                                                                                                                                                                                                                                                                                                                      |

| 18    | CH6             |                                                                                                                                                                                                                                                                                                                      |

| 19    | DGND            | Digital ground.                                                                                                                                                                                                                                                                                                      |

| 20    | DVDD            | Supply input for internal digital circuits. Bypass locally with a 4.7µF capacitor to ground.                                                                                                                                                                                                                         |

| 21    | SFM             | Determines the sync frequency multiplier for SYNC input, DIM input or internal dimming frequency.                                                                                                                                                                                                                    |

| 22    | FLT             | Fault output, active low and open drain. An external pull-up is required. May be wire-or'd with other devices.                                                                                                                                                                                                       |

| 23    | DIM             | Input for an externally applied PWM dimming signal.                                                                                                                                                                                                                                                                  |

| 24    | SYNC            | Input for synchronizing the PWM drive signal to an external signal. When synchronization is not used, connect SYNC to ground.                                                                                                                                                                                        |

|       | lerside<br>late | The exposed metal plate on the underside is at ground potential and may be connected to ground or left floating. It provides heat sinking and should be soldered to a copper area on the PCB.                                                                                                                        |

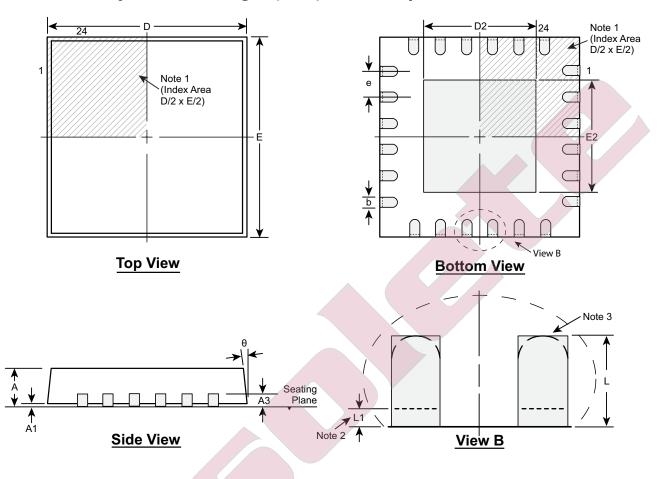

### 24-Lead QFN Package Outline (K7) 4.00x4.00mm body, 0.80mm height (max), 0.50mm pitch

Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symbol            |     | A    | A1   | A3          | b    | D    | D2   | Е    | E2   | е           | L    | L1   | θ               |

|-------------------|-----|------|------|-------------|------|------|------|------|------|-------------|------|------|-----------------|

| Dimension<br>(mm) | MIN | 0.70 | 0.00 | 0.20<br>REF | 0.18 | 3.85 | 2.55 | 3.85 | 2.55 | 0.50<br>BSC | 0.25 | 0.03 | <b>0</b> 0      |

|                   | NOM | 0.75 | 0.02 |             | 0.25 | 4.00 | 2.70 | 4.00 | 2.70 |             | 0.35 | -    | -               |

|                   | MAX | 0.80 | 0.05 |             | 0.30 | 4.15 | 2.80 | 4.15 | 2.80 |             | 0.45 | 0.15 | 14 <sup>0</sup> |

Drawings not to scale.

Supertex Doc.#: DSPD-24QFNK74X4P050, Version A031609.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2012 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

Downloaded from Elcodis.com electronic components distributor

Supertex inc.