# L6699

## Enhanced high voltage resonant controller

### Datasheet - production data

## Features

- Symmetrical duty cycle, variable frequency control of resonant half bridge

- Self-adjusting adaptive deadtime

- High-accuracy oscillator

- 2-level OCP: frequency-shift and immediate shutdown

- Interface with PFC controller

- Anti-capacitive-mode protection

- Burst-mode operation at light load

- Input for brownout protection or power-on/off sequencing

- "Safe-start" procedure prevents hard switching at startup

- 600 V rail compatible high-side gate driver with integrated bootstrap diode and high dv/dt immunity

- -300/800 mA high-side and low-side gate drivers with UVLO pull-down

- SO16N package

### **Applications**

- SMPS for LCD TVs, desktop and AIO PCs, servers, Telecom power

- AC-DC adapter, open frame SMPS

### Table 1. Device summary

| Order codes | Package | Packing       |

|-------------|---------|---------------|

| L6699D      | SO16N   | Tube          |

| L6699DTR    | 501014  | Tape and reel |

#### January 2013

#### Doc ID 022835 Rev 2

1/38

www.st.com

This is information on a product in full production.

# Contents

| 1  | Description 4                           |

|----|-----------------------------------------|

| 2  | Electrical ratings                      |

| 3  | Thermal data                            |

| 4  | Pin connections                         |

| 5  | Electrical data9                        |

| 6  | Application information12               |

|    | 6.1 Oscillator                          |

|    | 6.2 Adaptive deadtime 15                |

|    | 6.3 Safe-start procedure 17             |

| 7  | Operation at no load or very light load |

| 8  | Current sensing, OCP and OLP 24         |

| 9  | Capacitive-mode detection function      |

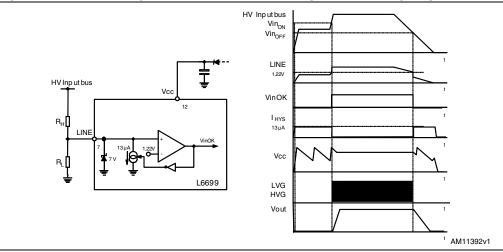

| 10 | Line sensing function                   |

| 11 | Latched shutdown                        |

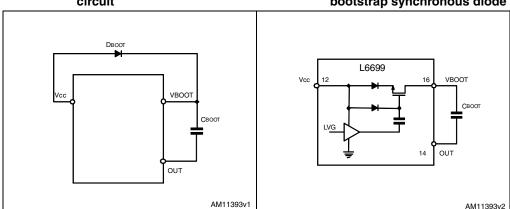

| 12 | Bootstrap section                       |

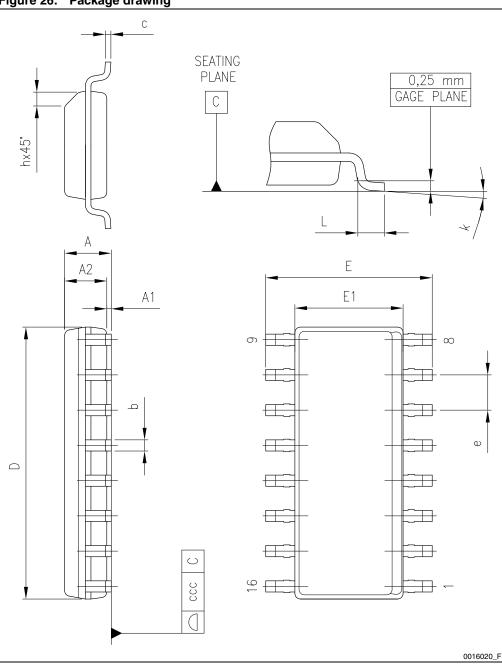

| 13 | Package information                     |

| 14 | Revision history                        |

# List of figures

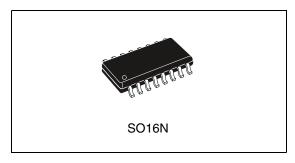

| Figure 1.  | Block diagram                                                                                   | 1          |

|------------|-------------------------------------------------------------------------------------------------|------------|

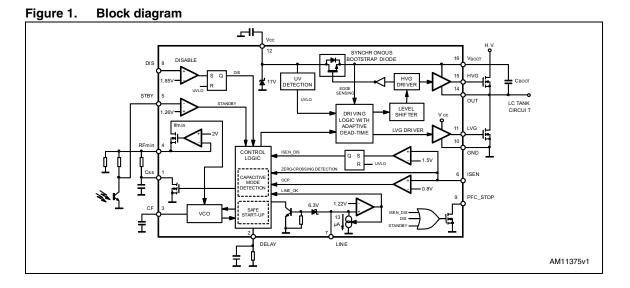

| Figure 2.  | Pin connections (top view)                                                                      | 6          |

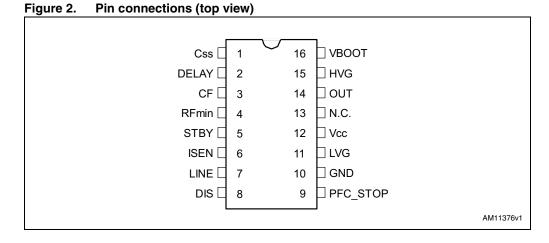

| Figure 3.  | Typical system block diagram.                                                                   |            |

| Figure 4.  | Multimode operation of the L6699 1                                                              |            |

| Figure 5.  | Oscillator's internal block diagram1                                                            |            |

| Figure 6.  | Oscillator waveforms and their relationship with gate-driving signals                           |            |

| Figure 7.  | Adaptive deadtime: principle schematic                                                          |            |

| Figure 8.  | Relevant timing diagrams                                                                        |            |

| Figure 9.  | Detailed view of deadtime during low-to-high transition of half bridge midpoint 1               |            |

| Figure 10. | Comparison startup behavior: traditional controller (left), with L6699 (right) 1                |            |

| Figure 11. | Comparison of initial cycles after startup: traditional controller (left), with L6699 (right) 1 |            |

| Figure 12. | Soft-start circuit.                                                                             | 20         |

| Figure 13. | Input impedance vs. frequency curve in an LLC resonant half bridge                              | 20         |

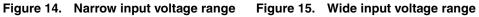

| Figure 14. | Narrow input voltage range.                                                                     | 21         |

| Figure 15. | Wide input voltage range                                                                        | 21         |

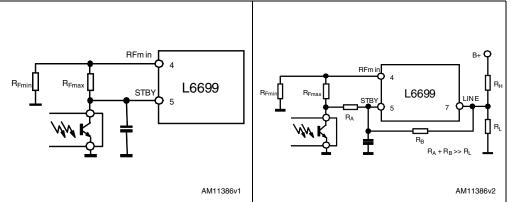

| Figure 16. | Load-dependent operating modes: timing diagram                                                  | 22         |

| Figure 17. | How the L6699 can switch off a PFC controller at light load                                     | 23         |

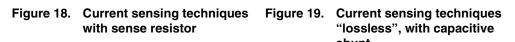

| Figure 18. | Current sensing techniques with sense resistor                                                  | 24         |

| Figure 19. | Current sensing techniques "lossless", with capacitive shunt                                    | <u>2</u> 4 |

| Figure 20. | Soft-start and delayed shutdown upon overcurrent timing diagram                                 |            |

|            | (safe-start details are not shown) 2                                                            | 27         |

| Figure 21. | Details of hard-switching transition during capacitive-mode operation                           | 28         |

| Figure 22. | Line sensing function: internal block diagram and timing diagram                                | 31         |

| Figure 23. | Bootstrap supply: standard circuit.                                                             | 33         |

| Figure 24. | Bootstrap supply: internal bootstrap synchronous diode                                          | 33         |

| Figure 25. | SO16N dimensions                                                                                | 34         |

| Figure 26. | Package drawing                                                                                 | 35         |

| Figure 27. | Recommended footprint (dimensions are in mm)                                                    | 36         |

## 1 Description

The L6699 is a double-ended controller specific to series-resonant half bridge topology. Both LLC and LCC configurations are supported. It provides symmetrical complementary duty cycle: the high-side switch and the low-side switch are driven ON/OFF 180° out-ofphase for exactly the same time. Output voltage regulation is obtained by modulating the operating frequency. The deadtime inserted between the turn-off of one switch and the turnon of the other one is automatically adjusted to best fit the transition times of the half bridge midpoint. To drive the high-side switch with the bootstrap approach, the IC incorporates a high voltage floating structure able to withstand more than 600 V with a synchronous-driven high voltage DMOS that replaces the external fast-recovery bootstrap diode.

The IC enables the user to set the operating frequency range of the converter by means of a high-accuracy externally programmable oscillator.

At startup, in addition to the traditional frequency-shift soft-start (the switching frequency starts from a preset maximum value and then decays as far as the steady-state value determined by the control loop), a proprietary circuit controls the half bridge to prevent hard-switching from occurring in the initial cycles because of the unbalance in the V·s applied to the transformer.

At light load the IC can be forced to enter a controlled burst-mode operation that keeps the converter input consumption as low as possible.

IC protection functions include a current sense input for OCP with frequency shift and delayed shutdown with automatic restart. Fast shutdown with automatic restart occurs if this first-level protection cannot control the primary current. Additionally, the IC prevents the converter from working in or too close to the capacitive mode, to guarantee soft-switching. A latched disable input (DIS) can be used to implement OTP and/or OVP. The combination of these protection features offers the highest degree of safety.

Other functions include a not-latched active-low disable input with current hysteresis, useful for power sequencing or for brownout protection, and an interface with the PFC controller that enables the switching-off of the pre-regulator during fault conditions or during burst-mode operation.

### L6699

# 2 Electrical ratings

| Table 2. Absolute maximum ratings            |    |                                                             |                                                                                          |      |

|----------------------------------------------|----|-------------------------------------------------------------|------------------------------------------------------------------------------------------|------|

| Symbol Pin                                   |    | Parameter                                                   | Value                                                                                    | Unit |

| V <sub>BOOT</sub>                            | 16 | Floating supply voltage ( $I_{leak} \le 5\mu A$ )           | -1 to 618                                                                                | V    |

| HVG                                          | 15 | HVG voltage V <sub>OUT</sub> -0.3 to V <sub>BOOT</sub> +0.3 |                                                                                          | V    |

| V <sub>OUT</sub>                             |    |                                                             | -3 up to a value included<br>in the range V <sub>BOOT</sub> -18<br>and V <sub>BOOT</sub> | V    |

| dV <sub>OUT</sub> /dt                        | 14 | Floating ground max. slew rate                              | 50                                                                                       | V/ns |

| V <sub>CC</sub>                              | 12 | IC supply voltage (Icc $\leq$ 25 mA)                        | Self-limited                                                                             | V    |

| LVG                                          | 11 | LVG voltage -0.3 to V <sub>CC</sub> +0.3                    |                                                                                          | V    |

| $V_{PFC\_STOP}$                              | 9  | Maximum voltage (pin open)                                  | -0.3 to V <sub>CC</sub>                                                                  | V    |

| I <sub>PFC_STOP</sub>                        | 9  | Maximum sink current (pin low)                              | Self-limited                                                                             | А    |

| V <sub>LINEmax</sub>                         | 7  | Maximum pin voltage (Ipin ≤1 mA)                            | Self-limited                                                                             | V    |

| I <sub>RFmin</sub>                           | 4  | Maximum source current                                      | 2                                                                                        | mA   |

| VISEN                                        | 6  | Current sense voltage                                       | -3 to 5                                                                                  | V    |

| 1 to 5,<br>8 Analog inputs & outputs voltage |    | -0.3 to 5                                                   | V                                                                                        |      |

| Тj                                           |    | Junction temperature operating range                        | ng range -40 to 150                                                                      |      |

| T <sub>stg</sub>                             |    | Storage temperature                                         | -55 to 150                                                                               | °C   |

Table 2.Absolute maximum ratings

# 3 Thermal data

### Table 3. Thermal data

| Symbol                | Parameter                                            | Value | Unit |

|-----------------------|------------------------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Max. thermal resistance, junction-to-ambient (SO16N) | 120   | °C/W |

| P <sub>tot</sub>      | Power dissipation @tamb = 50 °C (SO16N)              | 0.83  | W    |

## 4 Pin connections

Table 4. Pin functions

| N. | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | C <sub>SS</sub> | Soft-start. This pin connects an external capacitor to GND and a resistor to $RF_{min}$ (pin 4) that set both the initial oscillator frequency and the time constant for the frequency shift that occurs as the chip starts up (soft-start). An internal switch discharges this capacitor every time the chip turns off (V <sub>CC</sub> < UVLO, LINE < 1.25 V, DIS > 1.85 V, ISEN > 1.5 V, DELAY > 2 V) to make sure it is soft-started next. Additionally the switch is activated when the voltage on the current sense pin (ISEN) exceeds 0.8 V or when the converter is working too close to, or in, the capacitive-mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2  | DELAY           | Delayed shutdown upon overcurrent. A capacitor and a resistor are connected from this pin to GND to set both the maximum duration of an overcurrent condition before the IC stops switching and the delay after which the IC restarts switching. Every time the voltage on the ISEN pin exceeds 0.8 V the capacitor is charged by 350 $\mu$ A current pulses and is slowly discharged by the external resistor. If the voltage on the DELAY pin reaches 2 V, the soft-start capacitor is completely discharged so that the switching frequency is pushed to its maximum value and the 350 $\mu$ A current source is kept always on. As the voltage on the DELAY pin exceeds 3.5 V the IC stops switching and the internal generator is turned off, so that the voltage on the pin decays because of the external resistor. The IC is soft-restarted as the voltage drops below 0.3 V. In this way, under short-circuit conditions, the converter works intermittently with very low input average power. If the voltage on the ISEN pin exceeds 1.5 V, the L6699 is immediately stopped and the 350 $\mu$ A current source is kept on until the voltage on the DELAY pin reaches 3.5 V. Then, the generator is turned off and the voltage on the pin decays because of the external resistor. Also in this case the IC is soft-restarted as the voltage on the DELAY pin reaches 3.5 V. Then, the generator is turned off and the voltage on the pin decays because of the external resistor. Also in this case the IC is soft-restarted as the voltage drops below 0.3 V. |

| 3  | CF              | Timing capacitor. A capacitor connected from this pin to GND is charged and discharged by internal current generators programmed by the external network connected to pin 4 ( $RF_{min}$ ) and determines the switching frequency of the converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| N. | Name              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4  | RF <sub>min</sub> | Minimum oscillator frequency setting. This pin provides an accurate 2 V reference, and a resistor connected from this pin to GND defines a current that is used to set the minimum oscillator frequency. To close the feedback loop that regulates the converter output voltage by modulating the oscillator frequency, the phototransistor of an optocoupler is connected to this pin through a resistor. The value of this resistor sets the maximum operating frequency. Initial operating frequency should be set below 300 kHz; it is recommended not to exceed such limit. An R-C series connected from this pin to GND sets frequency shift at startup to prevent excessive energy inrush (soft-start).                                                                                                                                                                                                           |

| 5  | STBY              | Burst-mode operation threshold. The pin senses some voltage related to the feedback control, which is compared to an internal reference (1.26 V). If the voltage on the pin is lower than the reference, the IC enters an idle state and its quiescent current is reduced. The chip restarts switching as the voltage exceeds the reference by 30 mV. Soft-start is not invoked. This function realizes burst-mode operation when the load falls below a level that can be programmed by properly choosing the resistor connecting the optocoupler to the RF <sub>min</sub> pin (see <i>Figure 1: Block diagram</i> ). Tie the pin to RF <sub>min</sub> if burst-mode is not used.                                                                                                                                                                                                                                       |

| 6  | ISEN              | Current sense input. The pin senses the instantaneous primary current though a sense resistor or a capacitive divider for lossless sensing. If the voltage exceeds a 0.8 V threshold the soft-start capacitor connected to pin 1 is internally discharged: the frequency increases and so limits the power throughput. Under output short-circuit, this normally results in a nearly constant peak primary current. This condition is allowed for a maximum time set at pin 2. If the current keeps on building up despite this frequency increase, a second comparator referenced to 1.5 V disables switching immediately and activates a restart delay procedure (see DELAY pin description for more information). This pin is used also for capacitive-mode operation detection and for hard-switching prevention at startup. Do not short the pin to ground; this would prevent the device from operating correctly. |

| 7  | LINE              | Line sensing input. The pin is to be connected to the high voltage input bus with a resistor divider to perform either AC or DC (in systems with PFC) brownout protection. A voltage below 1.25 V shuts down the IC, lowers its consumption and discharges the soft-start capacitor. IC operation is enabled as the voltage exceeds 1.25 V. The comparator is provided with current hysteresis: an internal 13 $\mu$ A current generator is ON as long as the voltage applied at the pin is below 1.25 V, and is OFF if this value is exceeded. Bypass the pin with a capacitor to GND to reduce noise pick-up. The voltage on the pin is top-limited by an internal Zener. Tie the pin to V <sub>CC</sub> with a =100 k $\Omega$ resistor if not used.                                                                                                                                                                  |

| 8  | DIS               | Latched device shutdown. Internally, the pin connects a comparator that, when the voltage on the pin exceeds 1.85 V, shuts the IC down and brings its consumption almost to a "before startup" level. The information is latched and it is necessary to recycle the supply voltage of the IC to enable it to restart: the latch is removed as the voltage on the $V_{CC}$ pin goes below the UVLO threshold. Tie the pin to GND if the function is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9  | PFC_STOP          | Open-drain ON/OFF control of PFC controller. This pin, normally open, is intended for stopping the PFC controller, for protection purposes or during burst-mode operation. It goes low when the IC is shut down by DIS > 1.85 V, ISEN > 1.5 V and STBY < 1.25 V. The pin is pulled low also when capacitive mode operation is detected and when the voltage on the DELAY pin exceeds 2 V. In this latter case it goes back open as the voltage falls below 0.3 V. During UVLO, it is open. Leave the pin unconnected if not used.                                                                                                                                                                                                                                                                                                                                                                                        |

Table 4.

Pin functions (continued)

| N. | Name              | Function                                                                                                                                                                                                                                                                             |

|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | GND               | Chip ground. Current return for both the low-side gate-drive current and the bias current of the IC. All of the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                              |

| 11 | LVG               | Low-side gate-drive output. The driver is capable of 0.3 A min. source and 0.8 A min. sink peak current to drive the lower MOSFET of the half bridge leg. The pin is actively pulled to GND during UVLO.                                                                             |

| 12 | V <sub>CC</sub>   | Supply voltage of both the signal part of the IC and the low-side gate driver. Sometimes a small bypass capacitor (0.1 $\mu$ F typ.) to GND may be useful to obtain a clean bias voltage for the signal part of the IC.                                                              |

| 13 | N.C.              | High voltage spacer. The pin is not internally connected to isolate the high voltage pin and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                 |

| 14 | OUT               | High-side gate-drive floating ground. Current return for the high-side gate-drive current. Lay out the connection of this pin carefully to avoid too large spikes below ground.                                                                                                      |

| 15 | HVG               | High-side floating gate-drive output. The driver is capable of 0.3 A min. source<br>and 0.8 A min. sink peak current to drive the upper MOSFET of the half bridge<br>leg. A resistor internally connected to pin 14 (OUT) ensures that the pin is not<br>floating during UVLO.       |

| 16 | V <sub>BOOT</sub> | High-side gate-drive floating supply voltage. The bootstrap capacitor connected between this pin and pin 14 (OUT) is fed by an internal synchronous bootstrap diode driven in-phase with the low-side gate-drive. This patented structure replaces the normally used external diode. |

Table 4. Pin functions (continued)

### Figure 3. Typical system block diagram

## 5 Electrical data

Tj = -25 to +125 °C, V<sub>CC</sub> = 15 V, V<sub>BOOT</sub> = 15 V, C<sub>HVG</sub> = C<sub>LVG</sub> = 1 nF; C<sub>F</sub> = 470 pF; RF<sub>min</sub> = 12 K $\Omega$ ; unless otherwise specified.

Table 5.

Electrical characteristics

| Symbol                | Parameter                                    | Test condition                                                                        | Min. | Тур. | Max. | Unit  |

|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|-------|

| lc supply v           | oltage                                       |                                                                                       |      |      |      |       |

| V <sub>CC</sub>       | Operating range                              | After device turn-on                                                                  | 8.85 |      | 16   | V     |

| V <sub>CCOn</sub>     | Turn-on threshold                            | Voltage rising                                                                        | 10   | 10.7 | 11.4 | V     |

| V <sub>CCOff</sub>    | Turn-off threshold                           | Voltage falling                                                                       | 7.45 | 8.15 | 8.85 | V     |

| Hys                   | Hysteresis                                   |                                                                                       |      | 2.55 |      | V     |

| Vz                    | V <sub>CC</sub> clamp voltage                | Iclamp = 15 mA                                                                        | 16   | 17   | 17.9 | V     |

| Supply cur            | rent                                         |                                                                                       |      |      |      |       |

| I <sub>start-up</sub> | Startup current                              | Before device turn-on<br>$V_{CC} = V_{CCOn} - 0.2 V$                                  |      | 250  | 300  | μA    |

| ۱ <sub>q</sub>        | Quiescent current                            | Device on, V <sub>STBY</sub> = 1 V                                                    |      | 1    | 1.3  | mA    |

| I <sub>op</sub>       | Operating current                            | Device on, $V_{STBY} = V_{RFmin}$                                                     |      | 3    | 4.1  | mA    |

| ۱ <sub>q</sub>        | Residual consumption                         | $V_{\text{DIS}} > 1.92$ V or $V_{\text{DELAY}} > 3.65$ V or $V_{\text{LINE}} < 1.2$ V |      | 400  | 500  | μA    |

| High-side f           | loating gate-drive supply                    |                                                                                       |      | •    | •    |       |

| R <sub>DS(on)</sub>   | Synchronous bootstrap diode<br>ON-resistance | V <sub>LVG</sub> = high                                                               |      | 150  |      |       |

| Overcurren            | t comparator                                 |                                                                                       |      |      |      |       |

| I <sub>ISEN</sub>     | Input bias current                           | V <sub>ISEN</sub> = 0 to V <sub>ISENdis</sub>                                         |      |      | -1   | μA    |

| V <sub>ISENx</sub>    | Frequency shift threshold                    | Voltage rising <sup>(1)</sup>                                                         | 0.76 | 0.80 | 0.84 | V     |

| V <sub>ISENdis</sub>  | Immediate stop threshold                     | Voltage rising <sup>(1)</sup>                                                         | 1.43 | 1.5  | 1.55 | V     |

| Line sensir           | ng                                           |                                                                                       |      |      |      |       |

| V <sub>LINE</sub>     | Threshold voltage                            | Voltage rising or falling <sup>(1)</sup>                                              | 1.18 | 1.22 | 1.26 | V     |

| I <sub>Hys</sub>      | Current hysteresis                           | V <sub>LINE</sub> = 1.2 V                                                             | 10   | 13   | 16   | μA    |

| V <sub>clamp</sub>    | Clamp level                                  | I <sub>LINE</sub> = 1 mA                                                              | 6    |      |      | V     |

|                       | sable function                               |                                                                                       |      |      |      |       |

| I <sub>DIS</sub>      | Input bias current                           | V <sub>DIS</sub> = 0 to 1.92 V                                                        |      |      | -1   | μA    |

| V <sub>DIS</sub>      | Disable threshold                            | Voltage rising <sup>(1)</sup>                                                         | 1.78 | 1.85 | 1.92 | V     |

| Oscillator            |                                              |                                                                                       |      |      |      |       |

| 4                     |                                              |                                                                                       | 58.2 | 60   | 61.8 | 1.11- |

| f <sub>osc</sub>      | Oscillation frequency                        | $R_{\rm RFmin}$ = 2.7 k $\Omega$                                                      | 225  | 235  | 245  | kHz   |

| Table 5.                      | Electrical characteristics (                     | continued)                                                               |      | r    |      |      |

|-------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| Symbol                        | Parameter                                        | Test condition                                                           | Min. | Тур. | Max. | Unit |

| T <sub>D</sub> <sup>(2)</sup> | Deadtime self-adjustment                         | Minimum value                                                            |      | 0.23 |      | 110  |

| D'                            | range                                            | Maximum value                                                            |      | 0.7  |      | μs   |

| V <sub>CFp</sub>              | Peak value                                       |                                                                          |      | 3.9  |      | V    |

| V <sub>CFv</sub>              | Valley value                                     |                                                                          |      | 0.9  |      | V    |

| N/                            | Veltage reference on him 4                       | (1)                                                                      | 1.93 | 2    | 2.07 | V    |

| V <sub>REF</sub>              | Voltage reference on pin 4                       | $I_{REF} = -2 \text{ mA}^{(1)}$                                          | 1.8  | 2    | 2.07 | V    |

| K <sub>M</sub>                | Current mirroring ratio                          |                                                                          |      | 1    |      | A/A  |

| RF <sub>min</sub>             | Timing resistor range                            |                                                                          | 1    |      | 100  | kΩ   |

| Zero-curren                   | t comparator                                     |                                                                          |      |      |      |      |

| V <sub>ZCD neg</sub>          | Threshold voltage (-)                            |                                                                          |      | -10  |      | mV   |

| V <sub>ZCD pos</sub>          | Threshold voltage (+)                            |                                                                          |      | +10  |      | mV   |

| Pfc_stop fu                   | nction                                           |                                                                          |      |      |      |      |

| l <sub>leak</sub>             | High level leakage current                       | $V_{PFC\_STOP} = V_{CC}, V_{DIS} = 0 V$                                  |      |      | 1    | μA   |

| R <sub>PFC_STOP</sub>         | ON-state resistance                              | $I_{PFC\_STOP} = 1 \text{ mA}, V_{DIS} > 1.92 \text{ V}$                 |      | 130  | 200  | Ω    |

| Soft-start fu                 | inction                                          |                                                                          |      |      |      |      |

| I <sub>leak</sub>             | Open-state current                               | $V(C_{SS}) = 2 V$                                                        |      |      | 0.5  | μA   |

| R                             | Discharge resistance                             |                                                                          |      | 120  |      | Ω    |

| T <sub>DISCH</sub>            | C <sub>SS</sub> discharge duration               | V <sub>ISEN</sub> > V <sub>ISENx</sub> or approaching<br>capacitive-mode |      | 5    |      | μs   |

| DISOT                         |                                                  | Capacitive-mode detected                                                 |      | 50   |      |      |

| Standby fur                   | nction                                           | I                                                                        |      |      |      |      |

| I <sub>STBY</sub>             | Input bias current                               | V <sub>STBY</sub> = 0 to 1.3 V                                           |      |      | -1   | μA   |

| V <sub>STBY</sub>             | Disable threshold                                | Voltage falling <sup>(1)</sup>                                           | 1.22 | 1.26 | 1.3  | V    |

| Hys                           | Hysteresis                                       | Voltage rising                                                           |      | 30   |      | mV   |

| Delayed shu                   | utdown function                                  | ł                                                                        |      | Į    |      | Į    |

|                               |                                                  | V <sub>DELAY</sub> = 1 V                                                 |      | 1    |      |      |

| l <sub>leak</sub>             | Open-state current                               | V <sub>DELAY</sub> = 1 V, after shutdown                                 |      | -0.1 | -0.5 | μA   |

| I <sub>CHARGE</sub>           | Charge current                                   | V <sub>DELAY</sub> = 2.5 V, V <sub>ISEN</sub> = 0.85 V                   | 250  | 350  | 450  | μA   |

| Vth <sub>1</sub>              | Threshold for forced operation at max. frequency | Voltage rising <sup>(1)</sup>                                            | 1.92 | 2.0  | 2.08 | V    |

| Vth <sub>2</sub>              | Shutdown threshold                               | Voltage rising <sup>(1)</sup>                                            | 3.35 | 3.5  | 3.65 | V    |

| Vth <sub>3</sub>              | Restart threshold                                | Voltage falling <sup>(1)</sup>                                           | 0.27 | 0.3  | 0.33 | V    |

| Low-side ga                   | ate driver (voltages referred to                 |                                                                          | I    | 1    | I    | 1    |

| V <sub>LVGL</sub>             | Output low voltage                               | I <sub>sink</sub> = 200 mA                                               |      |      | 1.5  | V    |

| V <sub>LVGH</sub>             | Output high voltage                              | I <sub>source</sub> = 5 mA                                               | 12.8 | 13.3 |      | V    |

Table 5.

Electrical characteristics (continued)

10/38

Doc ID 022835 Rev 2

57

| L | 6699 |  |

|---|------|--|

|   | 0033 |  |

| Symbol                | Parameter                        | Test condition                                 | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------|------------------------------------------------|------|------|------|------|

| I <sub>sourcepk</sub> | Peak source current              |                                                | -0.3 |      |      | А    |

| I <sub>sinkpk</sub>   | Peak sink current                |                                                | 0.8  |      |      | А    |

| t <sub>f</sub>        | Fall time                        |                                                |      | 30   |      | ns   |

| t <sub>r</sub>        | Rise time                        |                                                |      | 60   |      | ns   |

|                       | UVLO saturation                  | $V_{CC} = 0$ to $V_{CCOn}$ , $I_{sink} = 2$ mA |      |      | 1.1  | V    |

| High-side g           | ate driver (voltages referred to | o out)                                         |      |      | •    |      |

| V <sub>LVGL</sub>     | Output low voltage               | I <sub>sink</sub> = 200 mA                     |      |      | 1.5  | V    |

| V <sub>LVGH</sub>     | Output high voltage              | I <sub>source</sub> = 5 mA                     | 12.8 | 13.3 |      | V    |

| I <sub>sourcepk</sub> | Peak source current              |                                                | -0.3 |      |      | Α    |

| I <sub>sinkpk</sub>   | Peak sink current                |                                                | 0.8  |      |      | Α    |

| t <sub>f</sub>        | Fall time                        |                                                |      | 30   |      | ns   |

| t <sub>r</sub>        | Rise time                        |                                                |      | 60   |      | ns   |

|                       | HVG-OUT pull-down                |                                                |      | 22   |      | kΩ   |

Table 5.

Electrical characteristics (continued)

1. Values tracking each other.

2. Refer to adaptive deadtime section, Figure 9.

## 6 Application information

The L6699 is an advanced double-ended controller specific to resonant half bridge topology. In these converters the MOSFETs of the half bridge leg are alternately switched on and off (180° out-of-phase) for exactly the same time. This is commonly referred to as symmetrical operation at "50% duty cycle", although the real duty cycle, i.e. the ratio of the ON-time of either switch to the switching period, is actually less than 50%. The reason is that there is a deadtime  $T_D$  inserted between the turn-off of either MOSFET and the turn-on of the other one, where both MOSFETs are off. This deadtime is essential in order for the converter to work correctly: it enables soft-switching and, then, high-frequency operation with high efficiency and low EMI emissions.

A special feature of this IC is that it is able to automatically adjust  $T_D$  within a range so that it best fits the transition times of the half bridge midpoint (adaptive deadtime). This allows the user to optimize the design of the resonant tank so that soft-switching can be achieved with a lower level of reactive energy (i.e. magnetizing current), therefore optimizing efficiency under a broader load range, from full to light load.

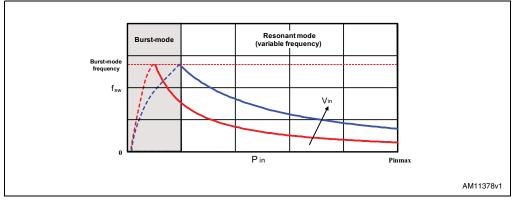

To perform converter output voltage regulation the device is able to operate in different modes (*Figure 1*), depending on the load conditions:

- Variable frequency at heavy and medium/light load. A relaxation oscillator (see Section 6.1: Oscillator for more details) generates a symmetrical triangular waveform, which MOSFET switching is locked to. The frequency of this waveform is related to a current that is modulated by the feedback circuitry. As a result, the tank circuit driven by the half bridge is stimulated at a frequency dictated by the feedback loop to keep the output voltage regulated, therefore exploiting its frequency-dependent transfer characteristics.

- 2. Burst-mode control with no or very light load. When the load falls below a value, the converter enters a controlled intermittent operation, where a series of a few switching cycles at a nearly fixed frequency are spaced out by long idle periods where both MOSFETs are in the OFF-state. A further load decrease is translated into longer idle periods and then in a reduction of the average switching frequency. When the converter is completely unloaded, the average switching frequency can go down even to few hundred hertz, therefore minimizing magnetizing current losses as well as all frequency-related losses and making it easier to comply with energy saving specifications.

### Figure 4. Multimode operation of the L6699

12/38

## 6.1 Oscillator

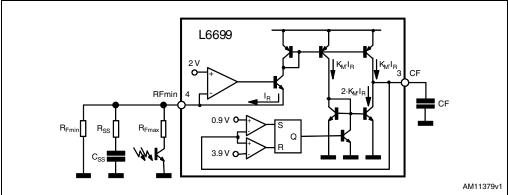

The oscillator is programmed externally by means of a capacitor (CF), connected from pin 3 (CF) to ground, that is alternately charged and discharged by the current defined with the network connected to pin 4 ( $RF_{min}$ ). The pin provides an accurate 2 V reference with about 2 mA source capability; the higher the current sourced by the pin, the higher the oscillator frequency. The block diagram of *Figure 5* shows a simplified internal circuit that explains the operation.

The network that loads the  $\mathsf{RF}_{\min}$  pin generally comprises three branches:

- 1. a resistor RF<sub>min</sub> connected between the pin and ground that determines the minimum operating frequency.

- 2. a resistor RFmax connected between the pin and the collector of the (emittergrounded) phototransistor that transfers the feedback signal from the secondary side back to the primary side; while in operation, the phototransistor modulates the current through this branch - therefore modulating the oscillator frequency - to perform output voltage regulation; the value of RFmax determines the maximum frequency the half bridge is operated at when the phototransistor is fully saturated.

- an R-C series circuit (C<sub>SS</sub>+ R<sub>SS</sub>) connected between the pin and ground that enables the setting up of a frequency shift at startup (see Section 6.3: Safe-start procedure). Note that the contribution of this branch is zero during steady-state operation.

### Figure 5. Oscillator's internal block diagram

The following approximate relationships hold for the minimum and the maximum oscillator frequency respectively:

Equation 1

$$f_{min} = \frac{1}{3 \cdot CF \cdot RF_{min}} \quad ; \quad f_{max} = \frac{1}{3 \cdot CF \cdot (RF_{min} // RF_{max})}$$

| After fixing CF | according to Table 6: |

|-----------------|-----------------------|

|-----------------|-----------------------|

Table 6.

Recommended values for CF as a function of the startup frequency f<sub>start</sub>

| f <sub>start</sub> [kHz] | CF [pF] | f <sub>start</sub> [kHz] | CF [pF] |

|--------------------------|---------|--------------------------|---------|

| 150                      | 680     | 230 - 240                | 180     |

| 160                      | 560     | 250                      | 150     |

| 170                      | 470     | 260                      | 120     |

| 180                      | 390     | 270                      | 100     |

| 190 – 200                | 330     | 280                      | 82      |

| 210                      | 270     | 290                      | 68      |

| 220                      | 220     | 300                      | 56      |

Value of  $RF_{min}$  and  $RF_{max}$  is selected so that the oscillator frequency is able to cover the entire range needed for regulation, from the minimum value  $f_{min}$  (at minimum input voltage and maximum load) to the maximum value  $f_{max}$  (at maximum input voltage and minimum load):

Equation 2

$$\mathsf{RF}_{\mathsf{min}} = \frac{1}{3 \cdot \mathsf{CF} \cdot \mathsf{f}_{\mathsf{min}}} \quad ; \quad \mathsf{RF}_{\mathsf{max}} = \frac{\mathsf{RF}_{\mathsf{min}}}{\frac{\mathsf{f}_{\mathsf{max}}}{\mathsf{f}_{\mathsf{min}}} - 1}$$

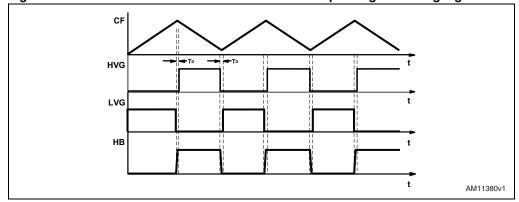

Figure 6. Oscillator waveforms and their relationship with gate-driving signals

A different selection criterion is given for RF<sub>max</sub> if burst-mode operation is to be used (see *Section 7: Operation at no load or very light load*).

In *Figure 6* the timing relationship between the oscillator waveform and the gate-drive signal, as well as the midpoint of the half bridge leg (HB) is shown. Note that the low-side gate-drive is turned on while the oscillator's triangle is ramping up and the high-side gate-drive is turned on while the triangle is ramping down. In this way, at startup, or as the IC resumes switching during burst-mode operation, the low-side MOSFET is switched on first to charge the bootstrap capacitor. As a result, the bootstrap capacitor is always charged and ready to supply the high-side floating driver (see *Section 12: Bootstrap section*).

Doc ID 022835 Rev 2

14/38

### 6.2 Adaptive deadtime

A deadtime  $T_D$  inserted between the turn-off of either switch and the turn-on of the complementary one, where both switches are in the OFF-state, is essential to achieve soft-switching. Its value must be larger than the time  $T_T$  needed for the rail-to-rail swing of the half bridge midpoint. This duration  $T_T$  depends on the total parasitic capacitance of the half bridge midpoint, which must be completely charged or depleted and the value of the resonant tank current during the transition.

With good approximation, the tank current during the transition time  $T_T$  can be considered constant and equal to the "switched current"  $I_S$ , i.e. the value of the tank current as the transition begins. If  $C_{HB}$  denotes the total parasitic capacitance of the half bridge midpoint (it includes the Coss of the MOSFETs, the transformer's primary winding parasitic capacitance, plus other stray contributors), the condition for soft-switching is:

Equation 3

$$T_{T} = \frac{C_{HB}}{I_{S}} Vin \le T_{D}$$

which should be met under all operating conditions. This formula suggests that  $T_D$  should be large enough to always exceed  $T_T$ , especially with maximum Vin and at no load, where  $I_S$  is at a minimum and  $T_T$  at a maximum. However, a too long deadtime may lead to the loss of soft-switching too: in fact, the tank current must not change its sign within the deadtime, which could lead to the turn-on of either MOSFET with a non-zero drain-to-source voltage or, even worse, with the body diode of the other MOSFET conducting (capacitive mode operation - see *Section 9: Capacitive-mode detection function* for more details). This may occur at maximum load and minimum Vin, especially when the tank circuit is designed for a low magnetizing current to optimize light load efficiency. Additionally, a too long deadtime may increase conduction losses in the body diodes and significantly limit the operating frequency of the half bridge.

A good approach is to automatically adjust  $T_D$  so that it tracks  $T_T$ , keeping  $T_T \leq T_D$  under all operating conditions. This is the objective of the adaptive deadtime function in the L6699.

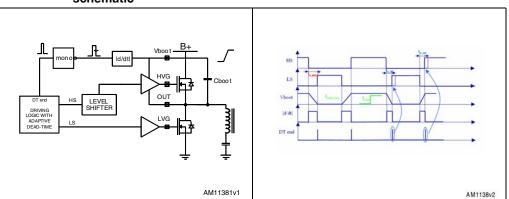

*Figure 7* and *Figure 8* show the principle schematic and its key waveforms. An edge detector (the ld/dtl block) senses that the half bridge midpoint (connected to the OUT pin) is swinging from B+ to GND or vice versa through the  $V_{BOOT}$  pin, which moves exactly following the OUT pin (due to Cboot there is a DC voltage difference between them). The output of the ld/dtl block is high as long as the OUT pin is swinging and, as the transition is completed, the output goes low. A monostable circuit, sensitive to negative-going edges, releases a pulse that marks the end of the deadtime.

# Figure 7. Adaptive deadtime: principle Figure 8. Relevant timing diagrams schematic

Note that the "Driving logic…" block sets a minimum deadtime  $T_{D\_MIN}$  ( $\approx 230$  ns) below which  $T_D$  cannot go, to prevent simultaneous conduction of the high-side and the low-side switch, and also a maximum deadtime  $T_{D\_MAX}$  to guarantee proper operation of the half bridge.  $T_{D\_MAX}$  is internally set at either 700 ns or one fourth of the oscillator cycle, whichever is shorter.

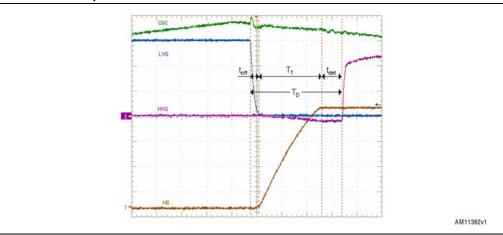

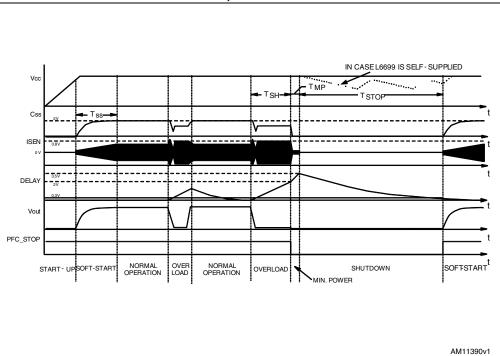

Figure 9. Detailed view of deadtime during low-to-high transition of half bridge midpoint

The actual deadtime  $T_D$  that can be observed during operation does not depend only on the adjustment circuit of *Figure 7*. This fact can be explained with the aid of the oscilloscope image shown in *Figure 9*.

It illustrates a detailed view of the low-to-high transition of the half bridge midpoint (waveform labeled HB) along with the high-side gate-drive (HVG), the low-side gate-drive (LVG) and the oscillator voltage on pin CF (OSC). Obviously, the information that follows applies to the high-to-low transition as well.

There are three contributors to  $T_D$ :

- The turn-off delay t<sub>OFF</sub> of the Power MOSFET, which depends on the input characteristics of the specific MOSFET and the speed its gate is driven

- The transition time T<sub>T</sub> the half bridge midpoint takes for a rail-to-rail swing

- The detection time t<sub>det</sub> that elapses from the end of the half bridge midpoint swing to the gate-drive signal of the other MOSFET going high; this includes the detection time as well as the propagation delay along the downstream logic circuitry up to the driver output.

It is important to point out that the value of  $T_{D\_MIN}$  specified in the electrical characteristics is essentially tdet: therefore the minimum observable  $T_D$  is always longer.  $T_{D\_MAX}$ , on the other hand, is counted starting from the negative-going edge of the gate-drive signal, so it actually fixes a maximum limit for  $T_D$ :  $T_D \leq T_{D\_MAX}$ .

Finally, it is worth stating that the adaptive deadtime function does not significantly increase efficiency by itself. It is a degree of freedom that must be exploited for this purpose when designing the resonant tank. Essentially, it allows the use of a higher magnetizing inductance in the transformer, which minimizes the magnetizing current and, then, the conduction losses associated to it. Additionally, this may reduce the switched current  $I_S$  to the minimum required to achieve soft-switching, therefore reducing turn-off switching losses in MOSFETs. Efficiency at medium and light load greatly benefits from this optimization.

### 6.3 Safe-start procedure

In the L6699 a new startup procedure, termed "safe-start", has been implemented to prevent loss of soft-switching during the initial switching cycles, which is not 100% guaranteed by the usual soft-start procedure.

Sweeping the operating frequency from an initial high value, that should not exceed 300 kHz, down to the point where the control loop takes over, which is commonly referred to as soft-start, has a twofold benefit. On the one hand, since the deliverable power depends inversely on frequency, it progressively increases the converter's power capability, therefore avoiding excessive inrush current. On the other hand, it makes the converter initially work at frequencies higher than the upper resonance frequency of the LLC tank circuit, which ensures inductive-mode operation (i.e. with the tank current lagging the square wave voltage generated by the half bridge) and, therefore, soft-switching.

However, the last statement is true under a quasi-static approximation, i.e. when the operating point of the resonant tank is slowly varying around a steady-state condition. This approximation is not correct during the very first switching cycles of the half bridge, where the initial conditions of the tank circuit can be away from those under steady-state. Therefore, hard-switching is possible during the transient period needed to reach the slowly varying steady-state condition dictated by the soft-start action. A non-zero initial voltage on the resonant capacitor Cr and transformer flux imbalance during the previously mentioned transient period are the possible causes of hard-switching in the initial cycles.

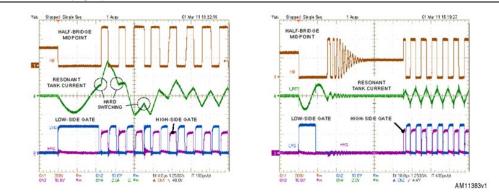

In high voltage half bridge controllers it is customary to start the switching activity by turning on the low-side MOSFET for a preset time to pre-charge the bootstrap capacitor (see *Section 12: Bootstrap section*) and ensure proper driving of the high-side MOSFET from the first cycle. In traditional controllers, normal switching starts right at the end of the pre-charge time, as shown in the left-hand image in *Figure 10*.

# Figure 10. Comparison startup behavior: traditional controller (left), with L6699 (right)

A non-zero initial voltage on the resonant capacitor may cause the very first turn-on of the high-side MOSFET to occur with non-zero drain-to-source voltage while the body diode of the low-side MOSFET is conducting, therefore invoking its reverse recovery. More hard-switching cycles may follow (see the left-hand image in *Figure 10*). These events are few but potentially hazardous: they could cause the destruction of both MOSFETs, should the resulting dv/dt across the low-side MOSFET exceed its maximum rating (see *Section 9: Capacitive-mode detection function* for more details).

To prevent this hard-switching cycle(s) with body diode reverse recovery, the L6699 waits about 50  $\mu$ s after the pre-charge time before starting switching (see the right-hand image in *Figure 10*). This idle time is normally long enough to let the tank current decay to essentially zero in case of an initially charged resonant capacitor. On the other hand, it is too short for the bootstrap capacitor to be significantly discharged.

To understand the origin of transformer flux imbalance it is worth remembering that the half bridge is driven with 50% duty cycle, so that under steady-state conditions the voltage across the resonant capacitor Cr has a DC component equal to Vin/2. Consequently, the transformer's primary winding is symmetrically driven by  $a \pm Vin/2$  square wave.

At startup, however, the voltage across Cr is often quite different from Vin/2, so it takes some time for its DC component to reach the steady-state value Vin/2. During this transient, the transformer is not driven symmetrically and, then, there is a significant V·s imbalance in two consecutive half-cycles. If this imbalance is large, there is a significant difference in the up and down slopes of the tank current and, the duration of the two half-cycles being the same, the current may not reverse in a switching half-cycle, as shown in the left-hand image in *Figure 11*. Once again, one MOSFET can be turned on while the body diode of the other is conducting and this may happen for a few cycles.

To prevent this, the L6699 is provided with a proprietary circuit that modifies the normal operation of the oscillator during the initial switching cycles, so that the initial V·s unbalance is nearly eliminated. Its operation is such that current reversal in every switching half-cycle and, then, soft-switching is ensured.

L6699

# Figure 11. Comparison of initial cycles after startup: traditional controller (left), with L6699 (right)

It goes without saying that when either MOSFET is turned on for the very first time, this occurs with a non-zero drain-to-source voltage. Therefore, strictly speaking, hard-switching is still there. However, this type of one-shot hard-switching, where the body diode of the other MOSFET is not reverse recovered, is of little concern. In fact, the related capacitive power loss is thermally insignificant and, with a proper gate-drive circuit, spurious turn-on of the other MOSFET through Cgd injection is easily prevented.

The timing diagrams of *Figure 11* compare the startup behavior of a resonant converter driven by a traditional resonant controller with that of a converter driven by the L6699. During the initial phase, the ramps of the oscillator are synchronized to the zero-crossings of the tank current, so that a trapezoidal waveform appears across CF. As a result, the duty cycle of the half bridge is initially considerably less than 50% and the tank current changes its sign every half-cycle. The device goes to normal operation after approximately 50  $\mu$ s from the first switching cycle. If the timing capacitor CF is selected according to *Table 6*, this transition is nearly seamless and just a small perturbation of the tank current can be observed.

Using capacitor values significantly different from those provided in *Table 6* might cause large perturbations during the transition. This might bring the half bridge close to losing soft-switching with a consequent activation of the capacitive-mode detection function.

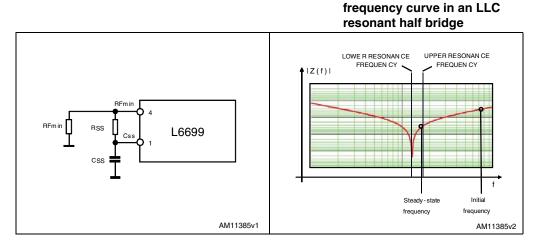

With the L6699 the soft-start function is easily realized with the addition of an R-C series circuit from pin 4 ( $RF_{min}$ ) to ground (see *Figure 13*).

Initially, the capacitor  $C_{SS}$  is totally discharged, so that the series resistor  $R_{SS}$  is effectively parallel with  $RF_{min}$  and the resulting initial frequency is determined by  $R_{SS}$  and  $RF_{min}$  only, as the optocoupler's phototransistor is cut off (as long as the output voltage is not too far away from the regulated value):

Equation 4

$$f_{start} = \frac{1}{3 \cdot CF \cdot (RF_{min} //R_{SS})}$$

The  $C_{SS}$  capacitor is progressively charged until its voltage reaches the reference voltage (2 V) and, consequently, the current through  $R_{SS}$  goes to zero. This conventionally takes 5 times the constants  $R_{SS}$   $C_{SS}$ , however, the soft-start phase really ends when the output voltage has got close to the regulated value and the feedback loop has taken over, so that

Figure 12. Soft-start circuit

the operating frequency is essentially determined by the current sunk by the optocoupler's phototransistor.

During this frequency sweep phase the operating frequency decays following the exponential charge of  $C_{SS}$ : then, it initially changes relatively quickly but the rate of change gets slower and slower. This counteracts the non-linear frequency dependence of the tank circuit that makes the converter's input impedance change little as frequency is away from resonance and change very quickly as frequency approaches resonance frequency (see *Figure 13*).

Figure 13. Input impedance vs.

As a result, the DC input current smoothly increases, without the peaking that occurs with linear frequency sweep, and the output voltage reaches the regulated value with almost no overshoot.

Typically,  $R_{SS}$  and  $C_{SS}$  is selected based on the following relationships:

Equation 5

$$R_{ss} = \frac{RF_{min}}{\frac{f_{start}}{f_{min}} - 1} \quad ; \quad C_{ss} = \frac{3 \cdot 10^{-3}}{R_{ss}}$$

where f<sub>start</sub> is recommended to not be over 300 kHz. Please refer to the timing diagram of *Figure 20* to see some significant signals during the soft-start phase.

## 7 Operation at no load or very light load

When the resonant half bridge is lightly loaded or totally unloaded, its switching frequency reaches its maximum value. To keep the output voltage under control and avoid losing softswitching in these conditions, there must be some current flowing through the transformer's magnetizing inductance. This current can be kept relatively low because of the adaptive deadtime function; however, it produces power losses that prevent the converter's no load consumption from achieving very low values anyhow.

To overcome this issue, the L6699 enables the user to make the converter operate intermittently (burst-mode operation), with a series of a few switching cycles spaced out by long idle periods where both MOSFETs are in the OFF-state, so that the average switching frequency can be substantially reduced. As a result, the average value of the residual magnetizing current and the associated losses is considerably cut down, therefore facilitating the converter to comply with energy saving specifications.

The L6699 can be operated in burst-mode by using pin 5 (STBY): if the voltage applied to this pin falls below 1.26 V, the IC enters an idle state where both gate-drive outputs are low, the oscillator is stopped, the soft-start capacitor  $C_{SS}$  keeps its charge and only the 2V reference at the RF<sub>min</sub> pin stays alive to minimize IC consumption and V<sub>CC</sub> capacitor discharge. The IC resumes normal operation as the voltage on the pin exceeds 1.26 V by 30 mV.

In the L6699, the half bridge stops and restarts during burst-mode are more accurately controlled with respect to its predecessors: the last cycle before stopping and the first cycle after restarting are such that the DC voltage across the resonant capacitor Cr always stays close to its steady-state value Vin/2. In this way, the anomalous current peaks due to V·s unbalance in the transformer are minimized.

To implement burst-mode operation, the voltage applied to the STBY pin needs to be related to the feedback loop. *Figure 14* shows the simplest implementation, suitable to a narrow input voltage range (e.g. when there is a PFC front-end).

Essentially,  $RF_{max}$  defines the switching frequency  $f_{max}$  above which the L6699 enters burstmode operation. Once  $f_{max}$  is fixed,  $RF_{max}$  is found from the relationship:

Equation 6

$$\mathsf{RF}_{\max} = \frac{3}{8} \cdot \frac{\mathsf{RF}_{\min}}{\frac{\mathsf{f}_{\max}}{\mathsf{f}_{\min}} - 1}$$

Note that, unlike the  $f_{max}$  considered in the Section 6.1: Oscillator, here  $f_{max}$  is associated to some load Pout<sub>B</sub> greater than the minimum one. Pout<sub>B</sub> is normally such that the transformer's peak currents are low enough not to cause audible noise.

The resonant converter's switching frequency, however, depends also on the input voltage; so, in case there is quite a large input voltage range, with the circuit of *Figure 14* the value of Pout<sub>B</sub> would change considerably. In this case it is recommended to use the arrangement shown in *Figure 15*, where the information on the converter's input voltage is added to the voltage applied to the STBY pin. Due to the strongly non-linear relationship between switching frequency and input voltage, it is more practical to find empirically the right amount of correction  $R_A / (R_A + R_B)$  needed to minimize the change in Pout<sub>B</sub>. Take care in choosing the total value  $R_A + R_B$  much greater than  $R_L$  to minimize the effect on the LINE pin voltage (see *Section 10: Line sensing function*).

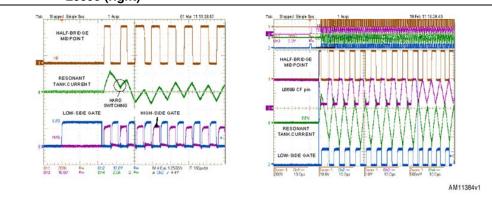

Figure 16. Load-dependent operating modes: timing diagram

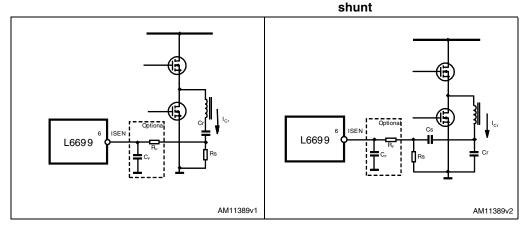

Whichever circuit is in use, its operation can be described as follows. As the load falls below the value  $Pout_B$  the frequency tries to exceed the maximum programmed value  $f_{max}$  and the voltage on the STBY pin (V<sub>STBY</sub>) goes below 1.26 V. The IC then stops with both gate-drive outputs low, so that both MOSFETs of the half bridge leg are in the OFF-state. The voltage  $V_{STBY}$  now increases as a result of the feedback reaction to the energy delivery stop and, as it exceeds 1.29 V, the IC restarts switching. After a while,  $V_{STBY}$  goes down again in response to the energy burst and stops the IC. In this way the converter works in a burst-mode fashion with a nearly constant switching frequency. A further load decrease then increases the time between consecutive bursts and/or reduces the duration of each burst. This reduces the average switching frequency, which can go down even to few hundred hertz. The timing diagram of *Figure 16* illustrates this kind of operation, showing the most significant signals. A small capacitor (typically in the hundred pF) from the STBY pin to ground, placed as close to the IC as possible to reduce switching noise pick-up, helps obtain clean operation.

Doc ID 022835 Rev 2

51

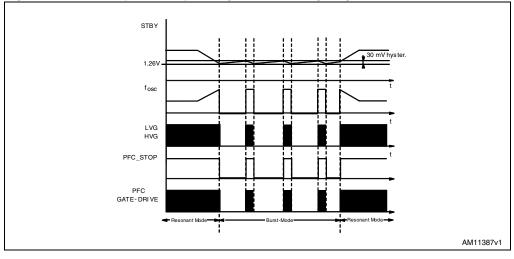

Figure 17. How the L6699 can switch off a PFC controller at light load

To help the user meet energy saving requirements even in power-factor-corrected systems, where a PFC pre-regulator precedes the DC-DC converter, the L6699 allows that the PFC pre-regulator can be turned off during burst-mode operation, therefore eliminating the no load consumption of this stage (0.5 - 1 W). There is no compliance issue in that, because EMC regulations on low-frequency harmonic emissions refer to nominal load, no limit is envisaged when the converter operates with light or no load.

To do so, the L6699 provides pin 8 (PFC\_STOP): it is an open drain output, normally open, that is asserted low when the IC is idle during burst-mode operation. This signal is externally used for switching off the PFC controller and the pre-regulator as shown in *Figure 17*. When the L6699 is in UVLO the pin is kept open to allow the PFC controller to start first.

The PFC\_STOP pin is also used by some protection functions (OCP, OLP and latched shutdown). Please refer to the relevant sections for more information.

In the L6699 the current sense input ISEN (pin 6) senses the current flowing in the resonant tank to perform multiple tasks:

- 1. Primary overcurrent protection (OCP function).

- 2. Hard-switching cycles prevention at startup (see Section 6.3: Safe-start procedure).

- 3. Capacitive-mode detection during operation (see *Section 9: Capacitive-mode detection function*).

In this section the discussion is concentrated on the OCP function.

Unlike PWM-controlled converters, where energy flow is controlled by the duty cycle of the primary switch (or switches), in a resonant half bridge the duty cycle is fixed and energy flow is controlled by its switching frequency. This has an impact on the way current limitation can be realized. While in PWM-controlled converters energy flow can be limited simply by terminating switch conduction in advance when the sensed current exceeds a preset threshold (cycle-by-cycle limitation), in a resonant half bridge the most efficient way to reduce an excessive current level is to increase the switching frequency, i.e. the oscillator frequency.

In *Figure 18* and *19* a couple of current sensing methods are illustrated.

Note:

The L6699 must sense the instantaneous tank current for proper operation of the smooth startup function and the capacitive-mode detection circuit. Therefore, if a smoothing RC circuit (the one shown in the dashed box) is used to reduce the noise level on the ISEN pin, its time constant RF CF should be in the range of 100 - 200 ns. With slightly longer time constants it is recommended that converter operation close to the capacitive-mode boundary and during short-circuit, as well as at the end of the smooth-start phase, be checked for possible hard-switching cycles. With considerably longer time constants (> 200 ns) hard-switching under the above mentioned conditions becomes very likely.

24/38

Doc ID 022835 Rev 2

The ISEN pin, which is also able to withstand negative voltages, is internally connected to the input of a first comparator, referenced to  $V_{ISENx}$  (0.8 V typ. 0.76 V min.), and to that of a second comparator referenced to 1.5 V. The operation of the second comparator is described later.

If the voltage externally applied to the pin by either circuit in *Figure 18* and *19* exceeds 0.8 V the first comparator is tripped and this causes an internal switch to be turned on for 5  $\mu$ s and discharges the soft-start capacitor C<sub>SS</sub> (see *Section 6.3: Safe-start procedure*). This quickly increases the oscillator frequency and thereby limits energy transfer. Under output short-circuit conditions, this operation results in a peak primary current that periodically oscillates below the maximum value allowed by the sense resistor Rs.

In the circuit shown in *Figure 18*, Rs is placed directly in series to the resonant tank. Its value can be determined using the equation:

Equation 7

$$Rs = \frac{0.76}{I_{Crpkx}}$$

where  $I_{Crpkx}$  is the maximum expected peak current flowing through the resonant capacitor and the primary winding of the transformer, which is related to the maximum load and the minimum input voltage. The power dissipation in Rs can be approximately found with:

Equation 8

$$P_{Rs} \approx 0.4 \cdot I_{Crpkx}$$

The circuit shown in *Figure 19* operates as a capacitive current divider; Cs is typically selected equal to Cr/100 or less and is a low-loss type, and the sense resistor Rs is selected as:

Equation 9

$$Rs = \frac{0.77}{I_{Crpkx}} \cdot \left(1 + \frac{C_r}{Cs}\right)$$

and the associated power dissipation is reduced by a factor (1+Cr/Cs). This circuit is then recommended when the efficiency target is very high.

This OCP is effective in limiting primary-to-secondary energy flow in case of an overload or an output short-circuit, but the output current through the secondary winding and rectifiers under these conditions may be so high that it endangers converter safety if continuously flowing. To prevent any damage it is customary to force the converter to work intermittently, which brings the average output current to values such that the thermal stress for the transformer and the rectifiers can be easily handled.

If intermittent operation upon overload or short-circuit is desired, the designer can program externally the maximum time  $T_{SH}$  that the converter is allowed to run under these conditions. Overloads or short-circuits lasting less than  $T_{SH}$  do not cause any other action,

therefore providing the system with immunity to short duration phenomena. If, instead,  $T_{SH}$  is exceeded, an overload protection (OLP) procedure is activated that shuts down the L6699 and, in case of continuous overload/short-circuit, results in continuous intermittent operation with a user-defined duty cycle.

This function is realized on pin 2 (DELAY), with a capacitor  $C_{Delay}$  and a parallel resistor  $R_{Delay}$  connected to ground. As the voltage on the ISEN pin exceeds 0.8 V, the first OCP comparator, in addition to turning on the switch that discharges  $C_{SS}$ , turns on a current generator that sources 350 µA for 50 µs from the DELAY pin and charges  $C_{Delay}$ . During an overload/short-circuit the OCP comparator and the internal current source is repeatedly activated and  $C_{Delay}$  is charged with an average current depending essentially on  $C_{SS}$ ,  $R_{SS}$ , the characteristics of the resonant circuit, and the short-circuit impedance; the discharge due to  $R_{Delay}$  is negligible because the associated time constant is typically much longer.

This operation continues until the voltage on  $C_{Delay}$ , V(DELAY), reaches 2 V, which defines the time  $T_{SH}$ , or until the overload/short-circuit disappears, whichever occurs first. There is not a simple relationship that links  $T_{SH}$  to  $C_{Delay}$ , so it is more practical to determine  $C_{Delay}$ experimentally. As a rough indication, using 1 µF for  $C_{Delay}$ ,  $T_{SH}$  should be around 100 ms in case of a dead short on the output.