74ABT16374 16-Bit D-Type Flip-Flop with 3-STATE Outputs

## 74ABT16374 16-Bit D-Type Flip-Flop with 3-STATE Outputs

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

The ABT16374 contains sixteen non-inverting D-type flipflops with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. A buffered clock (CP) and Output Enable ( $\overline{OE}$ ) are common to each byte and can be shorted together for full 16-bit operation.

#### **Features**

- Separate control logic for each byte

- 16-bit version of the ABT374

- Edge-triggered D-type inputs

- Buffered Positive edge-triggered clock

- High impedance glitch free bus loading during entire power up and power down cycle

- Non-destructive hot insertion capability

- Guaranteed latch-up protection

#### **Ordering Code:**

| Order Number                                                                                          | Package Number | Package Description                                                         |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|

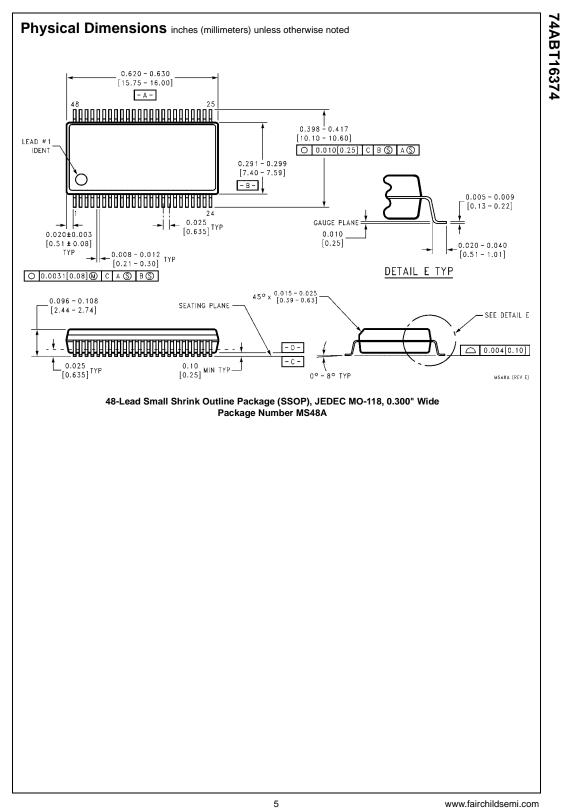

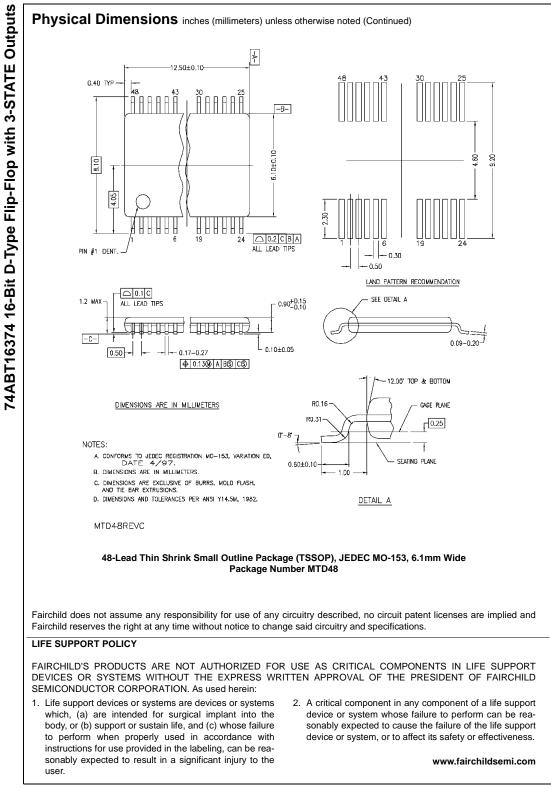

| 74ABT16374CSSC                                                                                        | MS48A          | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide      |  |  |  |  |

| 74ABT16374CMTD                                                                                        | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |  |  |  |  |

| Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code. |                |                                                                             |  |  |  |  |

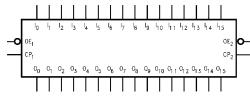

#### Logic Symbol

#### **Pin Descriptions**

| Pin Name                        | Description                              |  |  |  |  |  |

|---------------------------------|------------------------------------------|--|--|--|--|--|

| <del>OE</del> n                 | 3-STATE Output Enable Input (Active LOW) |  |  |  |  |  |

| CPn                             | Clock Pulse Input (Active Rising Edge)   |  |  |  |  |  |

| D <sub>0</sub> -D <sub>15</sub> | Data Inputs                              |  |  |  |  |  |

| O <sub>0</sub> -O <sub>15</sub> | 3-STATE Outputs                          |  |  |  |  |  |

CP. Do GND D-D-z Vcc  $D_4$ D<sub>5</sub> GND D<sub>6</sub> 37 12 07 D7 36  $0_{R}$ 3 D<sub>8</sub> 35 00 1.4 D<sub>9</sub> GND 15 34 GND 16 010 33 D<sub>10</sub> 17 32 011 D<sub>11</sub> V<sub>CC</sub> 18 3 Vcc 19 30 012 D<sub>12</sub> 0<sub>13</sub> · 20 29 D1 3 GND • 21 GND 28 014 -22 27 - D<sub>14</sub> 0<sub>15</sub> · 23 26 D<sub>15</sub>  $\overline{OE}_2$ 24 25 CP<sub>2</sub>

© 2005 Fairchild Semiconductor Corporation DS011668

#### **Functional Description**

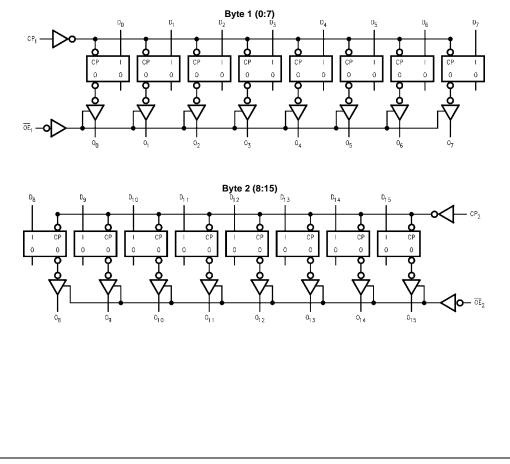

Logic Diagrams

The ABT16374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte has a buffered clock and buffered Output Enable common to all flip-flops within that byte. The description which follows applies to each byte. Each flip-flop will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP<sub>n</sub>) transition. With the Output Enable  $(\overline{OE}_n)$  LOW, the contents of the flip-flops are available at the outputs. When  $\overline{OE}_n$  is HIGH, the outputs go to the high impedance state. Operation of the OE<sub>n</sub> input does not affect the state of the flip-flops.

#### **Truth Tables**

|              | Inputs                   |                                          | Outputs                                    |

|--------------|--------------------------|------------------------------------------|--------------------------------------------|

| CP1          | OE <sub>1</sub>          | D <sub>0</sub> -D <sub>7</sub>           | 0 <sub>0</sub> –0 <sub>7</sub>             |

| ~            | L                        | Н                                        | Н                                          |

| ~            | L                        | L                                        | L                                          |

| L            | L                        | Х                                        | (Previous)                                 |

| х            | Н                        | Х                                        | Z                                          |

|              |                          |                                          |                                            |

|              | Inputs                   |                                          | Outputs                                    |

| CP2          | Inputs $\overline{OE}_2$ | D <sub>8</sub> –D <sub>15</sub>          | Outputs<br>O <sub>8</sub> –O <sub>15</sub> |

| CP2          |                          | <b>D<sub>8</sub>-D<sub>15</sub></b><br>Н |                                            |

| CP2<br>      |                          |                                          | 0 <sub>8</sub> –0 <sub>15</sub>            |

| CP2<br><br>L |                          | Н                                        | 0 <sub>8</sub> –0 <sub>15</sub>            |

H = HIGH Voltage Level

L = LOW Voltage Level X = Immaterial

Z = High Impedance

2 mgn mpodanoo

#### Absolute Maximum Ratings(Note 1)

# PS(Note 1) Recommended Operating Conditions

74ABT16374

| Storage Temperature                         | -65°C to +150°C               | Conditions                                                                           |                             |

|---------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------------------|

| Ambient Temperature under Bias              | -55°C to +125°C               | Free Air Ambient Temperature                                                         | -40°C to +85°C              |

| Junction Temperature under Bias             | -55°C to +150°C               | Supply Voltage                                                                       | +4.5V to +5.5V              |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                | Minimum Input Edge Rate (ΔV/Δt)                                                      |                             |

| Input Voltage (Note 2)                      | -0.5V to +7.0V                | Data Input                                                                           | 50 mV/ns                    |

| Input Current (Note 2)                      | -30 mA to +5.0 mA             | Enable Input                                                                         | 20 mV/ns                    |

| Voltage Applied to Any Output               |                               | Clock Input                                                                          | 100mV/ns                    |

| in the Disabled or                          |                               |                                                                                      |                             |

| Power-Off State                             | -0.5V to 5.5V                 |                                                                                      |                             |

| in the HIGH State                           | –0.5V to $V_{CC}$             |                                                                                      |                             |

| Current Applied to Output                   |                               |                                                                                      |                             |

| in LOW State (Max)                          | twice the rated $I_{OL}$ (mA) |                                                                                      |                             |

| DC Latchup Source Current:                  |                               |                                                                                      |                             |

| OE Pin                                      | –350 mA                       |                                                                                      |                             |

| (Across Comm Operating Range)               |                               | Note 1: Absolute maximum ratings are value                                           |                             |

| Other Pins                                  | –500 mA                       | may be damaged or have its useful life imp<br>under these conditions is not implied. | aired. Functional operation |

| Over Voltage Latchup (I/O)                  | 10V                           | Note 2: Either voltage limit or current limit is su                                  | fficient to protect inputs. |

## DC Electrical Characteristics

| Symbol           | Param                             | neter           | Min  | Тур | Max  | Units | V <sub>cc</sub> | Conditions                                               |

|------------------|-----------------------------------|-----------------|------|-----|------|-------|-----------------|----------------------------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage                |                 | 2.0  |     |      | V     |                 | Recognized HIGH Signal                                   |

| V <sub>IL</sub>  | Input LOW Voltage                 |                 |      |     | 0.8  | V     |                 | Recognized LOW Signal                                    |

| V <sub>CD</sub>  | Input Clamp Diode Vo              | oltage          |      |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA                                 |

| V <sub>OH</sub>  | Output HIGH Voltage               |                 | 2.5  |     |      | V     | Min             | I <sub>OH</sub> = -3 mA                                  |

|                  |                                   |                 | 2.0  |     |      | V     | Min             | I <sub>OH</sub> = -32 mA                                 |

| V <sub>OL</sub>  | Output LOW Voltage                |                 |      |     | 0.55 | V     | Min             | I <sub>OL</sub> = 64 mA                                  |

| I <sub>IH</sub>  | Input HIGH Current                |                 |      |     | 1    | μA    | Max             | V <sub>IN</sub> = 2.7V (Note 3)                          |

|                  |                                   |                 |      |     | 1    | μΛ    | IVIAA           | $V_{IN} = V_{CC}$                                        |

| I <sub>BVI</sub> | Input HIGH Current B              | Breakdown Test  |      |     | 7    | μA    | Max             | V <sub>IN</sub> = 7.0V                                   |

| IIL              | Input LOW Current                 |                 |      |     | -1   | μA    | Max             | V <sub>IN</sub> = 0.5V (Note 3)                          |

|                  |                                   |                 |      |     | -1   | μΛ    | IVIAA           | $V_{IN} = 0.0V$                                          |

| V <sub>ID</sub>  | Input Leakage Test                |                 | 4.75 |     |      | V     | 0.0             | I <sub>ID</sub> = 1.9 μA                                 |

|                  |                                   |                 |      |     |      |       |                 | All Other Pins Grounded                                  |

| I <sub>OZH</sub> | Output Leakage Curr               | ent             |      |     | 10   | μΑ    | 0-5.5V          | $V_{OUT} = 2.7V; \overline{OE} = 2.0V$                   |

| I <sub>OZL</sub> | Output Leakage Curr               | ent             |      |     | -10  | μΑ    | 0-5.5V          | $V_{OUT} = 0.5V; \overline{OE} = 2.0V$                   |

| I <sub>OS</sub>  | Output Short-Circuit (            | Current         | -100 |     | -275 | mA    | Max             | $V_{OUT} = 0.0V$                                         |

| I <sub>CEX</sub> | Output HIGH Leakage               | e Current       |      |     | 50   | μA    | Max             | V <sub>OUT</sub> = V <sub>CC</sub>                       |

| I <sub>ZZ</sub>  | Bus Drainage Test                 |                 |      |     | 100  | μA    | 0.0             | $V_{OUT} = 5.5V$ ; All Others $V_{CC}$ or GND            |

| I <sub>CCH</sub> | Power Supply Curren               | t               |      |     | 2.0  | mA    | Max             | All Outputs HIGH                                         |

| I <sub>CCL</sub> | Power Supply Curren               | ıt              |      |     | 62   | mA    | Max             | All Outputs LOW                                          |

| I <sub>CCZ</sub> | Power Supply Curren               | ıt              |      |     | 2.0  | mA    | Max             | $\overline{OE} = V_{CC}$ ; All Others at $V_{CC}$ or GND |

| I <sub>CCT</sub> | Additional I <sub>CC</sub> /Input | Outputs Enabled |      |     | 2.5  | mA    |                 | $V_I = V_{CC} - 2.1V$                                    |

|                  |                                   | Outputs 3-STATE |      |     | 2.5  | mA    | Max             | Enable Input $V_I = V_{CC} - 2.1V$                       |

|                  |                                   | Outputs 3-STATE |      |     | 2.5  | mA    |                 | Data Input $V_I = V_{CC} - 2.1V$                         |

|                  |                                   |                 |      |     |      |       |                 | All Others at V <sub>CC</sub> or GND                     |

| ICCD             | Dynamic I <sub>CC</sub>           | No Load         |      |     |      | mA/   | May             | Outputs Open                                             |

|                  | (Note 3)                          |                 |      |     | 0.30 | MHz   | Max             | OE = GND, (Note 4)                                       |

|                  |                                   |                 |      |     |      |       |                 | One Bit Toggling, 50% Duty Cycle                         |

Note 3: Guaranteed, but not tested.

Note 4: For 8-bit toggling,  $I_{CCD} < 0.8 \mbox{ mA/MHz}.$

74ABT16374

### **AC Electrical Characteristics**

| Symbol           | Parameter               |     | $T_A = +25 ^\circ \text{C}$ $V_{CC} = +5.0 \text{V}$ $C_L = 50  \text{pF}$ |     |     | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.5V \text{ to } 5.5V$ $C_{L} = 50 \text{ pF}$ |     |

|------------------|-------------------------|-----|----------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------|-----|

|                  |                         | Min | Тур                                                                        | Max | Min | Max                                                                                                      |     |

| f <sub>MAX</sub> | Maximum Clock Frequency | 150 |                                                                            |     | 150 |                                                                                                          | MHz |

| t <sub>PLH</sub> | Propagation Delay       | 1.8 |                                                                            | 6.2 | 1.8 | 6.2                                                                                                      |     |

| t <sub>PHL</sub> | CP to On                | 1.8 |                                                                            | 5.9 | 1.8 | 5.9                                                                                                      | ns  |

| t <sub>PZH</sub> | Output Enable Time      | 1.2 |                                                                            | 5.6 | 1.2 | 5.6                                                                                                      |     |

| t <sub>PZL</sub> |                         | 1.6 |                                                                            | 5.3 | 1.6 | 5.3                                                                                                      | ns  |

| t <sub>PHZ</sub> | Output Disable Time     | 2.2 |                                                                            | 7.1 | 2.2 | 7.1                                                                                                      |     |

| t <sub>PLZ</sub> |                         | 2.2 |                                                                            | 6.6 | 2.2 | 6.6                                                                                                      | ns  |

#### **AC Operating Requirements**

| Symbol             | Parameter                   | $T_{A} = +25^{\circ}C$<br>$V_{CC} = +5.0V$<br>$C_{L} = 50 \text{ pF}$ |     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$<br>$V_{CC} = 4.5V \text{ to } 5.5V$<br>$C_L = 50 \text{ pF}$ |     | Units |

|--------------------|-----------------------------|-----------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------|-----|-------|

|                    |                             | Min                                                                   | Max | Min                                                                                                        | Max |       |

| t <sub>S</sub> (H) | Setup Time, HIGH            | 1.1                                                                   |     | 1.1                                                                                                        |     | ns    |

| t <sub>S</sub> (L) | or LOW D <sub>n</sub> to CP | 1.1                                                                   |     | 1.1                                                                                                        |     | 115   |

| t <sub>H</sub> (H) | Hold Time, HIGH             | 1.3                                                                   |     | 1.3                                                                                                        |     | ns    |

| t <sub>H</sub> (L) | or LOW D <sub>n</sub> to CP | 1.3                                                                   |     | 1.3                                                                                                        |     | 115   |

| t <sub>W</sub> (H) | Pulse Width, CP             | 3.0                                                                   |     | 3.0                                                                                                        |     |       |

| t <sub>W</sub> (L) | HIGH or LOW                 | 3.0                                                                   |     | 3.0                                                                                                        |     | ns    |

#### Capacitance

| Symbol                    | Parameter          | Тур  | Units | Conditions<br>(T <sub>A</sub> = 25°C) |

|---------------------------|--------------------|------|-------|---------------------------------------|

| C <sub>IN</sub>           | Input Capacitance  | 5.0  | pF    | $V_{CC} = 0V$                         |

| C <sub>OUT</sub> (Note 5) | Output Capacitance | 11.0 | pF    | $V_{CC} = 5.0V$                       |

Note 5:  $C_{OUT}$  is measured at frequency f = 1 MHz, per MIL-STD-883, Method 3012.