### **General Description**

The MAX9178 quad low-voltage differential signaling (LVDS) line driver with high-ESD tolerance is ideal for applications requiring high data rates and low power with reduced noise. The MAX9178 is guaranteed to transmit data at speeds up to 400Mbps (200MHz) over controlled impedance of media of approximately  $100\Omega$ . The transmission media can be printed circuit (PC) board traces, backplanes, or cables.

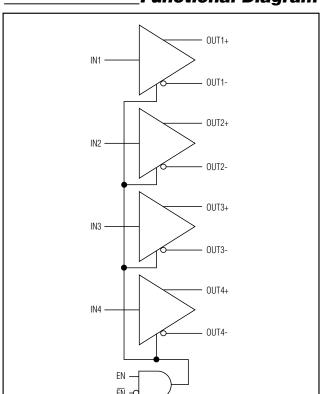

The MAX9178 accepts four LVTTL/LVCMOS inputs and translates them to LVDS output signals. All inputs tolerate overshoot of VCC +1V and undershoot of -1V. The EN and  $\overline{\rm EN}$  inputs are ANDed together and control the high-impedance outputs. When the device is disabled, power drops to ultra-low 12.6mW (typ). Outputs conform to the ANSI TIA/EIA-644 LVDS standard.

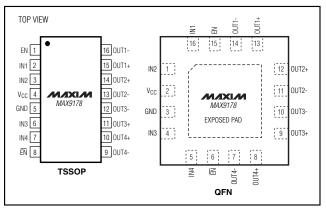

The MAX9178 operates from a single +3.3V supply, and is available in a 16-pin TSSOP and 16-pin thin QFN package with exposed pad. The MAX9178 is specified for operation from -40°C to +85°C.

### **Applications**

Digital Copiers DSLAMs

Laser Printers Network

Cell Phone Base Switches/Routers

Stations

Add/Drop Muxes

Digital Cross-Connects

Backplane

Interconnect

Clock Distribution

Functional Diagram appears at end of data sheet.

## Pin Configurations

### **Features**

- ♦ Flow-Through Pinout Simplifies PC Board Layout Reduces Crosstalk

- ♦ Pin Compatible with DS90LV047A and MAX9123

- ♦ Guaranteed 400Mbps Data Rate

- Single-Ended Inputs Tolerate 1V Overshoot/Undershoot

- ♦ 250ps Maximum Pulse Skew

- ♦ IEC 61000-4-2 Level 4 ESD Tolerance on LVDS Outputs

- ♦ Conforms to ANSI TIA/EIA-644 LVDS Standard

- ♦ Single +3.3V Supply

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX9178EUE | -40°C to +85°C | 16 TSSOP        |

| MAX9178ETE | -40°C to +85°C | 16 Thin QFN-EP* |

\*EP = Exposed pad.

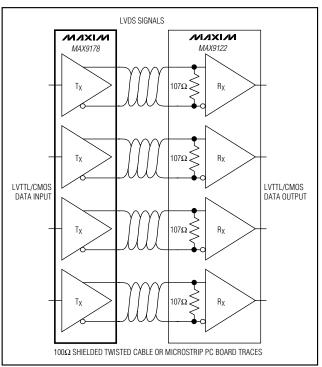

## \_Typical Application Circuit

\_\_\_\_\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

MIXIM

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                                | 0.3V to +4.0V        |

|-------------------------------------------------------|----------------------|

| IN_, EN, EN to GND1.4V                                | to $(V_{CC} + 1.4V)$ |

| OUT_ to GND                                           | 0.3V to +4.0V        |

| Short-Circuit Duration (OUT_)                         | Continuous           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                      |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°              | C)755mW              |

| 16-Pin QFN (derate 16.9mW/°C above +70°C              | )1349mW              |

| Storage Temperature Range                             |                      |

| Maximum Junction Temperature                          | +150°C               |

| ESD Protection<br>Human Body Model |        |

|------------------------------------|--------|

| All Pins to GND                    | ±2kV   |

| OUT                                | ±2kV   |

| IEC 61000-4-2 Level 4              |        |

| Contact Discharge (OUT_)           | ±8kV   |

| Air Discharge (OUT_)               |        |

| Lead Temperature (soldering, 10s)  | +300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100\Omega \pm 1\%, IN_= \text{high or low, EN} = \text{high, } \overline{\text{EN}} = \text{low, T}_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                                                        | SYMBOL           | DL CONDITIONS                                                              |       | TYP    | MAX                 | UNITS |

|----------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------|-------|--------|---------------------|-------|

| LVDS OUTPUTS (OUT_+, OUT)                                                        |                  |                                                                            |       |        |                     |       |

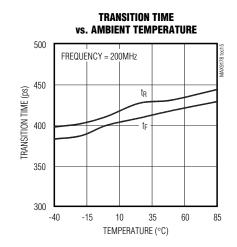

| Differential Output Voltage                                                      | V <sub>OD</sub>  | Figure 1                                                                   | 250   | 368    | 450                 | mV    |

| Change in Magnitude of V <sub>OD</sub><br>Between Complementary Output<br>States | ΔV <sub>OD</sub> | Figure 1                                                                   |       | 0.3    | 25                  | mV    |

| Offset Voltage                                                                   | Vos              | Figure 1                                                                   | 1.125 | 1.28   | 1.375               | V     |

| Change in Magnitude of VOS<br>Between Complementary Output<br>States             | ΔV <sub>OS</sub> | Figure 1                                                                   |       | 0.3    | 25                  | mV    |

| Output High Voltage                                                              | Voн              | Figure 1                                                                   |       |        | 1.6                 | V     |

| Output Low Voltage                                                               | V <sub>OL</sub>  | Figure 1                                                                   | 0.90  |        |                     | V     |

| Unterminated Output High Voltage                                                 | Vohut            | Output open, Figure 6                                                      | 1.9   |        |                     | V     |

| Unterminated Output Low<br>Voltage                                               | Volut            | Output open, Figure 6                                                      |       |        | 0.1                 | V     |

| Differential Output Short-Circuit<br>Current Magnitude                           | IOSD             | V <sub>OD</sub> = 0 (Note 3)                                               |       |        | 9                   | mA    |

| Output Short-Circuit Current                                                     | los              | OUT_+ = 0 at IN_ = high,<br>or OUT = 0 at IN_ = low                        |       |        | -9                  | mA    |

| Output High-Impedance Current                                                    | loz              | $EN = low and \overline{EN} = high,$<br>$OUT_{-} = 0 or V_{CC}, no load$   | -0.5  | ±0.002 | +0.5                | μΑ    |

| Power-Off Output Current                                                         | loff             | $V_{CC}$ , IN_, EN, $\overline{EN}$ = 0 or open, OUT_ = 0 or 3.6V, no load | -0.5  | ±0.001 | +0.5                | μΑ    |

| INPUTS (IN_, EN, EN)                                                             |                  |                                                                            |       |        |                     |       |

| High-Level Input Voltage                                                         | VIH              |                                                                            | 2.0   |        | V <sub>CC</sub> + 1 | V     |

| Low-Level Input Voltage                                                          | VIL              |                                                                            | -1.0  |        | +0.8                | V     |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, R_L = 100\Omega \pm 1\%, IN_= \text{ high or low, EN} = \text{high, } \overline{EN} = \text{low, } T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER      | SYMBOL           | CONDITIONS                                                                   | MIN  | TYP   | MAX | UNITS |

|----------------|------------------|------------------------------------------------------------------------------|------|-------|-----|-------|

|                |                  | $0 \le IN_, EN, \overline{EN} \le V_{CC}$                                    | -20  | 5     | +20 | μΑ    |

| Input Current  | I <sub>IN</sub>  | $V_{CC} \le IN_{-}$ , $EN$ , $\overline{EN} \le V_{CC} + 1$                  |      | 0.67  | 1.5 | A     |

|                |                  | $-1V \le IN_{-}$ , EN, $\overline{EN} \le 0$                                 | -1.5 | -0.46 |     | mA    |

| SUPPLY CURRENT |                  |                                                                              |      |       |     |       |

|                | Icc              | $IN_{-} = V_{CC}$ or 0, $EN = V_{CC}$ , $\overline{EN} = 0$ , no load        |      | 3.8   | 6.0 |       |

| Supply Current | ICCL             | $IN_{-} = V_{CC}$ or 0, $EN = V_{CC}$ , $\overline{EN} = 0$ , outputs loaded |      | 18    | 25  | mA    |

|                | I <sub>CCZ</sub> | $IN_{-} = V_{CC}$ or 0, $EN = 0$ , $\overline{EN} = V_{CC}$                  |      | 3.8   | 6   |       |

#### **SWITCHING CHARACTERISTICS**

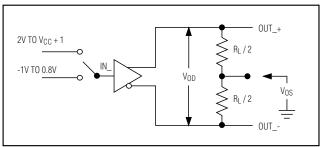

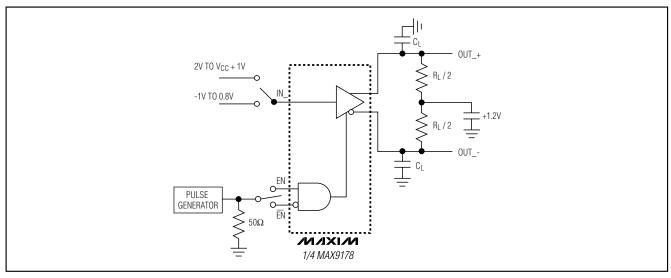

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100\Omega \pm 1\%, C_L = 15 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C},$  unless otherwise noted.) (Notes 4–7)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                       | MIN  | TYP  | MAX  | UNITS |  |

|-----------------------------------------------|-----------------|------------------------------------------------------------------|------|------|------|-------|--|

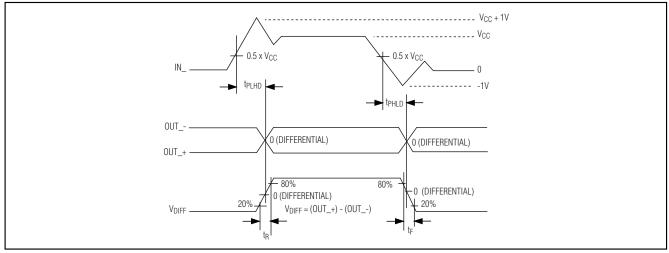

| Differential Propagation Delay<br>High to Low | tPHLD           | Figures 2, 3                                                     | 0.9  | 1.4  | 2.0  | ns    |  |

| Differential Propagation Delay<br>Low to High | tPLHD           | Figures 2, 3                                                     | 0.9  | 1.5  | 2.0  | ns    |  |

| Differential Pulse Skew                       | tskD1           | Figures 2, 3 (Note 8)                                            |      | 0.1  | 0.25 | ns    |  |

| Differential Channel-to-Channel<br>Skew       | tSKD2           | Figures 2, 3 (Note 9)                                            |      | 0.15 | 0.35 | ns    |  |

| Differential Part-to-Part Skew                | tskD3           | Figures 2, 3 (Note 10)                                           |      |      | 0.9  | no    |  |

| Dillerential Part-to-Part Skew                | tskD4           | Figures 2, 3 (Note 11)                                           |      |      | 1.1  | ns    |  |

| Rise Time                                     | t <sub>R</sub>  | Figures 2, 3                                                     | 0.20 | 0.43 | 0.70 | ns    |  |

| Fall Time                                     | tF              | Figures 2, 3                                                     | 0.20 | 0.41 | 0.70 | ns    |  |

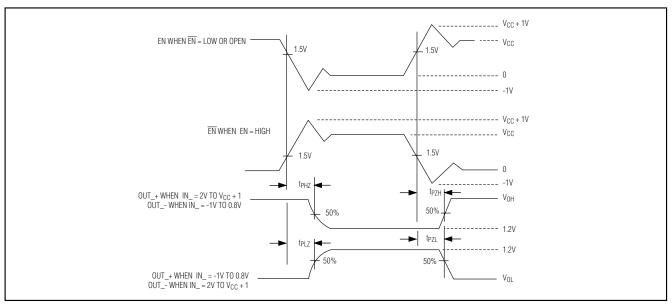

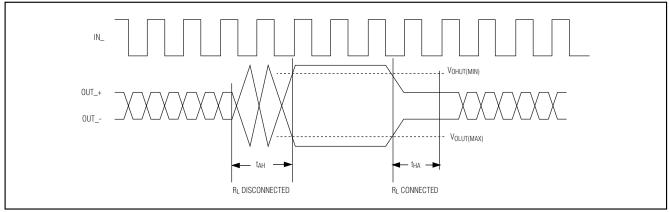

| Disable Time High to Z                        | tphz            | Figures 4, 5                                                     |      | 3.9  | 5    | ns    |  |

| Disable Time Low to Z                         | tpLZ            | Figures 4, 5                                                     |      | 3.9  | 5    | ns    |  |

| Enable Time Z to High                         | tpzh            | Figures 4, 5                                                     |      | 5.0  | 7    | ns    |  |

| Enable Time Z to Low                          | tpzL            | Figures 4, 5                                                     |      | 5.0  | 7    | ns    |  |

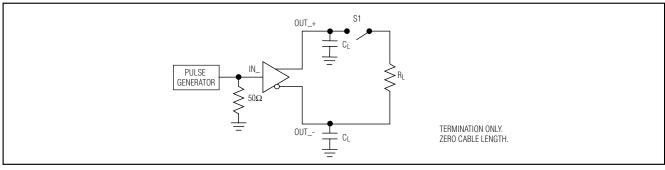

| Active to High Time                           | t <sub>AH</sub> | $R_L = 80\Omega$ to $132\Omega \pm 1\%$ ; Figures 6, 7           |      | 50   | 100  | ns    |  |

| High to Active Time                           | tha             | $R_L = 80\Omega$ to $132\Omega \pm 1\%$ ; Figures 6, 7 (Note 12) |      | 1.0  | 1.5  | μs    |  |

| Maximum Operating Frequency                   | fMAX            | (Note 13)                                                        | 200  |      |      | MHz   |  |

- **Note 1:** Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are 100% tested at TA = +85°C.

- Note 2: Currents into the device are positive, and current out of the device is negative. All voltages are referenced to ground except Vop, ΔVop, Vos, and ΔVos.

- Note 3: Guaranteed by design.

- Note 4: AC parameters are guaranteed by design and characterization. Limits are set at ±6 sigma.

- Note 5: CL includes probe and jig capacitance.

- **Note 6:** Pulse generator output for AC tests:  $t_R = t_F = 1$ ns (0.2 x V<sub>CC</sub> to 0.8 x V<sub>CC</sub>), 50% duty cycle,  $R_O = 50\Omega$ , V<sub>OH</sub> = V<sub>CC</sub> + 1V settling to V<sub>CC</sub>, V<sub>OL</sub> = -1V settling to zero, frequency = 200MHz.

### **SWITCHING CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, R_L = 100\Omega \pm 1\%, C_L = 15 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}) (Notes 4–7)$

- Note 7: Pulse generator output for tpHz, tpLz, tpZH, tpZL, tAH, and tHA tests:  $t_R = t_F = 1$ ns (0.2 x V<sub>CC</sub> to 0.8 x V<sub>CC</sub>), 50% duty cycle,  $t_{CC} = 1$ 00kHz.

- Note 8: tskp1 is the magnitude of the difference of differential propagation delay. tskp1 = ltpHLD tpLHpl.

- Note 9: tskp2 is the magnitude difference of tphlp or tplhp of one channel to the tphlp or tplhp of another channel on the same device.

- **Note 10:** tskp3 is the magnitude of the difference of any differential propagation delays between devices at the same Vcc and within 5°C of each other.

- Note 11: t<sub>SKD4</sub> is the magnitude of the difference of any differential propagation delays between devices operating over the rated supply and temperature ranges.

- Note 12: After t<sub>HA</sub> time, all switching characteristics specifications are met.

- **Note 13:** Meets all AC parameters at  $f_{MAX} = 200MHz$  with  $|V_{OD}| \ge 250mV$ .

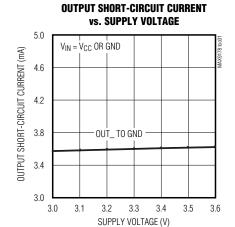

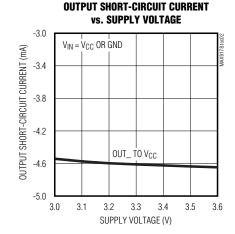

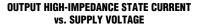

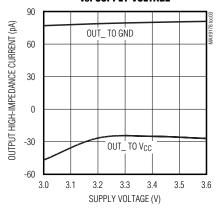

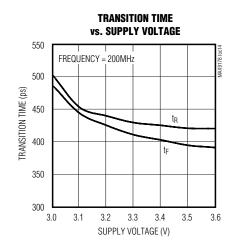

### Typical Operating Characteristics

$(V_{CC} = +3.3V, R_{I} = 100\Omega, C_{I} = 15pF, T_{A} = +25^{\circ}C, \text{ unless otherwise noted.})$

## DIFFERENTIAL OUTPUT VOLTAGE vs. Supply voltage

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, R_L = 100\Omega, C_L = 15pF, T_A = +25^{\circ}C, unless otherwise noted.)$

## \_Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, R_L = 100\Omega, C_L = 15pF, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Pin Description**

| Р     | IN  | NAME        | FUNCTION                                                                                                                   |  |  |  |  |

|-------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TSSOP | QFN | NAME        | FUNCTION                                                                                                                   |  |  |  |  |

| 1     | 15  | EN          | LVTTL/LVCMOS Enable Input. All outputs are disabled when EN is low. Internally pulled down.                                |  |  |  |  |

| 2     | 16  | IN1         | LVTTL/LVCMOS Input 1. Input internally pulled down.                                                                        |  |  |  |  |

| 3     | 1   | IN2         | LVTTL/LVCMOS Input 2. Input internally pulled down.                                                                        |  |  |  |  |

| 4     | 2   | Vcc         | Power-Supply. Bypass V <sub>CC</sub> to GND with 0.1µF and 0.001µF ceramic capacitors.                                     |  |  |  |  |

| 5     | 3   | GND         | Ground                                                                                                                     |  |  |  |  |

| 6     | 4   | IN3         | LVTTL/LVCMOS Input 3. Input internally pulled down.                                                                        |  |  |  |  |

| 7     | 5   | IN4         | LVTTL/LVCMOS input 4. Input internally pulled down.                                                                        |  |  |  |  |

| 8     | 6   | ĒN          | LVTTL/LVCMOS Inverting Enable Input. All outputs are disabled when $\overline{\text{EN}}$ is high. Internally pulled down. |  |  |  |  |

| 9     | 7   | OUT4-       | Inverting LVDS Output 4                                                                                                    |  |  |  |  |

| 10    | 8   | OUT4+       | Noninverting LVDS Output 4                                                                                                 |  |  |  |  |

| 11    | 9   | OUT3+       | Noninverting LVDS Output 3                                                                                                 |  |  |  |  |

| 12    | 10  | OUT3-       | Inverting LVDS Output 3                                                                                                    |  |  |  |  |

| 13    | 11  | OUT2-       | Inverting LVDS Output 2                                                                                                    |  |  |  |  |

| 14    | 12  | OUT2+       | Noninverting LVDS Output 2                                                                                                 |  |  |  |  |

| 15    | 13  | OUT1+       | Noninverting LVDS Output 1                                                                                                 |  |  |  |  |

| 16    | 14  | OUT1-       | Inverting LVDS Output 1                                                                                                    |  |  |  |  |

|       | EP  | Exposed Pad | Exposed Pad. Solder to ground plane.                                                                                       |  |  |  |  |

5 \_\_\_\_\_\_ NIXIN

### **Test Circuits/Timing Diagrams**

Figure 1. Driver V<sub>OD</sub> and V<sub>OS</sub> Test Circuit

Figure 2. Transition Time and Propagation Delay Test Circuit

Figure 3. Transition Time and Propagation Delay Waveform Timing

Figure 4. High-Impedance Delay Test Circuit

## Test Circuits/Timing Diagrams (continued)

Figure 5. High-Impedance Delay Waveform Timing

Figure 6. Active-to-High and High-to-Active Test Circuit

Figure 7. Active-to-High and High-to-Active Timing Diagram

3 \_\_\_\_\_\_**/\/**/**X**|*/*/

### **Detailed Description**

The LVDS interface standard is a signaling method intended for point-to-point communication over a controlled-impedance medium as defined by the ANSI/TIA/EIA-644 and IEEE 1596.3 standards. The LVDS standard uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption, while reducing EMI emissions and system susceptibility to noise.

The MAX9178 is a 400Mbps quad differential LVDS driver that is designed for high-speed, point-to-point, and low-power applications. This device accepts LVTTL/LVCMOS input levels and translates them to LVDS output signals.

The MAX9178 generates a 2.5mA to 4.5mA output current using a current-steering configuration. This current-steering approach induces less ground bounce and no shoot-through current, enhancing noise margin and system speed performance. The driver outputs are short-circuit current limited, and enter a high-impedance state when the device is not powered or is disabled.

The current-steering architecture of the MAX9178 requires a resistive load to terminate the signal and complete the transmission loop. Because the device switches current and not voltage, the actual output voltage swing is determined by the value of the termination resistor at the input of an LVDS receiver. Logic states are determined by the direction of current flow through the termination resistor. With a typical 3.7mA output current, the MAX9178 produces an output voltage of 370mV when driving a  $100\Omega$  load.

#### **Termination**

The termination resistors should match the differential impedance of the transmission line. Output voltage levels depend upon the value of the termination resistor. The MAX9178 is optimized for point-to-point interface with 100 $\Omega$  termination resistors at the receiver inputs. Termination resistance values may range between  $90\Omega$  and  $132\Omega$ , depending on the characteristic impedance of the transmission medium. Table 1 lists the I/O functions.

#### **Termination Detection**

The MAX9178 has a limited-capability termination detection circuit at each output that drives the output high when the output termination is removed (or is not present at power-up), and starts the output switching when a termination is connected. These circuits prevent EMI and crosstalk that occur (due to reflections) if an unterminated line is driven.

**Table 1. Input/Output Function Table**

| ENABLES                                 |      | OUTPUT    | INPUTS | OUTPUTS |     |  |

|-----------------------------------------|------|-----------|--------|---------|-----|--|

| EN                                      | EN   | LOAD      | IN_    | OUT_+   | OUT |  |

|                                         | L or | Connected | L      | L       | Η   |  |

| Н                                       | open | Connected | Н      | Η       | L   |  |

| All other combinations of enable inputs |      | X         | Х      | Z       | Z   |  |

Z = High impedance.

**Table 2. Cable Lengths and Frequencies**

| CONDITIONS                                   | CABLE<br>LENGTH (m) | TYPICAL<br>SWITCHING<br>FREQUENCY<br>(MHz) |  |  |

|----------------------------------------------|---------------------|--------------------------------------------|--|--|

| 100 $\Omega$ cable termination,              | 1                   | 10.75                                      |  |  |

| 5pF load (each output to ground), 10% to 90% | 2                   | 8.5                                        |  |  |

| duty cycle                                   | 4                   | 7.8                                        |  |  |

Bench testing with CAT-5E unshielded twisted-pair cable showed the termination detection working for the cable lengths and frequencies listed in Table 2. Other combinations of cable length and frequency are possible.

The termination detection worked with 30m of CAT-5 at 3MHz and with alternating 3MHz and 9MHz. The termination detection is prevented from working at various cable lengths, switching frequencies, and data patterns by reflections that discharge the detection circuit.

## **Applications Information**

#### **Power-Supply Bypassing**

Bypass VCC with high-frequency, surface-mount ceramic  $0.1\mu F$  and  $0.001\mu F$  capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to VCC.

#### **Differential Traces**

Output trace characteristics affect the performance of the MAX9178. Use controlled-impedance traces to match trace impedance to the transmission medium. Eliminate reflections and ensure that noise couples as common mode by running the differential trace pairs close together. Reduce skew by matching the electrical length of the traces. Excessive skew can result in a degradation of magnetic field cancellation.

X = Don't care.

Maintain the distance between the differential traces to avoid discontinuities in differential impedance. Minimize the number of vias to further prevent impedance discontinuities.

#### **Cables and Connectors**

Transmission media should have a nominal differential impedance of  $100\Omega$ . To minimize impedance discontinuities, use cables and connectors that have matched differential impedance.

Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to canceling effects. Balanced cables tend to pick up noise as common mode, which is rejected by the LVDS receiver.

#### Overshoot and Undershoot Voltage Protection

The MAX9178 is designed to protect the inputs (IN\_, EN, and EN) against latchup due to transient overshoot and undershoot voltage. If the input voltage goes above VCC or below GND by up to 1V, an internal circuit limits input current to 1.5mA.

#### IEC 61000-4-2 Level 4 ESD Protection

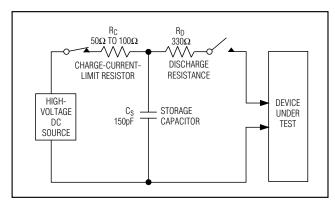

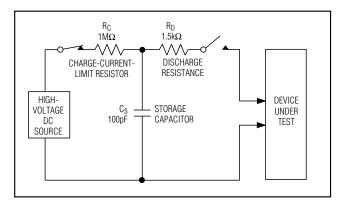

The IEC 61000-4-2 standard specifies ESD tolerance for electronic systems. The IEC 61000-4-2 model (Figure 8) specifies a 150pF capacitor that is discharged into the device through a 330 $\Omega$  resistor. The MAX9178 outputs are rated for IEC 61000-4-2 level 4 (±8kV Contact Discharge and ±15kV Air Discharge). The Human Body Model (HBM, Figure 9) specifies a 100pF capacitor that is discharged into the device through a 1.5k $\Omega$  resistor.

The IEC 61000-4-2 circuit discharges higher peak current and more energy than the HBM circuit due to the lower series resistance and larger capacitor.

#### **Board Layout**

A four-layer PC board that provides separate power, ground, LVDS signals, and input signals is recommended. Separate the LVTTL/LVCMOS and LVDS signals to prevent coupling.

Figure 8. IEC 61000-4-2 Contact Discharge ESD Test Model

Figure 9. Human Body ESD Test Model

## **Functional Diagram**

## \_Chip Information

TRANSISTOR COUNT: 1089

PROCESS: CMOS

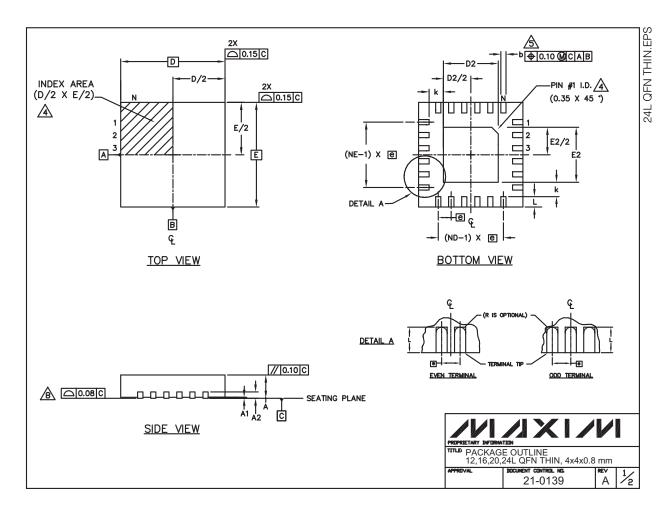

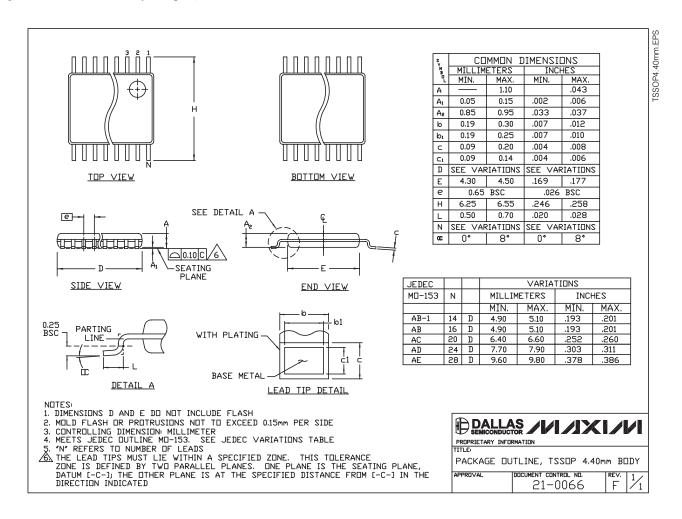

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|               | COMMON DIMENSIONS |          |            |         |          |                  |          |       |           |          |       |      |

|---------------|-------------------|----------|------------|---------|----------|------------------|----------|-------|-----------|----------|-------|------|

| PKG           | 12L 4×4           |          |            | 16L 4×4 |          | 20L 4×4          |          |       | 24L 4×4   |          |       |      |

| REF.          | MIN.              | NDM.     | MAX.       | MIN.    | NOM.     | MAX.             | MIN.     | NDM.  | MAX.      | MIN.     | NDM.  | MAX. |

| Α             | 0.70              | 0.75     | 0.80       | 0.70    | 0.75     | 0.80             | 0.70     | 0.75  | 0.80      | 0.70     | 0.75  | 0.80 |

| A1            | 0.0               | 0.02     | 0.05       | 0.0     | 0.02     | 0.05             | 0.0      | 0.02  | 0.05      | 0.0      | 0.02  | 0.05 |

| A2            |                   | 0.20 REF |            |         | 0.20 REF |                  | 0.20 REF |       |           | 0.20 REF |       |      |

| lo            | 0.25              | 0.30     | 0.35       | 0.25    | 0.30     | 0.35             | 0.20     | 0.25  | 0.30      | 0.18     | 0.23  | 0.30 |

| D             | 3.90              | 4.00     | 4.10       | 3.90    | 4.00     | 4.10             | 3.90     | 4.00  | 4.10      | 3.90     | 4.00  | 4.10 |

| Ε             | 3.90              | 4.00     | 4.10       | 3.90    | 4.00     | 4.10             | 3.90     | 4.00  | 4.10      | 3.90     | 4.00  | 4.10 |

| e             |                   | 0.80 BS0 | <b>)</b> . |         | 0.65 BSC | 5 BSC. 0.50 BSC. |          |       | 0.50 BSC. |          |       |      |

| k             | 0.25              | -        | -          | 0.25    | -        | -                | 0.25     | ı     | -         | 0.25     | -     | •    |

| L             | 0.45              | 0.55     | 0.65       | 0.45    | 0.55     | 0.65             | 0.45     | 0.55  | 0.65      | 0.30     | 0.40  | 0.50 |

| N             |                   | 12       |            |         | 16       |                  | 20       |       | 24        |          |       |      |

| ND            |                   | 3        |            | 4       |          | 5                |          |       | 6         |          |       |      |

| NE            |                   | 3        |            | 4       |          | 5                |          | 6     |           |          |       |      |

| Jedec<br>Var. |                   | WGGB     |            |         | WGGC     |                  |          | WGGD- | 1         |          | WGGD- | 2    |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |

|------------------------|------|------|------|------|------|------|

| PKG.                   |      | D2   |      |      | E2   |      |

| CODES                  | MIN. | NDM. | MAX. | MIN. | NOM. | MAX. |

| T1244-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T1644-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2044-1                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

| T2444-1                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- 6 ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220.

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.