##

## 16:1 Serializer, 3.3V, 2.5Gbps, SDH/SONET, with Clock Synthesis and LVPECL Inputs

### **General Description**

The MAX3891 serializer converts 16-bit wide, 155Mbps parallel data to 2.5Gbps serial data in ATM and SDH/SONET applications. The MAX3891 is ideal for interfacing with high-speed digital circuitry. This device accepts single-ended LVPECL data inputs and delivers differential LVPECL data and clock outputs. An internal 2.5Gbps serial clock, synthesized by a fully integrated PLL that accepts multiple input reference clock rates, retimes the output data stream. The MAX3891 operates from a single +3.3V supply and accepts differential LVPECL reference clock rates of 155.52MHz, 77.76MHz, 51.84MHz, or 38.88MHz. A CML loopback data output is provided to facilitate system diagnostic testing. The MAX3891 is available in the extended temperature range (-40°C to +85°C) in a 64-pin TQFP exposed pad (EP) package.

### **Applications**

2.5Gbps SDH/SONET Transmission Systems 2.5Gbps Access Nodes Add/Drop Multiplexers Digital Cross-Connects ATM Backplanes

#### Features

- ♦ Single +3.3V Supply

- **♦ 495mW Power Consumption**

- ♦ Exceeds ANSI, ITU, and Bellcore Specifications

- ♦ 155Mbps (16-bit wide) Parallel to 2.5Gbps Serial Conversion

- ♦ Clock Synthesis for 2.5Gbps

- ♦ Multiple Clock Reference Frequencies (155.52MHz, 77.76MHz, 51.84MHz, 38.88MHz)

- ♦ Additional High-Speed Output for System **Loopback Testing**

- ♦ Single-Ended PECL Data Inputs

- ♦ Differential PECL Clock Inputs and Serial Data **Outputs**

### **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |  |  |

|------------|----------------|-------------|--|--|

| MAX3891ECB | -40°C to +85°C | 64 TQFP EP* |  |  |

<sup>\*</sup>EP = Exposed Pad

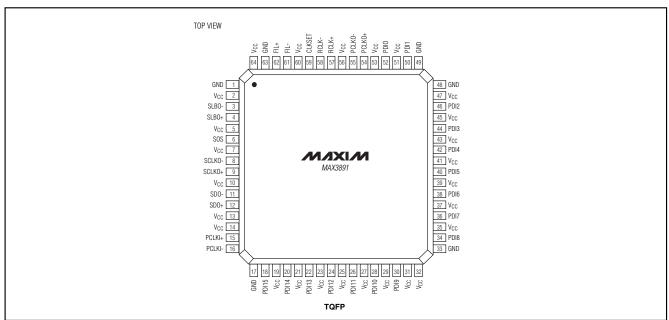

## Pin Configuration

Typical Application Circuit appears at end of data sheet.

MIXIM

Maxim Integrated Products 1

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| Terminal Voltage (with respect to GND)                             | Continuous Power Dissipation (T <sub>A</sub> = +85°C) |

|--------------------------------------------------------------------|-------------------------------------------------------|

| VCC0.5V to +5.0V                                                   | 64-Pin TQFP-EP (derate 45.5mW/°C above +85°C)2.9W     |

| All Inputs, FIL+, FIL0.5V to (V <sub>CC</sub> + 0.5V)              | Operating Temperature Range40°C to +85°C              |

| Output Currents                                                    | Storage Temperature Range60°C to +150°C               |

| PECL Outputs (SDO±, SCLKO±, PCLKO±)50mA<br>CML Outputs (SLBO±)15mA | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{PECL loads} = 50\Omega \pm 1\% \text{ to } (V_{CC} - 2 \text{V}), \text{CML loads} = 50\Omega \pm 1\% \text{ to } V_{CC}, \text{TA} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3 \text{V} \text{ and } T_{A} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                | SYMBOL           | CONDITIONS                           | MIN                        | TYP | MAX                         | UNITS |

|------------------------------------------|------------------|--------------------------------------|----------------------------|-----|-----------------------------|-------|

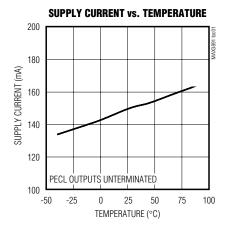

| Supply Current                           | Icc              | PECL outputs unterminated, SOS = iow |                            | 150 | 230                         | mA    |

| PECL OUTPUTS (SDO±, SCLKO                | ±, PCLKO±)       |                                      |                            |     |                             |       |

| Output Voltage High                      | V <sub>OH</sub>  | $T_A = 0$ °C to +85°C                | V <sub>CC</sub><br>- 1.025 |     | V <sub>C</sub> C<br>- 0.88  | V     |

|                                          |                  | T <sub>A</sub> = -40°C               | V <sub>CC</sub><br>- 1.085 |     | V <sub>C</sub> C<br>- 0.88  |       |

| Output Voltage Low                       | V <sub>OL</sub>  | $T_A = 0$ °C to +85°C                | V <sub>CC</sub> - 1.81     |     | V <sub>CC</sub><br>- 1.62   | V     |

|                                          |                  | T <sub>A</sub> = -40°C               | V <sub>CC</sub> - 1.83     |     | V <sub>C</sub> C<br>- 1.555 | V     |

| PECL INPUTS (PDI_, PCLKI±, RC            | LK±)             |                                      |                            |     |                             |       |

| Input High Voltage                       | VIH              |                                      | V <sub>CC</sub> - 1.16     |     | V <sub>CC</sub><br>- 0.88   | V     |

| Input Low Voltage                        | VIL              |                                      | V <sub>CC</sub> - 1.81     |     | V <sub>CC</sub><br>- 1.48   | V     |

| Input Current High PDI_, RCLKI±          | lін              |                                      | -10                        |     | +10                         | μΑ    |

| Input Current Low PDI_, RCLKI±           | IIL              |                                      | -10                        |     | +10                         | μΑ    |

| Input Current High PCLKI±                | lін              |                                      | -60                        |     | +60                         | μΑ    |

| Input Current Low PCLKI±                 | Ι <sub>Ι</sub> L |                                      | -60                        |     | +60                         | μΑ    |

| PROGRAMMING INPUT (CLKSE                 | Τ)               |                                      |                            |     |                             |       |

| CLKSET Input Current                     | ICLKSET          | CLKSET = GND or V <sub>CC</sub>      |                            |     | ±500                        | μΑ    |

| TTL INPUT (SOS)                          |                  |                                      |                            |     |                             |       |

| TTL Input High Voltage                   | VIH              |                                      | 2.0                        |     |                             | V     |

| TTL Input Low Voltage                    | VIL              |                                      |                            |     | 8.0                         | V     |

| TTL Input High Current                   | lін              |                                      | -10                        |     | +10                         | μΑ    |

| TTL Input Low Current                    | I <sub>IL</sub>  |                                      | -10                        |     | +10                         | μΑ    |

| CURRENT MODE LOGIC (CML)                 | OUTPUTS (        | SLBO±)                               |                            |     |                             |       |

| CML Differential Output Voltage<br>Swing | V <sub>OD</sub>  | $R_L = 50 \Omega$ to $V_{CC}$        | 100                        |     | 400                         | mV    |

| CML Single-Ended Output<br>Impedance     | Ro               |                                      |                            | 50  |                             | Ω     |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{PECL loads} = 50\Omega \pm 1\% \text{ to } (V_{CC} - 2 \text{V}), \text{CML loads} = 50\Omega \pm 1\% \text{ to } V_{CC}, \text{T}_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values}$  are at T<sub>A</sub> = +25  $^{\circ}$ C and V<sub>CC</sub> = +3.3 V, unless otherwise noted.) (Note 1)

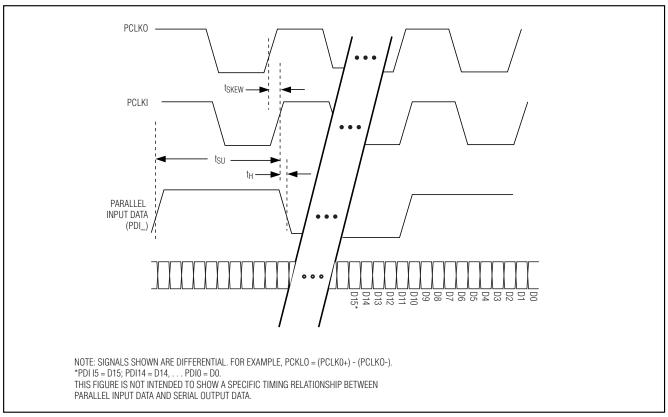

| PARAMETER                                                             | SYMBOL                          | CONDITIONS                        | MIN | TYP    | MAX  | UNITS |

|-----------------------------------------------------------------------|---------------------------------|-----------------------------------|-----|--------|------|-------|

| Serial Clock Rate                                                     | fsclk                           |                                   |     | 2.488  |      | GHz   |

| Parallel Data Setup Time                                              | tsu                             | (Notes 2, 3)                      | 300 |        |      | ps    |

| Parallel Data-Hold Time                                               | tH                              | (Notes 2, 3)                      | 700 |        |      | ps    |

| PCLKO to PCLKI Skew                                                   | tskew                           | Figure 1                          | 0   |        | +4.0 | ns    |

| Output Jitter Generation (SCLKO±)                                     |                                 | Jitter bandwidth = 12kHz to 20MHz |     |        | 3    | psRMS |

| PECL Differential Output (SDO±, SCLKO±) Rise/Fall Time                | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%                        |     |        | 120  | ps    |

| Parallel Input Clock Rate                                             | fPCLKI                          |                                   |     | 155.52 |      | MHz   |

| Reference Clock Input (RCLK±)<br>Rise/Fall Time                       | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%, f = 155.52MHz         |     |        | 1.0  | ns    |

| Parallel Clock Output (PCLKO±)<br>Rise/Fall Time                      | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%                        |     |        | 1.0  | ns    |

| Serial-Clock Output (SCLKO±)<br>to Serial-Data Output (SDO±)<br>Delay | tsclk-sd                        | SCLKO rising edge to SDO edge     | 110 |        | 290  | ps    |

- **Note 1:** AC characteristics are guaranteed by design and characterization.

- Note 2: Setup and hold times are relative to the rising edge of PCLKI+, measured by applying a 155.52MHz differential parallel clock with rise/fall time = 1ns (20% to 80%). See Figure 1.

- **Note 3:** Setup and hold time measurements assume that the PCLKI and PDI signals are from the same source and have identical common-mode voltages, swings, and slew rates.

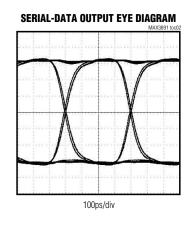

## Typical Operating Characteristics

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

TOTAL WIDEBAND RMS JITTER = 2.059ps, PEAK-TO-PEAK JITTER = 16.70ps

## **Pin Description**

| PIN                                                                                                                      | NAME             | FUNCTION                                                                                                                                                                                                                                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 17, 33, 48,<br>49, 63                                                                                                 | GND              | Ground                                                                                                                                                                                                                                               |  |  |

| 2, 5, 7, 10,<br>13, 14, 19,<br>21, 23, 25,<br>27, 29, 31,<br>32, 35, 37,<br>39, 41, 43,<br>45, 47, 51,<br>53, 56, 60, 64 | Vcc              | +3.3V Supply Voltage                                                                                                                                                                                                                                 |  |  |

| 3                                                                                                                        | SLBO-            | System Loopback Negative Output. Enabled when SOS is high.                                                                                                                                                                                           |  |  |

| 4                                                                                                                        | SLBO+            | System Loopback Positive Output. Enabled when SOS is high.                                                                                                                                                                                           |  |  |

| 6                                                                                                                        | SOS              | System Loopback Output Select, TTL Input. System loopback disabled when low.                                                                                                                                                                         |  |  |

| 8                                                                                                                        | SCLKO-           | Negative PECL Serial Clock Output                                                                                                                                                                                                                    |  |  |

| 9                                                                                                                        | SCLKO+           | Positive PECL Serial Clock Output                                                                                                                                                                                                                    |  |  |

| 11                                                                                                                       | SDO-             | Negative PECL Serial Data Output                                                                                                                                                                                                                     |  |  |

| 12                                                                                                                       | SDO+             | Positive PECL Serial Data Output                                                                                                                                                                                                                     |  |  |

| 15                                                                                                                       | PCLKI+           | Positive PECL Parallel Clock Input. Connect the incoming parallel-clock signal to the PCLKI inputs.  Note that data is updated on the positive transition of the PCLKI signal.                                                                       |  |  |

| 16                                                                                                                       | PCLKI-           | Negative PECL Parallel Clock Input. Connect the incoming parallel-clock signal to the PCLKI inputs.  Note that data is updated on the positive transition of the PCLKI signal.                                                                       |  |  |

| 18, 20, 22,<br>24, 26, 28,<br>30, 34, 36,<br>38, 40, 42,<br>44, 46, 50, 52                                               | PDI15 to<br>PDI0 | Single-Ended PECL Parallel Data Inputs. Data is clocked on the PCLKI positive transition. PDI15 is transmitted first.                                                                                                                                |  |  |

| 54                                                                                                                       | PCLKO+           | Positive PECL Parallel Clock Output. Use positive transition of PCLKO to clock the overhead management circuit.                                                                                                                                      |  |  |

| 55                                                                                                                       | PCLKO-           | Negative PECL Parallel Clock Output. Use positive transition of PCLKO to clock the overhead management circuit.                                                                                                                                      |  |  |

| 57                                                                                                                       | RCLK+            | Positive Reference Clock Input. Connect a PECL-compatible crystal reference clock to the RCLK inputs.                                                                                                                                                |  |  |

| 58                                                                                                                       | RCLK-            | Negative Reference Clock Input. Connect a PECL-compatible crystal reference clock to the RCLK inputs.                                                                                                                                                |  |  |

| 59                                                                                                                       | CLKSET           | Reference Clock Rate Programming Pin: CLKSET = V <sub>CC</sub> : Reference Clock Rate = 155.52MHz CLKSET = Open: Reference Clock Rate = 77.76MHz CLKSET = 20kΩ to GND: Reference Clock Rate = 51.84MHz CLKSET = GND: Reference Clock Rate = 38.88MHz |  |  |

| 61                                                                                                                       | FIL-             | Filter Capacitor Input. Connect a 0.33μF capacitor between FIL+ and FIL-                                                                                                                                                                             |  |  |

| 62                                                                                                                       | FIL+             | Filter Capacitor Input. Connect a 0.33μF capacitor between FIL+ and FIL-                                                                                                                                                                             |  |  |

| EP                                                                                                                       | Exposed<br>Pad   | Ground. This must be soldered to a circuit board for proper electrical and thermal performance (see exposed pad package information).                                                                                                                |  |  |

Figure 1. Timing Diagram

### Detailed Description

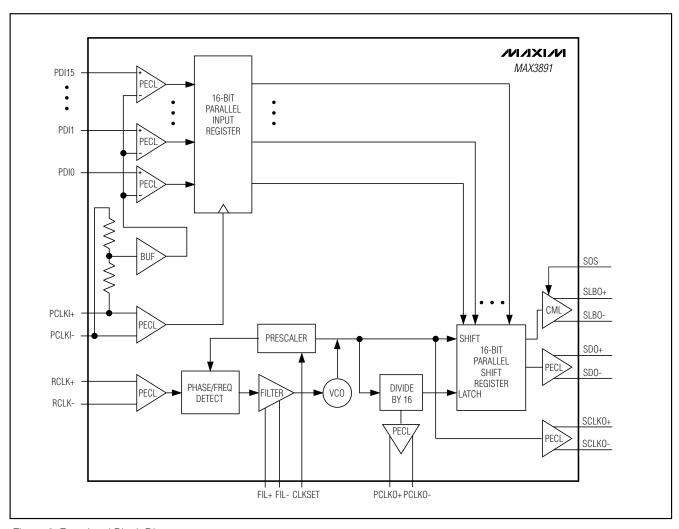

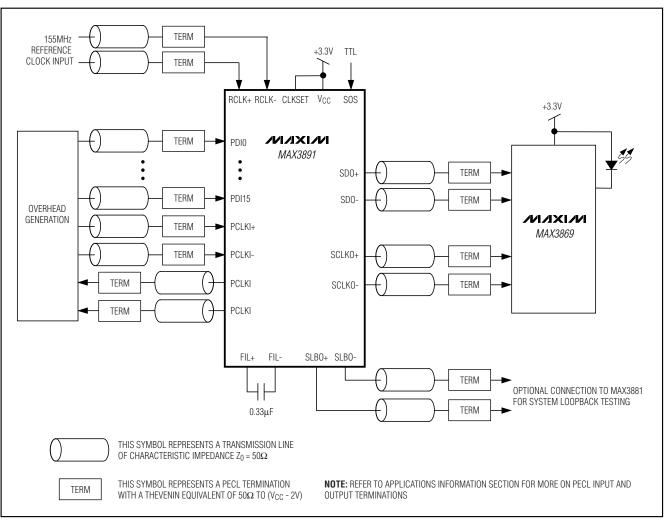

The MAX3891 converts 16-bit wide, 155Mbps data to 2.5Gbps serial data (Figure 2). The MAX3891 is composed of a 16-bit parallel input register, a 16-bit shift register, control and timing logic, PECL output buffers and a frequency-synthesizing PLL, consisting of a phase/frequency detector, loop filter/amplifier, voltage-controlled oscillator, and prescaler.

The PLL synthesizes an internal 2.5Gbps reference used to clock the output shift register. This clock is generated from the external 155.52MHz, 77.76MHz, 51.84MHz, or 38.88MHz reference-clock signal (RCLK).

The incoming parallel data is clocked into the MAX3891 on the rising transition of the parallel clock-input signal (PCLKI). Proper operation is ensured if the parallel-input register is latched within a window of time (tskew),

defined with respect to the parallel clock-output signal (PCLKO). PCLKO is the synthesized 2.488Gbps internal serial-clock signal divided by 16. The allowable PCLKO to PCLKI skew is 0ns to 4ns. This defines a timing window after the PCLKO rising edge, during which a PCLKI rising edge may occur (Figure 1).

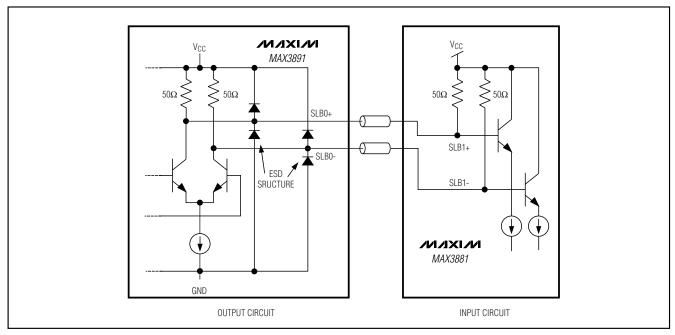

#### System Loopback

The MAX3891 is designed to provide system loopback testing. The loopback outputs (SLBO) of the MAX3891 may be directly connected to the loopback inputs of a deserializer (MAX3881) for system diagnostics. To enable the SLBO outputs, apply a TTL logic-high signal to the SOS input. The same signal that controls the SOS enable input may also be used to control the SIS enable input on the MAX3881.

Figure 2. Functional Block Diagram

## Applications Information

### **Setup and Hold Time Requirements**

The setup and hold-time specifications assume that the parallel clock-input signal (PCLKI) and parallel-data input signal (PDI\_) are from the same source. They should have identical common-mode voltages, signal amplitudes, and slew rates. If PCLKI and PDI\_ differ significantly, the setup and hold-time requirements must be modified to account for these differences. Define tDEG as the adjustment to the setup and hold-time requirement when there are significant differences between PCLKI and PDI\_.

$$t_{DEG} = VCM_{DIFF} \times \frac{t_{T}}{\left(\frac{0.6}{V_{OH} - V_{OL}}\right)}$$

where tT is the transition time (20%–80%) of the parallel-data and clock-input signals,  $V_{OH}$  and  $V_{OL}$  are the input high and low voltage, respectively, of the parallel-data and clock-input signals, and VCMDIFF is the difference in common-mode voltages of the parallel-data and clock-input signals.

The adjusted setup (tsuadu) and hold-time (thadu) requirements become

tsuadj (or thadj) = tsu (or th) + tdeg

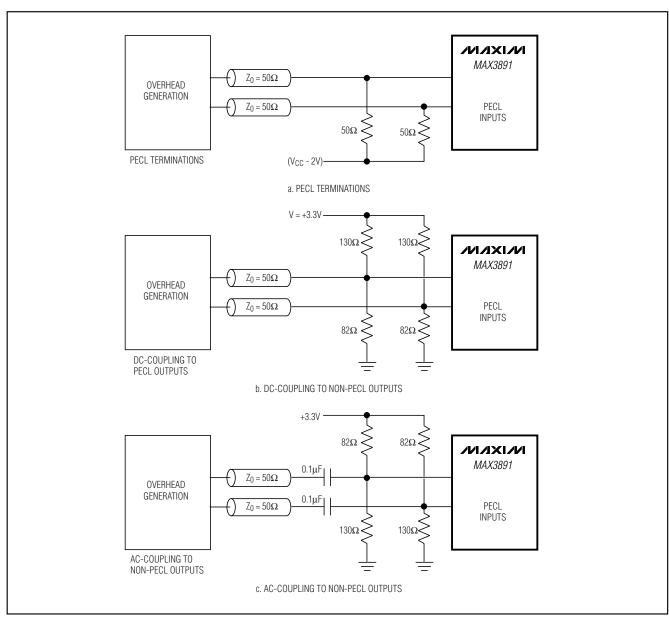

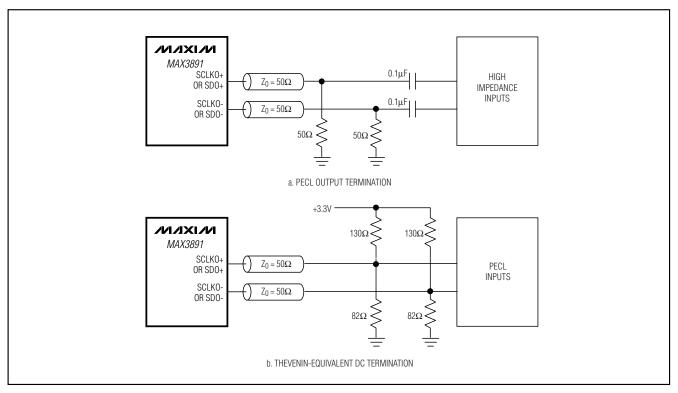

#### **PECL Input and Output Terminations**

It is important to bias the MAX3891's PECL data and clock IOs appropriately. Figures 3 and 4 show alternative PECL output termination methods. A circuit that provides  $50\Omega$  to (VCC - 2V) should be used in conjunction with controlled impedance transmission lines for proper termination. Use Thevenin equivalent termination when a (VCC - 2V) supply is not available. If ACcoupling is necessary, make sure that the coupling capacitor follows the  $50\Omega$  or Thevenin equivalent DC termination. To ensure best performance, the differential outputs (SDO± and PCLKO±) must have balanced loads.

#### **Current-Mode Logic Outputs**

The system loopback outputs (SLBO) of the MAX3891 are CML compatible. The configuration of the MAX3891 current-mode logic (CML) output circuit includes internal  $50\Omega$  back termination to VCC (Figure 5). These outputs are intended to drive a terminated  $50\Omega$  transmission line.

#### **Layout Techniques**

For best performance, use good high-frequency layout techniques. Filter voltage supplies and keep ground connections short. Use multiple vias where possible. Use controlled impedance transmission lines to interface with the MAX3891 clock and data inputs and outputs.

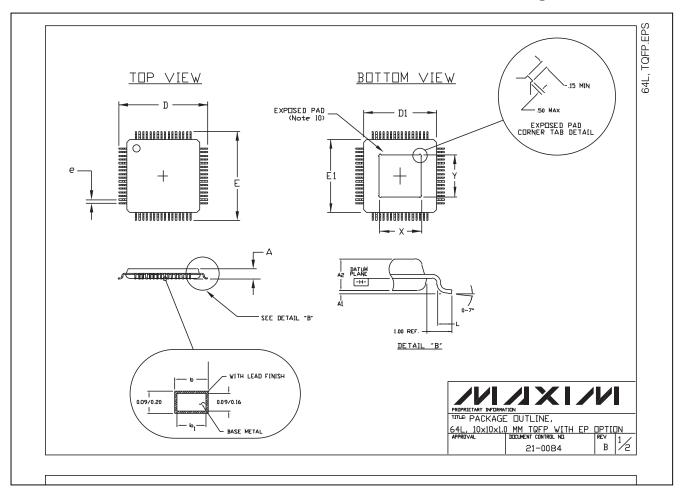

### **Exposed Pad Package**

The 64-pin exposed pad (EP) TQFP incorporates features that provide a very low thermal-resistance path for heat removal. The MAX3891 EP must be soldered directly to a ground plane with good thermal conductance.

### **Chip Information**

TRANSISTOR COUNT: 1712

PROCESS: Bipolar

Figure 3. Alternative PECL-Input Termination

Figure 4. Alternative PECL-Output Termination

Figure 5. Current-Mode Logic

NIXIN

### **Typical Application Circuit**

10 \_\_\_\_\_\_\_/N/JXI/VI

## Package Information

### Package Information (continued)

NOTES:

1. ALL DIMENSIONS AND TOLERANCING CONFORM TO ANSI Y14.5—1982.

2. DATUM PLANE [—H—] IS LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

3. DIMENSIONS DI AND EL DO NOT INCLUDE MOLD PROTRUSION.

4. THE TOP OF PACKAGE IS SMALLER THAN THE BOTTOM OF PACKAGE BY 0.15 MILLIMETERS.

5. DIMENSION & DOORS NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM TOTAL IN EXCESS OF THE & DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. CONTROLLING DIMENSION: MILLIMETER.

7. THIS OUTTINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO—136, VARIATION AJ.

8. LEADS SHALL BE COPLANAR WITHIN .004 INCH.

9. EXPOSED DIE PAD SHALL BE COPLANAR WITH BOTTOM OF PACKAGE WITHIN 2 MILS (.05 MM).

10. DIMENSIONS X & Y APPLY TO EXPOSED PAD (EP) VERSIONS ONLY. SEE INDIVIDUAL PRODUCT DATASHEET TO DETERMINE IF A PRODUCT USES EXPOSED PAD PACKAGE. JEDEC VARIATION ALL DIMENSIONS IN MILLIMETERS MIN. MAX. Α 1.20 Αı 0.05 0.15 Aa 0.95 1.05 D 12.00 BSC D<sub>1</sub> 10.00 B2C. Ε 12.00 BSC Εı 10.00 BSC L 0.45 0.75 Ŋ 64 0.50 BSC Ь 0.17 0.27 lo1 0.17 0.23 ×Χ 4 70 5.30 64L, 10×10×1.0 MM TQFP WITH EP \* EXPOSED PAD (Note 10) 21-0084

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.