#### **General Description**

The MAX3803 equalizer automatically provides compensation for transmission-medium losses encountered with FR4 stripline and cable in an incredibly small 2mm  $\times$  2.5mm package. It is ideal for backplane applications requiring up to 40in between the line card and the switch card or up to 10m of twin ax cable between racks. Its small size provides placement and routing flexibility. The CML inputs and outputs are DC-coupled and can be terminated to a supply as low as +1.1V. The MAX3803 operates from 0°C to +85°C and consumes 160mW at +3.3V.

#### \_Applications

Backplane Interconnect Rack-to-Rack Interconnect Common-Mode Voltage Translation

(LVDS, PECL, or CML)

#### \_Features

- DC-Coupled Input and Output to Terminations as Low as +1.1V

- ♦ 2mm × 2.5mm UCSP<sup>™</sup>

- 1Gbps to 3.2Gbps Operating Range

- Spans 40in (1m) of FR4

- Spans 10m, 28AWG Twin Ax

- Receive Equalization to Reduce ISI

**Ordering Information**

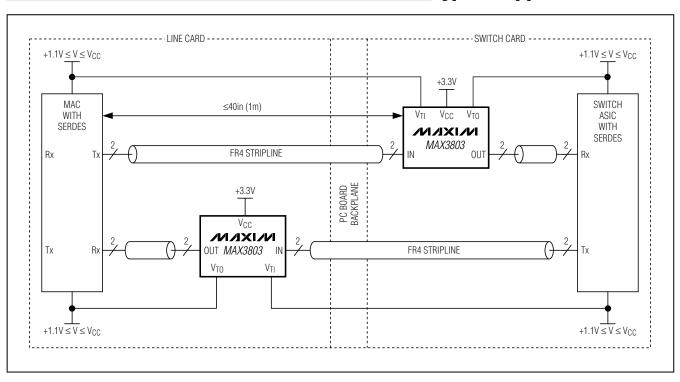

**Typical Application Circuit**

| PART         | TEMP RANGE   | PIN-PACKAGE |

|--------------|--------------|-------------|

| MAX3803UBP-T | 0°C to +85°C | 5 x 4 UCSP  |

#### Pin Configuration appears at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage, V<sub>CC</sub>, V<sub>TI</sub>, and V<sub>TO</sub> ....-0.5V to +6V Continuous Output Current ....-25mA to +25mA IN±, OUT±, EN....-0.5V to (V<sub>CC</sub> + 0.5V) Operating Ambient Temperature Range ......0°C to +85°C Storage Ambient Temperature Range......55°C to +150°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| PARAMETER                     | SYMBOL          | CONDITIONS                   | MIN   | ТҮР | MAX             | UNITS      |

|-------------------------------|-----------------|------------------------------|-------|-----|-----------------|------------|

| Supply Voltage                | V <sub>CC</sub> |                              | 3.0   | 3.3 | 3.6             | V          |

| Input Termination Voltage     | VTI             |                              | 1.1   |     | VCC             | V          |

| Output Termination Voltage    | V <sub>TO</sub> |                              | 1.1   |     | V <sub>CC</sub> | V          |

| Supply Noise Tolerance        |                 | 10Hz ≤ f < 100Hz             |       | 100 |                 |            |

|                               |                 | 100Hz ≤ f < 1MHz             |       | 40  |                 | $mV_{P-P}$ |

|                               |                 | 1MHz ≤ f ≤ 2.5GHz            |       | 10  |                 | ]          |

| Operating Ambient Temperature |                 |                              | 0     | 25  | 85              | °C         |

| Bit Rate                      |                 | NRZ data                     | 2.488 |     | 3.125           | Gbps       |

| CID                           |                 | Consecutive identical digits |       |     | 100             | bits       |

#### **ELECTRICAL CHARACTERISTICS**

(Typical values are at +3.3V and at  $T_A = +25^{\circ}$ C, unless otherwise noted. Specifications guaranteed over specified operating conditions.)

| PARAMETER                          | SYMBOL                          | CONDITIONS                                       | MIN                        | ТҮР                         | МАХ                        | UNITS             |

|------------------------------------|---------------------------------|--------------------------------------------------|----------------------------|-----------------------------|----------------------------|-------------------|

|                                    |                                 | EN = high                                        |                            | 45                          | 67                         | mA                |

| Supply Current (Note 1)            |                                 | EN = low                                         |                            | 14                          | 32                         |                   |

| Output Driver Supply Current       |                                 | (Note 2)                                         |                            | 9                           | 14                         | mA                |

| Input Swing (Note 1)               |                                 | Measured differentially at point A (Figure 1)    | 400                        |                             | 1000                       | mV <sub>P-P</sub> |

| Input Common-Mode Voltage<br>Range |                                 | (Note 1)                                         | V <sub>TI</sub> -<br>0.25V |                             | V <sub>TI</sub> -<br>0.10V | V                 |

| Input Return Loss                  |                                 | 100MHz to 2.5GHz                                 |                            | 10                          |                            | dB                |

| Input Resistance                   |                                 | Single ended (Note 1)                            | 42.5                       | 50                          | 57.5                       | Ω                 |

| Output Swing (Nates 1, 2)          |                                 | EN = high                                        | 440                        | 525                         | 680                        | mV <sub>P-P</sub> |

| Output Swing (Notes 1, 3)          |                                 | EN = low                                         |                            | 30                          |                            |                   |

| Output Common-Mode Voltage         |                                 |                                                  |                            | V <sub>TO</sub> -<br>0.112V |                            | V                 |

| Output Resistance                  |                                 | Single ended (Note 1)                            | 42.5                       | 50                          | 57.5                       | Ω                 |

| Output Return Loss                 |                                 | 100MHz to 2.5GHz                                 |                            | 10                          |                            | dB                |

| Output Transition Time             | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% (Notes 2, 4)                          | 40                         | 70                          | 100                        | ps                |

| Differential Skew                  |                                 | Difference in 50% crossing between OUT+ and OUT- |                            | 10                          |                            | ps                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(Typical values are at +3.3V and at  $T_A = +25^{\circ}$ C, unless otherwise noted. Specifications guaranteed over specified operating conditions.)

| PARAMETER                                                                | SYMBOL          | CONDITIONS          | MIN | ТҮР       | MAX       | UNITS             |

|--------------------------------------------------------------------------|-----------------|---------------------|-----|-----------|-----------|-------------------|

|                                                                          |                 | 0in, 6-mil FR4      |     | 0.01      | 0.10      |                   |

|                                                                          |                 | 10in, 6-mil FR4     |     | 0.04      | 0.10      |                   |

|                                                                          |                 | 20in, 6-mil FR4     |     | 0.05      | 0.10      |                   |

| Residual Deterministic Jitter Output                                     |                 | 30in, 6-mil FR4     |     | 0.05      | 0.15      |                   |

| (2.5Gbps, CJTPAT) (Notes 2, 5)                                           |                 | 40in, 6-mil FR4     |     | 0.07      | 0.15      | UI                |

|                                                                          |                 | 3m Tensolite cable  |     | 0.03      | 0.10      |                   |

|                                                                          |                 | 5m Tensolite cable  |     | 0.1       | 0.20      |                   |

|                                                                          |                 | 10m Tensolite cable |     | 0.14      | 0.25      |                   |

|                                                                          |                 | 0in, 6-mil FR4      |     | 0.01      | 0.10      |                   |

| Residual Deterministic Jitter Output                                     |                 | 10in, 6-mil FR4     |     | 0.06      | 0.10      | ]                 |

| (2.5Gbps, 2 <sup>7</sup> PRBS + 100 CID)                                 |                 | 20in, 6-mil FR4     |     | 0.11      | 0.15      | UI                |

| (Notes 2, 6)                                                             |                 | 30in, 6-mil FR4     |     | 0.15 0.20 | ]         |                   |

|                                                                          |                 | 3m Tensolite cable  |     | 0.09      | 0.15      | 1                 |

|                                                                          |                 | 0in, 6-mil FR4      |     | 0.01      | 0.10      | -                 |

|                                                                          |                 | 10in, 6-mil FR4     |     | 0.02      | 0.10      |                   |

|                                                                          |                 | 20in, 6-mil FR4     |     | 0.03      | 0.03 0.15 |                   |

| Residual Deterministic Jitter Output<br>(3.125Gbps, CJTPAT) (Notes 2, 7) |                 | 30in, 6-mil FR4     |     | 0.06      | 0.15      | UI                |

| (3.123Gbps, CUTFAT)(Notes 2, 7)                                          |                 | 40in, 6-mil FR4     |     | 0.11      | 0.25      |                   |

|                                                                          |                 | 3m Tensolite cable  |     | 0.05 0.10 | ]         |                   |

|                                                                          |                 | 5m Tensolite cable  |     | 0.16      | 0.25      | ō                 |

| Random Jitter Output                                                     |                 | (Notes 2, 4)        |     | 2         | 3         | ps <sub>RMS</sub> |

| Latency                                                                  |                 | From IN to OUT      |     | 0.3       |           | ns                |

| Low-Frequency Cutoff                                                     |                 |                     |     | 15        |           | kHz               |

| LVTTL Input High Voltage                                                 | VIH             | (Note 1)            | 1.5 |           |           | V                 |

| LVTTL Input Low Voltage                                                  | VIL             | (Note 1)            |     |           | 0.5       | V                 |

| LVTTL Input High Current                                                 | IIН             | (Note 1)            |     |           | 10        | μA                |

| LVTTL Input Low Current                                                  | ١ <sub>١L</sub> | (Note 1)            |     |           | 10        | μA                |

Note 1: Production tested at  $T_A = +25^{\circ}$ C. Specifications over temperature are guaranteed by design and characterization.

Note 2: Specifications are guaranteed by design and characterization.

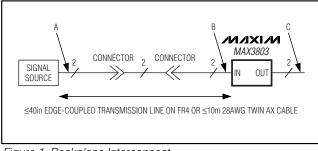

Note 3: Measured differentially at point C with 50 $\Omega \pm 1\%$  at each side (Figure 1).

Note 4: Using a 00000111111 or equivalent pattern at selected bit rate. Measured at 600mV<sub>P-P</sub> input voltage, 10m cable or 40in FR4, at 2.5Gbps and within 2in of output pins.

Note 5: Difference in peak-to-peak deterministic jitter between reference points A and C in Figure 1. Evaluated at 2.5Gbps with CJTPAT.

**Note 6:** Difference in peak-to-peak deterministic jitter between reference points A and C in Figure 1. Evaluated at 2.5Gbps with a PRBS 2<sup>7</sup> with 100 CIDs input pattern.

Note 7: Difference in peak-to-peak deterministic jitter between reference points A and C in Figure 1. Evaluated at 3.125Gbps with CJTPAT.

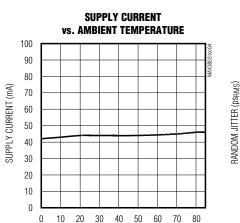

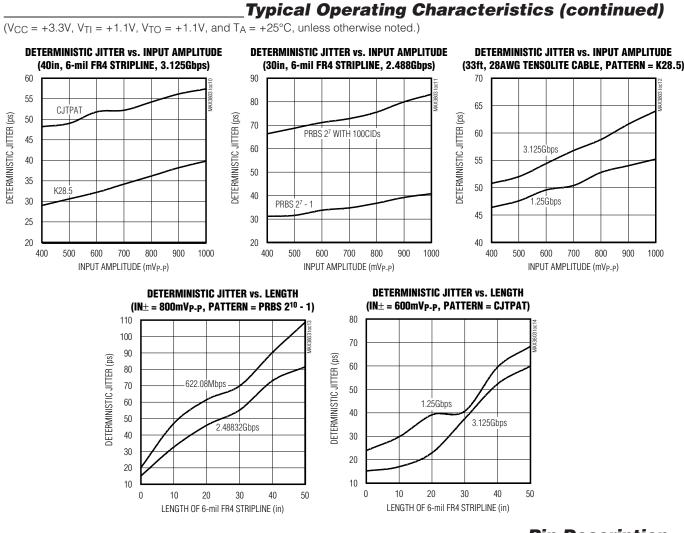

(V<sub>CC</sub> = +3.3V, V<sub>TI</sub> = +1.1V, V<sub>TO</sub> = +1.1V, and  $T_A$  = +25°C, unless otherwise noted.)

40 10 20 30 50 60 70 AMBIENT TEMPERATURE (°C)

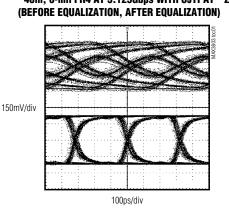

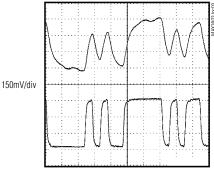

150mV/div

(BEFORE EQUALIZATION, AFTER EQUALIZATION)

100ps/div

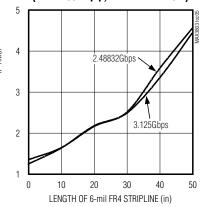

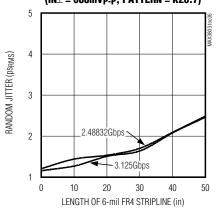

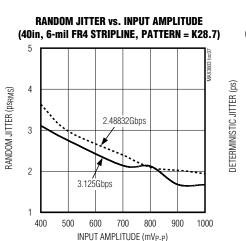

**RANDOM JITTER vs. LENGTH**  $(IN \pm = 400 mV_{P-P}, PATTERN = K28.7)$

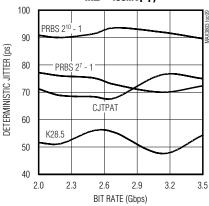

**Typical Operating Characteristics**

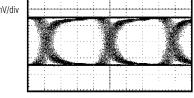

40in, 6-mil FR4 AT 3.125Gbps WITH CJTPAT 20ft TENSOLITE CABLE AT 2.48832Gbps WITH PRBS 2<sup>23</sup> - 1 30in, 6-mil FR4 AT 3.125Gbps WITH K28.5 (BEFORE EQUALIZATION, AFTER EQUALIZATION)

**RANDOM JITTER vs. LENGTH**  $(IN \pm = 800 mV_{P-P}, PATTERN = K28.7)$

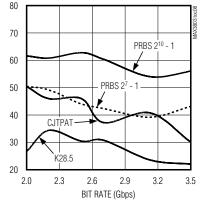

**DETERMINISTIC JITTER vs. BIT RATE** (33ft, 28AWG TENSOLITE CABLE,  $IN \pm = 400 mV_{P-P}$

**DETERMINISTIC JITTER vs. BIT RATE** (30in, 6-mil FR4 STRIPLINE,  $IN \pm = 1000 mV_{P-P}$ )

4

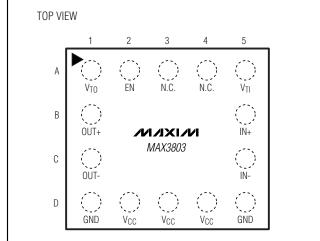

#### **Pin Description**

| PIN        | NAME            | NAME FUNCTION                                                                                                                          |  |  |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1         | V <sub>TO</sub> | Output Termination Voltage                                                                                                             |  |  |

| A2         | EN              | Enable. Connect to $V_{CC}$ to enable the equalizer core. Connect to GND to disable the equalizer core, TTL. Do not leave unconnected. |  |  |

| A3, A4     | N.C.            | No Connection                                                                                                                          |  |  |

| A5         | V <sub>TI</sub> | Input Termination Voltage                                                                                                              |  |  |

| B1         | OUT+            | Positive Data Output, CML                                                                                                              |  |  |

| B5         | IN+             | Positive Data Input, CML                                                                                                               |  |  |

| C1         | OUT-            | Negative Data Output, CML                                                                                                              |  |  |

| C5         | IN-             | Negative Data Input, CML                                                                                                               |  |  |

| D1, D5     | GND             | Supply Ground                                                                                                                          |  |  |

| D2, D3, D4 | Vcc             | Core Supply Voltage                                                                                                                    |  |  |

MAX3803

#### Detailed Description \_and Applications Information

The MAX3803 is an adaptive equalizer designed to extend the reach of transmission lines in high-frequency backplane and rack-to-rack interconnect applications. The MAX3803 automatically adjusts to attenuation caused by skin-effect and dielectric losses. Although optimized for coded and scrambled data between 2.488Gbps and 3.125Gbps, the MAX3803 provides effective compensation for rates between 1Gbps and 3.2Gbps.

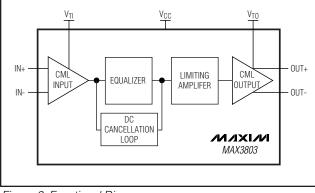

The MAX3803 consists of low common-mode input and output buffers, an equalizer core, a DC-offset-correction loop, and a limiting amplifier (Figure 2).

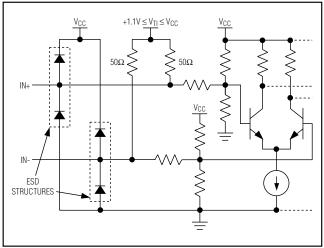

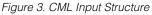

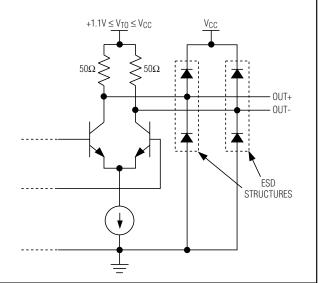

**Low Common-Mode Input and Output** The MAX3803 permits DC-coupling to CML transmitters and receivers that require termination voltages as low as 1.1V and as high as V<sub>CC</sub>. Use the V<sub>TI</sub> and V<sub>TO</sub> pins to maintain compatible common-mode levels between the data source and load. V<sub>TI</sub> and V<sub>TO</sub> are independent and can be used to bridge two common-mode requirements without the use of DC-blocking capacitors. See Figure 3 and Figure 4 for the equivalent input and output structures.

Figure 1. Backplane Interconnect

Figure 2. Functional Diagram

#### **Media Equalization**

Equalization at the input compensates for high-frequency loss encountered with FR4 stripline (edge-coupled) or 28AWG twin ax. The equalizer core is an amplifier with a self-adjusting frequency response.

#### **DC Cancellation Loop**

The DC cancellation loop removes the pulse-width distortion caused by internal offsets. The closed-loop response creates a low-frequency cutoff of approximately 15kHz, below which the offset control tracks the AC signal. This also sets the limit on the maximum time

Figure 4. CML Output Structure

M/IXI/M

required to reach a balanced mark/space ratio (i.e., 50%). This permits the use of scrambled data as found in SONET and SDH transmissions.

#### **Limiting Amplifier**

The limiting amplifier limits the outputs of the equalizer so all frequencies are at the same output voltage level.

#### **Enable Function**

Connect the EN pin to  $V_{CC}$  to enable the equalizer core. Connect the EN pin to GND to disable the equalizer core when valid data is not present to save power. When EN is low, the outputs are static with approximately  $30mV_{P-P}$  differential. This pin must be connected to  $V_{CC}$  or GND.

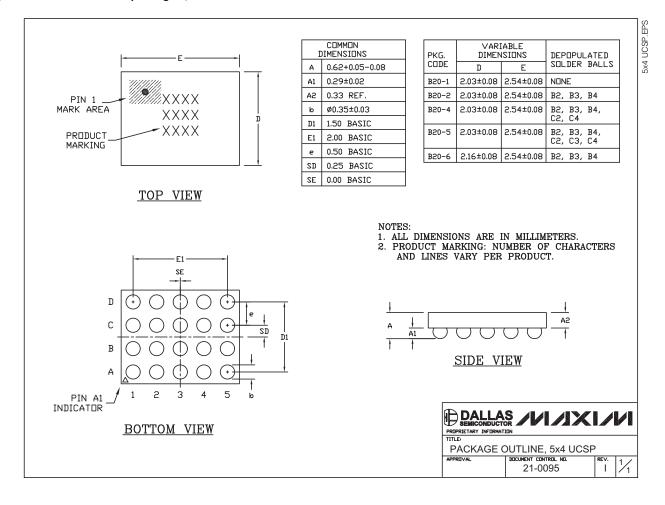

#### Packaging

The MAX3803 is packaged in a 2.5mm  $\times$  2mm, 5  $\times$  4 chip-scale package (USCP). The six center ball positions (B2, B3, B4, C2, C3, C4) are not populated, leaving fourteen perimeter balls. This package does not require underfill over an ambient temperature range of 0°C to +85°C. Thermal dissipation is provided through the GND connection. Go to Maxim's website, www.maximic.com, for the latest packaging information and details about UCSP layout and handling.

#### Layout Techniques

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance transmission lines to interface with the MAX3803 high-speed inputs and outputs. Power-supply decoupling should be placed as close to the V<sub>CC</sub> as possible. To reduce feedthrough, isolate input signals from output signals.

**Pin Configuration**

UCSP 2.5mm × 2mm

# **MAX3803**

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

8 \_

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.