# 1-/2-/4-Channel **Digital Potentiometers**

# AD8400/AD8402/AD8403

#### **FEATURES**

256-position variable resistance device Replaces 1, 2, or 4 potentiometers  $1 k\Omega$ ,  $10 k\Omega$ ,  $50 k\Omega$ ,  $100 k\Omega$ Power shutdown—less than 5 µA 3-wire, SPI-compatible serial data input 10 MHz update data loading rate 2.7 V to 5.5 V single-supply operation **Qualified for automotive applications**

#### **APPLICATIONS**

Mechanical potentiometer replacement Programmable filters, delays, time constants Volume control, panning Line impedance matching Power supply adjustment

#### **GENERAL DESCRIPTION**

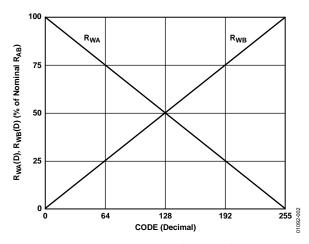

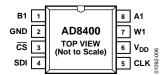

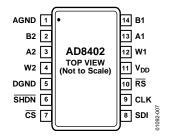

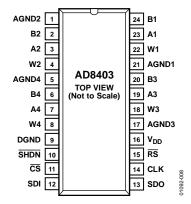

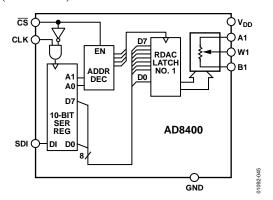

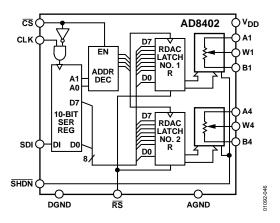

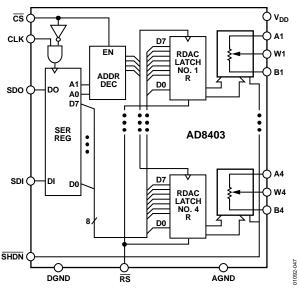

The AD8400/AD8402/AD8403 provide a single-, dual-, or quad-channel, 256-position, digitally controlled variable resistor (VR) device. 1 These devices perform the same electronic adjustment function as a mechanical potentiometer or variable resistor. The AD8400 contains a single variable resistor in the compact SOIC-8 package. The AD8402 contains two independent variable resistors in space-saving SOIC-14 surface-mount packages. The AD8403 contains four independent variable resistors in 24-lead PDIP, SOIC, and TSSOP packages. Each part contains a fixed resistor with a wiper contact that taps the fixed resistor value at a point determined by the digital code loaded into the controlling serial input register. The resistance between the wiper and either endpoint of the fixed resistor varies linearly with respect to the digital code transferred into the VR latch. Each variable resistor offers a completely programmable value of resistance between the A terminal and the wiper or the B terminal and the wiper. The fixed A-to-B terminal resistance of 1 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , or 100 k $\Omega$  has a  $\pm 1\%$ channel-to-channel matching tolerance with a nominal temperature coefficient of 500 ppm/°C. A unique switching circuit minimizes the high glitch inherent in traditional switched resistor designs, avoiding any make-before-break or break-before-make operation.

(continued on Page 3)

# Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

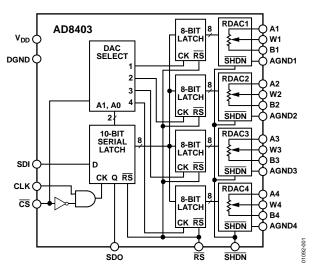

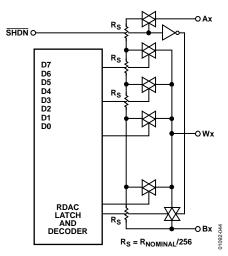

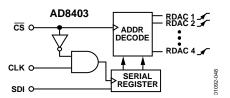

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

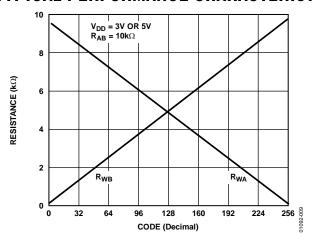

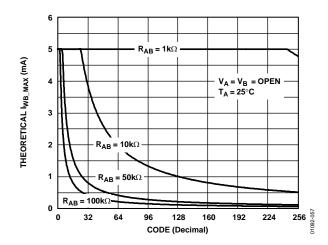

Figure 2. R<sub>WA</sub> and R<sub>WB</sub> vs. Code

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. www.analog.com Tel: 781.329.4700 Fax: 781.461.3113

© 2010 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>1</sup> The terms digital potentiometer, VR, and RDAC are used interchangeably.

# **TABLE OF CONTENTS**

| Features 1                                                           | ESD Caution                                   | 11 |

|----------------------------------------------------------------------|-----------------------------------------------|----|

| Applications                                                         | Pin Configurations and Function Descriptions  | 12 |

| General Description1                                                 | Typical Performance Characteristics           | 14 |

| Functional Block Diagram1                                            | Test Circuits                                 | 19 |

| Revision History                                                     | Theory of Operation                           | 20 |

| Specifications                                                       | Programming the Variable Resistor             | 20 |

| Electrical Characteristics—10 k $\Omega$ Version4                    | Programming the Potentiometer Divider         | 21 |

| Electrical Characteristics—50 $k\Omega$ and 100 $k\Omega$ Versions 6 | Digital Interfacing                           | 21 |

| Electrical Characteristics—1 k $\Omega$ Version                      | Applications                                  | 24 |

| Electrical Characteristics—All Versions                              | Active Filter                                 | 24 |

| Timing Diagrams10                                                    | Outline Dimensions                            | 26 |

| Absolute Maximum Ratings11                                           | Ordering Guide                                | 30 |

| Serial Data-Word Format11                                            | Automotive Products                           | 31 |

| REVISION HISTORY                                                     |                                               |    |

| 7/10—Rev. D to Rev. E                                                | 11/01—Rev. B to Rev. C                        |    |

| Changes to Features Section1                                         | Addition of new Figure                        |    |

| Changes to IAB Continuous Current Parameter (Table 5)11              | Edits to Specifications                       |    |

| Updated Outline Dimensions26                                         | Edits to Absolute Maximum Ratings             |    |

| Changes to Ordering Guide30                                          | Edits to TPCs 1, 8, 12, 16, 20, 24, 35        | 9  |

| Added Automotive Products Section31                                  | Edits to                                      |    |

| 10/05—Rev. C to Rev. D                                               | the Programming the Variable Resistor Section | 13 |

| Updated FormatUniversal                                              |                                               |    |

| Changes to Features1                                                 |                                               |    |

| Changes to Table 14                                                  |                                               |    |

| Changes to Table 26                                                  |                                               |    |

| Changes to Table 38                                                  |                                               |    |

| Changes to Table 511                                                 |                                               |    |

| Added Figure 3618                                                    |                                               |    |

| Replaced Figure 3719                                                 |                                               |    |

| Changes to Theory of Operation Section20                             |                                               |    |

| Changes to Applications Section24                                    |                                               |    |

| Updated Outline Dimensions26                                         |                                               |    |

| Changes to Ordering Guide28                                          |                                               |    |

|                                                                      |                                               |    |

## **GENERAL DESCRIPTION**

(continued from Page 1)

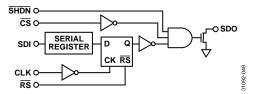

Each VR has its own VR latch that holds its programmed resistance value. These VR latches are updated from an SPI-compatible, serial-to-parallel shift register that is loaded from a standard 3-wire, serial-input digital interface. Ten data bits make up the data-word clocked into the serial input register.

The data-word is decoded where the first two bits determine the address of the VR latch to be loaded, and the last eight bits are the data. A serial data output pin at the opposite end of the serial register allows simple daisy chaining in multiple VR applications without additional external decoding logic.

The reset  $(\overline{RS})$  pin forces the wiper to midscale by loading  $80_H$  into the VR latch. The  $\overline{SHDN}$  pin forces the resistor to an end-to-end open-circuit condition on the A terminal and shorts the wiper to the  $\overline{B}$  terminal, achieving a microwatt power shutdown state. When  $\overline{SHDN}$  is returned to logic high, the previous latch settings put the wiper in the same resistance setting prior to shutdown. The digital interface is still active in shutdown so that code changes can be made that will produce new wiper positions when the device is taken out of shutdown.

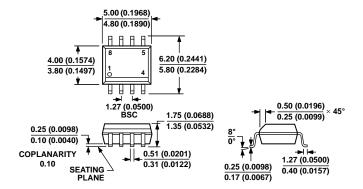

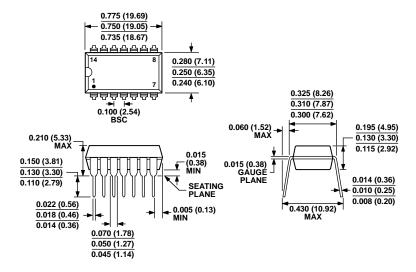

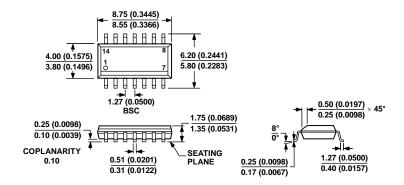

The AD8400 is available in the SOIC-8 surface mount. The AD8402 is available in both surface-mount (SOIC-14) and 14-lead PDIP packages, while the AD8403 is available in a narrow-body, 24-lead PDIP and a 24-lead, surface-mount package. The AD8402/AD8403 are also offered in the 1.1 mm thin TSSOP-14/TSSOP-24 packages for PCMCIA applications. All parts are guaranteed to operate over the extended industrial temperature range of -40°C to +125°C.

# **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS—10 KΩ VERSION**

$V_{DD} = 3 \text{ V} \pm 10\% \text{ or } 5 \text{ V} \pm 10\%, V_A = V_{DD}, V_B = 0 \text{ V}, -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1.

| Parameter                                   | Symbol                   | Symbol Conditions                                                            |                       |        | Max      | Unit   |

|---------------------------------------------|--------------------------|------------------------------------------------------------------------------|-----------------------|--------|----------|--------|

| DC CHARACTERISTICS RHEOSTAT N               | 10DE (Specific           | ations Apply to All VRs)                                                     |                       |        |          |        |

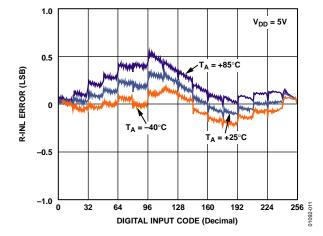

| Resistor Differential NL <sup>2</sup>       | R-DNL                    | $R_{WB}$ , $V_A$ = no connect                                                | -1                    | ±1/4   | +1       | LSB    |

| Resistor Nonlinearity <sup>2</sup>          | R-INL                    | $R_{WB}$ , $V_A$ = no connect                                                | -2                    | ±1/2   | +2       | LSB    |

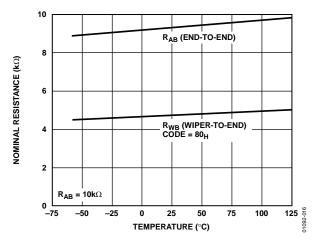

| Nominal Resistance <sup>3</sup>             | R <sub>AB</sub>          | $T_A = 25$ °C, model: AD840XYY10                                             | 8                     | 10     | 12       | kΩ     |

| Resistance Tempco                           | $\Delta R_{AB}/\Delta T$ | $V_{AB} = V_{DD}$ , wiper = no connect                                       |                       | 500    |          | ppm/°C |

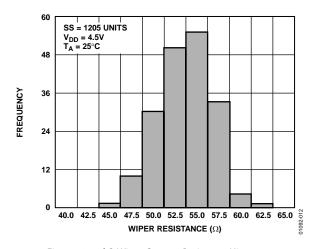

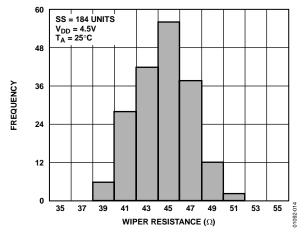

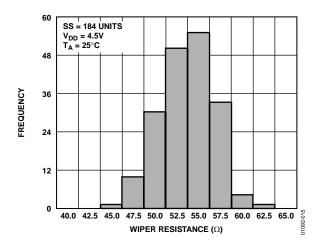

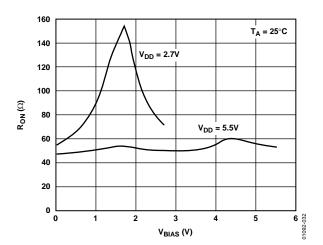

| Wiper Resistance                            | Rw                       | $V_{DD} = 5V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 50     | 100      | Ω      |

|                                             | Rw                       | $V_{DD} = 3V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 200    |          | Ω      |

| Nominal Resistance Match                    | $\Delta R/R_{AB}$        | CH 1 to CH 2, CH 3, or CH 4, $V_{AB} = V_{DD}$ , $T_A = 25^{\circ}C$         |                       | 0.2    | 1        | %      |

| DC CHARACTERISTICS POTENTIOM                | ETER DIVIDER             | (Specifications Apply to All VRs)                                            |                       |        |          |        |

| Resolution                                  | N                        |                                                                              | 8                     |        |          | Bits   |

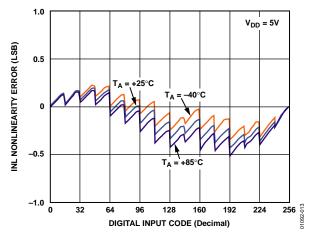

| Integral Nonlinearity <sup>4</sup>          | INL                      |                                                                              | -2                    | ±1/2   | +2       | LSB    |

| Differential Nonlinearity⁴                  | DNL                      | $V_{DD} = 5 V$                                                               | -1                    | ±1/4   | +1       | LSB    |

|                                             | DNL                      | $V_{DD} = 3 \text{ V, } T_A = 25^{\circ}\text{C}$                            | -1                    | ±1/4   | +1       | LSB    |

|                                             | DNL                      | $V_{DD} = 3 \text{ V, } T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$   | -1.5                  | ±1/2   | +1.5     | LSB    |

| Voltage Divider Tempco                      | $\Delta V_W/\Delta T$    | Code = 80 <sub>H</sub>                                                       |                       | 15     |          | ppm/°C |

| Full-Scale Error                            | V <sub>WFSE</sub>        | Code = FF <sub>H</sub>                                                       | -4                    | -2.8   | 0        | LSB    |

| Zero-Scale Error                            | V <sub>wzse</sub>        | Code = 00 <sub>H</sub>                                                       | 0                     | 1.3    | 2        | LSB    |

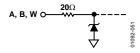

| RESISTOR TERMINALS                          |                          |                                                                              |                       |        |          |        |

| Voltage Range⁵                              | V <sub>A, B, W</sub>     |                                                                              | 0                     |        | $V_{DD}$ | ٧      |

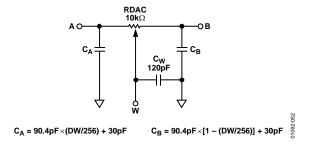

| Capacitance <sup>6</sup> Ax, Capacitance Bx | C <sub>A, B</sub>        | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 75     |          | рF     |

| Capacitance <sup>6</sup> Wx                 | Cw                       | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 120    |          | рF     |

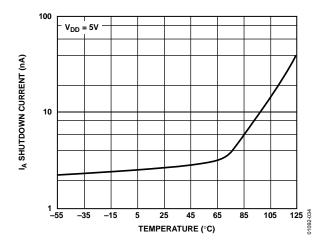

| Shutdown Current <sup>7</sup>               | I <sub>A_SD</sub>        | $V_A = V_{DD}$ , $V_B = 0$ V, $\overline{SHDN} = 0$                          |                       | 0.01   | 5        | μΑ     |

| Shutdown Wiper Resistance                   | Rw_sd                    | $V_A = V_{DD}, V_B = 0 \text{ V}, \overline{SHDN} = 0, V_{DD} = 5 \text{ V}$ |                       | 100    | 200      | Ω      |

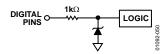

| DIGITAL INPUTS AND OUTPUTS                  |                          |                                                                              |                       |        |          |        |

| Input Logic High                            | V <sub>IH</sub>          | $V_{DD} = 5 V$                                                               | 2.4                   |        |          | ٧      |

| Input Logic Low                             | V <sub>IL</sub>          | $V_{DD} = 5 \text{ V}$                                                       |                       |        | 0.8      | ٧      |

| Input Logic High                            | V <sub>IH</sub>          | $V_{DD} = 3 V$                                                               | 2.1                   |        |          | ٧      |

| Input Logic Low                             | V <sub>IL</sub>          | $V_{DD} = 3 V$                                                               |                       |        | 0.6      | ٧      |

| Output Logic High                           | V <sub>OH</sub>          | $R_L = 2.2 \text{ k}\Omega \text{ to } V_{DD}$                               | V <sub>DD</sub> – 0.1 |        |          | ٧      |

| Output Logic Low                            | V <sub>OL</sub>          | $I_{OL} = 1.6 \text{ mA}, V_{DD} = 5 \text{ V}$                              |                       |        | 0.4      | ٧      |

| Input Current                               | I <sub>IL</sub>          | $V_{IN} = 0 \text{ V or } 5 \text{ V}, V_{DD} = 5 \text{ V}$                 |                       |        | ±1       | μΑ     |

| Input Capacitance <sup>6</sup>              | C <sub>IL</sub>          |                                                                              |                       | 5      |          | pF     |

| POWER SUPPLIES                              |                          |                                                                              |                       |        |          |        |

| Power Supply Range                          | V <sub>DD</sub> range    |                                                                              | 2.7                   |        | 5.5      | ٧      |

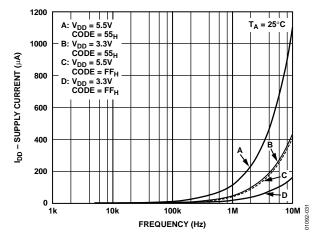

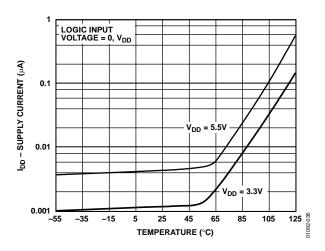

| Supply Current (CMOS)                       | I <sub>DD</sub>          | $V_{IH} = V_{DD}$ or $V_{IL} = 0$ V                                          |                       | 0.01   | 5        | μΑ     |

| Supply Current (TTL) <sup>8</sup>           | I <sub>DD</sub>          | $V_{IH} = 2.4 \text{ V or } 0.8 \text{ V}, V_{DD} = 5.5 \text{ V}$           |                       | 0.9    | 4        | mA     |

| Power Dissipation (CMOS) <sup>9</sup>       | P <sub>DISS</sub>        | $V_{IH} = V_{DD} \text{ or } V_{IL} = 0 \text{ V}, V_{DD} = 5.5 \text{ V}$   |                       |        | 27.5     | μW     |

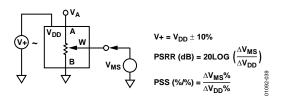

| Power Supply Sensitivity                    | PSS                      | $V_{DD} = 5 V \pm 10\%$                                                      |                       | 0.0002 | 0.001    | %/%    |

| ,                                           | PSS                      | $V_{DD} = 3 V \pm 10\%$                                                      |                       | 0.006  | 0.03     | %/%    |

| Parameter Symbol                         |                  | Conditions                                                                        | Min | Typ <sup>1</sup> | Max | Unit   |

|------------------------------------------|------------------|-----------------------------------------------------------------------------------|-----|------------------|-----|--------|

| DYNAMIC CHARACTERISTICS <sup>6, 10</sup> |                  |                                                                                   |     |                  |     |        |

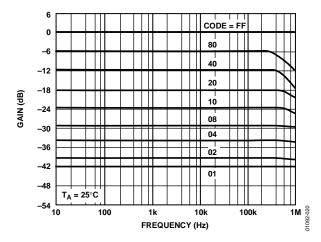

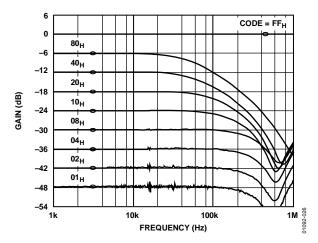

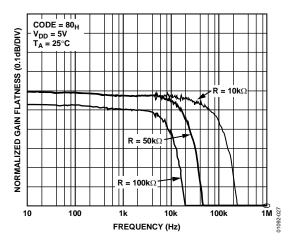

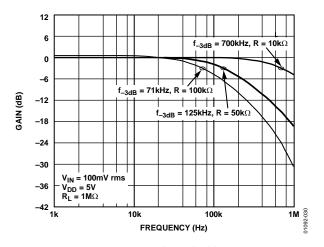

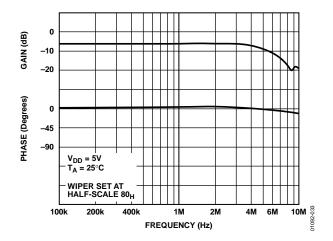

| Bandwidth –3 dB                          | BW_10 K          | $R = 10 \text{ k}\Omega$                                                          |     | 600              |     | kHz    |

| <b>Total Harmonic Distortion</b>         | THDw             | $V_A = 1 \text{ V rms} + 2 \text{ V dc}, V_B = 2 \text{ V dc}, f = 1 \text{ kHz}$ |     | 0.003            |     | %      |

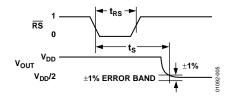

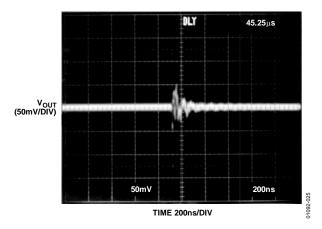

| V <sub>w</sub> Settling Time             | ts               | $V_A = V_{DD}$ , $V_B = 0$ V, $\pm 1\%$ error band                                |     | 2                |     | μs     |

| Resistor Noise Voltage                   | e <sub>NWB</sub> | $R_{WB} = 5 \text{ k}\Omega, f = 1 \text{ kHz}, \overline{RS} = 0$                |     | 9                |     | nV/√Hz |

| Crosstalk <sup>11</sup>                  | C <sub>T</sub>   | $V_A = V_{DD}, V_B = 0 V 		 -65$                                                  |     |                  | dB  |        |

<sup>&</sup>lt;sup>1</sup> Typical represents average readings at 25°C and  $V_{DD} = 5 \text{ V}$ .

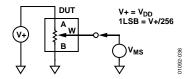

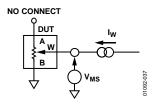

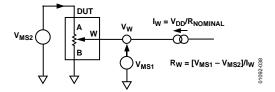

<sup>&</sup>lt;sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See the test circuit in Figure 38.  $I_W = 50 \mu A$  for  $V_{DD} = 3$  V and  $I_W = 400 \mu A$  for  $V_{DD} = 5$  V for the 10 kΩ versions.

$<sup>^3</sup>$   $V_{AB} = \dot{V_{DD}}$  , wiper (Vw) = no connect.

<sup>&</sup>lt;sup>4</sup> INL and DNL are measured at  $V_W$  with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions. See the test circuit in Figure 37.

<sup>&</sup>lt;sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

<sup>&</sup>lt;sup>7</sup> Measured at the Ax terminals. All Ax terminals are open-circuited in shutdown mode.

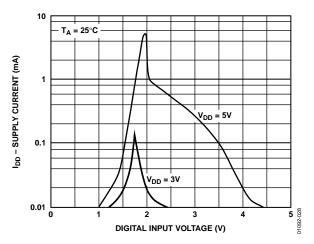

<sup>8</sup> Worst-case supply current is consumed when the input logic level is at 2.4 V, a standard characteristic of CMOS logic. See Figure 28 for a plot of IDD vs. logic voltage.

$<sup>^9</sup>$  P<sub>DISS</sub> is calculated from (I<sub>DD</sub>  $\times$  V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

<sup>&</sup>lt;sup>10</sup> All dynamic characteristics use  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>11</sup> Measured at a V<sub>W</sub> pin where an adjacent V<sub>W</sub> pin is making a full-scale voltage change.

#### ELECTRICAL CHARACTERISTICS—50 K $\Omega$ AND 100 K $\Omega$ VERSIONS

$V_{DD} = 3~V~\pm~10\%~or~5~V~\pm~10\%, V_{A} = V_{DD}, V_{B} = 0~V, -40°C \leq T_{A} \leq +125°C, unless~otherwise~noted.$

Table 2.

| Parameter                                                          | Symbol                                           | Conditions                                                                   | Min                   | Typ <sup>1</sup> | Max      | Unit   |

|--------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------|-----------------------|------------------|----------|--------|

| DC CHARACTERISTICS RHEOSTAT MODE (Specifications Apply to All VRs) |                                                  | tions Apply to All VRs)                                                      |                       |                  |          |        |

| Resistor Differential NL <sup>2</sup>                              | R-DNL                                            | $R_{WB}$ , $V_A = No$ Connect                                                | -1                    | ±1/4             | +1       | LSB    |

| Resistor Nonlinearity <sup>2</sup>                                 | R-INL                                            | $R_{WB}$ , $V_A = No$ Connect                                                | -2                    | ±1/2             | +2       | LSB    |

| Nominal Resistance <sup>3</sup>                                    | R <sub>AB</sub>                                  | T <sub>A</sub> = 25°C, Model: AD840XYY50                                     | 35                    | 50               | 65       | kΩ     |

|                                                                    | R <sub>AB</sub>                                  | T <sub>A</sub> = 25°C, Model: AD840XYY100                                    | 70                    | 100              | 130      | kΩ     |

| Resistance Tempco                                                  | $\Delta R_{AB}/\Delta T$                         | $V_{AB} = V_{DD}$ , Wiper = No Connect                                       |                       | 500              |          | ppm/°C |

| Wiper Resistance                                                   | Rw                                               | $V_{DD} = 5V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 50               | 100      | Ω      |

|                                                                    | Rw                                               | $V_{DD} = 3V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 200              |          | Ω      |

| Nominal Resistance Match                                           | $\Delta R/R_{AB}$                                | CH 1 to CH 2, CH 3, or CH 4, $V_{AB} = V_{DD}$ , $T_A = 25^{\circ}C$         |                       | 0.2              | 1        | %      |

| DC CHARACTERISTICS POTENTION                                       | METER DIVIDER (                                  | Specifications Apply to All VRs)                                             |                       |                  |          |        |

| Resolution                                                         | N                                                |                                                                              | 8                     |                  |          | Bits   |

| Integral Nonlinearity <sup>4</sup>                                 | INL                                              |                                                                              | -4                    | ±1               | +4       | LSB    |

| Differential Nonlinearity <sup>4</sup>                             | DNL                                              | $V_{DD} = 5 V$                                                               | -1                    | ±1/4             | +1       | LSB    |

|                                                                    | DNL                                              | $V_{DD} = 3 \text{ V, } T_A = 25^{\circ}\text{C}$                            | -1                    | ±1/4             | +1       | LSB    |

|                                                                    | DNL                                              | $V_{DD} = 3 \text{ V, } T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$   | -1.5                  | ±1/2             | +1.5     | LSB    |

| Voltage Divider Tempco                                             | $\Delta V_{w}/\Delta T$                          | Code = 80 <sub>H</sub>                                                       |                       | 15               |          | ppm/°C |

| Full-Scale Error                                                   | $V_{WFSE}$                                       | Code = FF <sub>H</sub>                                                       | -1                    | -0.25            | 0        | LSB    |

| Zero-Scale Error                                                   | V <sub>wzse</sub>                                | Code = 00 <sub>H</sub>                                                       | 0                     | +0.1             | +1       | LSB    |

| RESISTOR TERMINALS                                                 |                                                  |                                                                              |                       |                  |          |        |

| Voltage Range⁵                                                     | V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> |                                                                              | 0                     |                  | $V_{DD}$ | V      |

| Capacitance <sup>6</sup> Ax, Bx                                    | C <sub>A</sub> , C <sub>B</sub>                  | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 15               |          | рF     |

| Capacitance <sup>6</sup> Wx                                        | Cw                                               | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 80               |          | pF     |

| Shutdown Current <sup>7</sup>                                      | I <sub>A_SD</sub>                                | $V_A = V_{DD}$ , $V_B = 0$ V, $\overline{SHDN} = 0$                          |                       | 0.01             | 5        | μA     |

| Shutdown Wiper Resistance                                          | R <sub>W_SD</sub>                                | $V_A = V_{DD}, V_B = 0 \text{ V}, \overline{SHDN} = 0, V_{DD} = 5 \text{ V}$ |                       | 100              | 200      | Ω      |

| DIGITAL INPUTS AND OUTPUTS                                         |                                                  | , , , , , , , , , , , , , , , , , , , ,                                      |                       |                  |          |        |

| Input Logic High                                                   | VIH                                              | $V_{DD} = 5 V$                                                               | 2.4                   |                  |          | V      |

| Input Logic Low                                                    | V <sub>IL</sub>                                  | $V_{DD} = 5 \text{ V}$                                                       |                       |                  | 0.8      | V      |

| Input Logic High                                                   | VIH                                              | $V_{DD} = 3 V$                                                               | 2.1                   |                  |          | V      |

| Input Logic Low                                                    | VIL                                              | $V_{DD} = 3 V$                                                               |                       |                  | 0.6      | V      |

| Output Logic High                                                  | V <sub>OH</sub>                                  | $R_L = 2.2 \text{ k}\Omega \text{ to } V_{DD}$                               | V <sub>DD</sub> - 0.1 |                  |          | V      |

| Output Logic Low                                                   | Vol                                              | $I_{OL} = 1.6 \text{ mA}, V_{DD} = 5 \text{ V}$                              |                       |                  | 0.4      | V      |

| Input Current                                                      | I <sub>IL</sub>                                  | $V_{IN} = 0 \text{ V or } 5 \text{ V}, V_{DD} = 5 \text{ V}$                 |                       |                  | ±1       | μΑ     |

| Input Capacitance <sup>6</sup>                                     | C <sub>IL</sub>                                  | ,                                                                            |                       | 5                |          | pF     |

| POWER SUPPLIES                                                     |                                                  |                                                                              |                       |                  |          | i      |

| Power Supply Range                                                 | V <sub>DD</sub> range                            |                                                                              | 2.7                   |                  | 5.5      | ٧      |

| Supply Current (CMOS)                                              | I <sub>DD</sub>                                  | $V_{IH} = V_{DD}$ or $V_{IL} = 0$ V                                          |                       | 0.01             | 5        | μA     |

| Supply Current (TTL) <sup>8</sup>                                  | I <sub>DD</sub>                                  | $V_{IH} = 2.4 \text{ V or } 0.8 \text{ V}, V_{DD} = 5.5 \text{ V}$           |                       | 0.9              | 4        | mA     |

| Power Dissipation (CMOS) <sup>9</sup>                              | P <sub>DISS</sub>                                | $V_{IH} = V_{DD}$ or $V_{IL} = 0$ V, $V_{DD} = 5.5$ V                        |                       |                  | 27.5     | μW     |

| Power Supply Sensitivity                                           | PSS                                              | $V_{DD} = 5 V \pm 10\%$                                                      |                       | 0.0002           | 0.001    | %/%    |

| 11,7                                                               | PSS                                              | $V_{DD} = 3 V \pm 10\%$                                                      |                       | 0.006            | 0.03     | %/%    |

| Parameter                                | Symbol                  | Conditions                                                                        | Min | Typ <sup>1</sup> | Max | Unit   |

|------------------------------------------|-------------------------|-----------------------------------------------------------------------------------|-----|------------------|-----|--------|

| DYNAMIC CHARACTERISTICS <sup>6, 10</sup> |                         |                                                                                   |     |                  |     |        |

| Bandwidth –3 dB                          | BW_50 K                 | $R = 50 \text{ k}\Omega$                                                          |     | 125              |     | kHz    |

|                                          | BW_100 K                | $R = 100 \text{ k}\Omega$                                                         |     | 71               |     | kHz    |

| <b>Total Harmonic Distortion</b>         | THDw                    | $V_A = 1 \text{ V rms} + 2 \text{ V dc}, V_B = 2 \text{ V dc}, f = 1 \text{ kHz}$ |     | 0.003            |     | %      |

| V <sub>w</sub> Settling Time             | ts_50 K                 | $V_A = V_{DD}$ , $V_B = 0$ V, $\pm 1\%$ error band                                |     | 9                |     | μs     |

|                                          | ts_100 K                | $V_A = V_{DD}$ , $V_B = 0$ V, $\pm 1\%$ error band                                |     | 18               |     | μs     |

| Resistor Noise Voltage                   | е <sub>NWB</sub> _50 К  | $R_{WB} = 25 \text{ k}\Omega$ , $f = 1 \text{ kHz}$ , $\overline{RS} = 0$         |     | 20               |     | nV/√Hz |

|                                          | е <sub>NWB</sub> _100 К | $R_{WB} = 50 \text{ k}\Omega, f = 1 \text{ kHz}, \overline{RS} = 0$               |     | 29               |     | nV/√Hz |

| Crosstalk <sup>11</sup>                  | Ст                      | $V_A = V_{DD}, V_B = 0 V$                                                         |     | -65              |     | dB     |

<sup>&</sup>lt;sup>1</sup> Typicals represent average readings at 25°C and  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See the test circuit in Figure 38.  $I_W = V_{DD}/R$  for  $V_{DD} = 3$  V or 5 V for the 50 k $\Omega$  and 100 k $\Omega$  versions.

$<sup>^{3}</sup>$   $V_{AB} = V_{DD}$ , wiper  $(V_{W}) = no$  connect.

$<sup>^4</sup>$  INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions. See the test circuit in Figure 37.

<sup>&</sup>lt;sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

Measured at the Ax terminals. All Ax terminals are open-circuited in shutdown mode.

Worst-case supply current consumed when input logic level at 2.4 V, standard characteristic of CMOS logic. See Figure 28 for a plot of I<sub>DD</sub> vs. logic voltage.

$<sup>^9</sup>$  P<sub>DISS</sub> is calculated from ( $I_{DD} \times V_{DD}$ ). CMOS logic level inputs result in minimum power dissipation.

<sup>&</sup>lt;sup>10</sup> All dynamic characteristics use  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>11</sup> Measured at a V<sub>W</sub> pin where an adjacent V<sub>W</sub> pin is making a full-scale voltage change.

#### **ELECTRICAL CHARACTERISTICS—1 KΩ VERSION**

$V_{DD} = 3~V~\pm~10\%~or~5~V~\pm~10\%, V_{A} = V_{DD}, V_{B} = 0~V, -40°C \leq T_{A} \leq +125°C, unless~otherwise~noted.$

Table 3.

| Parameter                               | Symbol                          | Conditions                                                                   | Min                   | Typ <sup>1</sup> | Max      | Unit   |

|-----------------------------------------|---------------------------------|------------------------------------------------------------------------------|-----------------------|------------------|----------|--------|

| DC CHARACTERISTICS RHEOSTAT MODE (Sp    | ecifications <i>P</i>           | Apply to All VRs)                                                            |                       |                  |          |        |

| Resistor Differential NL <sup>2</sup>   | R-DNL                           | $R_{WB}$ , $V_A = no connect$                                                | -5                    | -1               | +3       | LSB    |

| Resistor Nonlinearity <sup>2</sup>      | R-INL                           | $R_{WB}$ , $V_A$ = no connect                                                | -4                    | ±1.5             | +4       | LSB    |

| Nominal Resistance <sup>3</sup>         | R <sub>AB</sub>                 | T <sub>A</sub> = 25°C, model: AD840XYY1                                      | 0.8                   | 1.2              | 1.6      | kΩ     |

| Resistance Tempco                       | $\Delta R_{AB}/\Delta T$        | $V_{AB} = V_{DD}$ , wiper = no connect                                       |                       | 700              |          | ppm/°C |

| Wiper Resistance                        | Rw                              | $V_{DD} = 5V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 53               | 100      | Ω      |

|                                         | Rw                              | $V_{DD} = 3V$ , $I_W = V_{DD}/R_{AB}$                                        |                       | 200              |          | Ω      |

| Nominal Resistance Match                | $\Delta R/R_{AB}$               | CH 1 to CH 2, $V_{AB} = V_{DD}$ , $T_A = 25^{\circ}C$                        |                       | 0.75             | 2        | %      |

| DC CHARACTERISTICS POTENTIOMETER DIV    | IDER (Specifi                   | cations Apply to All VRs)                                                    |                       |                  |          |        |

| Resolution                              | N                               |                                                                              | 8                     |                  |          | Bits   |

| Integral Nonlinearity <sup>4</sup>      | INL                             |                                                                              | -6                    | ±2               | +6       | LSB    |

| Differential Nonlinearity <sup>4</sup>  | DNL                             | $V_{DD} = 5 V$                                                               | -4                    | -1.5             | +2       | LSB    |

| ·                                       | DNL                             | $V_{DD} = 3 \text{ V, } T_A = 25^{\circ}\text{C}$                            | -5                    | -2               | +5       | LSB    |

| Voltage Divider Temperature Coefficient | $\Delta V_W/\Delta T$           | Code = 80H                                                                   |                       | 25               |          | ppm/°C |

| Full-Scale Error                        | $V_{WFSE}$                      | Code = FF <sub>H</sub>                                                       | -20                   | -12              | 0        | LSB    |

| Zero-Scale Error                        | V <sub>WZSE</sub>               | Code = 00 <sub>H</sub>                                                       | 0                     | 6                | 10       | LSB    |

| RESISTOR TERMINALS                      |                                 |                                                                              |                       |                  |          |        |

| Voltage Range⁵                          | $V_A, V_B, V_W$                 |                                                                              | 0                     |                  | $V_{DD}$ | V      |

| Capacitance <sup>6</sup> Ax, Bx         | C <sub>A</sub> , C <sub>B</sub> | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 75               |          | рF     |

| Capacitance <sup>6</sup> Wx             | Cw                              | $f = 1$ MHz, measured to GND, code = $80_H$                                  |                       | 120              |          | pF     |

| Shutdown Supply Current <sup>7</sup>    | I <sub>A_SD</sub>               | $V_A = V_{DD}$ , $V_B = 0$ V, $\overline{SHDN} = 0$                          |                       | 0.01             | 5        | μA     |

| Shutdown Wiper Resistance               | R <sub>W_SD</sub>               | $V_A = V_{DD}, V_B = 0 \text{ V}, \overline{SHDN} = 0, V_{DD} = 5 \text{ V}$ |                       | 50               | 100      | Ω      |

| DIGITAL INPUTS AND OUTPUTS              |                                 |                                                                              |                       |                  |          |        |

| Input Logic High                        | V <sub>IH</sub>                 | $V_{DD} = 5 \text{ V}$                                                       | 2.4                   |                  |          | V      |

| Input Logic Low                         | V <sub>IL</sub>                 | $V_{DD} = 5 \text{ V}$                                                       |                       |                  | 0.8      | V      |

| Input Logic High                        | V <sub>IH</sub>                 | $V_{DD} = 3 \text{ V}$                                                       | 2.1                   |                  |          | V      |

| Input Logic Low                         | V <sub>IL</sub>                 | $V_{DD} = 3 \text{ V}$                                                       |                       |                  | 0.6      | V      |

| Output Logic High                       | V <sub>OH</sub>                 | $R_L = 2.2 \text{ k}\Omega \text{ to } V_{DD}$                               | V <sub>DD</sub> – 0.1 |                  |          | V      |

| Output Logic Low                        | V <sub>OL</sub>                 | $I_{OL} = 1.6 \text{ mA}, V_{DD} = 5 \text{ V}$                              |                       |                  | 0.4      | V      |

| Input Current                           | I <sub>IL</sub>                 | $V_{IN} = 0 \text{ V or } 5 \text{ V, } V_{DD} = 5 \text{ V}$                |                       |                  | ±1       | μΑ     |

| Input Capacitance <sup>6</sup>          | C <sub>IL</sub>                 |                                                                              |                       | 5                |          | pF     |

| POWER SUPPLIES                          |                                 |                                                                              |                       |                  |          |        |

| Power Supply Range                      | V <sub>DD</sub> range           |                                                                              | 2.7                   |                  | 5.5      | V      |

| Supply Current (CMOS)                   | I <sub>DD</sub>                 | $V_{IH} = V_{DD}$ or $V_{IL} = 0$ V                                          |                       | 0.01             | 5        | μΑ     |

| Supply Current (TTL) <sup>8</sup>       | I <sub>DD</sub>                 | $V_{IH} = 2.4 \text{ V or } 0.8 \text{ V}, V_{DD} = 5.5 \text{ V}$           |                       | 0.9              | 4        | mA     |

| Power Dissipation (CMOS) <sup>9</sup>   | P <sub>DISS</sub>               | $V_{IH} = V_{DD}$ or $V_{IL} = 0$ V, $V_{DD} = 5.5$ V                        |                       |                  | 27.5     | μW     |

| Power Supply Sensitivity                | PSS                             | $\Delta V_{DD} = 5 \text{ V} \pm 10\%$                                       |                       | 0.0035           | 0.008    | %/%    |

|                                         | PSS                             | $\Delta V_{DD} = 3 V \pm 10\%$                                               |                       | 0.05             | 0.13     | %/%    |

| Parameter                                | Symbol | Conditions                                                                        | Min | Typ <sup>1</sup> | Max | Unit   |

|------------------------------------------|--------|-----------------------------------------------------------------------------------|-----|------------------|-----|--------|

| DYNAMIC CHARACTERISTICS <sup>6, 10</sup> |        |                                                                                   |     |                  |     |        |

| Bandwidth –3 dB                          | BW_1 K | $R = 1 k\Omega$                                                                   |     | 5,000            |     | kHz    |

| Total Harmonic Distortion                | THDw   | $V_A = 1 \text{ V rms} + 2 \text{ V dc}, V_B = 2 \text{ V dc}, f = 1 \text{ kHz}$ |     | 0.015            |     | %      |

| V <sub>W</sub> Settling Time             | ts     | $V_A = V_{DD}$ , $V_B = 0$ V, $\pm 1\%$ error band                                |     | 0.5              |     | μs     |

| Resistor Noise Voltage e <sub>NWB</sub>  |        | $R_{WB} = 500 \Omega$ , $f = 1 \text{ kHz}$ , $\overline{RS} = 0$                 |     | 3                |     | nV/√Hz |

| Crosstalk <sup>11</sup>                  | Ст     | $V_A = V_{DD}$ , $V_B = 0$ V                                                      |     | -65              |     | dB     |

<sup>&</sup>lt;sup>1</sup> Typicals represent average readings at 25°C and  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. See the test circuit in Figure 38.  $I_W = 500 \mu A$  for  $V_{DD} = 3 V$  and  $I_W = 2.5 mA$  for  $V_{DD} = 5 V$  for 1 kΩ version.

$<sup>^3</sup>$   $V_{AB} = V_{DD}$ , wiper  $(V_W) = no$  connect.

<sup>&</sup>lt;sup>4</sup> INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions. See the test circuit in Figure 37.

<sup>&</sup>lt;sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

<sup>&</sup>lt;sup>7</sup> Measured at the Ax terminals. All Ax terminals are open-circuited in shutdown mode.

<sup>&</sup>lt;sup>8</sup> Worst-case supply current is consumed when the input logic level is at 2.4 V, a standard characteristic of CMOS logic. See Figure 28 for a plot of I<sub>DD</sub> vs. logic voltage.

$<sup>^9</sup>$  P<sub>DISS</sub> is calculated from (I<sub>DD</sub> × V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

<sup>&</sup>lt;sup>10</sup> All dynamic characteristics use  $V_{DD} = 5 \text{ V}$ .

<sup>&</sup>lt;sup>11</sup> Measured at a V<sub>W</sub> pin where an adjacent V<sub>W</sub> pin is making a full-scale voltage change.

#### **ELECTRICAL CHARACTERISTICS—ALL VERSIONS**

$V_{\rm DD} = 3 \ V \pm 10\%$  or  $5 \ V \pm 10\%$ ,  $V_{\rm A} = V_{\rm DD}$ ,  $V_{\rm B} = 0 \ V$ ,  $-40^{\circ} C \le T_{\rm A} \le +125^{\circ} C$ , unless otherwise noted.

#### Table 4.

| Parameter                                  | Symbol                            | Conditions                                                        | Min | Typ <sup>1</sup> | Max | Unit |

|--------------------------------------------|-----------------------------------|-------------------------------------------------------------------|-----|------------------|-----|------|

| SWITCHING CHARACTERISTICS <sup>2, 3</sup>  |                                   |                                                                   |     |                  |     |      |

| Input Clock Pulse Width                    | t <sub>CH</sub> , t <sub>CL</sub> | Clock level high or low                                           | 10  |                  |     | ns   |

| Data Setup Time                            | t <sub>DS</sub>                   |                                                                   | 5   |                  |     | ns   |

| Data Hold Time                             | t <sub>DH</sub>                   |                                                                   | 5   |                  |     | ns   |

| CLK to SDO Propagation Delay⁴              | t <sub>PD</sub>                   | $R_L = 1 \text{ k}\Omega \text{ to 5 V, } C_L \leq 20 \text{ pF}$ | 1   |                  | 25  | ns   |

| CS Setup Time                              | t <sub>CSS</sub>                  |                                                                   | 10  |                  |     | ns   |

| CS High Pulse Width                        | t <sub>CSW</sub>                  |                                                                   | 10  |                  |     | ns   |

| Reset Pulse Width                          | t <sub>RS</sub>                   |                                                                   | 50  |                  |     | ns   |

| CLK Fall to $\overline{CS}$ Rise Hold Time | t <sub>CSH</sub>                  |                                                                   | 0   |                  |     | ns   |

| CS Rise to Clock Rise Setup                | t <sub>CS1</sub>                  |                                                                   | 10  |                  |     | ns   |

$<sup>^{1}</sup>$  Typicals represent average readings at 25°C and  $V_{DD} = 5 \text{ V}$ .

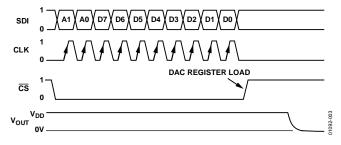

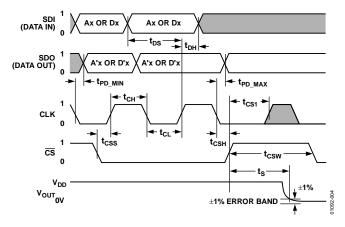

#### **TIMING DIAGRAMS**

Figure 3. Timing Diagram

Figure 5. Reset Timing Diagram

Figure 4. Detailed Timing Diagram

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

<sup>&</sup>lt;sup>3</sup> See the timing diagram in Figure 3 for location of measured values. All input control voltages are specified with  $t_R = t_F = 1$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V. Switching characteristics are measured using  $V_{DD} = 3$  V or 5 V. To avoid false clocking, a minimum input logic slew rate of 1 V/µs should be maintained.

$<sup>^4</sup>$  Propagation delay depends on the value of  $V_{DD}$ ,  $R_L$ , and  $C_L$  (see the Applications section).

#### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| ParameterRating $V_{DD}$ to GND $-0.3 \text{ V}, +8 \text{ V}$ $V_A$ , $V_B$ , $V_W$ to GND $0 \text{ V}$ , $V_{DD}$ Maximum Current $1_{WB}$ , $1_{WB}$ , $1_{WB}$ Pulsed $\pm 20 \text{ mA}$ $1_{WB}$ Continuous $(R_{WB} \le 1 \text{ k}\Omega, A \text{ Open})^1$ $\pm 5 \text{ mA}$ $1_{WA}$ Continuous $(R_{WB} \le 1 \text{ k}\Omega/10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega)^1$ $\pm 5 \text{ mA}$ $1_{AB}$ Continuous $(R_{AB} = 1 \text{ k}\Omega/10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega)^1$ $\pm 5 \text{ 40} \text{ mA}/±2.1 \text{ mA}/5.00 \text{ mA}/±5.40 \text{ mA}/±5.40 \text{ mA}/±5.40 \text{ mA}/5.40 \text{ mA}/±5.40 \text{ mA}/±5.40 \text{ mA}/5.40  $                                                                                                                                                                                                                                                                                                                             | 1 able 5.                                                                   |                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|

| $V_{A}, V_{B}, V_{W} \text{ to GND} \\ \text{Maximum Current} \\ I_{WB}, I_{WA} \text{ Pulsed} \\ I_{WB} \text{ Continuous } (R_{WB} \leq 1 \text{ k}\Omega, \text{ A Open})^1 \\ I_{WA} \text{ Continuous } (R_{WB} \leq 1 \text{ k}\Omega, \text{ B Open})^1 \\ I_{AB} \text{ Continuous } (R_{AB} = 1 \text{ k}\Omega/10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega)^1 \\ \text{Digital Input and Output Voltage} \\ \text{to GND} \\ \text{Operating Temperature Range} \\ \text{Maximum Junction Temperature} \\ (T_{J} \text{ Maximum}) \\ \text{Storage Temperature} \\ \text{Lead Temperature (Soldering, 10 sec)} \\ \text{Package Power Dissipation} \\ \text{Thermal Resistance } (\theta_{JA}) \\ \text{SOIC } (R-8) \\ \text{PDIP } (N-14) \\ \text{PDIP } (N-24) \\ \text{SOIC } (R-24) \\ \text{TSSOP-14 } (\text{RU-14}) \\ \text{O V, } V_{DD} \\ \text{$\pm 20 \text{ mA}} \\ \pm 2.1 \text{ mA} / \pm 2.1 \text{ mA} / \pm 2.1 \text{ mA} / \pm 540 \text{ µA} / \pm 2.1 \text{ mA} / \pm 2.1 \text{ mA}$ | Parameter                                                                   | Rating                                                 |

| Maximum Current $I_{WB}, I_{WA} \text{ Pulsed}$ $I_{WB} \text{ Continuous } (R_{WB} \le 1 \text{ k}\Omega, \text{ A Open})^1$ $I_{WA} \text{ Continuous } (R_{WA} \le 1 \text{ k}\Omega, \text{ B Open})^1$ $I_{AB} \text{ Continuous } (R_{AB} = 1 \text{ k}\Omega/10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega)^1$ $Digital \text{ Input and Output Voltage to GND}$ $Operating \text{ Temperature Range}$ $Maximum \text{ Junction Temperature } (T_J \text{ Maximum})$ $Storage \text{ Temperature } (Soldering, 10 \text{ sec})$ $Package \text{ Power Dissipation}$ $Thermal \text{ Resistance } (\theta_{JA})$ $SOIC (R-8)$ $PDIP (N-14)$ $PDIP (N-24)$ $SOIC (R-24)$ $TSSOP-14 (RU-14)$ $120^{\circ}C/W$ $180^{\circ}C/W$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>DD</sub> to GND                                                      | -0.3 V, +8 V                                           |

| $ _{WB},  _{WA} \text{ Pulsed} $ $ _{WB} \text{ Continuous } (R_{WB} \le 1 \text{ k}\Omega, \text{ A Open})^1$ $ _{WA} \text{ Continuous } (R_{WA} \le 1 \text{ k}\Omega, \text{ B Open})^1$ $ _{AB} \text{ Continuous } (R_{AB} = 1 \text{ k}\Omega/10 \text{ k}\Omega/50 \text{ k}\Omega/100 \text{ k}\Omega)^1$ $ _{Digital } \text{ Input and Output Voltage to GND}$ Operating Temperature Range  Maximum Junction Temperature (T <sub>J</sub> Maximum)  Storage Temperature (Soldering, 10 sec) Package Power Dissipation  Thermal Resistance (θ <sub>JA</sub> )  SOIC (R-8) PDIP (N-14) PDIP (N-24) SOIC (R-14) SOIC (R-24) TSSOP-14 (RU-14) $ _{DDIP} \text{ Continuous } (R_{WB} \le 1 \text{ k}\Omega, \text{ A Open})^1$ ±5 mA ±2.1 mA/±2.1 mA/ ±540 μA/±540 μA  0 V, 7 V  150°C 150°C 150°C (T <sub>J</sub> max − T <sub>A</sub> )/θ <sub>JA</sub> 158°C/W 158°C/W 158°C/W 120°C/W 120°C/W 180°C/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $V_A$ , $V_B$ , $V_W$ to GND                                                | 0 V, V <sub>DD</sub>                                   |

| $  _{WB} Continuous (R_{WB} ≤ 1 kΩ, A Open)^1   _{WA} Continuous (R_{WA} ≤ 1 kΩ, B Open)^1   _{I_{AB}} Continuous (R_{AB} = 1 kΩ/10 kΩ/ 50 kΩ/100 kΩ)^1   _{Digital Input and Output Voltage to GND                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Maximum Current                                                             |                                                        |

| $ I_{WA} Continuous (R_{WA} ≤ 1 kΩ, B Open)^1  I_{AB} Continuous (R_{AB} = 1 kΩ/10 kΩ/ 50 kΩ/100 kΩ)^1  Digital Input and Output Voltage to GND  Operating Temperature Range  Maximum Junction Temperature  (TJ Maximum)  Storage Temperature  Lead Temperature (Soldering, 10 sec)  Package Power Dissipation  Thermal Resistance (θJA)  SOIC (R-8)  PDIP (N-14)  PDIP (N-24)  SOIC (R-24)  SOIC (R-24)  TSSOP-14 (RU-14)   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Iwb, Iwa Pulsed                                                             | ±20 mA                                                 |

| I <sub>AB</sub> Continuous (R <sub>AB</sub> = 1 kΩ/10 kΩ/ $_{50}$ kΩ/100 kΩ) <sup>1</sup> ±2.1 mA/±2.1 mA/ $_{\pm}$ 540 μA/±540 μA 0 V, 7 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $I_{WB}$ Continuous ( $R_{WB} \le 1 \text{ k}\Omega$ , A Open) <sup>1</sup> | ±5 mA                                                  |

| 50 kΩ/100 kΩ)¹ $\pm 540  \mu A/\pm 540  \mu A$ Digital Input and Output Voltage<br>to GND0 V, 7 VOperating Temperature Range $-40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ Maximum Junction Temperature<br>(TJ Maximum) $150^{\circ}\text{C}$ Storage Temperature $-65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ Lead Temperature (Soldering, 10 sec) $300^{\circ}\text{C}$ Package Power Dissipation $(T_J \max - T_A)/\theta_{JA}$ Thermal Resistance $(\theta_{JA})$ $158^{\circ}\text{C/W}$ SOIC (R-8) $158^{\circ}\text{C/W}$ PDIP (N-14) $83^{\circ}\text{C/W}$ PDIP (N-24) $63^{\circ}\text{C/W}$ SOIC (R-14) $120^{\circ}\text{C/W}$ SOIC (R-24) $70^{\circ}\text{C/W}$ TSSOP-14 (RU-14) $180^{\circ}\text{C/W}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $I_{WA}$ Continuous ( $R_{WA} \le 1 \text{ k}\Omega$ , B Open) <sup>1</sup> | ±5 mA                                                  |

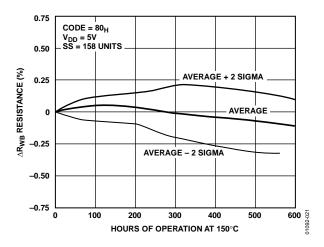

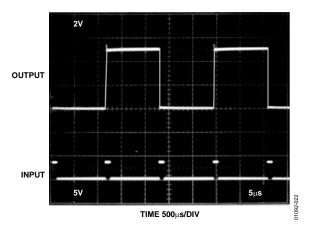

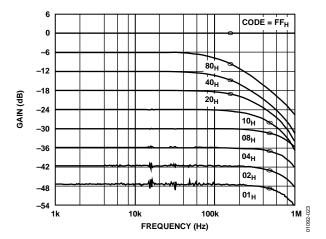

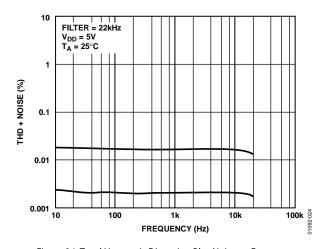

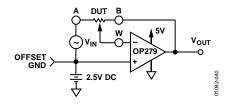

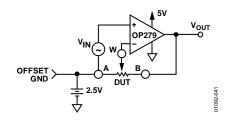

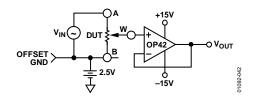

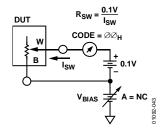

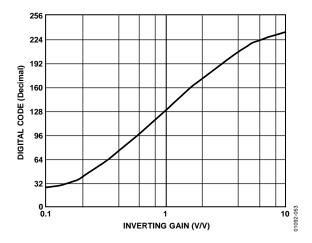

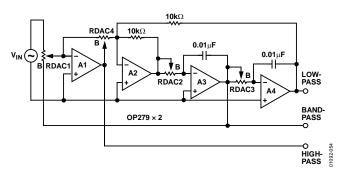

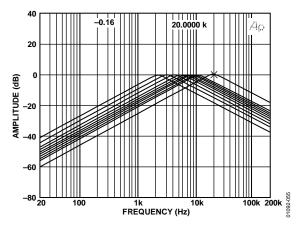

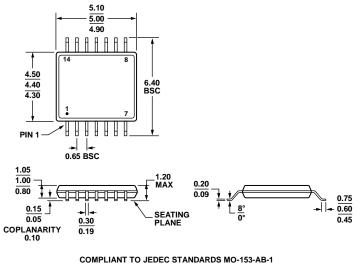

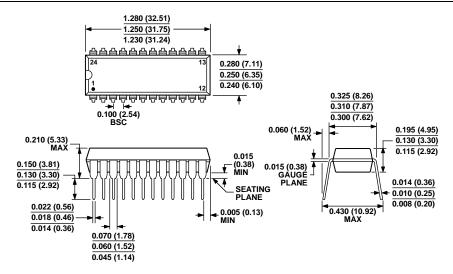

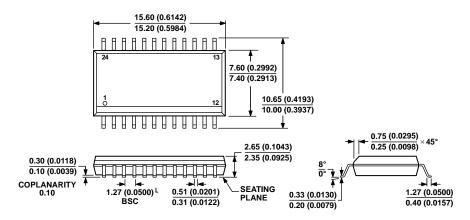

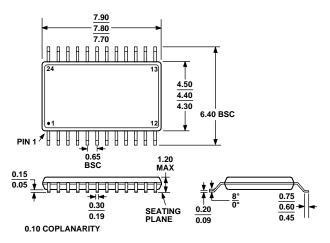

| to GND  Operating Temperature Range  Maximum Junction Temperature (T <sub>J</sub> Maximum)  Storage Temperature  Lead Temperature (Soldering, 10 sec)  Package Power Dissipation  Thermal Resistance (θ <sub>JA</sub> )  SOIC (R-8)  PDIP (N-14)  PDIP (N-24)  SOIC (R-14)  SOIC (R-24)  TSSOP-14 (RU-14)  150°C to +125°C  300°C  (T <sub>J</sub> max – T <sub>A</sub> )/θ <sub>JA</sub> 158°C/W  83°C/W  63°C/W  120°C/W  70°C/W  180°C/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                             | ==, ==,                                                |