### **FEATURES**

- Single-chip CardBus host adapter

- Direct connection to PCI bus and two PC Card sockets

- Compliant with PCI 2.1, PCMCIA 2.1, PC Card Standard, and JEIDA 4.1

- CL-PD672X—compatible register set, ExCA<sup>TM</sup>-compatible

- Programmable interrupt protocol: External Hardware, PCI/Way, PCI, or PC/PCI interrupt signalling modes

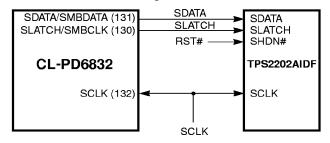

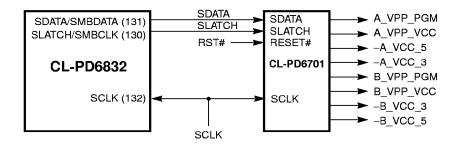

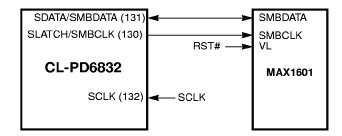

- Serial interface to power-control devices

- Hardware suspend capability

- Seven fully programmable memory or I/O windows per socket

- Programmable CardBus timing (up to 33 MHz)

- Support for PCI/Way DMA (distributed DMA)

- ZV Port support for multimedia applications

- ATA disk interface support

- Supports low-voltage PC Card specification

- Socket-to-socket transfer (bus master) capability

- Programmable per-socket activity indicators

- Pin-compatible with the CL-PD6730

# PCI-to-CardBus Host Adapter

### **OVERVIEW**

The CL-PD6832 is a single-chip CardBus host adapter solution capable of controlling two fully independent CardBus sockets. It is compliant with PCI 2.1, PCMCIA 2.1, PC Card Standard, and JEIDA 4.1. The CL-PD6832 is optimized for use in notebook and handheld computers where reduced form factor and low power consumption are critical design objectives.

To minimize system power consumption, the CL-PD6832 employs energy-efficient, mixed-voltage technology. The device also provides a Hardware Suspend mode that reduces much of the power consumption.

The CL-PD6832 allows easy translation of incoming memory commands to PC Card 16 I/O commands for processors with memory commands only. It enables these processors to use PC Card I/O devices with fully programmable windows. All CL-PD6832 control registers can either be memory-or I/O-mapped. (cont.)

# PCI BUS PC CARD SOCKET 1 PC CARD SOCKET 2 PC CARD SOCKET 2

Version 1.0 June 1998

# **OVERVIEW** (cont.)

PC applications typically access PC Cards through the socket/card-services software interface. The register set in the CL-PD6832 is a superset of the CL-PD672X register set, assuring full compatibility with existing socket/card-services software and PC Card applications.

The CL-PD6832 provides a fully buffered PC Card interface, requiring no external logic for buffering signals to and from the interface. Power consumption is controlled by limiting signal transitions on the PC CardBus.

### **ADVANTAGES**

2

| Notebook Computer Design Priorities | Supporting Features                                                                                                                |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| ■ Small form factor                 | ☐ Single-chip solution                                                                                                             |

|                                     | <ul> <li>No external buffers for host or socket interfacing</li> </ul>                                                             |

|                                     | ☐ Efficient board layout                                                                                                           |

| ■ Minimum power consumption         | ☐ Hardware suspend capability                                                                                                      |

|                                     | ☐ Mixed-voltage operation                                                                                                          |

| ■ High performance                  | <ul> <li>Programmable timing supports more cards, faster reads and writes</li> </ul>                                               |

|                                     | ☐ Bus mastering on PCI bus                                                                                                         |

| ■ Flexibility                       | <ul> <li>Programmable interrupt protocol: External<br/>Hardware, PCI/Way, PCI, or PC/PCI interrupt<br/>signalling modes</li> </ul> |

|                                     | ☐ Supports serial interface to power control devices                                                                               |

| ■ Compatibility                     | ☐ Compliant with PC Card Standard, PCMCIA 2.1, and JEIDA 4.1                                                                       |

|                                     | ☐ Compliant with PCI 2.1                                                                                                           |

|                                     | <ul> <li>□ CL-PD672X–compatible register set,</li> <li>ExCA™-compatible</li> </ul>                                                 |

ADVANCE DATA SHEET v1.0 June 1998

# **Table of Contents**

| 1. | CO         | NVENTIONS                                                                         | 7  |

|----|------------|-----------------------------------------------------------------------------------|----|

| 2. | PIN        | INFORMATION                                                                       | 9  |

|    | 2.1        | Pin Diagrams                                                                      |    |

|    | 2.2        | Pin Description Conventions                                                       |    |

|    | 2.3        | Pin Descriptions                                                                  |    |

| 3. | INT        | RODUCTION TO THE CL-PD6832                                                        | 25 |

|    | 3.1        | System Architecture                                                               |    |

|    | _          | 3.1.1 PC Card Basics                                                              |    |

|    |            | 3.1.2 CL-PD6832 Windowing Capabilities                                            |    |

|    |            | 3.1.3 Zoomed Video Port                                                           |    |

|    |            | 3.1.4 Interrupts                                                                  |    |

|    |            | 3.1.5 PCI/Way DMA                                                                 |    |

|    |            | 3.1.6 CL-PD6832 Power Management                                                  |    |

|    |            | 3.1.7 Socket Power Management Features                                            |    |

|    |            | 3.1.8 Bus Sizing                                                                  |    |

|    |            | 3.1.9 Programmable PC Card Timing                                                 |    |

|    |            | 3.1.10 ATA Mode Operation                                                         |    |

|    |            | 3.1.11 PC Card Sensing                                                            | 37 |

|    | 3.2        | Host Access to Registers                                                          |    |

|    | 3.3        | Power-On Setup                                                                    | 40 |

| 4. | REC        | SISTER DESCRIPTION CONVENTIONS                                                    | 41 |

| 5. | PCI        | CONFIGURATION REGISTERS                                                           | 43 |

| -  | 5.1        | Vendor ID and Device ID                                                           |    |

|    | 5.2        | Command and Status                                                                | 45 |

|    | 5.3        | Revision ID and Class Code                                                        | 48 |

|    | 5.4        | Cache Line Size, Latency Timer, Header Type, and BIST                             |    |

|    | 5.5        | Memory Base Address                                                               |    |

|    | 5.6        | CardBus Status                                                                    |    |

|    | 5.7        | PCI Bus Number, CardBus Number, Subordinate Bus Number, and CardBus Latency Timer |    |

|    | 5.8<br>5.9 | Memory Limit 0.1                                                                  |    |

|    | 5.10       | Memory Limit 0–1                                                                  |    |

|    | 5.11       | I/O Limit 0–1                                                                     |    |

|    | 5.12       |                                                                                   |    |

|    | 5.13       |                                                                                   |    |

|    | 5.14       | PC Card 16-Bit IF Legacy Mode Base Address                                        |    |

|    | 5.15       | DMA Slave Configuration Register                                                  | 63 |

|    |            | Socket Number                                                                     |    |

| 6. |            | RDBUS REGISTERS                                                                   |    |

|    | 6.1        | Status Event                                                                      |    |

|    | 6.2        | Status Mask                                                                       |    |

|    | 6.3        | Present State                                                                     |    |

|    | 6.4        | Event Force                                                                       |    |

|    | 6.5        | Control                                                                           | /2 |

June 1998

ADVANCE DATA SHEET v1.0

CONTENTS

June 1998

ADVANCE DATA SHEET v1.0

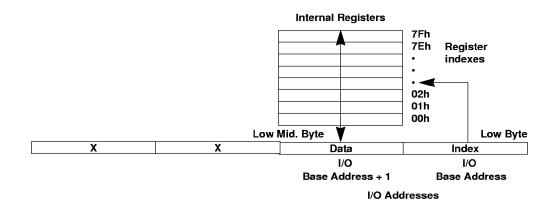

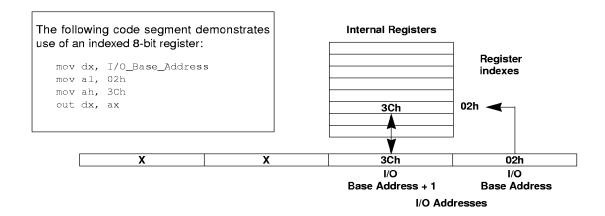

| 7.  | OPE                  | ERATIC                                      | ON REGISTERS                                                               | 75         |

|-----|----------------------|---------------------------------------------|----------------------------------------------------------------------------|------------|

|     | 7.1                  | Index                                       |                                                                            | 75         |

|     | 7.2                  | Data                                        |                                                                            | 80         |

| 8.  | DEV                  | ICE C                                       | ONTROL REGISTERS                                                           | 81         |

|     | 8.1                  |                                             | Revision                                                                   |            |

|     | 8.2                  |                                             | ce Status                                                                  |            |

|     | 8.3                  | Power                                       | Control                                                                    | 84         |

|     | 8.4                  | Interru                                     | pt and General Control                                                     | 86         |

|     | 8.5                  | Card S                                      | Status Change                                                              | 88         |

|     | 8.6                  |                                             | gement Interrupt Configuration                                             |            |

|     | 8.7                  | Mappir                                      | ng Enable                                                                  | 91         |

| 9.  | WIN                  | IDOW I                                      | MAPPING REGISTERS                                                          | 93         |

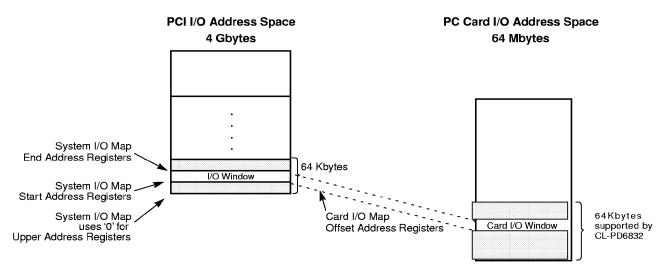

|     | 9.1                  | I/O Wir                                     | ndow Mapping Registers                                                     | 94         |

|     |                      | 9.1.1                                       | I/O Window Control                                                         | 94         |

|     |                      | 9.1.2                                       | System I/O Map 0-1 Start Address Low                                       | 96         |

|     |                      | 9.1.3                                       | System I/O Map 0-1 Start Address High                                      | 96         |

|     |                      | 9.1.4                                       | System I/O Map 0-1 End Address Low                                         | 97         |

|     |                      | 9.1.5                                       | System I/O Map 0-1 End Address High                                        | 97         |

|     |                      | 9.1.6                                       | Card I/O Map 0-1 Offset Address Low                                        | 98         |

|     |                      | 9.1.7                                       | Card I/O Map 0-1 Offset Address High                                       | 98         |

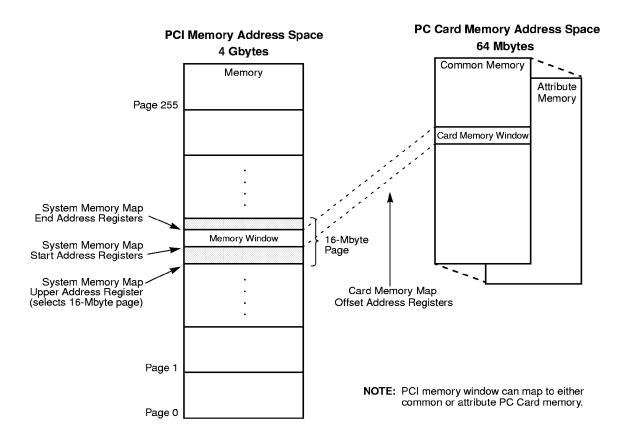

|     | 9.2                  | Memor                                       | ry Window Mapping Registers                                                | 99         |

|     |                      | 9.2.1                                       | System Memory Map 0–4 Start Address Low                                    | 99         |

|     |                      | 9.2.2                                       | System Memory Map 0-4 Start Address High                                   | 100        |

|     |                      | 9.2.3                                       | System Memory Map 0-4 End Address Low                                      | 101        |

|     |                      | 9.2.4                                       | System Memory Map 0-4 End Address High                                     | 102        |

|     |                      | 9.2.5                                       | Card Memory Map 0-4 Offset Address Low                                     | 103        |

|     |                      | 9.2.6                                       | Card Memory Map 0-4 Offset Address High                                    | 104        |

| 10. | GEN                  | NERAL                                       | . WINDOW MAPPING REGISTERS                                                 | 105        |

|     | 10.1                 | Genera                                      | al Mapping Registers for I/O Mode                                          | 107        |

|     |                      | 10.1.1                                      |                                                                            |            |

|     |                      | 10.1.2                                      | Gen Map 0–6 Start Address High (I/O)                                       |            |

|     |                      | 10.1.3                                      |                                                                            |            |

|     |                      | 10.1.4                                      | Gen Map 0–6 End Address High (I/O)                                         |            |

|     |                      |                                             | Gen Map 0–6 Offset Address Low (I/O)                                       |            |

|     |                      |                                             | Gen Map 0–6 Offset Address High (I/O)                                      |            |

|     | 10.2                 |                                             | al Mapping Register for Memory Mode                                        |            |

|     |                      |                                             | Gen Map 0–6 Start Address Low (Memory)                                     |            |

|     |                      |                                             | Gen Map 0–6 Start Address High (Memory)                                    |            |

|     |                      |                                             | Gen Map 0–6 End Address Low (Memory)                                       |            |

|     |                      |                                             | Gen Map 0–6 End Address High (Memory)                                      |            |

|     |                      |                                             | Gen Map 0–6 Offset Address Low (Memory)                                    |            |

|     |                      | 10.2.5                                      |                                                                            |            |

|     |                      |                                             |                                                                            | 114        |

| 11  | FY <sup>-</sup>      | 10.2.6                                      | Gen Map 0–6 Offset Address High (Memory)                                   |            |

| 11. |                      | 10.2.6<br><b>TENSI</b> (                    | Gen Map 0–6 Offset Address High (Memory)<br>ON REGISTERS                   | 115        |

| 11. | 11.1                 | 10.2.6<br><b>TENSI</b><br>Misc C            | Gen Map 0–6 Offset Address High (Memory)<br>ON REGISTERS<br>Control 1      | <b>115</b> |

| 11. | 11.1<br>11.2         | 10.2.6<br><b>FENSIC</b><br>Misc C<br>FIFO C | Gen Map 0–6 Offset Address High (Memory)  ON REGISTERS  Control 1  Control |            |

| 11. | 11.1<br>11.2<br>11.3 | 10.2.6 FENSIC Misc C FIFO C Misc C          | Gen Map 0–6 Offset Address High (Memory)<br>ON REGISTERS<br>Control 1      |            |

4

**CONTENTS**

|      |      | Extended Index                                                    |     |

|------|------|-------------------------------------------------------------------|-----|

|      | 11.7 |                                                                   |     |

|      |      | 11.7.1 Extension Control 1                                        |     |

|      |      | 11.7.2 Gen Map 0–6 Upper Address (Memory)                         |     |

|      |      | 11.7.3 External Data (Index 2Fh) 11.7.4 External Data (Index 6Fh) |     |

|      |      | 11.7.5 Extension Control 2                                        |     |

|      |      |                                                                   |     |

|      |      | 11.7.6 PCI Space Control                                          |     |

|      |      | 11.7.7 PC Card Space Control                                      |     |

|      |      | 11.7.8 Window Type Select                                         |     |

|      |      | 11.7.9 Misc Control 3                                             |     |

|      |      | 11.7.10 SMB Socket Power Control Address                          |     |

|      |      | 11.7.11 Gen Map 0–6 Extra Control (I/O and Memory)                |     |

|      |      | 11.7.12 Extension Card Status Change                              |     |

|      |      | 11.7.13 Misc Control 4                                            |     |

|      |      | 11.7.14 Misc Control 5                                            |     |

|      |      | 11.7.15 Misc Control 6                                            |     |

|      | 11.8 |                                                                   |     |

|      |      | 11.8.1 Mask Revision Byte                                         |     |

|      |      | 11.8.2 Product ID Byte                                            |     |

|      |      | 11.8.3 Device Capability Byte A                                   |     |

|      |      | 11.8.4 Device Capability Byte B                                   |     |

|      |      | 11.8.5 Device Implementation Byte A                               |     |

|      |      | 11.8.6 Device Implementation Byte B                               |     |

|      |      | 11.8.7 Device Implementation Byte C                               |     |

|      |      | 11.8.8 Device Implementation Byte D                               | 141 |

| 12.  | TIMI | ING REGISTERS                                                     | 143 |

|      | 12.1 | Setup Timing 0–1                                                  | 143 |

|      |      | Command Timing 0-1                                                |     |

|      |      | Recovery Timing 0–1                                               |     |

| 13.  | DM/  | A OPERATION REGISTERS                                             | 147 |

|      | 13.1 |                                                                   |     |

|      | 13.2 | Mid Low Address                                                   | 148 |

|      | 13.3 | Mid High Address                                                  | 148 |

|      | 13.4 | 9                                                                 |     |

|      |      | Low Count                                                         |     |

|      |      | Mid Count                                                         |     |

|      | 13.7 | 0                                                                 |     |

|      | 13.8 |                                                                   |     |

|      |      | Request Register                                                  |     |

|      |      | 0 Mode Register                                                   |     |

|      |      | Mask Register                                                     |     |

| 1 /1 |      | •                                                                 |     |

| 14.  |      | MODE OPERATION                                                    |     |

| 15.  |      | CTRICAL SPECIFICATIONS                                            |     |

|      |      | Absolute Maximum Ratings                                          |     |

|      |      | DC Specifications                                                 |     |

|      | 15.3 | AC Timing Specifications                                          | 161 |

|      |      |                                                                   |     |

June 1998

ADVANCE DATA SHEET v1.0

CONTENTS

# CL-PD6832 PCI-to-CardBus Host Adapter

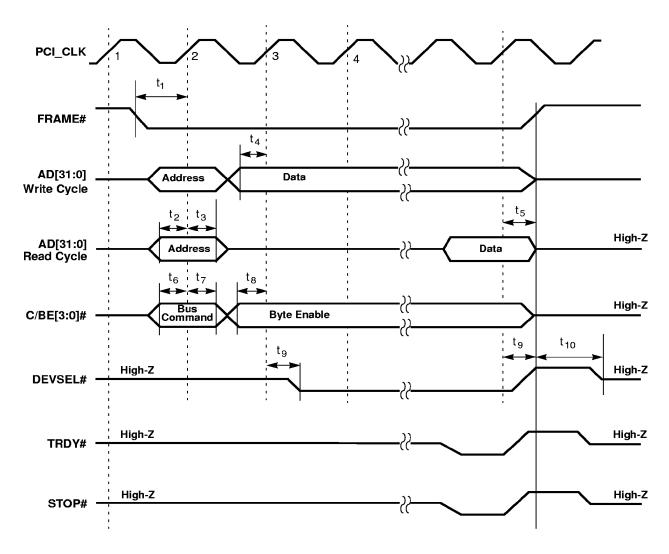

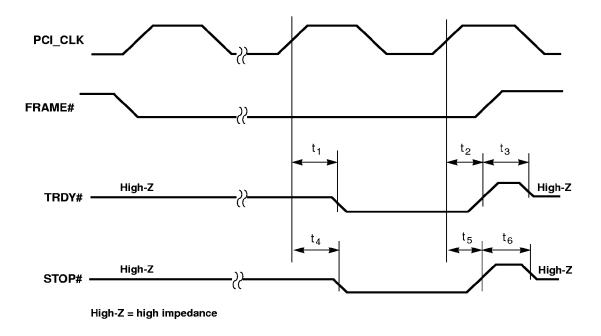

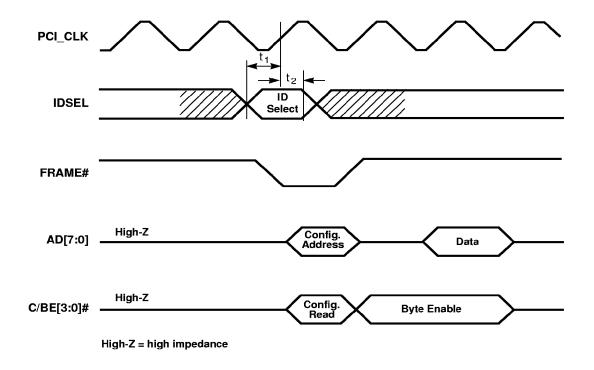

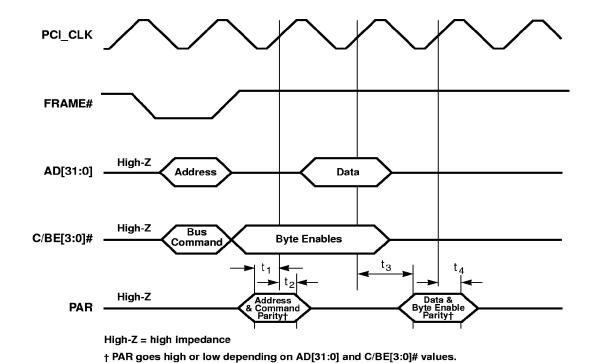

|     | 15.3.1      | PCI Bus Timing                           | 162 |

|-----|-------------|------------------------------------------|-----|

|     |             | System Interrupt Timing                  |     |

|     |             | PC Card (PCMCIA) Bus Timing Calculations |     |

|     | 15.3.4      | PC Card (PCMCIA) Bus Timing              | 169 |

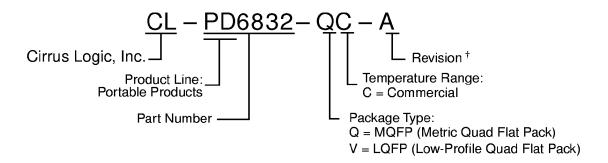

| 16. | PACKAGE     | SPECIFICATIONS                           | 175 |

| 17. | ORDERING    | G INFORMATION                            | 177 |

| Α.  | Pin Listing | js                                       | 179 |

| Α.  | Pin Listing | JS                                       |     |

6 CONTENTS ADVANCE DATA SHEET v1.0 June 1998

### 1. CONVENTIONS

### Register and Bit Conventions

In this document, the names of the CL-PD6832 internal registers are boldface (for example, **Chip Revision** and **Power Control** are register names). The names of bit fields are written with initial uppercase letters (for example, Card Power On and Battery Voltage Detect are bit field names).

Bits within words and words within various memory spaces are generally numbered with 0 (zero) as the least-significant bit or word. For example, the least-significant bit of a byte is bit 0, and the most-significant bit is bit 7.

In addition, number ranges for bit fields and words are presented with the most-significant value first. Thus, when discussing a bit field within a register, the bit number of the most-significant bit is written first, followed by a colon (:), and then the bit number of the least-significant bit (for example, bits 7:0).

### Abbreviations and Acronyms

The following table lists abbreviations and acronyms used in this document.

| Acronym or<br>Abbreviation | Definition                                              |

|----------------------------|---------------------------------------------------------|

| AC                         | alternating current                                     |

| ACPI                       | advanced configuration and power interface              |

| ATA                        | AT-attachment                                           |

| CIS                        | card information structure                              |

| DAC                        | digital-to-analog converter                             |

| DC                         | direct current                                          |

| DMA                        | direct memory access                                    |

| EEPROM                     | electrically erasable/programmable read-<br>only memory |

| EEROM                      | electrically erasable read-only memory                  |

| GPIO                       | general-purpose I/O                                     |

| IDE                        | integrated device electronics                           |

| IRQ                        | interrupt request                                       |

| ISA                        | industry standard architecture                          |

| JEIDA                      | Japanese Electronic Industry<br>Development Association |

| LQFP                       | low-profile quad flat pack                              |

| Acronym or<br>Abbreviation | Definition (cont.)                                      |  |  |

|----------------------------|---------------------------------------------------------|--|--|

| LSB                        | least-significant bit                                   |  |  |

| MQFP                       | metric quad flat pack                                   |  |  |

| MSB                        | most-significant bit                                    |  |  |

| MUX                        | multiplexer                                             |  |  |

| PCI                        | peripheral component interconnect                       |  |  |

| PCM                        | pulse coded modulation                                  |  |  |

| PCMCIA                     | Personal Computer Memory Card International Association |  |  |

| PME                        | power management enable                                 |  |  |

| R2                         | Release 2 (PC Card 16)                                  |  |  |

| RFU                        | reserved for future use                                 |  |  |

| RU                         | read update                                             |  |  |

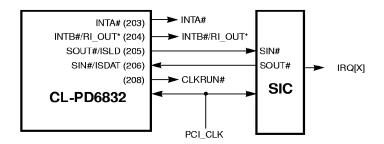

| SIC                        | serial interrupt controller                             |  |  |

| SMBus™                     | system management bus                                   |  |  |

| TC                         | terminal count                                          |  |  |

| VGA                        | video graphics array                                    |  |  |

| ZV                         | zoomed video                                            |  |  |

7

June 1998

ADVANCE DATA SHEET v1.0 CONVENTIONS

### Measurement Abbreviations

| Symbol            | Units of Measure                                  |  |  |

|-------------------|---------------------------------------------------|--|--|

| °C degree Celsius |                                                   |  |  |

| Gbyte             | gigabyte (2 <sup>30</sup> or 1,073,741,824 bytes) |  |  |

| Hz                | hertz (cycles per second)                         |  |  |

| Kbyte             | kilobyte (2 <sup>10</sup> or 1,024 bytes)         |  |  |

| kHz               | kilohertz (1,000 hertz)                           |  |  |

| Mbyte             | megabyte (2 <sup>20</sup> or 1,048,576 bytes)     |  |  |

| MHz               | megahertz (1,000,000 hertz)                       |  |  |

| μΑ                | microampere                                       |  |  |

| μs                | microsecond (1,000 nanoseconds)                   |  |  |

| mA                | milliampere                                       |  |  |

| ms                | millisecond (1,000 microseconds)                  |  |  |

| ns                | nanosecond                                        |  |  |

| pF                | picofarad                                         |  |  |

| V                 | volt                                              |  |  |

### Numbers

8

Hexadecimal numbers are presented with all letters in uppercase and a lowercase h appended. For example, *14h* and *03CAh* are hexadecimal numbers.

Binary numbers are enclosed in single quotation marks when in text. For example, '11' is a binary number.

Numbers not indicated by an *h* or single quotation marks are decimal.

The use of 'tbd' indicates values that are 'to be determined', 'n/a' designates 'not available', and 'n/c' indicates a pin that is a 'no connect'.

In addition, an uppercase X is used within numbers to indicate digits ignored by the CL-PD6832 within the current context. For example, '101XX01' is a binary number with bits 3:2 ignored.

CONVENTIONS ADVANCE DATA SHEET v1.0 June 1998

### 2. PIN INFORMATION

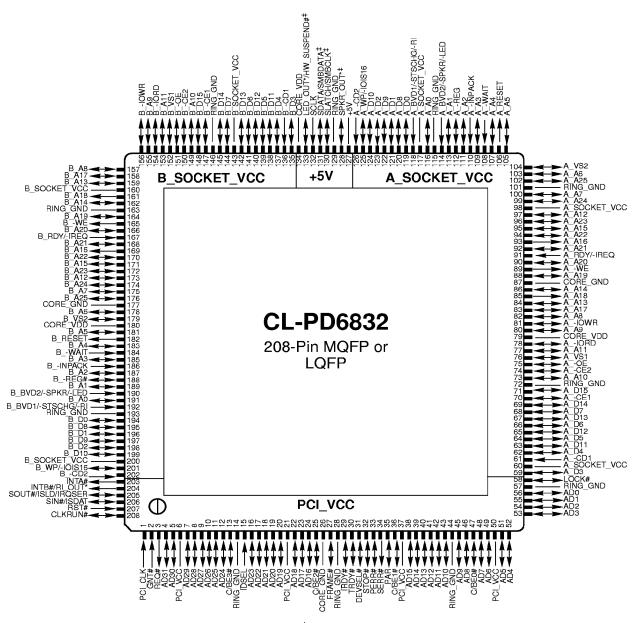

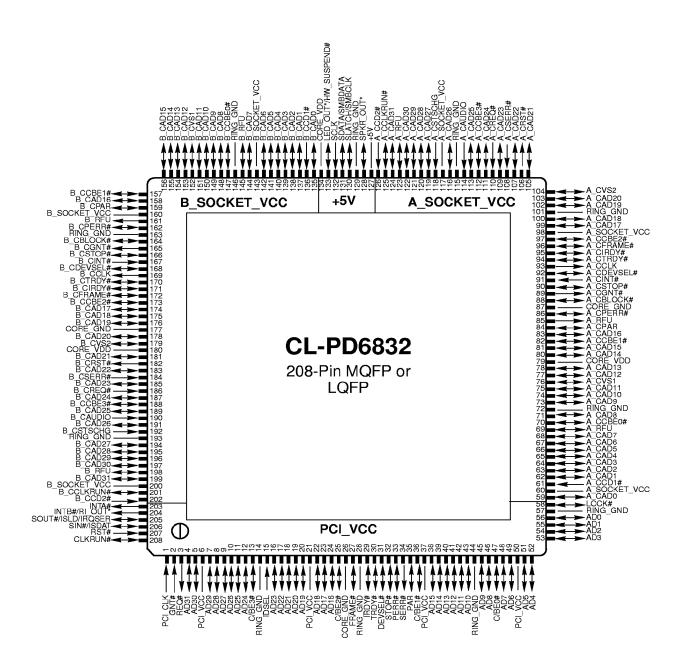

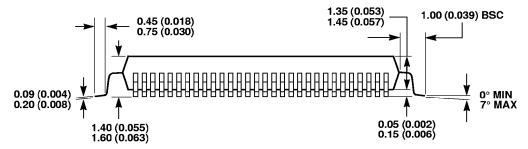

The CL-PD6832 is available in a 208-pin MQFP (metric quad flat pack) or LQFP (low-profile quad flat pack) package. (MQFP was formerly known as PQFP, and the LQFP was formerly know as VQFP.)

The CL-PD6832 interface pins can be divided into four groups:

- PCI bus interface pins

- PC Card socket interface pins (two sets)

- · Power control and general interface pins

- Power and ground pins

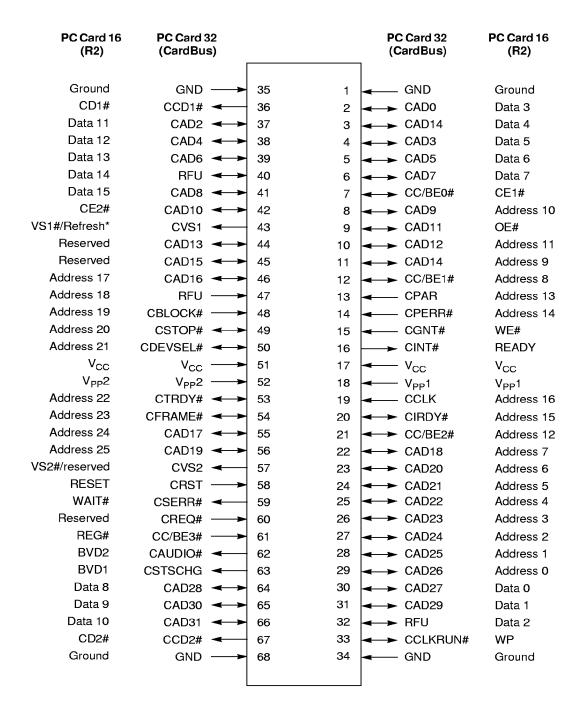

Refer to Figures 2-1 and 2-2 for the CL-PD6832 pin diagrams. Table 2-1 through Table 2-4 (starting on page 13) show the pin assignments and descriptions for the four groups of interface pins.

Tables A-1 and A-2 on page 180 show the PC Card 16 (R2) and PC Card 32 (CardBus) compatible pins in numerical order. Tables A-3 and A-4 on page 182 show the PC Card 16 (R2) and PC Card 32 (CardBus) compatible pins in alphabetical order.

June 1998

ADVANCE DATA SHEET v1.0

PIN INFORMATION

### 2.1 Pin Diagrams

**NOTE:** A double-dagger superscript (‡) at the end of the pin name indicates signals that are used for power-on configuration switches.

Figure 2-1. Pin Diagram for PC Card 16 (R2)

10 PIN INFORMATION ADVANCE DATA SHEET v1.0 June 1998

Figure 2-2. Pin Diagram for PC Card 32 (CardBus)

June 1998 ADVANCE DATA SHEET v1.0 PIN INFORMATION

### 2.2 Pin Description Conventions

The following conventions apply to the pin description tables in Section 2.3:

- A pound sign (#) at the end of a pin name indicates an active-low signal for the PCI bus, CardBus, and PCM-CIA bus.

- A dash (-) at the beginning of a pin name indicates an active-low signal for the PCMCIA bus.

- An asterisk (\*) at the end of a pin name indicates an active-low signal that is a general interface for the CL-PD6832.

- A double-dagger superscript (<sup>‡</sup>) at the end of the pin name indicates signals that are used for power-on configuration switches.

- A pin name ending in bracketed digits separated by a colon [n:n] indicates a multi-pin bus.

- The pin number (Pin Number) column indicates the package pin that carries the listed signal. Note that multipin buses are listed with the first pin number corresponding to the most-significant bit of the bus. For example, if pin numbers 4, 5, 7–12, 16–20, 22–24, 38–43, 45–46, 48–49, and 51–56 are associated with PCI Bus Address Input and Data Input/Output pins AD[31:0], then:

- AD31 is pin 4

- AD1 is pin 55

- AD0 is pin 56

- The quantity (Qty.) column indicates the number of pins used (per socket where applicable).

- The I/O-type code (I/O) column indicates the input and output configurations of the pins on the CL-PD6832.

The possible types are defined in the table below.

- The power-type code (Pwr.) column indicates the output drive power source for an output pin or the pull-up power source for an input pin on the CL-PD6832. The possible types are defined in the table below.

| I/O Type | Description                              |

|----------|------------------------------------------|

| ı        | Input pin                                |

| I-PU     | Input pin with internal pull-up resistor |

| 0        | Constant-driven output pin               |

| I/O      | Input/output pin                         |

| O-OD     | Open-drain output pin                    |

| O-TS     | Tristate output pin                      |

| GND      | Ground pin                               |

| PWR      | Power pin                                |

| Power Type | Output or Pull-up Power Source                                                                                  |

|------------|-----------------------------------------------------------------------------------------------------------------|

| 1          | +5V: powered from a 5-volt power<br>supply (in most systems; see the<br>description of +5V pin on page 23)      |

| 2          | A_SOCKET_VCC: powered from the Socket A V <sub>CC</sub> supply connecting to PC Card pins 17 and 51 of Socket A |

| 3          | B_SOCKET_VCC: powered from the Socket B V <sub>CC</sub> supply connecting to PC Card pins 17 and 51 of Socket B |

| 4          | PCI_VCC: powered from the PCI bus power supply                                                                  |

| 5          | CORE_VDD: powered from a 3.3-volt power supply                                                                  |

NOTE: All pin inputs are referenced to CORE VDD, independent of their output supply voltage.

• The drive-type (Drive) column describes the output drive-type of the pin (see DC specifications in Chapter 15 for more information). Note that the drive type listed for an input-only (I) pin is not applicable (–).

12 PIN INFORMATION ADVANCE DATA SHEET v1.0 June 1998

## 2.3 Pin Descriptions

**NOTE:** All pins are in tristate immediately following the RST#.

Table 2-1. PCI Bus Interface Pins

| Pin Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Number                                                   | Qty. | I/O | Pwr. | Drive        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----|------|--------------|

| AD[31:0]   | PCI Bus Address / Data Input/Outputs: These pins connect to PCI bus signals AD[31:0].                                                                                                                                                                                                                                                                                                                                                           | 4–5, 7–12,<br>16–20, 22–24,<br>38–43, 45–46,<br>48–49, 51–56 | 32   | I/O | 4    | PCI<br>Spec. |

| C/BE[3:0]# | PCI Bus Command / Byte Enables: The command signalling and byte enables are multiplexed on the same pins. During the address phase of a transaction, C/BE[3:0]# are interpreted as the bus commands. During the data phase, C/BE[3:0]# are interpreted as byte enables. The byte enables are valid for the entirety of each data phase, and they indicate which bytes in the 32-bit data path carry meaningful data for the current data phase. | 13, 25, 36, 47                                               | 4    | I/O | 4    | PCI<br>Spec. |

| FRAME#     | Cycle Frame: This signal driven by current master indicates that a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAME# is deasserted, the transaction is in its final phase.                                                                                                                                                                                                                           | 27                                                           | 1    | I/O | 4    | PCI<br>Spec. |

| IRDY#      | Initiator Ready: This signal indicates the initiating agent's ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#.                                                                                                                                                                                                                                                                           | 29                                                           | 1    | I/O | 4    | PCI<br>Spec. |

| TRDY#      | Target Ready: This signal indicates the target agent's ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#.                                                                                                                                                                                                                                                                                  | 30                                                           | 1    | I/O | 4    | PCI<br>Spec. |

| STOP#      | <b>Stop:</b> This signal indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                 | 32                                                           | 1    | I/O | 4    | PCI<br>Spec. |

| LOCK#      | Lock Transaction: This signal is used by a PCI master to perform a locked transaction to a target memory. LOCK# is used to prevent more than one master from using a particular system resource.                                                                                                                                                                                                                                                | 58                                                           | 1    | I/O | 4    | PCI<br>Spec  |

| IDSEL      | Initialization Device Select: This input is used as a chip select during configuration read and write transactions. This is a point-to-point signal. The CL-PD6832 must be connected to its own unique IDSEL line (from the PCI bus arbiter or one of the most-significant AD bus pins).                                                                                                                                                        | 15                                                           | 1    | I   | _    | _            |

| DEVSEL#    | <b>Device Select:</b> When actively driven, this signal indicates that the CL-PD6832 has decoded its own PCI address as the target of the current access. As an input, indicates whether any device on the bus has been selected.                                                                                                                                                                                                               | 31                                                           | 1    | I/O | 4    | PCI<br>Spec. |

June 1998

ADVANCE DATA SHEET v1.0

**Table 2-1. PCI Bus Interface Pins** (cont.)

| Pin Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin Number | Qty. | I/O         | Pwr. | Drive        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-------------|------|--------------|

| PERR#         | Parity Error: The CL-PD6832 drives this output active (low) if it detects a data parity error during a write phase.                                                                                                                                                                                                                                                                                                              | 33         | 1    | I/O         | 4    | PCI<br>Spec. |

| SERR#         | <b>System Error:</b> This output is pulsed by the CL-PD6832 to indicate an address parity error.                                                                                                                                                                                                                                                                                                                                 | 34         | 1    | O-<br>OD    | 4    | PCI<br>Spec. |

| PAR           | Parity: This pin is sampled in the clock cycle after completion of each corresponding address or write data phase. For read operations, this pin is driven from the cycle after TRDY# is asserted until the cycle after completion of each data phase. It ensures even parity across AD[31:0] and C/BE[3:0]#.                                                                                                                    | 35         | 1    | I/O         | 4    | PCI<br>Spec. |

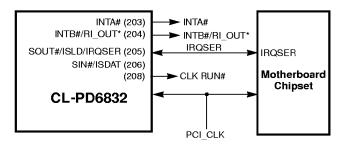

| PCI_CLK       | PCI Clock: This input provides timing for all transactions on the PCI bus to and from the CL-PD6832. All PCI bus interface signals described in this table (Table 2-1), except RST#, INTA#, and INTB# are sampled on the rising edge of PCI_CLK; and all the CL-PD6832 PCI bus interface timing parameters are defined with respect to this edge. This input can be operated at frequencies from 0 to 33 MHz.                    | 1          | 1    | I           | -    | -            |

| RST#          | <b>Device Reset:</b> This input is used to initialize all registers and internal logic to their reset states and place <i>all</i> the CL-PD6832 pins in a high-impedance state.                                                                                                                                                                                                                                                  | 207        | 1    | I           | -    | -            |

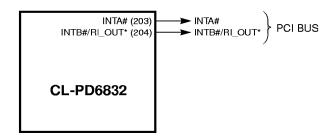

| INTA#         | PCI Bus Interrupt A: This output indicates a programmable interrupt request generated from any of a number of card actions. Although there is no specific mapping requirement for connecting interrupt lines from the CL-PD6832 to the system, a common use is to connect this pin to the PCI bus INTA# interrupt line and use the PCI Interrupt Signalling mode.                                                                | 203        | 1    | O-TS        | 4    | PCI<br>Spec. |

| INTB#/RI_OUT* | PCI Bus Interrupt B / Ring Indicate Output: In PCI Interrupt Signalling mode, this output can be used as an interrupt output connected to the PCI bus INTB# interrupt line. RI_OUT* and INTB# are open-drain outputs.  If Misc Control 2 register bit 7 is '1', this pin works as a ring indicate output from a socket's BVD1/-STSCHG/-RI input. Ring Indicate capability is available in all of the Interrupt Signalling modes. | 204        | 1    | OD,<br>O-TS | 4    | PCI<br>Spec. |

14 PIN INFORMATION ADVANCE DATA SHEET v1.0 June 1998

**Table 2-1.** PCI Bus Interface Pins (cont.)

| Pin Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin Number    | Qty. | I/O | Pwr. | Drive        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|-----|------|--------------|

| SOUT#/ISLD/<br>IRQSER | Serial Interrupt Output / Serial IRQ Load: In PCI Interrupt Signalling mode, this pin is a no connect. In PC/PCI Serial Interrupt Signalling mode, this pin is the serial interrupt output, SOUT#.  In PCI/Way Interrupt Signalling mode, this pin is the IRQSER signal, which is bidirectional.  In External-Hardware Interrupt Signalling mode, this pin is the load signal, ISLD, used to load the serially transmitted interrupt data into the external serial-to-parallel shifters. | 205           | 1    | I/O | 4    | PCI<br>Spec. |

| SIN#/<br>ISDAT        | Serial Interrupt Input / Serial IRQ Data: In PCI Interrupt Signalling mode, this pin is a no connect. In PC/PCI Serial Interrupt Signalling mode, this pin is the serial interrupt input, SIN#.  In External-Hardware Interrupt Signalling mode, this pin is the IRQ vector data, ISDAT, that is serially transmitted to the external serial-to-parallel shifters.                                                                                                                       | 206           | 1    | 1/0 | 4    | PCI<br>Spec. |

| CLKRUN#               | Clock Run: This pin is an input to indicate the status of PCI_CLK and an open-drain output to request the starting or speeding up of PCI_CLK. This pin complies with the Mobile PCI Mobile Design Guide.                                                                                                                                                                                                                                                                                 | 208           | 1    | I/O | 4    | PCI<br>Spec. |

| GNT#                  | <b>Grant:</b> This signal indicates that access to the bus has been granted.                                                                                                                                                                                                                                                                                                                                                                                                             | 2             | 1    | ı   | -    | _            |

| REQ#                  | Request: This signal indicates to the arbiter that the CL-PD6832 requests use of the bus.                                                                                                                                                                                                                                                                                                                                                                                                | 3             | 1    | 0   | 4    | PCI<br>Spec. |

| PCI_VCC               | PCI Bus V <sub>CC</sub> : These pins can be connected to either a 3.3- or 5-V power supply. The PCI bus interface pin outputs listed in this table (Table 2-1) operate at the voltage applied to these pins, independent of the voltage applied to other CL-PD6832 pin groups.                                                                                                                                                                                                           | 6, 21, 37, 50 | 4    | PWR | _    | _            |

June 1998 ADVANCE DATA SHEET v1.0 PIN INFORMATION

Table 2-2. Socket Interface Pins

| Pin Name <sup>1</sup>    | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                          | Pin N    | umber    | 0417 | I/O       | Pwr.   | Drive                 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|-----------|--------|-----------------------|

| Pin Name                 | Description-                                                                                                                                                                                                                                                                                                                                                                                                                      | Socket A | Socket B | Qty. | 1/0       | PWI.   | Drive                 |

| -REG#/<br>CCBE3#         | Register Access: During PC Card 16 memory cycles, this output chooses between attribute and common memory. During I/O cycles for non-DMA transfers, this signal is active (low). During ATA mode, this signal is always inactive. For DMA cycles on the CL-PD6832 to a DMA-capable card, -REG is inactive during I/O cycles to indicate DACK to the PC Card 16 card.  In CardBus mode, this pin is the command and byte enable 3. | 112      | 188      | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| A[25:24]/<br>CAD[19, 17] | PC Card 16 socket address 25:24 outputs. In CardBus mode, these pins are the CardBus address/data bits 19 and 17, respectively.                                                                                                                                                                                                                                                                                                   | 102, 99  | 176, 174 | 2    | I/O       | 2 or 3 | Card-<br>Bus<br>spec  |

| A23/<br>CFRAME#          | PC Card 16 socket address 23 output. In CardBus mode, this pin is the CardBus FRAME# signal.                                                                                                                                                                                                                                                                                                                                      | 96       | 172      | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec  |

| A22/<br>CTRDY#           | PC Card 16 socket address 22 output. In CardBus mode, this pin is the CardBus TRDY# signal.                                                                                                                                                                                                                                                                                                                                       | 94       | 170      | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec  |

| A21/<br>CDEVSEL#         | PC Card 16 socket address 21 output. In CardBus mode, this pin is the CardBus DEVSEL# signal.                                                                                                                                                                                                                                                                                                                                     | 92       | 168      | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec  |

| A20/<br>CSTOP#           | PC Card 16 socket address 20 output. In CardBus mode, this signal is the Card-Bus STOP# signal.                                                                                                                                                                                                                                                                                                                                   | 90       | 166      | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec  |

| A19/<br>CBLOCK#          | PC Card 16 socket address 19 output. In CardBus mode, this signal is the CardBus LOCK# signal used for locked transactions.                                                                                                                                                                                                                                                                                                       | 88       | 164      | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec  |

| A18/<br>RFU              | PC Card 16 socket address 18 output. In CardBus mode, this pin is reserved for future use.                                                                                                                                                                                                                                                                                                                                        | 85       | 161      | 1    | 0         | 2 or 3 | Card-<br>Bus<br>spec  |

| A17/<br>CAD16            | PC Card 16 socket address 17 output. In CardBus mode, this pin is the CardBus address/data bit 16.                                                                                                                                                                                                                                                                                                                                | 83       | 158      | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec  |

To differentiate the sockets in the pin diagram, all socket-specific pins have either A\_ or B\_ prepended to the pin names indicated. For example, A\_A[25:0] and B\_A[25:0] are the independent address buses to the sockets.

PIN INFORMATION

ADVANCE DATA SHEET v1.0

June 1998

<sup>&</sup>lt;sup>2</sup> When a socket is configured as an ATA drive interface, socket interface pin functions change. See Chapter 14.

Table 2-2. Socket Interface Pins (cont.)

| Pin Name <sup>1</sup>                                     | December 2                                                                                                                                                | Pin N                                                    | umber                                                                | 04   | 1/0       | Descri | Duise                 |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|------|-----------|--------|-----------------------|

| Pin Name                                                  | Description <sup>2</sup>                                                                                                                                  | Socket A                                                 | Socket B                                                             | Qty. | I/O       | Pwr.   | Drive                 |

| A16/<br>CCLK                                              | PC Card 16 socket address 16 output. In CardBus mode, this pin supplies the clock to the inserted card.                                                   | 93                                                       | 169                                                                  | 1    | 0         | 2 or 3 | Clock<br>spec.        |

| A15/<br>CIRDY#                                            | PC Card 16 socket address 15 output. In CardBus mode, this pin is the CardBus IRDY# signal.                                                               | 95                                                       | 171                                                                  | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec. |

| A14/<br>CPERR#                                            | PC Card 16 socket address 14 output. In CardBus, this pin is the CardBus PERR# signal.                                                                    | 86                                                       | 162                                                                  | 1    | I/O<br>PU | 2 or 3 | Card-<br>Bus<br>spec. |

| A13/<br>CPAR                                              | PC Card 16 socket address 13 output. In CardBus mode, this pin is the CardBus PAR signal.                                                                 | 84                                                       | 159                                                                  | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| A12/<br>CCBE2#                                            | PC Card 16 socket address 12 output. In CardBus mode, this pin is the command and byte enable 2.                                                          | 97                                                       | 173                                                                  | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| A[11:9]/<br>CAD[12, 9, 14]                                | PC Card 16 socket address 11:9 outputs. In CardBus mode, these pins are the CardBus address/data bits 12, 9, and 14, respectively.                        | 77, 73, 80                                               | 153, 149,<br>155                                                     | 3    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| A8/<br>CCBE1#                                             | PC Card 16 socket address 8 output. In CardBus mode, this pin is the command and byte enable 1.                                                           | 82                                                       | 157                                                                  | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| A[7:0]/<br>CAD[18, 20–26]                                 | PC Card 16 socket address 7:0 outputs. In CardBus mode, these pins are the CardBus address/data bits 18 and 20-26, respectively.                          | 100, 103,<br>105, 107,<br>109, 111,<br>113, 116          | 175, 178,<br>181, 183,<br>185, 187,<br>189, 191                      | 8    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| D15/<br>CAD8                                              | PC Card 16 socket data I/O bit 15. In CardBus mode, this pin is the CardBus address/data bit 8.                                                           | 71                                                       | 148                                                                  | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| D14/<br>RFU                                               | PC Card 16 socket data I/O bit 14. In CardBus mode, this pin is reserved for future use.                                                                  | 69                                                       | 145                                                                  | 1    | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

| D[13:3]/<br>CAD[6, 4, 2, 31,<br>30, 28, 7, 5, 3,<br>1, 0] | PC Card 16 socket data I/O bits 13:3. In CardBus mode, these pins are the CardBus address/data bits 6, 4, 2, 31, 30, 28, 7, 5, 3, 1, and 0, respectively. | 67, 65,63,<br>124, 122,<br>120, 68,<br>66, 64, 62,<br>59 | 142, 140,<br>138, 199,<br>197, 195,<br>144, 141,<br>139, 137,<br>135 | 11   | I/O       | 2 or 3 | Card-<br>Bus<br>spec. |

<sup>&</sup>lt;sup>1</sup> To differentiate the sockets in the pin diagram, all socket-specific pins have either A\_ or B\_ prepended to the pin names indicated. For example, A\_A[25:0] and B\_A[25:0] are the independent address buses to the sockets.

June 1998

PIN INFORMATION

<sup>&</sup>lt;sup>2</sup> When a socket is configured as an ATA drive interface, socket interface pin functions change. See Chapter 14.

**Table 2-2. Socket Interface Pins** (cont.)

| Pin Name <sup>1</sup>       | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                      | Pin N    | umber    | Qty.  | I/O        | Pwr.   | Drive                 |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|------------|--------|-----------------------|

| Pin Name*                   | Description-                                                                                                                                                                                                                                                                                                                                                                                  | Socket A | Socket B | Gity. | 1/0        | PWI.   | Drive                 |

| D2/<br>RFU                  | PC Card 16 socket data I/O bit 2. In CardBus mode, this pin is reserved for future use.                                                                                                                                                                                                                                                                                                       | 123      | 198      | 1     | 1/0        | 2 or 3 | Card-<br>Bus<br>spec. |

| D[1:0]/<br>CAD[29, 27]      | PC Card 16 socket data I/O bits 1:0. In CardBus mode, these pins are the CardBus address/data bits 29 and 27, respectively.                                                                                                                                                                                                                                                                   | 121, 119 | 196, 194 | 2     | I/O        | 2 or 3 | Card-<br>Bus<br>spec. |

| -OE/<br>CAD11               | Output Enable: This output goes active (low) to indicate a memory read from the PC Card 16 socket to the CL-PD6832.  In CardBus mode, this pin is the CardBus address/data bit 11.                                                                                                                                                                                                            | 75       | 151      | 1     | I/O        | 2 or 3 | Card-<br>Bus<br>spec. |

| -WE/<br>CGNT#               | Write Enable: This output goes active (low) to indicate a memory write from the CL-PD6832 to the PC Card 16 socket. In CardBus mode, this pin is the CardBus GNT# signal.                                                                                                                                                                                                                     | 89       | 165      | 1     | I/O        | 2 or 3 | Card-<br>Bus<br>spec. |

| -IORD/<br>CAD13             | I/O Read: This output goes active (low) for I/O reads from the socket to the CL-PD6832. In CardBus mode, this pin is the CardBus address/data bit 13.                                                                                                                                                                                                                                         | 78       | 154      | 1     | O-TS       | 2 or 3 | Card-<br>Bus<br>spec. |

| -IOWR/<br>CAD15             | I/O Write: This output goes active (low) for I/O writes from the CL-PD6832 to the socket. In CardBus mode, this pin is the CardBus address/data bit 15.                                                                                                                                                                                                                                       | 81       | 156      | 1     | I/O        | 2 or 3 | Card-<br>Bus<br>spec. |

| WP/<br>-IOIS16/<br>CCLKRUN# | Write Protect / I/O Is 16-Bit: In Memory Card Interface mode, this input is interpreted as the status of the write protect switch on the PC Card 16 card. In I/O Card Interface mode, this input indicates the size of the I/O data at the current address on the PC Card 16 card.  In CardBus mode, this pin is the CardBus CLKRUN# signal, which starts and stops the CardBus clock (CCLK). | 125      | 201      | 1     | I/O-<br>PU | 2 or 3 | Card-<br>Bus<br>spec. |

<sup>&</sup>lt;sup>1</sup> To differentiate the sockets in the pin diagram, all socket-specific pins have either A\_ or B\_ prepended to the pin names indicated. For example, A\_A[25:0] and B\_A[25:0] are the independent address buses to the sockets.

PIN INFORMATION ADVANCE DATA SHEET v1.0 June 1998

<sup>&</sup>lt;sup>2</sup> When a socket is configured as an ATA drive interface, socket interface pin functions change. See Chapter 14.

Table 2-2. Socket Interface Pins (cont.)

| Pin Name <sup>1</sup>   | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                    | Pin N    | umber    | Qty.  | I/O  | Pwr.   | Drive                 |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|------|--------|-----------------------|

| Pin Name                | Description-                                                                                                                                                                                                                                                                                                                                                                                | Socket A | Socket B | Gity. | 1/0  | PWI.   | Dilve                 |

| -INPACK/<br>CREQ#       | Input Acknowledge: The -INPACK function is not applicable in PCI bus environments. This pin should be connected to the PC Card socket's -INPACK pin, since this can be the DREQ signal during DMA cycles.  In CardBus mode, this pin is the CardBus REQ# signal.                                                                                                                            | 110      | 186      | 1     | I-PU | 2 or 3 | 1                     |

| RDY/<br>-IREQ/<br>CINT# | Ready / Interrupt Request: In Memory Card Interface mode, this input indicates to the CL-PD6832 that the card is either ready or busy. In I/O Card Interface mode, this input indicates a card interrupt request.  In CardBus mode, this pin is the CardBus Interrupt Request signal. This signal is active-low and level-sensitive.                                                        | 91       | 167      | 1     | I-PU | 2 or 3 | 1                     |

| -WAIT/<br>CSERR#        | Wait: This input indicates a request by the card to the CL-PD6832 to halt the cycle in progress until this signal is deactivated.  In CardBus mode, this pin is the CardBus SERR# signal.                                                                                                                                                                                                   | 108      | 184      | 1     | I-PU | 2 or 3 | -                     |

| -CD[2:1]/<br>CCD[2:1]#  | Card Detect: These inputs indicate to the CL-PD6832 that a card is in the socket. They are internally pulled high to the voltage of the +5V power pin.  In CardBus mode, these inputs are used in conjunction with CVS[2:1] to detect the presence and type of card.                                                                                                                        | 126, 61  | 202, 136 | 2     | I-PU | 1      | -                     |

| -CE2/<br>CAD10          | Card Enable: This pin is driven low by the CL-PD6832 during card access cycles to control byte/word card access CE1 enables even-numbered address bytes, and -CE2 enables odd-numbered address bytes. When configured for 8-bit cards, only -CE1 is active and A0 is used to indicate access of odd- or even-numbered bytes.  In CardBus mode, this pin is the CardBus address/data bit 10. | 74       | 150      | 1     | I/O  | 2 or 3 | Card-<br>Bus<br>spec. |

<sup>&</sup>lt;sup>1</sup> To differentiate the sockets in the pin diagram, all socket-specific pins have either A\_ or B\_ prepended to the pin names indicated. For example, A\_A[25:0] and B\_A[25:0] are the independent address buses to the sockets.

June 1998

PIN INFORMATION

<sup>&</sup>lt;sup>2</sup> When a socket is configured as an ATA drive interface, socket interface pin functions change. See Chapter 14.

**Table 2-2.** Socket Interface Pins (cont.)

| Pin Name <sup>1</sup>                 | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin N    | umber    | Otv  | I/O  | Pwr.   | Drive                 |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|------|--------|-----------------------|

| Pili Name                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Socket A | Socket B | Qty. | 1/0  | PWI.   | Drive                 |

| -CE1/<br>CCBE0#                       | Card Enable: This pin is driven low by the CL-PD6832 during card access cycles to control byte/word card access CE1 enables even-numbered address bytes, and -CE2 enables odd-numbered address bytes. When configured for 8-bit cards, only -CE1 is active and A0 is used to indicate access of odd- or even-numbered bytes.  In CardBus mode, this pin is the command and byte enable 0.                                                                                                                                                                                                               | 70       | 147      | 1    | I/O  | 2 or 3 | Card-<br>Bus<br>spec. |

| RESET/<br>CRST#                       | Card Reset: This output is low for normal operation and goes high to reset the card. To prevent reset glitches to a card, this signal is high-impedance unless a card is seated in the socket, card power is applied, and the card's interface signals are enabled.  In CardBus mode, this pin is the RST# input to the card, which is active-low.                                                                                                                                                                                                                                                      | 106      | 182      | 1    | O-TS | 2 or 3 | Card-<br>Bus<br>spec. |

| BVD2/<br>-SPKR/<br>-LED/<br>CAUDIO    | Battery Voltage Detect 2 / Speaker / LED: In Memory Card Interface mode, this input serves as the BVD2 (battery warning status) input. In I/O Card Interface mode, this input can be configured as a card's -SPKR binary audio input. For ATA or non-ATA (SFF-68) disk-drive support, this input can also be configured as a drive-status LED input.  In CardBus mode, this pin is the AUDIO input from the card.                                                                                                                                                                                       | 114      | 190      | 1    | I-PU | 2 or 3 | -                     |

| BVD1/<br>-STSCHG/<br>-RI/<br>-CSTSCHG | Battery Voltage Detect 1 / Status Change / Ring Indicate: In Memory Card Interface mode, this input serves as the BVD1 (battery-dead status) input. In I/O Card Interface mode, this input is the -STSCHG input, which indicates to the CL-PD6832 that the card's internal status has changed. If bit 7 of the Interrupt and General Control register is set to '1', this pin serves as the ring indicate input for wakeup-on-ring system power management support.  In CardBus mode, this pin is the CardBus Status Change used by the card to alert the system to changes in READY, WP, and BVD[2:1]. | 118      | 192      | 1    | I-PU | 2 or 3 | -                     |

<sup>&</sup>lt;sup>1</sup> To differentiate the sockets in the pin diagram, all socket-specific pins have either A\_ or B\_ prepended to the pin names indicated. For example, A\_A[25:0] and B\_A[25:0] are the independent address buses to the sockets.

PIN INFORMATION ADVANCE DATA SHEET v1.0 June 1998

<sup>&</sup>lt;sup>2</sup> When a socket is configured as an ATA drive interface, socket interface pin functions change. See Chapter 14.

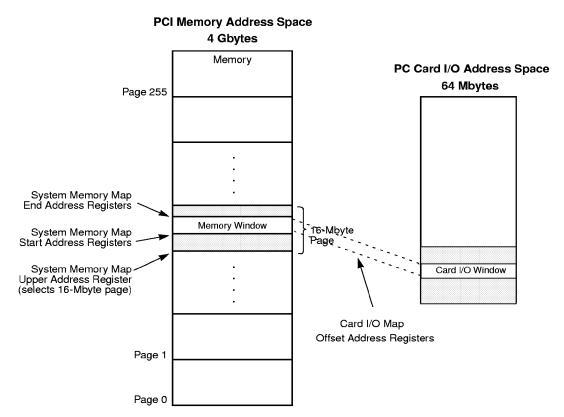

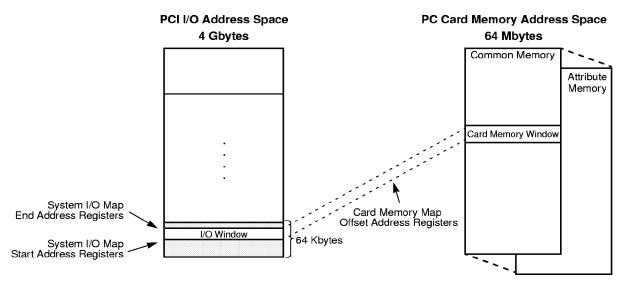

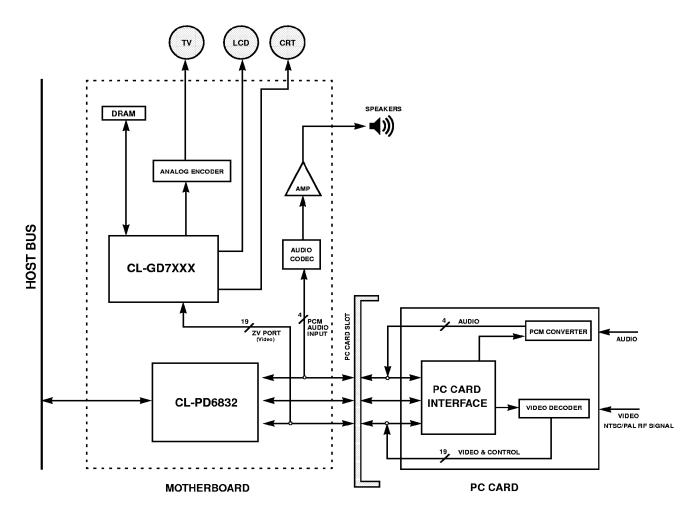

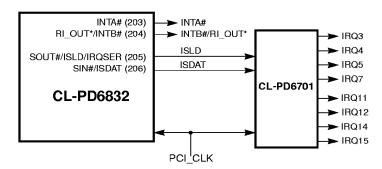

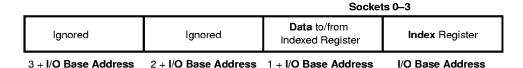

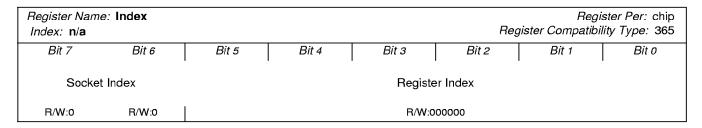

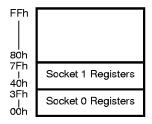

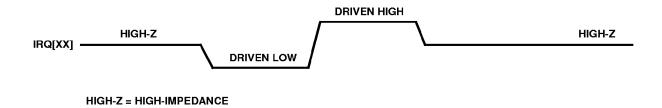

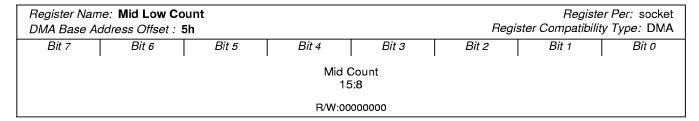

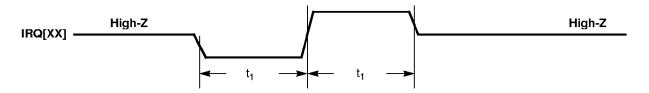

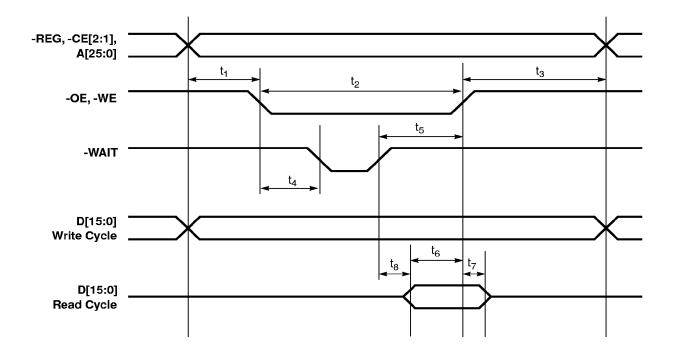

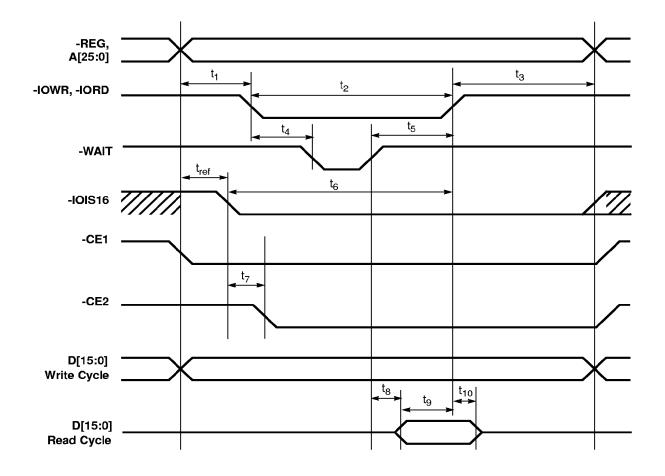

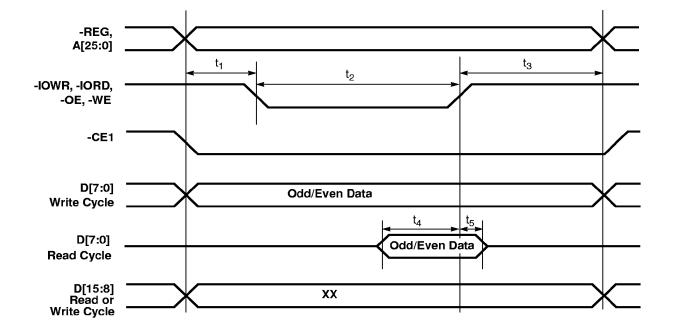

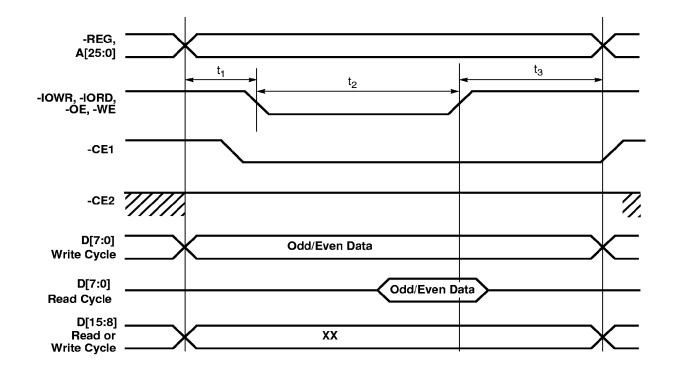

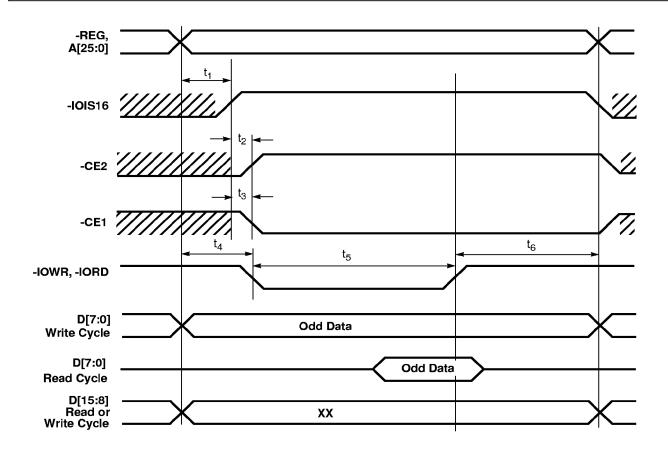

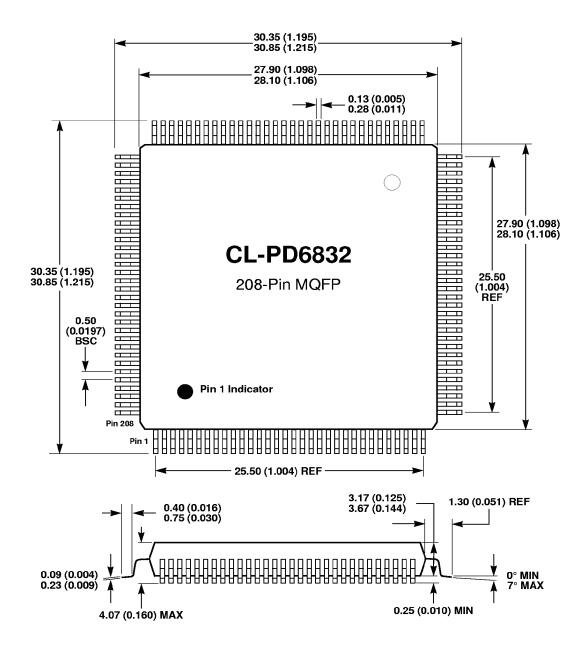

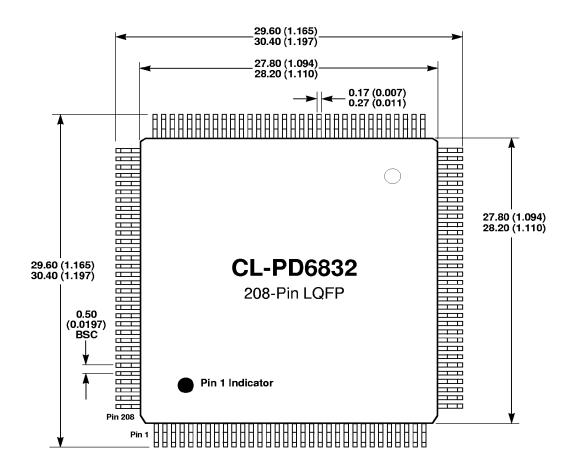

**Table 2-2. Socket Interface Pins** (cont.)