MITSUBISHI (MICMPTR/MIPRC)

T-52-33-15

PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### **DESCRIPTION**

The M5L8279P-5 is a programmable keyboard and display interface device that is designed to be used in combination with an 8-bit/16-bit microprocessor. This device is fabricated with N-channel silicon-gate ED-MOS process technology and is packed in a 40-pin DIL package. It needs only single 5V power supply.

#### **FEATURES**

- Single 5V supply voltage

- TTL compatible

- Keyboard mode

- Sensor matrix mode

- Strobed mode

- Internally provided key bounce protection circuit

- Programmable debounce time

- 2-key lockout/N-key'rollover

- 8-character keyboard FIFO

- Internally contained 16 × 8-bit display RAM

- Programmable right and left entry

#### **APPLICATION**

Microcomputer I/O device

64 contact key input device for such items as electronic cash registers

Dual 8- or single 16-alphanumeric display

#### **FUNCTION**

The total chip, consisting of a keyboard interface and a display interface, can be programmed by eight 8-bit commands. The keyboard portion is provided with a 64-bit key

debounce buffer and an  $8 \times 8$ -bit FIFO/SENSOR RAM. It operates in any one of the scanned keyboard mode, scanned sensor matrix mode or strobed entry mode. The display portion is provided with a  $16 \times 8$ -bit display RAM that can be organized into a dual  $16 \times 4$  configuration. Also, an 8-digit display configuration is possible by means of programming.

PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

## T-52-33-15

### MITSUBISHI (MICMPTR/MIPRC)

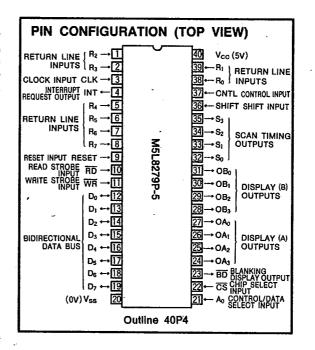

#### PIN DISCRIPTION

| pin                            | Name                        | Input or output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|-----------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R₀~R <sub>7</sub>              | Return line inputs          | ſn              | These are the return lines which are connected with the scan lines through the keys or sensor switches, and are used for 8-bit input in the strobed entry mode. They are provided with internal pullups to maintain them high-level until a switch closure pulls one low-level. They become active at low-level,                                                                                                              |

| CLK                            | Clock input                 | in              | Clock signal from the system which is used to generate internal timing.                                                                                                                                                                                                                                                                                                                                                       |

| INT                            | interrupt request output    | Out             | When there is any data in the FIFO during the keyboard mode or the strobed mode, this signal turns high-level so as to request interrupt to the CPU. It turns low-level each time data is read, but if any data remains in the FIFO it will turn high-level again and request interrupt to the CPU. End interrupt command resets INT signal.                                                                                  |

| RESET                          | Reset input                 | ln .            | Resets the chip when this signal is high-level. After the reset it assumes 16-digit, left-entry, encode display and 2-key lockout mode, and the prescale value of the clock becomes 31. The display RAM, however, is not cleared.                                                                                                                                                                                             |

| RD                             | Read strobe input           | In              | Functions to control data transfer to the data bus.                                                                                                                                                                                                                                                                                                                                                                           |

| WR                             | Write strobe input          | In              | Functions to control command/data transfer from the data bus.                                                                                                                                                                                                                                                                                                                                                                 |

| D <sub>0</sub> ~D <sub>7</sub> | Bidirectional data bus      | In/out          | All data and commands between the CPU and the chip are transferred through these lines.                                                                                                                                                                                                                                                                                                                                       |

| Ao                             | Control/data select         | ln              | When this signal is high-level, it indicates that the signals in and out are either command (in) or status (out). When low-level, it indicates they are data (in/out).                                                                                                                                                                                                                                                        |

| ĊŚ                             | Chip select input           | (n              | Chip select is enabled when this signal is low-level.                                                                                                                                                                                                                                                                                                                                                                         |

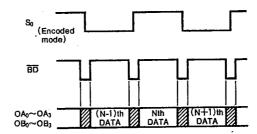

| BD                             | Blanking display output     | Out             | This signal is used in preventing overlapped display during digit switching. It also may be brought to low level by display blanking command.                                                                                                                                                                                                                                                                                 |

| OA₀~OA₃<br>OB₀~OB₃             | Display (A) and (B) outputs | Out             | These output ports can be used either as a dual 4-bit port or a single 8-bit port depending on an application, and the contents of the display RAM are output synchronizing with the scan timing signals. These two 4-bit ports may be blanked independently. Blanking may be activated with either high- or low-level signal by means of clear command.                                                                      |

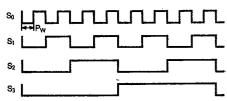

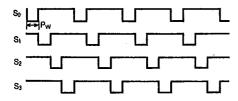

| S <sub>0</sub> ~S <sub>3</sub> | Scan timing outputs         | Out             | These signals are used to scan the key switch, the sensor matrix or the display digit. They can be eithe decoded or encoded, but it requires an external decoder in the encode mode. Signals S <sub>0</sub> ~S <sub>3</sub> are all turned to low-level when RESET is high-level.                                                                                                                                             |

| SHIFT                          | Shift input                 | In              | In the keyboard mode, the shift input becomes the second highest bit of the key input information and is stored in the FIFO. This input is ignored in the other modes. It is constantly kept at high-level by an internal pull resistor. The signal is active at high-level.                                                                                                                                                  |

| CNTL                           | Control input               | fn .            | In the keyboard mode, the control input becomes the most significant bit of the key input information and i stored in the FIFO. The signal is active at high-level. In the strobed entry mode, it becomes the strobe signal and stores the return input data in the FIFO at the rising edge of the input. It affects nothing internal is the sensor mode. It is constantly kept at high-level by an internal pullup resistor. |

#### **OPERATION**

One of the three operating modes, the keyboard mode is the most common, and allows programmed 2-key lockout and N-key rollover. Encoded timing signals corresponding with key input are stored in the FIFO through the keydebounce logic, and the debouncing time of the key is also programmable. In the sensor mode, the contents of the 8 X 8 key contacts are constantly stored in the FIFO/sensor RAM, generating an interrupt signal to the CPU each time there is a change in the contents. In the strobed entry mode, the CNTL input signal is used as a strobe for storing the 8 return line inputs to the FIFO/sensor RAM.

The display portion is provided with a 16 X 8-bit display RAM that can be organized into a dual 16 X 4-bit configuration. Also, an 8-digit display configuration is possible by means of programming. Input to the register can be performed by either left or right entry modes. In the auto increment mode, read and write can be carried out after designating the starting address only.

Both the keyboard and display sections are scanned by common scan timing signals that are derived from the basic clock pulse. This frequency-dividing ratio is changeable by means of programming. There are decode and encode modes for the scanning mode; timing signals that are decoded from the lower 2 bits of the scan counter are output in the decode mode, while the 4-bit binary output from the scan counter is decoded externally in the encode mode.

## M5L8279P-5

T-52-33-15

#### PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### COMMAND DESCRIPTION

There are eight commands provided for programming the operating modes of the M5L8279P-5. These commands are sent on the data bus with the signal  $\overline{\text{CS}}$  in low-level and the signal  $A_0$  in 1 and are stored in the M5L8279P-5 at the rising edge of the signal  $\overline{\text{WR}}$ . The order of the command execution is arbitrary.

#### 1. Mode Set Command

| MS    | В |   |   |   |   |   |   | L | SB |

|-------|---|---|---|---|---|---|---|---|----|

| Code: | 0 | 0 | 0 | D | D | κ | ĸ | К |    |

DD (Display mode set command)

- 0 0 8-8-bit character display-left entry

- 0 1 16-8-bit character display-left entry (Note1)

- 1 0 8-8-bit character display-right entry

- 1 1 16-8-bit character display-right entry

KKK (Keyboard mode set command)

- 0 0 0 Encoded display keyboard mode 2-key lockout (Note1)

- 0 0 1 Decoded display keyboard mode 2-key lockout

- 0 1 0 Encoded display keyboard mode N-key rollover

- 0 1 1 Decoded display keyboard mode N-key rollover

- 1 0-0 Encoded display, sensor mode

- 1 0 1 Decoded display, sensor mode

- 1 1 0 Encoded display, strobed entry mode

- 1 1 1 Decoded display, strobed entry mode

Note 1: Default after reset.

#### 2. Program Clock Command

| MS     | В |   |   |   |   |   |   | L | .SB |

|--------|---|---|---|---|---|---|---|---|-----|

| Code : | 0 | 0 | 1 | Р | Р | Ρ | Р | Р |     |

The external clock is divided by the prescaler value PPPP designated by this command to obtain the basic internal frequency.

When the internal clock is set to 100kHz, it will give a 5.1ms keyboard scan time and a 10.3ms debounce time. The prescale value that can be specified by PPPPP is from 2 to 31. In case PPPPP is 00000 or 00001, the prescale is set to 2. Default after a reset pulse is 31, but the prescale value is not cleared by the clear command.

#### 3. Read FIFO Command

| MSB   |   |   |   |    |   |   | LSB |   |                |  |  |  |

|-------|---|---|---|----|---|---|-----|---|----------------|--|--|--|

| Code: | 0 | 1 | 0 | ΑI | х | Α | Α   | Α | X = Don't care |  |  |  |

This command is used to specify that the following data readout ( $CS \cdot \overline{A_0} \cdot RD$ ) is from the FIFO. As long as data is to be read from the FIFO, no additional commands are necessary.

Al and AAA are used only in the sensor mode. AAA designates the address of the FIFO to be read, and Al is the auto-increment flag. Turning Al to 1 makes the address automatically incremented after the second read operation. This auto-increment bit does not affect the auto-increment of the display RAM.

#### 4. Read Display RAM Command

| M      | SB |   |   |    |   |   |   | Ł | .SI |

|--------|----|---|---|----|---|---|---|---|-----|

| Code ; | 0  | 1 | 1 | ΑI | Α | Α | Α | Α |     |

This command is used to specify that the following data readout ( $CS \cdot \overline{A_0} \cdot RD$ ) is from the display RAM. As long as data is to be read from the display RAM, no additional commands are necessary.

The data AAAA is the value with which the display RAM read/write counter is set, and it specifies the address of the display RAM to be read or written next.

Al is the auto-increment flag. Turning Al to 1 makes the address automatically incremented after the second read/write operation. This auto-increment bit does not affect the auto-increment of FIFO readout in the sensor mode.

#### 5. Write Display RAM Command

| MS    | В |   |   |    |   |   |   | t | .SB |

|-------|---|---|---|----|---|---|---|---|-----|

| Code: | 1 | 0 | 0 | ΑI | Α | Α | Α | Α |     |

With this command, following display RAM read/write addressing is achieved without changing the data readout source (FIFO or display RAM). Meaning of AI and AAAA are identical with read display RAM command.

#### 6. Display Write inhibit/Blanking Command

| MSB    |   |   |   |   |    |    |    | ŧ  | .SB            |

|--------|---|---|---|---|----|----|----|----|----------------|

| Code : | 1 | 0 | 1 | х | IW | IW | BL | BL | X = Don't care |

|        |   |   |   |   | A  | R  | Α  | A  |                |

The IW is a write inhibit bit to the display RAM that corresponds with the output A or B. Inhibit is activated by turning the IW 1.

The BL is used in blanking the out A or B. Blanking is activated by turning the BL 1. Setting both BL flags makes the signal  $\overline{BD}$  low-level so that it can be used in 8-bit display mode.

Resetting the flags makes all IW and BL turn 0.

#### 7. Clear Command

| ME    | 38 |   |   |   |    |    | •              | L  | .SB |

|-------|----|---|---|---|----|----|----------------|----|-----|

| Code: | 1  | 1 | 0 | С | Сь | Сь | C <sub>F</sub> | CA |     |

Cp: Clears the display RAM.

CD CD CD

- 0 X X No specific performance

- 1 0 X Entire contents of the display RAM are turned 0.

- 1 1 0 The contents of the display RAM are turned 20H (00100000 =  $0A_30A_20A_10A_0$  $0B_30B_20B_10B_0$ ).

- 1 1 Entire contents of the display RAM are turned 1.

#### MITSUBISHI(MICMPTR/MIPRC)

T-52-33-15

## PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

$C_{\text{F}}$ : Clears the status word and resets the interrupt signal (INT).

C<sub>A</sub>: Clears the display RAM and the status word and resets the interrupt signal (INT).

Clearing condition of the display RAM is determined by the lower 2 bits of the  $C_{\rm D}$

Clearing the display RAM needs some time ( $\sim$  160  $\mu$  second) and causes the display-unavailable status (DU) in the status word to be 1. The display RAM is not accessible for the duration of this time, even if the display mode was in 8-digit display mode or a decoded mode.

As both  $C_{\text{F}}$  and  $C_{\text{A}}$  function to reset the internal keydebounce counter, the key input under counting is ignored, and the internal FIFO counter is reset to make the interrupt signal low-level.

$C_A$  resets the internal timing counter, forcing  $S_0 \sim S_3$  to start from  $S_2 S_2 S_1 S_0 = 0000$  after the execution of the command.

8. End Interrupt/Error Mode Set Command

|       | MSB: | • |   |   |   |   |   | 1 | SB             |

|-------|------|---|---|---|---|---|---|---|----------------|

| Code: | 1    | 1 | 1 | E | х | X | Х | X | X = Don't care |

In the sensor matrix mode, an interrupt signal is generated at the beginning of the next key scan time to inhibit further writing to the FIFO when there is a change in the sensor switch. The interrupt request output INT is reset when the sensor RAM is read with the Auto-increment flag 0, or the execution of this command.

When E is kept in 0, depression of any sensor makes the second highest bit of the status word 1. When E is kept in 1, the status is kept 0 all the time.

When E is programmed to 1 in the N-key rollover mode, the execution of this command makes the chip operate in special error mode, during which time depression of more than two keys in a key debounce time causes an error and sets the second highest bit of the status word 1.

### STATUS WORD

MSB LSB

NNN: Indicates the number of characters in the FIFO during the keyboard and strobed entry modes.

- F: Indicates that the FIFO is filled up with 8 characters.

The number of characters existing in the FIFO (0 ~ 8 characters) can be known by means of the bits NNN and F (FNNN = 0000~FNNN = 1000).

- U: Underrun error flag This flag is set when a master CPU tries to read an empty FIFO.

- O: Overrun error flag

This flag is set when another character is strobed into a full FIFO.

The bits U and O cannot be cleared by status read.

They will be cleared by the clear command.

- S/E: Sensor closure/multiple error flag

When 111EXXXX is executed by turning E = 0, the bit

S/E in the status word is set when there is at least

one sensor closure.

When 111EXXXX is executed by turning E = 1

(special error mode), the bit S/E is set when there

are more than two key depressions made in a key

scan time.

- Display unavailable

This flag is set when a clear display command is executed, and announces that the display RAM is not accessible.

## M5L8279P-5

T-52-33-15

### PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### **CPU INTERFACE**

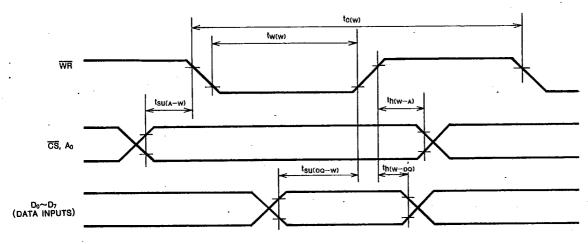

#### 1. Command Write

A command is written on the rising edge of the signal  $\overline{WR}$  with  $\overline{CS}$  low-level and  $A_0$  1.

#### 2. Data Write

Data is written to the display RAM on the rising edge of the signal  $\overline{WR}$  with  $\overline{CS}$  low-level and A<sub>0</sub> 0.

The address of the display RAM is also incremented on the rising edge of the signal  $\overline{WR}$  if AI is set for the display RAM.

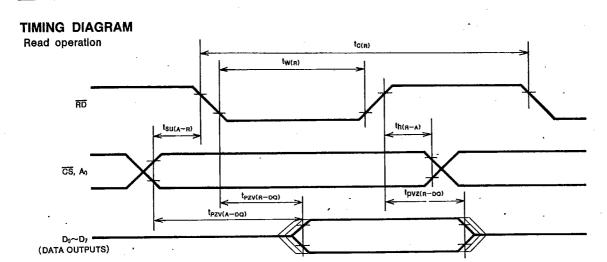

#### 3. Status Read

The status word is read when  $\overline{CS}$  and  $\overline{RD}$  are low-level and  $A_0$  is 1. The status word appears on the data bus as long as the signal  $\overline{RD}$  is low-level.

#### 4. Data Read

Data is read from either the FIFO or the display RAM with  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  are low-level and  $A_0$  is 0. The source of the data (FIFO or display RAM) is decided by the latest command (read display or read FIFO). The data read appears on the data bus as long as the signal  $\overline{\text{RD}}$  is low-level.

The trailing edge of the signal  $\overline{RD}$  increments the address of the FIFO or the display RAM when AI is set. After the reset, data will be read from the FIFO, however.

| Ao  | cs | RD | WR | Operation     |

|-----|----|----|----|---------------|

| 1   | L  | Н  | L  | Command write |

| 0   | L  | Н  | L  | Data write    |

| . 1 | L  | L, | н  | Status read   |

| 0   | L  | L  | н  | Data read     |

| х   | Н  | Х  | ×  | No operation  |

#### KEYBOARD INTERFACE

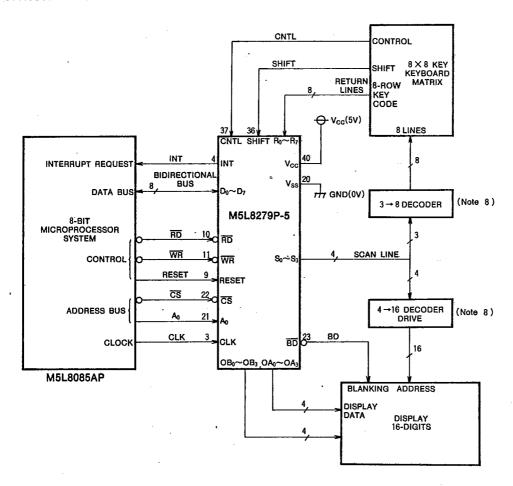

Keyboard interface is done by the scan timing signals ( $S_0 \sim S_3$ ), the return line inputs ( $R_0 \sim R_7$ ), the SHIFT and the CNTRL inputs.

In the decoded mode, the low-order of 2 bits of the internal scan counter are decoded and come out on the timing pins  $(S_0 \sim S_3)$ . In the encoded mode, the four binary bits of the scan counter are directly output on the timing pins, thus a 3-to-8 decoder must be employed to generate keyboard scan timing.

The return line inputs ( $R_0 \sim R_7$ ), the SHIFT and the CNTL inputs are pulled up high-level by internal pullup transistors until a switch closure pulls one low.

The internal key debounce logic works for a 64-key matrix that is obtained by combining the return line inputs with the scan timing.

For the keyboard interface, M5L8279P-5 has four distinctive modes that allow various kinds of applications. In the following explanation, a "key scan cycle" is the time needed to scan a 64-key matrix, and a "key debounce cycle" needs a duration of two "key scan" cycles. (In the decoded mode 32 keys, unlike 64 keys in the encoded mode, can be employed for a maximum key matrix due to the limit of timing signals.

However, both the key scan cycle and the key debounce cycle are the same as in the encoded mode.)

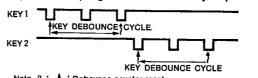

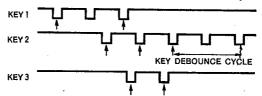

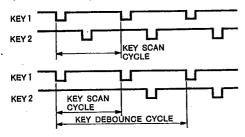

#### 1. 2-Key Lockout (Scanned Keyboard Mode)

The detection of a new key closure resets the internal debounce counter and starts counting. At the end of a key debounce cycle, the key is checked and entered into the FIFO if it is still down. An entry in the FIFO sets the INT output high. If any other keys are depressed in a key debounce cycle, the internal key debounce counter is reset each time it encounters a new key. Thus only a single-key depression within a key debounce duration is accepted, but all keys are ignored when more than two keys are depressed at the same time.

Example 1: Accepting two successive key depressions

Note 2: 1 Debounce counter reset

t : Key input

Example 2: Overlapped depression of three keys

Note 3: Only key 2 is acceptable

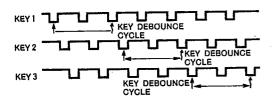

#### 2. N-Key Rollover (Scanned Keyboard Mode)

Each key depression is treated independently from all others so as to allow overlapped key depression. Detection of a new key depression makes the internal key debounce counter reset and start to count in a same manner as in the case of 2-key lockout. But, in N-key rollover, other key closures are entirely ignored within a key debounce cycle so that depression of any other keys would not reset the key debounce counter. In this way, overlapped key depression is allowed so as to enable the following key input:

The scanned key input signal does not always reflect the actual key depressing action, as the key matrix is scanned by the timing signal.

With N-key rollover, there is a mode provided with which error is caused when there are more than 2 key inputs in a key debounce cycle, which can be programmed by using the end interrupt/error mode set command. In this mode (special error mode), recognition of the above error sets the INT signal to high-level and sets the bit S/E in the status word.

In case 2 key entries are made separately in more than a debounce cycle, there would be no problem, as key depression is clearly identified. And no problem exists for 2-key lockout, as the both keys are recognized invalid.

#### Example of error (Special error mode)

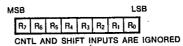

#### 3. Sensor Matrix Mode

The key debounce logic is disabled in this mode. As the image of the sensor switch is kept in the FIFO, any change in this status is reported to the CPU by means of the interrupt signal INT. Although a debounce circuit is not used in this mode, it has an advantage in that the CPU is able to know how long and when the sensor was depressed.

In the sensor matrix mode with the bit E=0 of the end interrupt/error mode set command, the second most significant bit of the status word (S/E bit) is set to 1 when any sensor switch is depressed.

Any sensor change detected by the M5L8279P-5 in one key scan cycle causes only once INT generation at the first timing of the next scan cycle.

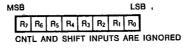

#### 4. Strobe Mode

The data is entered into the FIFO from the return lines ( $R_0 \sim R_7$ ) at the rising edge of a CNTL pulse. The INT goes high while any data exists in the FIFO, in the same manner as in the keyboard mode. The key debounce circuit will not operate.

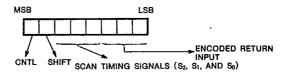

Formats of data entered into the FIFO in each of the above modes are described in the following:

#### Keyboard matrix

#### Sensor matrix mode

#### Storobe mode

## T-52-33-15

## MITSUBISHI (MICMPTR/MIPRC)

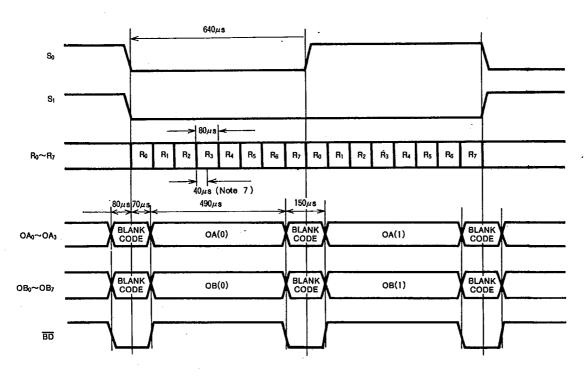

## DISPLAY INTERFACE

The display interface is done by 8 display outputs  $(OA_0 \sim OA_3, OB_0 \sim OB_3)$ , a blanking signal  $(\overline{BD})$ , and scan timing outputs  $(S_0 \sim S_3)$ .

The relation between the data bus and the display outputs is as shown below:

Clearing the display RAM is not achieved by the reset signal (9-pin) but requires the execution of the clear command.

The timing diagrams for both the encoded and decoded modes are shown below.

For the encoded mode, a 3-to-8 or 4-to-16 decoder is required, according to whether eight or sixteen digit display used.

#### (1) Encoded mode

#### (2) Decoded mode

Note 4 : Here  $P_{W}$  is  $640\mu s$  if the internal clock frequency is set to 100 kHz.

Timing relations of  $S_0$ ,  $\overline{BD}$ , and display outputs  $(OA_0 \sim OA_3, OB_0 \sim OB_3)$  are shown below.

PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

Note 5: Values of the output data shown in the slanted line areas are decided upon the clear command executed last to become the value of the display RAM after the reset. The values in the slanted areas after reset will go low-level. In the same manner, the values OA<sub>0</sub> ~ OA<sub>3</sub>, OB<sub>0</sub> ~ OB<sub>3</sub> are dependent on the clear command executed last. When the both A and B are blanked, the signal BD will be in low-level.

#### MITSUBISHI LSIs

## M5L8279P-5

T-52-33-15

## PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### 2. Right Entry KEY ENTRY METHODS The first data is entered in the rightmost position of a dis-1. Left Entry play. From the next entry, the display is shifted left one char-Address 0 in the display RAM corresponds to the leftmost acter and the new data is placed in the rightmost position. A position $(S_3S_2S_1S_0 = 0000)$ of a display and address 15 (or display position and a register address as viewed from the address 7 in 8-character display) to the rightmost position CPU change each time and do not correspond. $(S_3S_2S_1S_0 = 1111 \text{ or } S_2S_1S_0 = 111).$ The 17th (9th) character Auto-increment mode is entered back into the leftmost position. 14 15 0 • -DISPLAY RAM ADDRESS AS SEEN FROM THE CPU Auto-increment mode 1 1st entry 14 15 ←DISPLAY RAM ADDRESS AS SEEN FROM THE CPU 1st entry 2nd entry 2 2nd entry 3rd entry 2 14 15 15 16 16th entry 2 14 15 16 16th entry 14 15 2 15 16 17th entry 14 15 0 15 16 17 2 3 17th entry 0 14 15 18th entry 15 0 1 3 16 17 18 18th entry Auto-increment mode ←DISPLAY RAM ADDRESS AS SEEN FROM THE CPU Auto-increment mode 0 ←DISPLAY RAM 1st entry ADDRESS AS SEEN FROM THE CPU 1 1st entry 4 5 6 7 0 1 2 2nd entry 2nd entry **Execution of** the command 1 2 Execution of 10010101 1 the command ENTER NEXT AT LOCATIONS 5 AUTO-INCREMENT 10010101 ENTER NEXT AT LOCATIONS 5 AUTO-INCREMENT 2 3 4 5 6 7 0 2 3rd entry 1 2 3rd entry 2 3 4 5. 6 0

4th entry

4th entry

2

3

2

#### MITSUBISHI LSIs

## M5L8279P-5

# T-52-33-15

#### PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Parameter                            | Conditions                      | Ratings   | Unit     |

|----------------|--------------------------------------|---------------------------------|-----------|----------|

| Vga            | Supply voltage                       |                                 | -0.5~7    | . v      |

| V <sub>I</sub> | Input voltage                        | With respect to V <sub>SS</sub> | -0.5~7    | ٧        |

| Vo             | Output voltage                       |                                 | -0.5~7    | <b>v</b> |

| Pd             | Maximum power dissipation            | Ta=25°C                         | - 1000    | mW       |

| Topr           | Operating free-air temperature range |                                 | -20~75    | င        |

| Tatg           | Storage temperature range            |                                 | −60~150 · | Č        |

MITSUBISHI(MICMPTR/MIPRC)

## RECOMMENDED OPERATING CONDITIONS ( $T_a = -20 \sim 75^{\circ}C$ , unless otherwise noted.)

| Symbol | Parameter            |     | Limits |       | 11-14 |

|--------|----------------------|-----|--------|-------|-------|

| Symbol | ra anetei            | Min | Nom    | . Max | Unit  |

| Vcc    | Supply voltage       | 4.5 | 5      | 5.5   | ٧     |

| Vss    | Supply voltage (GND) |     | 0      |       | ٧     |

## **ELECTRICAL CHARACTERISTICS** $(T_a=-20 \sim 76 ^{\circ}\text{C}, V_{oc}=5 \text{V}\pm 10 \%, V_{ss}=0 \text{V}, \text{ unless otherwise noted.})$

| Symbol               | Parameter                                                  | Test conditions                     |                      | Limits      |      |      |

|----------------------|------------------------------------------------------------|-------------------------------------|----------------------|-------------|------|------|

|                      |                                                            |                                     | Min                  | Тур         | Max  | Unit |

| VIH(RL)              | High-level input voltage, for return line inputs           |                                     | 2.2                  | -           |      | v    |

| ViH                  | High-level input voltage, all others                       |                                     | 2.0                  |             |      | V    |

| VIL(RL)              | Low-level input voltage, for return line inputs            |                                     | Vss-0.5              |             | 1.4  | V    |

| ViL                  | Low-level input voltage, all others                        |                                     | V <sub>ss</sub> -0.5 |             | 0.8  | V    |

| VoH                  | High-level output voltage                                  | I <sub>OH</sub> =-400μA             | 2.4                  |             |      | V    |

| V <sub>OH(INT)</sub> | High-level output voltage, interrupt request output        | I <sub>OH</sub> =-400μA             | 3,5                  |             |      | V    |

| VoL                  | Low-level output voltage                                   | I <sub>OL</sub> =2.2mA              |                      |             | 0.45 | V    |

| laa.                 | Supply current from V <sub>CC</sub>                        |                                     |                      |             | 120  | mA   |

| 1                    | Input current, return line inputs, shift input and control | V <sub>i</sub> =V <sub>cc</sub>     |                      |             | 10   | μА   |

| li(RL)               | input                                                      | V₁=0V                               | -100                 |             |      |      |

| lı                   | Input current, all others                                  | V <sub>i</sub> =0V, V <sub>CC</sub> | -10                  |             | 10   | μА   |

| loz                  | Off-state output current                                   | Vo=0V~Vcc                           | -10                  | -           | 10   | μА   |

| C <sub>I</sub>       | Input terminal capacitance                                 | V <sub>i</sub> ≕V <sub>cc</sub>     | 5                    | <del></del> | 10   | pF   |

| Co                   | Output terminal capacitance                                | Vo=Vcc                              | 10                   |             | 20   | p₽   |

T-52-33-15

## PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

### TIMING REQUIREMENTS ( $T_a = -20 \sim 75 \text{C}$ , $V_{cc} = 5 \text{V} \pm 10 \text{W}$ , $V_{ss} = 0 \text{V}$ , unless otherwise noted.)

MITSUBISHI(MICMPTR/MIPRC)

#### Read Cycle

| Symbol            | Parameter                   | Took and distance | Limits |     |     | Unit |

|-------------------|-----------------------------|-------------------|--------|-----|-----|------|

|                   |                             | Test conditions   | Min    | Тур | Max | Unit |

| t <sub>C(B)</sub> | Read cycle time             |                   | 1000   |     |     | ពន   |

| tw(n)             | Read pulse width            | -                 | 250    |     |     | ns   |

| tsu(A-R)          | Address setup time befor RD |                   | 0      |     |     | ns   |

| th(R-A)           | Address setup time after RD |                   | 0      |     |     | ns   |

#### Write Cycle

| Symbol            | Parameter                       | Test conditions | Limits |     |     | Unit   |

|-------------------|---------------------------------|-----------------|--------|-----|-----|--------|

|                   |                                 |                 | Min    | Тур | Max | . Unit |

| t <sub>C(W)</sub> | Write cycle time                |                 | 1000   |     |     | กร     |

| tw(w)             | Write pulse width               |                 | 250    |     |     | ns     |

| tsu(A-W)          | Address setup time before WR    |                 | 0      |     |     | ns     |

| th(w-A)           | Address hold time after WR      |                 | 0      |     |     | ns     |

| tsu(DQ-W)         | Data Input setup time before WR | -               | 150    |     |     | ns     |

| th(w-pa)          | Data Input hold time after WR   |                 | 0      |     |     | ns     |

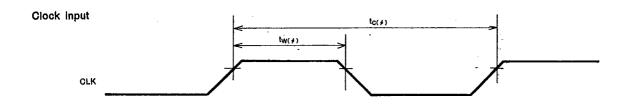

#### Other Timing

|         |                   | <b>*</b>        | Limits |     |     | Unit  |

|---------|-------------------|-----------------|--------|-----|-----|-------|

| Symbol  | Paramèter<br>-    | Test conditions | Min    | Тур | Max | Offit |

| to( + ) | Clock cycle time  |                 | 320    |     | DC  | ns    |

| tw(+)   | Clock pulse width |                 | 120    |     |     | กร    |

For an internal clock frequency of 100kHz

Key scan cycle time:

~ 5.1ms

490µs

Key debounce cycle time:

~10.3ms

Single digit display time:

Single-key scan time:

80µs

150µs 10µs

Display scan time:

~10.3ms

SWITCHING CHARACTERISTICS ( $T_a=-20\sim75\%$ ,  $V_{co}=5V\pm10\%$ ,  $V_{ss}=0V$ , unless otherwise noted.)

| Symbol     | Parameter                       | Test conditions       | Limits |     |     | Unit |

|------------|---------------------------------|-----------------------|--------|-----|-----|------|

|            |                                 |                       | Min    | Тур | Max | Unit |

| tpzv(R-DQ) | Output enable time after read   |                       |        |     | 150 | ns   |

| tpzv(A-DQ) | Output enabl time after address | C <sub>L</sub> ≕150pF |        |     | 250 | ns   |

| tpvz(R-DQ) | Output disable time after read  |                       | 10     |     | 100 | ns   |

Note 6 : A. C Testing waveform input pulse level input pulse rise time input pulse fall time Referens level input output

0.45~2.4V 20ns 20ns V<sub>IH</sub>=2V, V<sub>IL</sub>=0.8V V<sub>OH</sub>=2V, V<sub>OL</sub>=0.8V

Blanking time:

Internal clock cycle:

MITSUBISHI LSIs

## M5L8279P-5

T-52-33-15

## PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### Write operation

T-52-33-15

## MITSUBISHI(MICMPTR/MIPRC)

### PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

DISPLAY (This example is encoded display, left entry mode with internal clock cycle 10µsec. Scan timing output S2, S3 are not shown.)

Note 7: The scanned data on the return line is sampled serialy from R<sub>0</sub> to R<sub>7</sub>. Each data is latched in the middle of the each sampling period.

## M5L8279P-5

T-52-33-15

#### PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

#### **APPLICATION EXAMPLE**

Note 8: When using an 8-bit character display of more than 9 digits for the decoder display, it is necessary to provide two decoders for example 4 →10 decoder, 4 →16 decoder and key scan 3 → 8 decoder.

Only S₀, S₁ and S₂ may be used as inputs to the key scan 3 → 8 decoder.

(Don't drive the keyboard decoder with the MSB of the scan line.)